PRELIMINARY T-52-33-05

# 82261 CMOS MULTI-FUNCTION LSI PERIPHERAL

- CMOS Multi-function Peripheral Combining Four Components into Single Chip:

- -- 82C84A

- 82C59A

- -- 82C53

- --- 82C55A

- Same Functions and Complete Compatibility with Discrete NMOS Components\*

- Offers Optimal Board-Space Savings

- 80C86/C88 and 8086/88 Compatible

- 8 MHz Operation

- 100-Pin Gull-Wing Flat-package

- **Low-Power CMOS Technology**

- **TTL Compatible Inputs/Outputs**

The Intel 82261 is a high-performance CMOS multi-function peripheral designed to service the requirements of the 80C86/C88 and 8086/88 processors. The chip integrates four peripherals—82C84A, 82C59A, 82C53 and 82C55A, and is functionally identical to the discrete components. Its advanced, space-saving 100-pin gull-wing flat-package requires less than 1/3 board space of the separate components.

The clock oscillator (82C84A) generates up to 8 MHz system clock for the processor. The programmable interrupt controller (82C59A) can handle up to 8 vectored interrupts. Eight additional external interrupt controllers may be cascaded to support a maximum of 64 interrupts. The programmable interval timer (82C53) provides 3 independent 16-bit counters, each capable of handling clock inputs up to 5 MHz. The programmable I/O (82C55A) provides three 8-bit ports.

\*Except 8284A. Identical to 82C84A.

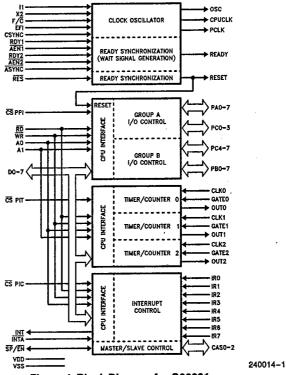

Figure 1. Block Diagram for G82261

PA1 22

PA0 23

V<sub>SS</sub> **2**4

V<sub>DD</sub> **□** 25

PRELIMINARY 82261 T-52-3 T-52-33-05 TOUR SERVICE OF SERVIC 100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76 75 🗖 V<sub>SS</sub> 74 🗖 🗚 v<sub>ss</sub> **d** 73 A1 v<sub>ss</sub> 口 72 🗖 IRO RDY1□ 71 🗖 IR1 AEN1 70 🗖 IR2 ASYNC 69 🗖 IR3 CSYNC 7 68 🗖 IR4 F/Ĉ□8 67 🗖 IR5 RES C 9 66 🗖 IR6 GATE2 10 65 🗖 IR7 OUT2 11 64 🗖 (NC) OUT1 12 63 (NC) о∪то 🗖 13 62 CSPIC (NC) ☐ 14 61 CSPIT V<sub>SS</sub> **□** 15 60 ☐ CSPPI PA7 🗖 16 59 🗖 V<sub>SS</sub> PA6 🗖 17 58 🗖 CLK2 PA5 18 57 GATE1 PA4 🗖 19 56 🗖 CLK1 PA3 🗖 20 55 CLK0 PA2 21

99D 57178

54 GATEO

53 INTA

52 1NT

51 **4** V<sub>SS</sub>

240014-2

Figure 2. 82261 Pin Configuration

intel

82261

PRELIMINARY

T-52-33-05

#### **FUNCTIONAL DESCRIPTION**

Figure 1 shows the functional block diagram of the 82261 LSI. A summary of features of individual functional units is listed below:

- A. Programmable Timer/Counter (Equivalent to 82C53)

- 3 16-bit counters—count binary/BCD

- Programmable rate generator

- Programmable one-shot

- · Square wave rate generator

- · Software triggered strobe

- Hardware triggered strobe

- B. Programmable Interrupt Controller (Equivalent to 89C59A)

- 8-level interrupt controller with programmable priorities

- Expandable to 64 levels in master/slave configuration

- · Masking capability for individual Interrupt levels

- C. Programmable I/O (Equivalent to 82C55A)

- 3 8-bit ports with programmable I/O operation

- Direct bit set/reset capabilities to ease peripheral control interface

- D. Clock Generator (Equivalent to 82C84A)

- Generates system and peripheral clocks for 8086/88 systems

- Supports a choice of a crystal or an external frequency source

- Provides READY synchronization

- Capable of clock synchronization with other 82C84A/82261 in multiprocessor configurations

- Generates system reset for the 8086/88 from Schmitt trigger input

For a detailed operation of these functional units, please refer to their respective data sheets in the Intel 'Microprocessor and Peripheral Handbook' (order #230843). The pin diagram and package dimensions for the 82261 are shown in Figure 2 and Figure 3 respectively.

240014-3

4826175 INTEL CORP (MIPRCS/PRPHL) PRELIMINARY 82261 T-52-33-05 18.00<sup>±0.2</sup> 22.90<sup>±0.4</sup> 0.10 = 0.10

Figure 3. Package Dimensions

UNIT = mm

99D 57181

PRELIMINARY

intel

82261

.T-52-33-05

# - Table 1. 82261 Pin Definitions\*

|               | <del></del> |      | Function                                                                                                                                                                                                                                   |  |  |  |  |

|---------------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol        | Pin         | Туре |                                                                                                                                                                                                                                            |  |  |  |  |

| D7-D0         | 78-85       | 1/0  | Bidirectional, TRI-STATE data bus. The bus is floated when RD, WR, and INTA are all active high.                                                                                                                                           |  |  |  |  |

| A1-A0         | 73-74       | I    | These input signals, in conjunction with $\overline{RD}$ , $\overline{WR}$ , and $\overline{CS}$ , are used to select the internal registers of each functional block. Refer to Tables 2–5 for a complete decoding information.            |  |  |  |  |

| WR            | 89          | ı    | An active low signal on this pin allows to write to the 82261. Data (D0-D7) is written to the 82261 at the rising edge of the $\overline{WR}$ pulse.                                                                                       |  |  |  |  |

| RD            | 88          | l    | An active low signal on this pin allows to read from the 82261.                                                                                                                                                                            |  |  |  |  |

| CSPIC         | 62          | 1    | Chip-Select for the Interrupt Controller block.                                                                                                                                                                                            |  |  |  |  |

| CSPIT         | 61          | ı    | Chip-Select for the Timer/Counter block.                                                                                                                                                                                                   |  |  |  |  |

| CSPPI         | 60          | 1    | Chip-Select for the I/O Control Block.                                                                                                                                                                                                     |  |  |  |  |

| RESET         | 93          | 0    | This is an active high signal used to reset the CPU. Internally, it is also used to reset the I/O port (82C55A). Its timing characteristics are determined by RES. All three ports, PA, PB, and PC, are set to the input mode upon reset.  |  |  |  |  |

| RES           | 9           | ı    | An active low on this pin generates the RESET signal. This is a schmitt trigger input to be connected to an R-C circuit to establish the power-up reset of proper duration.                                                                |  |  |  |  |

| X1, X2        | 1, 100      | . 1  | Crystal connection terminals. Crystal frequency should be three times the desired CPU clock rate. When F/C is strapped high, X1 should be tied to V <sub>CC</sub> or V <sub>SS</sub> , and X2 should be left open.                         |  |  |  |  |

| F/C           | 8           | ı    | $F/\overline{C}$ is a strapping option. When strapped low, CPU clock (CLK) is generated from the crystal input (X1, X2). When strapped high, CLK is generated from the EFI input.                                                          |  |  |  |  |

| EFI           | 98          | ı    | This input is used to generate the CPU clock (CLK) when the F/\overline{C} input is strapped high. The input signal is a square wave with 3 times the desired CPU clock. EFI must be tied high or low when F/\overline{C} is strapped low. |  |  |  |  |

| CLK           | .96         | 0    | System clock used by the CPU and other devices which connect to the processor's local bus. It has 1/3 of the crystal or the EFI frequency, and 1/3 duty cycle.                                                                             |  |  |  |  |

| PCLK          | 94          | 0    | Peripheral clock. It has 50% duty cycle and ½ of the CLK frequency.                                                                                                                                                                        |  |  |  |  |

| osc           | 97          | 0    | TTL level output of the internal oscillator circuitry. Its frequency is that of the crystal. The output is not affected when CSYNC is active high.                                                                                         |  |  |  |  |

| RDY1,<br>RDY2 | 4<br>91     | 1    | Data ready signals. When active high, it is an indication for the CPU from the currently selected device that data has been received, or is available. RDY1 is qualified by AEN1 while RDY2 is qualified by AEN2.                          |  |  |  |  |

| AEN1<br>AEN2  | 5<br>90     | ı    | Address enable signals. When active low, AEN1 qualifies RDY1, and AEN2 qualifies RDY2. Two AEN signals are provided to access two multi-master system buses. In non multi-master configurations, the AEN inputs are tied low.              |  |  |  |  |

| READY         | 92          | 0    | This is an active high signal synchronized with the RDY input. READY is cleared after the guaranteed hold time for the CPU has been met.                                                                                                   |  |  |  |  |

| ASYNC         | 6           | ı    | Ready synchronization mode select. When held low, READY becomes active after second synchronization. When high or open (an internal pull-up is provided), READY goes active with the first synchronization.                                |  |  |  |  |

99D 57182

82261

PRELIMINARY

T-52-33-05

### -Table 1. 82261 Pin Definitions\* (Continued)

|                         |                                                                    |      | Finallar                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|--------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                  | Pin                                                                | Туре | Function                                                                                                                                                                                                                                                                                                                                                                      |

| CSYNC                   | 7                                                                  | l    | Clock synchronization signal. This is an active high signal to permit other 82C84A and/or 82261 in the system to be synchronized to provide clocks that are in phase. Internal counters are reset when CSYNC is active high. Counting resumes when CSYNC goes low. CSYNC must be externally synchronized with EFI. Must be tied to ground when using the internal oscillator. |

| CLK0<br>CLK1<br>CLK2    | 55<br>56<br>58                                                     | -    | Clock input signal for corresponding timers/counters. When a count is set in a counter, count-down begins at the next falling edge of the related CLK.                                                                                                                                                                                                                        |

| OUT0<br>OUT1<br>OUT2    | 13<br>12<br>11                                                     | 0    | Timer/Counter outputs. The output waveforms are synchronized with the respective clocks.                                                                                                                                                                                                                                                                                      |

| GATE0<br>GATE1<br>GATE2 | 54<br>57<br>10                                                     | ı    | Gate Inputs. Control start/stop/reset operation in accordance with their respective timer/counter modes.                                                                                                                                                                                                                                                                      |

| PA7-PA0                 | 16-23                                                              | 1/0  | 8-bit I/O latch/buffer (same as 82C55A port A).                                                                                                                                                                                                                                                                                                                               |

| PB7-PB0                 | 35-43                                                              | 1/0  | 8-bit I/O latch/buffer (same as 82C55A port B).                                                                                                                                                                                                                                                                                                                               |

| PC7-PC0                 | 26-33                                                              | 1/0  | Same as 82C55A port C. It can be divided and used as two 4-bit ports under the mode control. Each 4-bit port contains a 4-bit latch and can be used for control signal outputs and status signal inputs in conjunction with ports A and B.                                                                                                                                    |

| IR7-IR0                 | 65-72                                                              | I    | Interrupt request signals. These are asynchronous inputs. A device may request an interrupt by raising (low → high) one of the IR lines (edge triggered method), or simply by holding it high (level triggered method).                                                                                                                                                       |

| INTA                    | 53                                                                 | l    | Interrupt acknowledge from the CPU. A sequence of INTA pulses issued by the CPU allows the 82261 to place the interrupt vector on the data bus.                                                                                                                                                                                                                               |

| INT                     | 52                                                                 | .0   | CPU interrupt. This pin goes active high whenever a valid interrupt request (IR) is asserted.                                                                                                                                                                                                                                                                                 |

| SP/EN                   | 48                                                                 | 1/0  | Slave program/Buffer enable. Used in the buffer mode to control buffer transceivers. In non-buffered mode it is used to designate a master $(SP=1)$ or slave $(SP=0)$ .                                                                                                                                                                                                       |

| V <sub>SS</sub>         | 2<br>3<br>15<br>24<br>34<br>44<br>51<br>59<br>75<br>77<br>86<br>95 | 1    | Ground.                                                                                                                                                                                                                                                                                                                                                                       |

| Vcc                     | 25<br>49<br>87<br>99                                               | ı    | Supply Voltage.                                                                                                                                                                                                                                                                                                                                                               |

<sup>\*</sup>Pins not listed here are all "No Connects" (NC).

4826175 0057183 5

4826175 INTEL CORP (MIPROS/PRPHL)

99D 57183

82261

T-52-33-05

PRELIMINARY

Table 2. Chip Selects for Individual Functional Blocks

| WR  | RD | CSPIT | CSPIO | CSPIC | ĪNTA | D0-7 | Operation of Data Bus         |

|-----|----|-------|-------|-------|------|------|-------------------------------|

| 1   | 0  | 0     | 1     | 1     | 1    | OUT  | Timer/Counter Part → Data     |

| i   | 0  | 1     | 0     | 1     | 1    | OUT  | I/O Part → Data               |

| i   | Ö  | 1     | 1     | 0     | 1    | OUT  | Interrupt Control Part → Data |

| 1 1 | Ì  | 1     | 1     | 1     | 0    | OUT  | Interrupt Control Part → Data |

| 0   | 1  | 0     | 1     | 1     | 1    | IN   | Data → Timer/Counter Part     |

| 0   | 1  | 1     | 0     | 1     | 1    | IN   | Data → I/O Part               |

| Ö   | 1  | 1     | 1     | 0     | • 1  | IN   | Data → Interrupt Control Part |

| 1   | 0  | Х     | X     | Х     | 1    | Z    | Data Bus High Impedance       |

| ×   | X  | 1     | 1     | 1     | 1    | Z    | Data Bus High Impedance       |

NOTE:

X stands for don't care

Table 3. Chip Selects for I/O Control Block

| A1  | A0  | WR  | RD  | CSPIO | Operation               |       |

|-----|-----|-----|-----|-------|-------------------------|-------|

| 0   | 0   | 1   | 0   | 0     | PA → Data Bus*          |       |

| . 0 | 1   | 1   | 0   | 0     | PB → Data Bus           | Read  |

| 1   | 0   | 1   | 0   | 0     | PC → Data Bus           |       |

| 1   | 1   | 1   | 0   | 0     | Inhibit                 |       |

| 0   | 0   | 0   | 1   | 0     | Data Bus → PA           | -     |

| Ō   | 1 1 | l o | · 1 | 0     | Data Bus → PB           |       |

| 1   | l ò | l ò | 1 1 | 0     | Data Bus → PC           | Write |

| 1   | 1   | 0   | 1   | 0     | Data Bus → Control      |       |

| X   | · X | Х   | Х   | 1     | Data Bus High Impedance |       |

| X   | X   | 1   | 1   | 0     | Data Bus High Impedance |       |

Table 4. Chip Selects for Timer/Counter Block

| A1 | A0 | WR | RD  | CSPIT | Operation of Bus              |

|----|----|----|-----|-------|-------------------------------|

| 0  | 0  | 1  | 0   | 0     | Read from Counter #0          |

| Ŏ  | 1  | 1  | 0   | 0     | Read from Counter #1          |

| 1  | 0  | 1  | 0   | 0     | Read from Counter #2          |

| 1  | 1  | 1  | 0   | 0     | No Operation (High Impedance) |

| 0  | 0  | 0  | 1   | 0     | Write to Counter #0           |

| Õ  | 1  | 0  | 1 1 | 0     | Write to Counter #1           |

| ì  | 0  | 0  | 1 1 | 0     | Write to Counter #2           |

| 1  | 1  | 0  | 1   | 0     | Write Mode Word               |

| X  | Х  | 1  | 1   | х     | Disable (High Impedance)      |

Table 5. Chip Selects for Interrupt Control Block

|    | Table 3. Only delete for interrupt definition block |     |     |    |       |      |                           |  |  |  |  |

|----|-----------------------------------------------------|-----|-----|----|-------|------|---------------------------|--|--|--|--|

| D4 | D3                                                  | .A0 | WR  | RD | CSPIC | INTA | Operation of Bus          |  |  |  |  |

| X  | X                                                   | 0   | 1   | 0  | 0     | 1    | Read from IRR, ISR        |  |  |  |  |

| X  | X                                                   | 1   | 1   | 0  | 0 .   | 1    | Read from IMR             |  |  |  |  |

| 0  | 0                                                   | 0   | 0   | 1  | 0     | 1    | Write OCW2                |  |  |  |  |

| Õ  | 1                                                   | Ö   | Ŏ   | 1  | Ö     | 1    | Write OCW3                |  |  |  |  |

| 1  | x                                                   | ٥   | Ó   | 1  | 0     | 1 1  | Write ICW1                |  |  |  |  |

| X  | x                                                   | 1   | Ó   | 1  | 0     | 1    | Write ICW2, ICW3 and ICW4 |  |  |  |  |

| X  | х                                                   | Х   | 1   | 1  | 0     | 1    | High Impedance            |  |  |  |  |

| X  | X                                                   | X   | l x | X  | 1     | 1    | High Impedance            |  |  |  |  |

| X  | X                                                   | Х   | 1   | 1  | 1     | 0    | Read the Interrupt Vector |  |  |  |  |

99D

PRELIMINARY

82261

T-52-33-05

#### ABSOLUTE MAXIMUM RATINGS

Operating Temperature .....0°C to +70°C Storage Temperature ..... -65°C to +150°C Supply Voltage  $V_{DD}$  ..... -0.3V to +7.0VVoltage on any Input . . . . . . . -0.3V to  $V_{DD} + 0.3V$ Voltage on any Output ...... -0.3V to  $V_{DD} + 0.3V$ Power Dissipation . . . . . . . . . . . . . . . . . . 500 mW

\*Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

NOTICE: Specifications contained within the following tables are subject to change.

### D.C. CHARACTERISTICS $T_A = 0^{\circ}C$ to $70^{\circ}C$ , $V_{CC} = +5V \pm 10\%$ .

| Symbol                             | Parameter                              | Min      | Max   | Units | Test Conditions                                                                                                                                                                                  |

|------------------------------------|----------------------------------------|----------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>                    | Input Low Voltage                      | +0.3V    | 0.8   | ٧     |                                                                                                                                                                                                  |

| ViH                                | Input High Voltage                     | 2.0      | Vcc   | V     | 2.5V for RES                                                                                                                                                                                     |

| V <sub>OL</sub>                    | Output Low Voltage                     |          | 0.45V | ٧     | (Note 1)                                                                                                                                                                                         |

| V <sub>OH</sub>                    | Output High Voltage                    | (Note 2) |       | V     | (Note 2)                                                                                                                                                                                         |

| ILI                                | Input Leakage Current                  | (Note 3) | +10   | μΑ    | V <sub>IN</sub> = V <sub>CC</sub> to 0V                                                                                                                                                          |

| lofL                               | Output Float Leakage Current           | -10      | +10   | μΑ    | V <sub>IN</sub> = V <sub>CC</sub> to 0V                                                                                                                                                          |

| I <sub>DAR</sub>                   | Darlington Drive Current               | -1       |       | mA    | For ports A, B, C of I/0 Control                                                                                                                                                                 |

| I <sub>DD</sub>                    | V <sub>CC</sub> Supply Current         |          | 80    | mA    | (Note 4)                                                                                                                                                                                         |

| ICCSB                              | V <sub>CC</sub> Supply Current-Standby |          | 10    | μΑ    | V <sub>CC</sub> = 5.5V  V <sub>IN</sub> = V <sub>CC</sub> or GND  Port Conditions  If I/P = Open/High  O/P = Open Only  With Data Bus = High/Low  CS = High  Reset = Low  Pure Inputs = Low/High |

| V <sub>INH</sub> -V <sub>IHR</sub> | RES Input Hysteresis                   | 0.25     |       | V     |                                                                                                                                                                                                  |

#### NOTES:

= 5 mA for CLK, PCLK, OSC, READY, RESET

= 2.5 mA for Ports A, B, C of I/O Control Block

= 2.2 mA for other outputs

= 2.2 mA for other outputs 2.  $V_{OH} = 4V$ ,  $I_{OH} = -1$  mA for CLK = 2.8V,  $I_{OH} = -1$  mA for PCLK, OSL, READY, RESET = 3.5V,  $I_{OH} = -100$   $\mu$ A for INT = 2.4V,  $I_{OH} = -400$   $\mu$ A for other outputs 3.  $I_{LI}$  Min = -300  $\mu$ A for IRO-IR7 and -200  $\mu$ A for ASYNC 4. Output: Open,  $f_{CLKO} \sim 2 = 5$  MHz,  $f_{OSC} = 24$  MHz

#### CAPACITANCE TA = 25°C, VCC = GND = 0V

| Symbol           | Parameter          | Min | Max | Units | Test Conditions               |

|------------------|--------------------|-----|-----|-------|-------------------------------|

| C <sub>IN</sub>  | Input Capacitance* |     | 10  | pF    | Unmeasured pins returned      |

| C <sub>I/O</sub> | I/O Capacitance*   |     | 20  | pF    | to GND f <sub>c</sub> = 1 MHz |

<sup>\*</sup>Except X1, X2, OSC, CLK, PCLK, READY, RESET.

82261

T-52-33-05

A.C. CHARACTERISTICS  $-T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{DD} = 5.0V \pm 10\%$

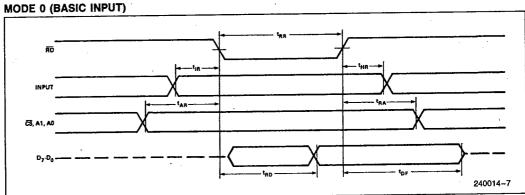

TIMINGS FOR READ/WRITE CYCLES (for timer/counter, I/O, and Interrupt control blocks)

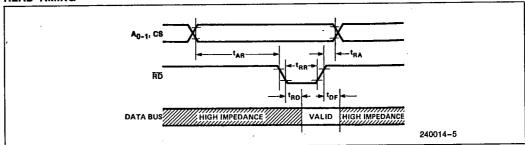

#### READ CYCLE

| Symbol          | Parameter                                                                       | Min     | Max | Units    |

|-----------------|---------------------------------------------------------------------------------|---------|-----|----------|

| t <sub>AR</sub> | CS*, Address Stable before READ for Timer/Counter for I/O and Interrupt Control | 30<br>0 |     | ns<br>ns |

| t <sub>RA</sub> | CS*, Address Hold Time for READ                                                 | 0       | •   | ns       |

| tan             | READ Pulse Width                                                                | 150     |     | ns       |

| t <sub>RD</sub> | Data Delay from READ (Note 1)                                                   |         | 120 | ns       |

| t <sub>DF</sub> | READ to Data Floating (Note 2)                                                  | 10      | 85  | ns       |

| t <sub>BV</sub> | Command Recovery Time                                                           | 200     |     | ns       |

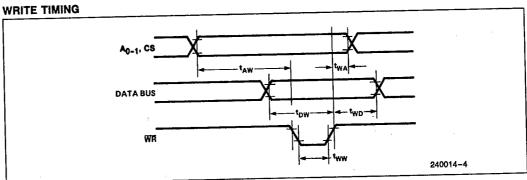

#### WRITE CYCLE

| Symbol          | Parameter                                                               | Min        | Max      | Units    |

|-----------------|-------------------------------------------------------------------------|------------|----------|----------|

|                 | CS, Address Stable before WRITE                                         | 0          |          | ns       |

| t <sub>WA</sub> | CS, Address Hold Time for WRITE                                         | 0          |          | ns       |

| tww             | WRITE Pulse Width<br>for Timer/Counter<br>for I/O and Interrupt Control | 160<br>120 |          | ns<br>ns |

| t <sub>DW</sub> | Data Set Up Time for WRITE                                              | 120        |          | ns       |

| twp             | Data Hold Time for WRITE                                                | 0          |          | ns       |

| t <sub>RV</sub> | Command Recovery Time                                                   | 200        | <u> </u> | ns       |

<sup>\*</sup>CS means CSPIT, CSPPI, or CSPIC.

#### NOTES:

1.  $C_L = 150 \text{ pF}.$ 2.  $C_L = 20 \text{ pF}, R_L = 2 \text{ K}\Omega.$

# WAVEFORMS FOR READ/WRITE CYCLES

(for Timer/Counter, I/O, and Interrupt Control Blocks)

2-323

intel

82261

PRELIMINARY T-52-33-05

### A.C. CHARACTERISTICS (Continued)

**WAVEFORMS FOR READ/WRITE CYCLES** (for Timer/Counter, I/O, and Interrupt Control Blocks) (Continued)

#### **READ TIMING**

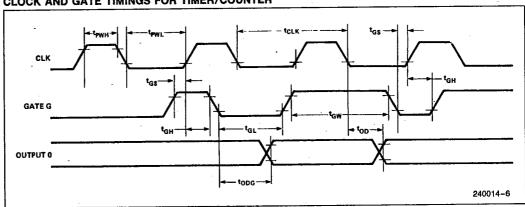

#### **CLOCK AND GATE TIMINGS FOR TIMER/COUNTER**

| Symbol           | Parameter                         | Min | Max | Units |

|------------------|-----------------------------------|-----|-----|-------|

| tCLK             | Clock Period                      | 200 | DC  | ns    |

| tpwH             | High Pulse Width                  | 80  |     | ns    |

| t <sub>PWL</sub> | Low Pulse Width                   | 60  |     | ns    |

| t <sub>GW</sub>  | Gate Width High                   | 50  |     | ns    |

| t <sub>GL</sub>  | Gate Width Low                    | 50  |     | ns    |

| tgs              | Gate Set Up Time to CLK↑          | 50  |     | ns    |

| tgн              | Gate Hold Time after CLK ↑        | 50  |     | ns    |

| top              | Output Delay from CLK ↓ (Note 1)  |     | 150 | ns    |

| topg             | Output Delay from Gate ↓ (Note 1) |     | 120 | ns    |

# NOTES:

# CLOCK AND GATE TIMINGS FOR TIMER/COUNTER

<sup>1.</sup> C<sub>L</sub> = 150 pF.

99D 57187

82261

PRELIMINARY T-52-33-05

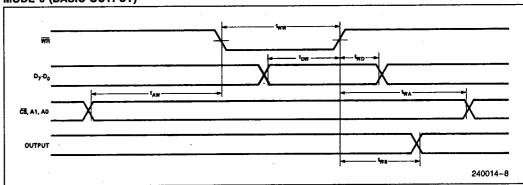

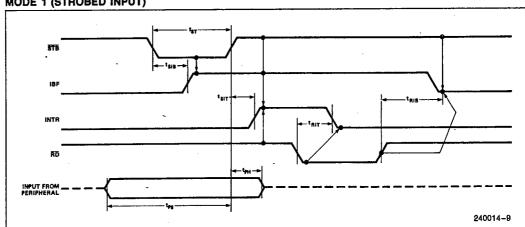

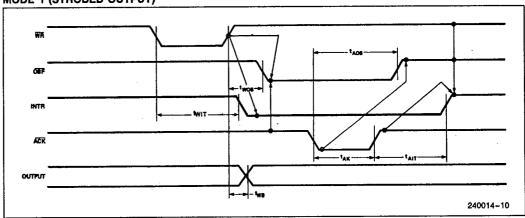

# TIMING FOR I/O CONTROL BLOCK

| Symbol           | Parameter                                          | Min | Max | Units | Test<br>Conditions      |

|------------------|----------------------------------------------------|-----|-----|-------|-------------------------|

| t <sub>WB</sub>  | WR = 1 to Output                                   |     | 350 | ns    | C <sub>L</sub> = 150 pF |

| t <sub>IR</sub>  | Peripheral Data Before RD                          | 0   |     | ns    |                         |

| tHR              | Peripheral Data After RD                           | 0   |     | ns    |                         |

| t <sub>AK</sub>  | ACK Pulse Width                                    | 300 |     | ns    |                         |

| tsT              | STB Pulse Width                                    | 350 |     | ns    |                         |

| tps              | Per. Date Before STB High                          | 0   |     | ns    | ·                       |

| t <sub>PH</sub>  | Per. Data After STB High                           | 150 |     | ns    |                         |

| t <sub>AD</sub>  | ACK = 0 to Output                                  |     | 300 | ns    | $C_{L} = 150  pF$       |

| t <sub>KD</sub>  | ACK = 1 to Output Float                            | 20  | 250 | ns    | C <sub>L</sub> = 150 pF |

| twoB             | $\overline{WR} = 1 \text{ to } \overline{OBF} = 0$ |     | 300 | ns    | C <sub>L</sub> = 150 pF |

| tAOB             | $\overline{ACK} = 0$ to $\overline{OBF} = 1$       |     | 350 | ns    | C <sub>L</sub> = 150 pF |

| t <sub>SIB</sub> | STB = 0 to IBF = 1                                 |     | 300 | ns    | C <sub>L</sub> = 150 pF |

| t <sub>RIB</sub> | $\overline{RD} = 1 \text{ to IBF} = 0$             |     | 300 | ns    | $C_{L} = 150  pF$       |

| tRIT             | RD = 0 to INTR = 1                                 |     | 400 | ns    | C <sub>L</sub> = 150 pF |

| tsıt             | STB = 1 to INTR = 1                                | -   | 300 | ns    | C <sub>L</sub> = 150 pF |

| tAIT             | ACK = 1 to INTR = 1                                |     | 350 | ns    | $C_{L} = 150  pF$       |

| t <sub>WIT</sub> | $\overline{WR} = 0$ to $\overline{INTR} = 0(1)$    |     | 450 | ns    | C <sub>L</sub> = 150 pF |

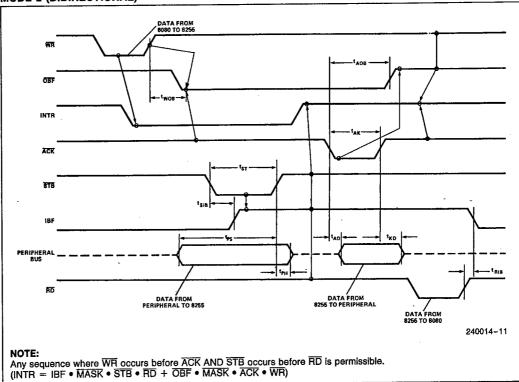

# **WAVEFORMS FOR I/O CONTROL BLOCK**

**NOTE:** 1. INTR  $\uparrow$  may occur as early as  $\overline{\text{WR}} \downarrow$ .

**PRELIMINARY**

82261

T-52-33-05

# A.C. CHARACTERISTICS (Continued)

MODE 0 (BASIC OUTPUT)

MODE 1 (STROBED INPUT)

MODE 1 (STROBED OUTPUT)

99D 57189

82261

PRELIMINARY

T-52-33-05

# WAVEFORMS FOR I/O CONTROL BLOCK (Continued)

MODE 2 (BIDIRECTIONAL)

99D 57190

82261

THE GREEN THE STATE OF THE STATE OF

PRELIMINARY

T-52-33-05

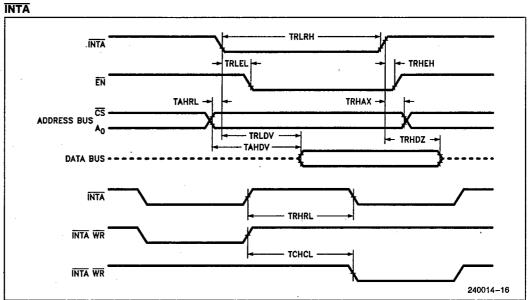

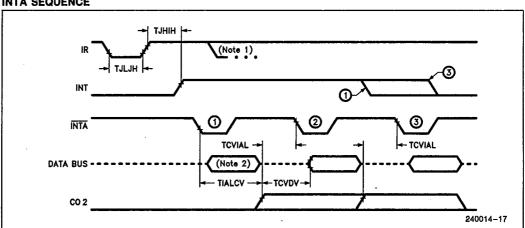

# TIMING FOR INTA CYCLES

#### TIMING REQUIREMENTS

| Symbol | Parameter                                                                                                  | Min | Max | Units | Test Conditions |

|--------|------------------------------------------------------------------------------------------------------------|-----|-----|-------|-----------------|

| TAHRL  | A0/CS Setup to INTA ↓                                                                                      | 0   |     | ns    |                 |

| TRHAX  | A0/CS Hold after ĪNTĀ↑                                                                                     | 0   |     | ns    |                 |

| TRLRH  | RD/INTA Pulse Width                                                                                        | 120 |     | ns    |                 |

| TJLJH  | Interrupt Request Width (Low)                                                                              | 100 |     | ns    | (Note 1)        |

| TCVIAL | Cascade Setup to Second or Third INTA ↓ (Slave Only)                                                       | 40  |     | ns    |                 |

| TRHRL  | End of INTA to next INTA within an INTA sequence only                                                      | 160 |     | ns    |                 |

| TCHCL  | End of Command to next Command (Not same command type) End of INTA sequence to next INTA sequence (Note 2) | 250 |     | ns    |                 |

#### NOTES:

# TIMING FOR INTA CYCLES (Continued)

#### **TIMING RESPONSES**

| Symbol | Parameter                                     | Min | Max | Units |

|--------|-----------------------------------------------|-----|-----|-------|

| TRLDV  | Data Valid from ĪNTĀ ↓                        |     | 120 | ns    |

| TRHDZ  | Data Float after INTA ↑                       | 10  | 85  | ns    |

| TJHIH  | Interrupt Output Delay                        |     | 300 | ns    |

| TIALCV | Cascade Valid from First INTA ↓ (Master Only) |     | 360 | ns    |

| TRLEL  | Enable Active from RD ↓ or INTA ↓             |     | 100 | ns    |

| TRHEH  | Enable Inactive from RD↑ or INTA↑             | ,   | 150 | ns    |

| TAHDV  | Data Valid from Stable Address (CS, A0, INT)  |     | 200 | ns    |

| TCVDV  | Cascade Valid to Valid Data                   |     | 200 | пѕ    |

<sup>1.</sup> This is the low time required to clear the input latch in the edge triggered mode.

2. Worst case timing for TCHCL in an actual microprocessor system is typically much greater than 400 ns (i.e. 8085A = 1.6 μs, 8085-A2 = 1 μs, 80C86 = 1 μs, 80C86-2 = 625 ns).

99D 57191

82261

PRELIMINARY T-52-33-05

### **WAVEFORMS FOR INTA CYCLES**

### **INTA SEQUENCE**

#### NOTES:

- Interrupt request must remain HIGH at least until leading edge of first INTA.

Cycle 1 in 80C86 and 80C88 systems, the Data Bus Is not active.

99D 57192

82261

PRELIMINARY T-52-33-05

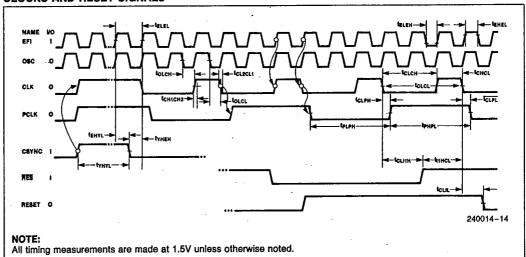

# TIMINGS FOR CLOCK GENERATOR BLOCK

#### **TIMING REQUIREMENTS**

| Symbol              | Parameter                        | Min                   | Max | Units | Test Conditions         |

|---------------------|----------------------------------|-----------------------|-----|-------|-------------------------|

| t <sub>EHEL</sub>   | External Frequency HIGH Time     | 13                    |     | ns    | 90%-90% V <sub>IN</sub> |

| teleh               | External Frequency LOW Time      | 13                    |     | ns    | 10%-10% V <sub>IN</sub> |

| tELEL               | EFI Period                       | 41.6                  |     | ns    |                         |

|                     | XTAL Frequency                   | 8                     | 24  | MHz   |                         |

| t <sub>R1VCL</sub>  | RDY1, RDY2 Active Setup to CLK   | 35                    |     | ns    | ASYNC = HIGH            |

| <sup>t</sup> R1VCH  | RDY1, RDY2 Active Setup to CLK   | 35                    |     | ns    | ASYNC = LOW             |

| t <sub>R1VCL</sub>  | RDY1, RDY2 Inactive Setup to CLK | 35                    |     | ns    |                         |

| t <sub>CLR1X</sub>  | RDY1, RDY2 Hold to CLK           | 0                     |     | ns    |                         |

| tayvcl              | ASYNC Setup to CLK               | 50                    |     | ns    |                         |

| tCLAYX              | ASYNC Hold to CLK                | 0                     |     | ns    |                         |

| t <sub>A1VR1V</sub> | AEN1, AEN2 Setup to RDY1, RDY2   | 15                    |     | ns    |                         |

| t <sub>CLA1X</sub>  | AEN1, AEN2 Hold to CLK           | 0                     |     | ns    |                         |

| tyHEH               | CSYNC Setup to EFI               | 20                    |     | ns    |                         |

| t <sub>EHYL</sub>   | CSYNC Hold to EFI                | 10                    |     | ns    |                         |

| tyHYL               | CSYNC Width                      | 2 • t <sub>ELEL</sub> |     | ns    |                         |

| t <sub>I1HCL</sub>  | RES Setup to CLK (Note 3)        | 65                    |     | ns    | (Note 2)                |

| t <sub>CLI1H</sub>  | RES Hold to CLK                  | 20                    |     | ns    | (Note 2)                |

| tiliH               | Input Rise Time                  |                       | 20  | ns    | (Note 1)                |

| t <sub>IHIL</sub>   | Input Fall Time                  |                       | 12  | ns    | (Note 1)                |

NOTES:

1. Transition between 0.8V and 2.0V.

2. Setup and hold necessary only to guarantee recognition at next clock.

3. For system reset, period of RES pulse must be at least 50 μs during or after power-on. Subsequent reset pulse should be 500 ns min.

99D 57193

82261

PRELIMINARY

T-52-33-05

# TIMINGS FOR CLOCK GENERATOR BLOCK (Continued)

#### **TIMING RESPONSES**

| Symbol             | Parameter                         | Min                                                    | Max | Units | Test Conditions                 |

|--------------------|-----------------------------------|--------------------------------------------------------|-----|-------|---------------------------------|

| t <sub>CLCL</sub>  | CLK Cycle Period                  | 125                                                    |     | ns    |                                 |

| <sup>t</sup> CHCL  | CLK HIGH Time                     | (1/3 t <sub>CLCL</sub> ) + 2                           |     | ns    |                                 |

| <sup>t</sup> CLCH  | CLK LOW Time                      | (2/3 t <sub>CLCL</sub> ) -15                           |     | ns    |                                 |

| tCH1CH2<br>tCL2CL1 | CLK Rise or Fall Time             |                                                        | 10  | ns    | 1.0V to 3.5V                    |

| t <sub>PHPL</sub>  | PCLK HIGH Time                    | t <sub>CLCL</sub> - 20                                 |     | ns    |                                 |

| t <sub>PLPH</sub>  | PCLK LOW Time                     | t <sub>CLCL</sub> - 20                                 |     | ns    |                                 |

| <sup>t</sup> RYLCL | Ready Inactive to<br>CLK (Note 2) | -8                                                     |     | ns    |                                 |

| <sup>t</sup> RYHCH | Ready Active to CLK (Note 1)      | ( <sup>2</sup> / <sub>3</sub> t <sub>CLCL</sub> ) — 15 |     | ns    |                                 |

| tCLIL              | CLK to Reset Delay                |                                                        | 40  | ns    |                                 |

| tCLPH              | CLK to PCLK HIGH DELAY            |                                                        | 22  | ns    |                                 |

| tCLPL              | CLK to PCLK LOW Delay             |                                                        | 22  | ns    |                                 |

| tolch              | OSC to CLK HIGH Delay             | -5                                                     | 22  | ns    |                                 |

| tolcl              | OSC to CLK LOW Delay              | 2                                                      | 35  | ns    |                                 |

| <sup>t</sup> OLOH  | Output Rise Time<br>(expect CLK)  |                                                        | 20  | ns    | Except CLK<br>from 0.8V to 2.0V |

| <sup>t</sup> OHOL  | Output Fall Time<br>(expect CLK)  |                                                        | 12  | ns    | Expect CLK from 2.0V to 0.8V    |

### NOTES:

Applies only to T3 and TW states.

Applies only to T2 states.

PRELIMINARY

4826175 INTEL CORP (MIPRCS/PRPHL)

82261

T-52-33-05

# WAVEFORMS FOR CLOCK GENERATOR BLOCK

#### **CLOCKS AND RESET SIGNALS**

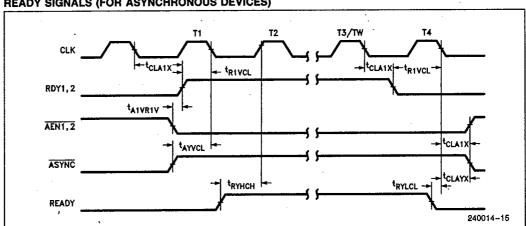

# READY SIGNALS (FOR ASYNCHRONOUS DEVICES)

PRELIMINARY

T-52-33-05

inte

82261

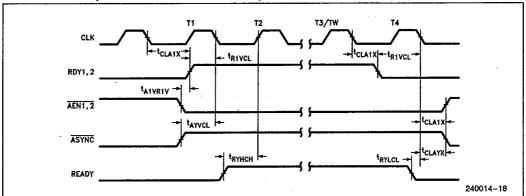

### WAVEFORMS FOR CLOCK GENERATOR BLOCK (Continued)

#### **READY SIGNALS (FOR SYNCHRONOUS DEVICES)**

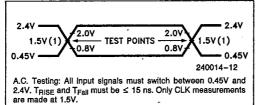

#### A.C. TESTING INPUT, OUTPUT WAVEFORM

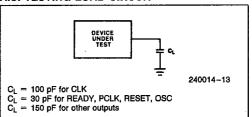

#### A.C. TESTING LOAD CIRCUIT

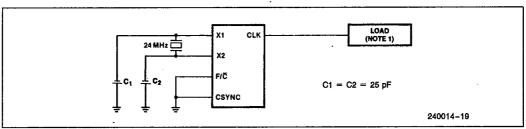

Clock High and Low Time (Using X1, X2)

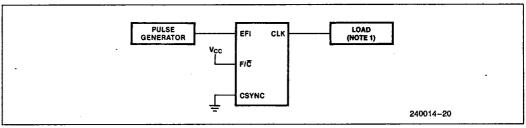

Clock High and Low Time (Using EFI)

**NOTE:** 1. C<sub>L</sub> = 100 pF

99D 57196

D PRELIMINARY

82261

T-52-33-05

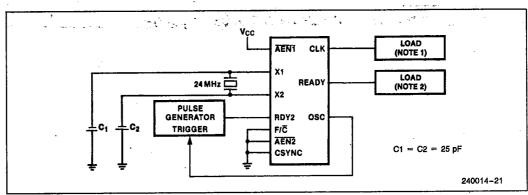

Ready to Clock (Using X1, X2)

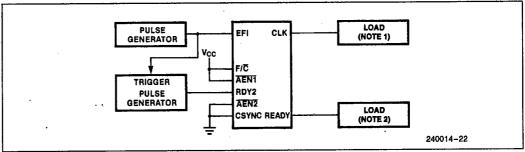

Ready To Clock (Using EFI)

**NOTES:** 1. C<sub>L</sub> = 100 pF 2. C<sub>L</sub> = 30 pF