# 8742 UNIVERSAL PERIPHERAL INTERFACE 8-BIT SLAVE MICROCONTROLLER

- 8742: 12 MHz

- Pin, Software and Architecturally Compatible with 8741A

- 8-Bit CPU plus ROM, RAM, I/O, Timer and Clock in a Single Package

- 2048 x 8 EPROM, 128 x 8 RAM, 8-Bit Timer/Counter, 18 Programmable I/O Pins

- One 8-Bit Status and Two Data Registers for Asynchronous Slave-to-Master Interface

- DMA, Interrupt, or Polled Operation Supported

- Fully Compatible with all Intel and Most Other Microprocessor Families

- Expandable I/O

- RAM Power-Down Capability

- Over 90 Instructions: 70% Single Byte

- Available in EXPRESS

- Standard Temperature Range

290256-2

The Intel 8742 is a general-purpose Universal Peripheral Interface that allows designers to grow their own customized solution for peripheral device control. It contains a low-cost microcomputer with 2K of program memory, 128 bytes of data memory, 8-bit timer/counter, and clock generator in a single 40-pin package. Interface registers are included to enable the UPI device to function as a peripheral controller in the MCS®-48, MCS-51, MCS-80, MCS-85, 8088, 8086 and other 8-, 16-bit systems.

The 8742 is software, pin, and architecturally compatible with the 8741A. The 8742 doubles the on-chip memory space to allow for additional features and performance to be incorporated in upgraded 8741A designs. For new designs, the additional memory and performance of the 8742 extends the UPI concept to more complex motor control tasks, 80-column printers and process control applications as examples.

Figure 1. Pin Configuration

November 1991 Order Number: 290256-001

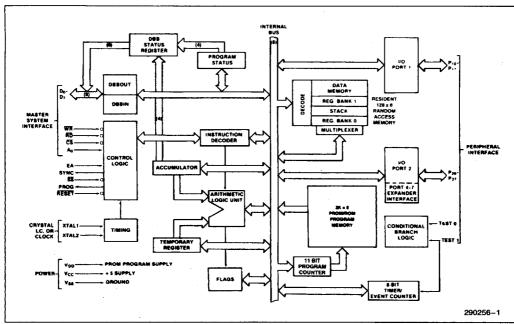

Figure 2. Block Diagram

**Table 1. Pin Description**

| Symbol                                  | DIP<br>Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------|-------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST 0,<br>TEST 1                       | 1<br>39           | _    | TEST INPUTS: Input pins which can be directly tested using conditional branch instructions.  FREQUENCY REFERENCE: TEST 1 (T <sub>1</sub> ) also functions as the event timer input (under software control). TEST 0 (T <sub>0</sub> ) is used during PROM programming and EPROM verification.                                                                                                                                                                                                                                                                                 |

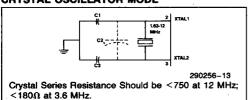

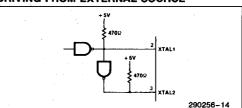

| XTAL 1,<br>XTAL 2                       | 2                 | - 1  | INPUTS: Inputs for a crystal, LC or an external timing signal to determine the internal oscillator frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RESET                                   | 4                 | 1    | RESET: Input used to reset status flip-flops and to set the program counter to zero.  RESET is also used during EPROM programming and verification.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SS                                      | 5                 | l    | <b>SINGLE STEP:</b> Single step input used in conjunction with the SYNC output to step the program through each instruction (EPROM). This should be tied to $\pm 5V$ when not used.                                                                                                                                                                                                                                                                                                                                                                                           |

| CS                                      | 6                 | _    | CHIP SELECT: Chip select input used to select one UPI microcomputer out of several connected to a common data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EA                                      | 7                 | _    | <b>EXTERNAL ACCESS:</b> External access input which allows emulation, testing and EPROM verification. This pin should be tied low if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RD                                      | 8                 | -    | <b>READ:</b> I/O read input which enables the master CPU to read data and status words from the OUTPUT DATA BUS BUFFER or status register.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Ao                                      | 9                 | _    | <b>COMMAND/DATA SELECT:</b> Address Input used by the master processor to indicate whether byte transfer is data ( $A_0=0$ , F1 is reset) or command ( $A_0=1$ , F1 is set). $A_0=0$ during program and verify operations.                                                                                                                                                                                                                                                                                                                                                    |

| WR                                      | 10                | 1    | WRITE: I/O write input which enables the master CPU to write data and command words to the UPI INPUT DATA BUS BUFFER.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SYNC                                    | 11                | 0    | <b>OUTPUT CLOCK</b> : Output signal which occurs once per UPI instruction cycle. SYNC can be used as a strobe for external circuitry; it is also used to synchronize single step operation.                                                                                                                                                                                                                                                                                                                                                                                   |

| D <sub>0</sub> -D <sub>7</sub><br>(BUS) | 12-19             | 1/0  | DATA BUS: Three-state, bidirectional DATA BUS BUFFER lines used to interface the UPI microcomputer to an 8-bit master system data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P <sub>10</sub> -P <sub>17</sub>        | 27-34             | 1/0  | PORT 1: 8-bit, PORT 1 quasi-bidirectional I/O lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P <sub>20</sub> -P <sub>27</sub>        | 21-24<br>35-38    | 1/0  | <b>PORT 2:</b> 8-bit, PORT 2 quasi-bidirectional I/O lines. The lower 4 bits $(P_{20}-P_{23})$ interface directly to the 8243 I/O expander device and contain address and data information during PORT 4-7 access. The upper 4 bits $(P_{24}-P_{27})$ can be programmed to provide interrupt Request and DMA Handshake capability. Software control can configure $P_{24}$ as Output Buffer Full (OBF) interrupt, $P_{25}$ as Input Buffer Full ( $\overline{\rm IBF}$ ) interrupt, $P_{26}$ as DMA Request (DRQ), and $P_{27}$ as DMA ACKnowledge ( $\overline{\rm DACR}$ ). |

| PROG                                    | 25                | 1/0  | PROGRAM: Multifunction pin used as the program pulse input during PROM programming.  During I/O expander access the PROG pin acts as an address/data strobe to the 8243.  This pin should be tied high if unused.                                                                                                                                                                                                                                                                                                                                                             |

| Vcc                                     | 40                |      | POWER: +5V main power supply pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>DD</sub>                         | 26                |      | <b>POWER:</b> +5V during normal operation. +21V during programming operation. Low power standby supply pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>SS</sub>                         | 20                |      | GROUND: Circuit ground potential.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# intel<sub>®</sub>

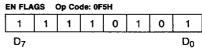

## **UPI-42 FEATURES**

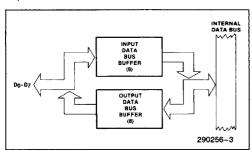

Two Data Bus Buffers, one for input and one for output. This allows a much cleaner Master/Slave protocol.

2. 8 Bits of Status

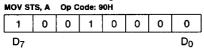

ST<sub>4</sub>-ST<sub>7</sub> are user definable status bits. These bits are defined by the "MOV STS, A" single byte, single cycle instruction. Bits 4-7 of the acccumulator are moved to bits 4-7 of the status register. Bits 0-3 of the status register are not affected.

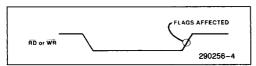

RD and WR are edge triggered. IBF, OBF, F<sub>1</sub> and INT change internally after the trailing edge of RD or WR.

During the time that the host CPU is reading the status register, the 8742 is prevented from updating this register or is "locked out".

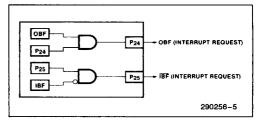

4. P<sub>24</sub> and P<sub>25</sub> are port pins or Buffer Flag pins which can be used to interrupt a master processor. These pins default to port pins on Reset.

If the "EN FLAGS" instruction has been executed,  $P_{24}$  becomes the OBF (Output Buffer Full) pin. A "1" written to  $P_{24}$  enables the OBF pin (the pin outputs the OBF Status Bit). A "0" written to  $P_{24}$  disables the OBF pin (the pin remains low). This pin can be used to indicate that valid data is available from the UPI-41A (in Output Data Bus Buffer).

If "EN FLAGS" has been executed,  $P_{25}$  becomes the  $\overline{\rm IBF}$  (Input Buffer Full) pin. A "1" written to  $P_{25}$  enables the  $\overline{\rm IBF}$  pin (the pin outputs the inverse of

the IBF Status Bit. A "0" written to  $P_{25}$  disables the  $\overline{\rm IBF}$  pin (the pin remains low). This pin can be used to indicate that the UPI is ready for data.

**Data Bus Buffer Interrupt Capability**

P<sub>26</sub> and P<sub>27</sub> are port pins or DMA handshake pins for use with a DMA controller. These pins default to port pins on Reset.

If the "EN DMA" instruction has been executed, P<sub>26</sub> becomes the DRQ (DMA Request) pin. A "1" written to P<sub>26</sub> causes a DMA request (DRQ is activated). DRQ is deactivated by DACK•RD, DACK•WR, or execution of the "EN DMA" instruction.

If "EN DMA" has been executed,  $P_{27}$  becomes the  $\overline{DACK}$  (DMA Acknowledge) pin. This pin acts as a chip select input for the Data Bus Buffer registers during DMA transfers.

**DMA Handshake Capability**

- The RESET input on the 8742, includes a 2-stage synchronizer to support reliable reset operation for 12 MHz operation.

- 7. When EA is enabled on the 8742, the program counter is placed on Port 1 and the lower three bits of Port 2 (MSB = P<sub>22</sub>, LSB = P<sub>10</sub>). On the 8742 this information is multiplexed with PORT DATA (see port timing diagrams at end of this data sheet).

# **APPLICATIONS**

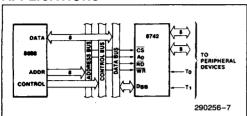

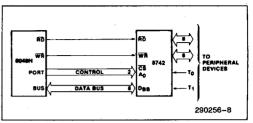

Figure 3, 8088-8742 Interface

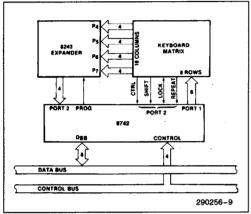

Figure 5. 8742-8243 Keyboard Scanner

Figure 4. 8048H-8742 Interface

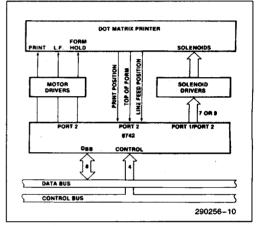

Figure 6. 8742 80-Column Matrix Printer Interface

# PROGRAMMING, VERIFYING, AND ERASING THE 8742 EPROM

# **Programming Verification**

In brief, the programming process consists of: activating the program mode, applying an address, latching the address, applying data, and applying a programming pulse. Each word is programmed completely before moving on to the next and is followed by a verification step. The following is a list of the pins used for programming and a description of their functions:

| Pin                | Function                                            |

|--------------------|-----------------------------------------------------|

| XTAL 1             | Clock-Input                                         |

| Reset              | Initialization and Address Latching                 |

| Test 0             | Selection of Program or Verify Mode                 |

| EA                 | Activation of Program/Verify Modes                  |

| BUS                | Address and Data Input<br>Data Output During Verify |

| P <sub>20-12</sub> | Address Input                                       |

| V <sub>DD</sub>    | Programming Power Supply                            |

| PROG               | Program Pulse Input                                 |

#### WARNING

An attempt to program a missocketed 8742 will result in severe damage to the part. An indication of a properly socketed part is the appearance of the SYNC clock output. The lack of this clock may be used to disable the programmer.

# The Program/Verify sequence is:

- A<sub>0</sub> = 0V, CS = 5V, EA = 5V, RESET = 0V, TESTO = 5V, V<sub>DD</sub> = 5V, clock applied or internal oscillator operating, BUS floating, PROG = 5V.

- 2. Insert 8742 in programming socket

- 3. TEST 0 = 0V (select program mode)

- 4. EA = 18V (active program mode)

- 5. Address applied to BUS and P<sub>20-22</sub>

- 6. RESET = 5V (latch address)

- 7. Data applied to BUS\*\*

- 8.  $V_{DD} = 21V$  (programming power)

- 9. PROG = V<sub>CC</sub> followed by one 50 ms pulse to 18V

- 10.  $V_{DD} = 5V$

- 11.TEST 0 = 5V (verify mode)

- 12. Read and verify data on BUS

- 13. TEST 0 = 0V

- 14. RESET = 0V and repeat from step 5

- 15. Programmer should be at conditions of step 1 when 8742 is removed from socket

## 8742 Erasure Characteristics

The erasure characteristics of the 8742 are such that erasure begins to occur when exposed to light with wavelengths shorter than approximately 4000 Angstroms (Å). It should be noted that sunlight and certain types of fluorescent lamps have wavelengths in the 3000-4000Å range. Data shows that constant exposure to room level fluorescent lighting could erase the typical 8742 in approximately 3 years while it would take approximately one week to cause erasure when exposed to direct sunlight. If the 8742 is to be exposed to these types of lighting conditions for extended periods of time, opaque labels are available from Intel which should be placed over the 8742 window to prevent unintentional erasure.

The recommended erasure procedure for the 8742 is exposure to shortwave ultraviolet light which has a wavelength of 2537Å. The integrated dose (i.e., UV intensity  $\times$  exposure time) for erasure should be a minimum of 15 w-sec/cm². The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with a 12,000  $\mu \text{W/cm²}$  power rating. The 8742 should be placed within one inch of the lamp tubes during erasure. Some lamps have a filter on their tubes which should be removed before erasure.

# **ABSOLUTE MAXIMUM RATINGS\***

| Ambient Temperature Under Bias0°C to 70°C |

|-------------------------------------------|

| Storage Temperature65°C to +150°C         |

| Voltage on Any Pin With Respect           |

| to Ground                                 |

| Power Dissipation                         |

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

# **D.C. CHARACTERISTICS** $T_A = 0^{\circ}$ to $+70^{\circ}$ C, $V_{CC} = V_{DD} = +5V \pm 10^{\circ}$

| Symbol                | Parameter                                                                                       | 87   | 42              | Units | Test                                                        |  |

|-----------------------|-------------------------------------------------------------------------------------------------|------|-----------------|-------|-------------------------------------------------------------|--|

| - Cymbol              | 7 diameter                                                                                      | Min  | Max             | Ointa | Conditions                                                  |  |

| V <sub>IL</sub>       | input Low Voltage (Except XTAL1, XTAL2, RESET)                                                  | -0.5 | 0.8             | ٧     |                                                             |  |

| V <sub>IL1</sub>      | Input Low Voltage (XTAL1, XTAL2, RESET)                                                         | -0.5 | 0.6             | V     |                                                             |  |

| V <sub>IH</sub>       | Input High Voltage (Except XTAL1, XTAL2, RESET)                                                 | 2.0  | V <sub>CC</sub> | ٧     |                                                             |  |

| V <sub>IH1</sub>      | Input High Voltage (XTLA1, XTAL2, RESET)                                                        | 3.5  | V <sub>CC</sub> | ٧     |                                                             |  |

| V <sub>OL</sub>       | Output Low Voltage (D <sub>0</sub> -D <sub>7</sub> )                                            |      | 0.45            | ٧     | I <sub>OL</sub> = 2.0 mA                                    |  |

| V <sub>OL1</sub>      | Output Low Voltage (P <sub>10</sub> -P <sub>17</sub> , P <sub>20</sub> -P <sub>27</sub> , Sync) |      | 0.45            | ٧     | $I_{OL} = 1.6  \text{mA}$                                   |  |

| V <sub>OL2</sub>      | Output Low Voltage (PROG)                                                                       |      | 0.45            | ٧     | $I_{OL} = 1.0 \text{ mA}$                                   |  |

| V <sub>OH</sub>       | Output High Voltage (D <sub>0</sub> -D <sub>7</sub> )                                           | 2.4  |                 | >     | $I_{OH} = -400 \mu A$                                       |  |

| V <sub>OH1</sub>      | Output High Voltage (All Other Outupts)                                                         | 2.4  |                 |       | $I_{OH} = -50 \mu\text{A}$                                  |  |

| կլ                    | Input Leakage Current (T <sub>0</sub> , T <sub>1</sub> , RD, WR, CS, A <sub>0</sub> , EA)       |      | ±10             | μΑ    | $V_{SS} \le V_{IN} \le V_{CC}$                              |  |

| I <sub>OFL</sub>      | Output Leakage Current (D <sub>0</sub> -D <sub>7</sub> , High Z State)                          |      | ±10             | μΑ    | V <sub>SS</sub> +0.45<br>≤V <sub>OUT</sub> ≤V <sub>CC</sub> |  |

| I <sub>LI</sub>       | Low Input Load Current (P <sub>10</sub> -P <sub>17</sub> , P <sub>20</sub> -P <sub>27</sub> )   |      | 0.3             | mA    | $V_{IL} = 0.8V$                                             |  |

| I <sub>LI1</sub>      | Low Input Load Current (RESET, SS)                                                              |      | 0.2             | mA    | $V_{IL} = 0.8V$                                             |  |

| I <sub>DD</sub>       | V <sub>DD</sub> Supply Current                                                                  |      | 10              | mA    | Typical = 5 mA                                              |  |

| Icc + I <sub>DD</sub> | Total Supply Current                                                                            |      | 125             | mA    | Typical = 60 mA                                             |  |

| l <sub>H</sub>        | Input Leakage Current (P <sub>10</sub> -P <sub>17</sub> , P <sub>20</sub> -P <sub>27</sub> )    |      | 100             | μΑ    | $V_{IN} = V_{CC}$                                           |  |

| C <sub>IN</sub>       | Input Capacitance                                                                               |      | 10              | pF    |                                                             |  |

| C <sub>1 0</sub>      | I/O Capacitance                                                                                 |      | 20              | рF    |                                                             |  |

# D.C. CHARACTERISTICS—PROGRAMMING

$T_A$  = 25°C ±5°C,  $V_{CC}$  = 5V ±5%,  $V_{DD}$  = 21V ±0.5V

| Symbol            | Parameter                                   | Min                  | Max  | Units | Test Conditions |

|-------------------|---------------------------------------------|----------------------|------|-------|-----------------|

| V <sub>DOH</sub>  | V <sub>DD</sub> Program Voltage High Level  | 20.5                 | 21.5 | V     |                 |

| V <sub>DDL</sub>  | V <sub>DD</sub> Voltage Low Level           | 4.75                 | 5.25 | V     |                 |

| V <sub>PH</sub>   | PROG Program Voltage High Level             | 17.5                 | 18.5 | V     |                 |

| V <sub>PL</sub>   | PROG Voltage Low Level                      | V <sub>CC</sub> -0.5 | Vcc  | ٧     |                 |

| VEAH              | EA Program or Verify Voltage High Level     | 17.5                 | 18.5 | ٧     |                 |

| VEAL              | EA Voltage Low Level                        |                      | 5.25 | V     |                 |

| I <sub>DD</sub>   | V <sub>DD</sub> High Voltage Supply Current |                      | 30.0 | mA    |                 |

| l <sub>PROG</sub> | PROG High Voltage Supply Current            |                      | 1.0  | mA.   | :               |

| <sup>I</sup> EA   | EA High Voltage Supply Current              |                      | 1.0  | mA    |                 |

4-106

**4826175 0161417 263**

<sup>\*</sup>WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

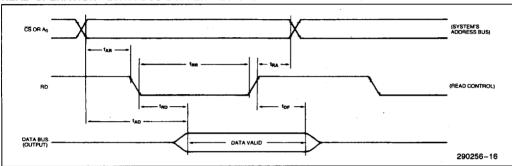

# **A.C. CHARACTERISTICS** $T_A = 0^{\circ}C$ to $+70^{\circ}C$ , $V_{SS} = 0V$ , $V_{CC} = V_{DD} = +5V \pm 10\%$ DBB READ

| Symbol          | Parameter                            | 87   | Units |                   |

|-----------------|--------------------------------------|------|-------|-------------------|

| Symbol          | Farameter                            | Min  | Max   | ]                 |

| t <sub>AR</sub> | CS, A <sub>0</sub> Setup to RD ↓     | 0    |       | ns                |

| t <sub>RA</sub> | CS, A <sub>0</sub> Hold after RD ↑   | 0 .  |       | กร                |

| t <sub>RR</sub> | RD Pulse Width                       | 160  |       | ns                |

| t <sub>AD</sub> | CS, A <sub>0</sub> to Data Out Delay |      | 130   | ns                |

| t <sub>RD</sub> | RD ↓ to Data Out Delay               |      | 130   | ns                |

| t <sub>DF</sub> | RD↑ to Data Float Delay              |      | 85    | ns                |

| tcy             | Cycle Time                           | 1.25 | 15    | μs <sup>(1)</sup> |

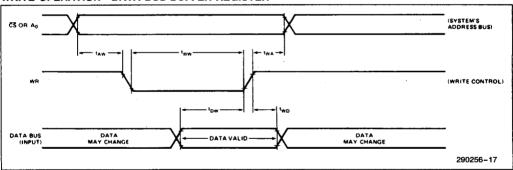

## **DBB WRITE**

| Symbol | Parameter                          | Min | Max | Units |

|--------|------------------------------------|-----|-----|-------|

| taw    | CS, A <sub>0</sub> Setup to WR ↓   | 0   |     | ns    |

| twa    | CS, A <sub>0</sub> Hold after WR ↑ | 0   |     | ns    |

| tww    | WR Pulse Width                     | 160 |     | ns    |

| tpw    | Data Setup to WR↑                  | 130 |     | ns    |

| twp    | Data Hold after WR ↑               | 0   |     | ns    |

#### NOTE:

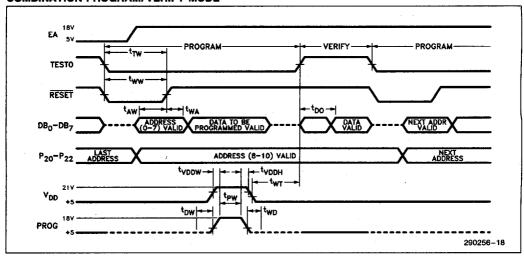

# A.C. CHARACTERISTICS $T_A = 25^{\circ}C \pm 5^{\circ}C$ , $V_{CC} = 5V \pm 5\%$ , $V_{DD} = +21V \pm 0.5$ PROGRAMMING

| Symbol                          | Parameter                                    | Min              | Max              | Units | Test Conditions |

|---------------------------------|----------------------------------------------|------------------|------------------|-------|-----------------|

| t <sub>AW</sub>                 | Address Setup Time to RESET ↑                | 4t <sub>CY</sub> |                  |       |                 |

| t <sub>WA</sub>                 | Address Hold Time after RESET ↑              | 4t <sub>CY</sub> |                  |       |                 |

| t <sub>DW</sub>                 | Data in Setup Time to PROG ↑                 | 4t <sub>CY</sub> |                  |       |                 |

| t <sub>WD</sub>                 | Data in Hold Time after PROG ↓               | 4t <sub>CY</sub> |                  |       |                 |

| tpH                             | RESET Hold Time to Verify                    | 4t <sub>CY</sub> |                  |       |                 |

| tvddw                           | V <sub>DD</sub> Setup Time to PROG ↑         | 0                | 1.0              | mS    |                 |

| tvddh                           | V <sub>DD</sub> Hold Time after PROG ↑       | 0                | 1.0              | mS    |                 |

| tpw                             | Program Pulse Width                          | 50               | 60               | mS    |                 |

| t <sub>TW</sub>                 | Test 0 Setup Time for Program Mode           | 4t <sub>CY</sub> |                  |       |                 |

| twr                             | Test 0 Hold Time after Program Mode          | 4t <sub>CY</sub> |                  |       |                 |

| t <sub>DO</sub>                 | Test 0 to Data Out Delay                     |                  | 4t <sub>CY</sub> |       |                 |

| tww                             | RESET Pulse Width to Latch Address           | 4t <sub>CY</sub> |                  |       |                 |

| t <sub>r</sub> , t <sub>f</sub> | V <sub>DD</sub> and PROG Rise and Fall Times | 0.5              | 2.0              | μs    | ,               |

| tcy                             | CPU Operation Cycle Time                     | 4.0              |                  | μs    |                 |

| t <sub>RE</sub>                 | RESET Setup Time before EA ↑                 | 4t <sub>CY</sub> |                  |       |                 |

#### NOTE:

If TEST 0 is high, t<sub>DO</sub> can be triggered by RESET ↑.

■ 4826175 O161418 1TT ■

4-107

<sup>1.</sup>  $T_{CY} = 15/f(XTAL)$

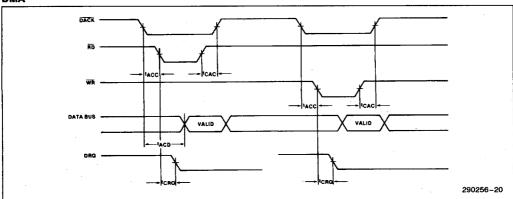

# A.C. CHARACTERISTICS DMA

| Symbol           | Parameter                | 8642 | Units |                   |

|------------------|--------------------------|------|-------|-------------------|

| Symbol           | Faranieter               | Min  | Max   | Oints             |

| tACC             | DACK to WR or RD         | 0    |       | ns                |

| tcac             | RD or WR to DACK         | 0    |       | ns                |

| t <sub>ACD</sub> | DACK to Data Valid       |      | 130   | ns                |

| t <sub>CRQ</sub> | RD or WR to L/RQ Cleared |      | 100   | ns <sup>(1)</sup> |

#### NOTE:

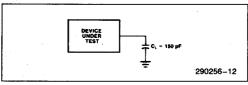

1.  $C_L = 150 pF$ .

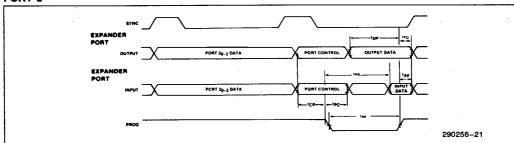

# A.C. CHARACTERISTICS PORT 2 $T_A = 0$ °C to +70°C, $V_{CC} = +5V \pm 10\%$

| Symbol          | Parameter                                      | f(t <sub>CY</sub> )      | 8742/8642 <sup>(3)</sup> |     | Units             |

|-----------------|------------------------------------------------|--------------------------|--------------------------|-----|-------------------|

| Cymbol          | r di dilitati                                  | 1(464)                   | Min                      | Max | Oilles            |

| tCP             | Port Control Setup before Falling Edge of PROG | 1/15 t <sub>CY</sub> -28 | 55                       |     | ns <sup>(1)</sup> |

| t <sub>PC</sub> | Port Control Hold after Falling Edge of PROG   | 1/10 t <sub>CY</sub>     | 125                      |     | ns(2)             |

| tPR             | PROG to Time P2 Input Must Be Valid            | 8/15 t <sub>CY</sub> -16 |                          | 650 | ns(1)             |

| tpF             | Input Data Hold Time                           |                          | 0                        | 150 | ns(2)             |

| t <sub>DP</sub> | Output Data Setup Time                         | 2/10 t <sub>CY</sub>     | 250                      |     | ns(1)             |

| t <sub>PD</sub> | Output Data Hold Time                          | 1/10 t <sub>CY</sub> -80 | 45                       |     | ns(2)             |

| tpp             | PROG Pulse Width                               | 6/10 t <sub>CY</sub>     | 750                      |     | ns                |

#### NOTES:

1.  $C_L = 80 \text{ pF.}$ 2.  $C_L = 20 \text{ pF.}$

3.  $t_{CY} = 1.25 \mu s$ .

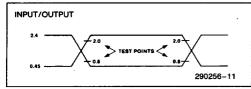

## A.C. TESTING INPUT/OUTPUT WAVEFORM

## A.C. TESTING LOAD CIRCUIT

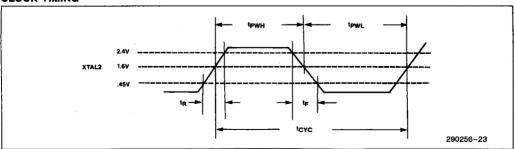

## **CRYSTAL OSCILLATOR MODE**

# **DRIVING FROM EXTERNAL SOURCE**

Rise and Fall Times Should Not Exceed 20 ns. Resistors to  $V_{CC}$  are Needed to Ensure  $V_{IH} = 3.5V$  if TTL Circuitry is Used.

4-108

**■** 4826175 0161419 036 **■**

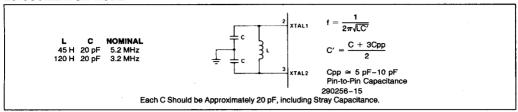

# LC OSCILLATOR MODE

# **WAVEFORMS**

# READ OPERATION-DATA BUS BUFFER REGISTER

#### WRITE OPERATION—DATA BUS BUFFER REGISTER

# **CLOCK TIMING**

4-109

4826175 O16142O 858 **E**

# **WAVEFORMS**

# **COMBINATION PROGRAM/VERIFY MODE**

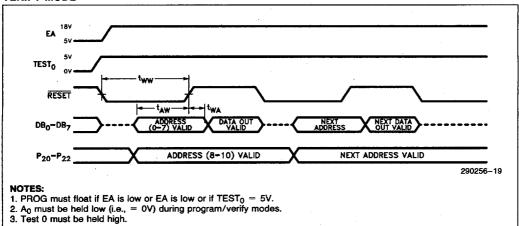

#### **VERIFY MODE**

The 8742 EPROM can be programmed by the following Intel products:

- Universal PROM Programmer (UPP 103) peripheral of the Intellec Development System with a UPP-549 Personality Card.

- 2. iUP-200/iUP-201 PROM Programmer with the iUP-F87/44 Personality Module.

# intel.

# **WAVEFORMS** (Continued)

# DMA

# PORT 2

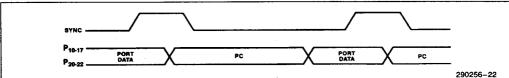

# PORT TIMING DURING EXTERNAL ACCESS (EA)

On the Rising Edge of SYNC and EA is Enabled, Port Data is Valid and can be Strobed on the Trailing Edge of Sync the Program Counter Contents are Available.

4-111