# 3.3V SYNC DRAM PLL Clock Driver

## FEATURES/BENEFITS

- 11 outputs

- Balanced Drive Outputs ±12mA

- Synchronous sleep mode disable (sOE) option

- · External feedback, internal loop filter

- · Low skew guaranteed between outputs

- Supports 33MHz to 125MHz SDRAMs

- JEDEC Compatible LVTTL

- 3.0V to 3.6V supply voltage

- · Industrial temperature range

- · Inputs are 5V tolerant

- · Available in 24-pin QSOP, TSSOP package

## **DESCRIPTION**

The QS5920 is a high-performance, low skew, low jitter, multiple output phase locked loop clock driver. It provides precise phase and frequency alignment of its clock outputs to an externally applied clock input signal. The QS5920 has been specially designed to interface with high speed SDRAM applications in the range of 33MHz to 125MHz and includes an internal RC filter which provides excellent jitter characteristics and eliminates the need for external components. The synchronous output enable ( $\overline{\text{sOE}}$ ) control sets all outputs except QFB (which may be used to maintain phase lock) LOW on a subsequent negative clock transition: partial output clock pulses are not produced.

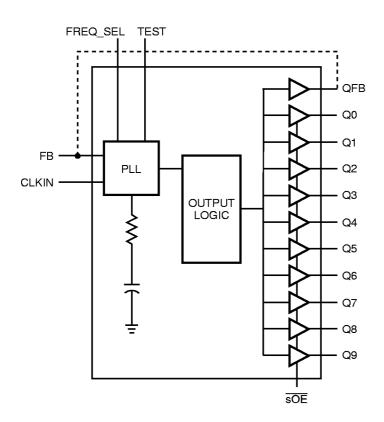

Figure 1. Logic Block Diagram and Pinout

**Table 1. Pin Description**

| Pin Name                | I/O | Functional Description                                                                                                                               |

|-------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKIN                   | I   | Clock input                                                                                                                                          |

| Q0Q9                    | 0   | Clock outputs                                                                                                                                        |

| FB                      | _   | PLL feedback input normally connected to QFB by user. May be connected to any output if $\overline{sOE}$ is strapped low.                            |

| QFB                     | 0   | Dedicated clock output for the FB pin (non-disable)                                                                                                  |

| sOE                     | 1   | Synchronous output enable. Asserted LOW for normal operation. When asserted HIGH, clock outputs (except QFB) are forced LOW.                         |

| TEST                    | -   | When LOW, PLL is in normal operation. When HIGH, it disables PLL and opens DC bypass. CLKIN goes to all outputs.                                     |

| FREQ_SEL <sup>(1)</sup> | Ι   | VCO frequency select. For optimising the VCO operating frequency. Set LOW for input frequencies within 33MHz to 75MHz, and HIGH for 76MHz to 125MHz. |

| V <sub>CC</sub>         | _   | Power supply for output buffers                                                                                                                      |

| V <sub>CCQ</sub>        |     | Power supply (quiet) for PLL                                                                                                                         |

| GND                     | _   | Ground supply for output buffers                                                                                                                     |

| GNDQ                    |     | Ground supply (quiet) for PLL                                                                                                                        |

#### Note:

# **Table 2. Absolute Maximum Ratings**

| Supply Voltage to Ground                           | 0.5V to +7.0V            |

|----------------------------------------------------|--------------------------|

| DC Output Voltage V <sub>OUT</sub>                 | $-0.5V$ to $V_{CC}+0.5V$ |

| DC Input Voltage V <sub>IN</sub>                   | –0.5V to +7.0V           |

| DC Input Diode Current with V <sub>I</sub> < 0     | –20mA                    |

| Maximum Power Dissipation At $T_A = 85^{\circ}C$ , |                          |

| T <sub>STG</sub> Storage Temperature               |                          |

Note: Stresses greater than those listed under absolute maximum ratings may cause permanent damage to QSI devices that result in functional or reliability type failures.

# Table 3. Capacitance

$T_A = 25^{\circ}C$ , f = 1MHz,  $V_{IN} = 0V$

|                 | QS  | ОР  | TSS | Units   |    |

|-----------------|-----|-----|-----|---------|----|

|                 | Тур | Max | Тур | Тур Мах |    |

| C <sub>IN</sub> | 5   | 7   | 5   | 7       | pF |

Note: Capacitance is characterized but not tested.

**Table 4. Recommended Operating Conditions**

| Symbol         | Parameter                     | Min | Max      | Unit |

|----------------|-------------------------------|-----|----------|------|

| $V_{CC}$       | Power Supply Voltage          | 3.0 | 3.6      | ٧    |

| $V_{IN}$       | Input Voltage                 | 0   | $V_{CC}$ | ٧    |

| T <sub>A</sub> | Ambient Operating Temperature | -40 | 85       | °C   |

<sup>1.</sup> If this input is switched, the function and timing of the outputs may glitch, and the PLL may require an additional  $t_{LOCK}$  time before all datasheet limits are achieved. When this pin is selected HIGH, the CLKIN input must not transition until  $V_{CC}$  has reached 2.8V.

**Table 5. DC Electrical Characteristics Over Operating Range**

| Symbol          | Parameter                          | Test Condition                                                                                                 | Min               | Typ <sup>(1)</sup> | Max               | Unit |

|-----------------|------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------|--------------------|-------------------|------|

| V <sub>IH</sub> | Input HIGH Voltage                 | Guaranteed Logic HIGH for inputs                                                                               | 2.0               |                    |                   | ٧    |

| $V_{IL}$        | Input LOW Voltage                  | Guaranteed Logic LOW for inputs                                                                                |                   |                    | 8.0               | ٧    |

| V <sub>IC</sub> | Clamp Diode Voltage                | $V_{CC} = Min., I_{IN} = -18mA$                                                                                |                   | -0.7               | -1.2              | ٧    |

| V <sub>OH</sub> | Output HIGH Voltage<br>(Q0:9, QFB) | $V_{CC} = Min., I_{OH} = -12mA$<br>$V_{CC} = Min., I_{OH} = -8mA$<br>$V_{CC} = Min., I_{OH} = -100\mu A$       | 2.0<br>2.4<br>2.8 |                    |                   | ٧    |

| V <sub>OL</sub> | Output LOW Voltage<br>(Q0:9, QFB)  | $V_{CC}$ = Min., $I_{OL}$ = 12mA<br>$V_{CC}$ = Min., $I_{OL}$ = 8mA<br>$V_{CC}$ = Min., $I_{OL}$ = 100 $\mu$ A |                   |                    | 0.5<br>0.4<br>0.2 | ٧    |

| I <sub>IN</sub> | Input Leakage Current              | $V_{CC} = Max., 0 \le V_{IN} \le V_{CC}$                                                                       |                   |                    | 1                 | μА   |

## Note:

## **Table 6. Power Supply Characteristics**

| Symbol           | Parameter                                  | Test Conditions                                                                        | Тур | Max | Unit                |

|------------------|--------------------------------------------|----------------------------------------------------------------------------------------|-----|-----|---------------------|

| I <sub>CCQ</sub> | Quiescent Power<br>Supply Current          | $V_{CC}$ = Max., TEST = High, CLKIN = Low $\overline{SOE}$ = Low, All outputs unloaded | 10  | 20  | mA                  |

| $\Delta I_{CC}$  | Power Supply Current<br>Per Input HIGH(1)  | $V_{CC} = Max., V_{IN} = 3.0V$                                                         | 1.0 | 30  | μА                  |

| I <sub>CCD</sub> | Dynamic Power Supply Current Per Output(1) | $V_{CC} = Max., C_L = 0pF$                                                             | 55  | 90  | μ <b>A</b> /<br>MHz |

| I <sub>C</sub>   | Total Power Supply Current(1)              | $V_{CC} = 3.3V, f_{CLKIN} = 50MHz, C_L = 165pF^{(2)}$                                  | 70  |     | mA                  |

| I <sub>C</sub>   | Total Power Supply Current(1)              | $V_{CC} = 3.3V, f_{CLKIN} = 100MHz, C_L = 165pF^{(2)}$                                 | 130 |     | mA                  |

#### Notes:

- 1. Guaranteed by characterization but not production tested.

- 2. For 11 outputs each loaded with 15pF.

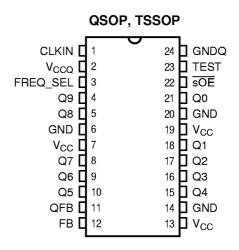

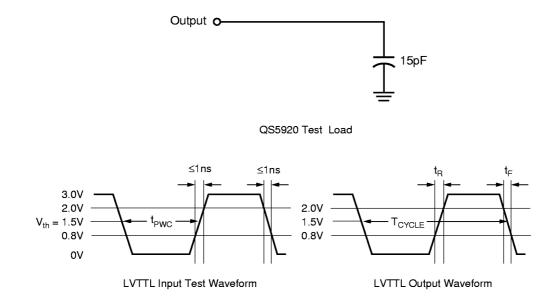

**Table 7. Switching Characteristics Over Operating Range**

| Symbol             | Description                                                    | Min                         | Max                         | Unit |

|--------------------|----------------------------------------------------------------|-----------------------------|-----------------------------|------|

| t <sub>PWC</sub>   | Input clock pulse, high or low(1)                              | 2.5                         | _                           | ns   |

| f <sub>CLKIN</sub> | Input frequency                                                | 33                          | 125                         | MHz  |

| t <sub>PD</sub>    | CLKIN input to FB delay(1,2)                                   | -500                        | +500                        | ps   |

| t <sub>SK1</sub>   | Output - Output skew, all outputs, same transition(1,2)        | _                           | 250                         | ps   |

| t <sub>J</sub>     | Cycle to cycle jitter, 65MHz <sup>(1,2)</sup>                  | -100                        | +100                        | ps   |

| t <sub>PW</sub>    | Output duty cycle distortion(1,2,3)                            | 45                          | 55                          | %    |

| t <sub>OPW</sub>   | Output pulse width distortion(1,2,3)                           | T <sub>CYCLE</sub> /2 -0.65 | T <sub>CYCLE</sub> /2 +0.65 | ns   |

| t <sub>LOCK</sub>  | CLKIN to phase lock                                            | 0.1                         | 0.5                         | ms   |

| $t_R, t_F$         | Output rise and fall times (0.8V to 2.0V) <sup>(1,2)</sup>     | _                           | 1.2                         | ns   |

| t <sub>DEV</sub>   | Skew between two outputs of different devices <sup>(1,4)</sup> | _                           | 1.25                        | ns   |

#### Notes:

- 1. This parameter is guaranteed by design and verified during production by statistical correlation.

- 2. Output Loading:  $C_L = 15pF$ .

- 3. Output signal is nominally 50% duty cycle: maximum error is  $\pm 5\%$  of the period or 0.65ns, whichever is the greater.

- 4. t<sub>DEV</sub> applies to any device operating under the same conditions (V<sub>CC</sub>, ambient temperature, package, air flow, etc.)

<sup>1.</sup> Typical values indicate  $V_{CC} = 3.3V$  and  $T_A = 25^{\circ}C$ .

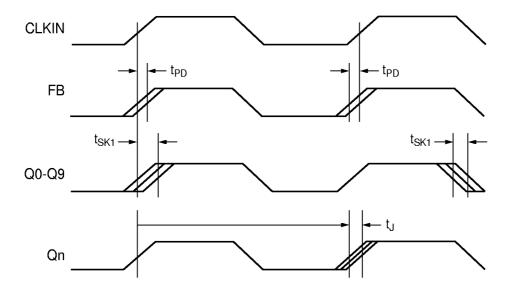

Figure 3. AC Test Loads and Waveforms

Figure 4. AC Timing Diagram

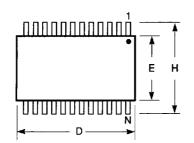

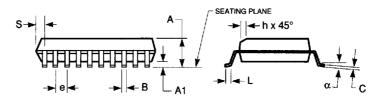

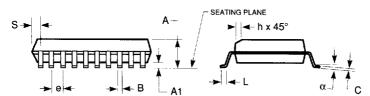

## 150-MIL QSOP - Package Code Q

Quarter-Size Outline Package Plastic Small Outline Gull-Wing

#### Notes:

- 1. Refer to applicable symbol list.

- 2. All dimensions are in inches.

- 3. N is the number of lead positions.

- Dimensions D and E are to be measured at maximum material condition but do not include mold flash. Allowable mold flash is 0.006in. per side.

- Lead coplanarity is 0.004in. maximum.

| JEDEC# | MO-137AB |        |       | MO-137AD  |       | MO-137AE  |       |           | MO-137AF |       |       |       |

|--------|----------|--------|-------|-----------|-------|-----------|-------|-----------|----------|-------|-------|-------|

| DWG#   | PSS-16A  |        |       | PSS-20A   |       | PSS-24A   |       |           | PSS-28A  |       |       |       |

| Symbol | Min      | Nom    | Max   | Min       | Nom   | Max       | Min   | Nom       | Max      | Min   | Nom   | Max   |

| Α      | 0.060    | 0.064  | 0.068 | 0.060     | 0.064 | 0.068     | 0.060 | 0.064     | 0.068    | 0.060 | 0.064 | 0.068 |

| A1     | 0.004    | 0.006  | 0.008 | 0.004     | 0.006 | 0.008     | 0.004 | 0.006     | 0.008    | 0.004 | 0.006 | 0.008 |

| В      | 0.009    | 0.010  | 0.012 | 0.009     | 0.010 | 0.012     | 0.009 | 0.010     | 0.012    | 0.009 | 0.010 | 0.012 |

| С      | 0.007    | 0.008  | 0.010 | 0.007     | 0.008 | 0.010     | 0.007 | 0.008     | 0.010    | 0.007 | 0.008 | 0.010 |

| D      | 0.189    | 0.193  | 0.197 | 0.337     | 0.341 | 0.344     | 0.337 | 0.341     | 0.344    | 0.386 | 0.390 | 0.394 |

| E      | 0.150    | 0.154  | 0.157 | 0.150     | 0.154 | 0.157     | 0.150 | 0.154     | 0.157    | 0.150 | 0.154 | 0.157 |

| е      | 0.       | 025 BS | С     | 0.025 BSC |       | 0.025 BSC |       | 0.025 BSC |          |       |       |       |

| н      | 0.230    | 0.236  | 0.244 | 0.230     | 0.236 | 0.244     | 0.230 | 0.236     | 0.244    | 0.230 | 0.236 | 0.244 |

| h      | 0.010    | 0.013  | 0.016 | 0.010     | 0.013 | 0.016     | 0.010 | 0.013     | 0.016    | 0.010 | 0.013 | 0.016 |

| L      | 0.016    | 0.025  | 0.035 | 0.016     | 0.025 | 0.035     | 0.016 | 0.025     | 0.035    | 0.016 | 0.025 | 0.035 |

| N      | 16       |        | 20    |           | 24    |           | 28    |           |          |       |       |       |

| α      | 0°       | 5°     | 8°    | 0°        | 5°    | 8°        | 0°    | 5°        | 8°       | 0°    | 5°    | 8°    |

| S      | 0.006    | 0.009  | 0.010 | 0.056     | 0.058 | 0.060     | 0.031 | 0.033     | 0.035    | 0.031 | 0.033 | 0.035 |

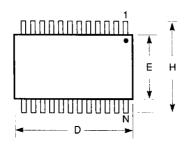

## 170-MIL TSSOP - Package Code PA

Thin Shrink Small Outline Package Plastic Small Outline Gull-Wing

#### Notes:

- 1. Refer to applicable symbol list.

- 2. N is the number of lead positions.

- Dimensions D and E are to be measured at maximum material condition but do not include mold flash. Allowable mold flash is 0.006in. per side.

- 4. Lead coplanarity is 0.004in. maximum.

| JEDEC# | М     | MO-153AD MO-153AD |       |      |         |      |  |  |  |

|--------|-------|-------------------|-------|------|---------|------|--|--|--|

| DWG#   | F     | PSS-240           |       | F    | PSS-240 | ;    |  |  |  |

| Symbol | Min   | Nom               | Max   | Min  | Nom     | Max  |  |  |  |

| Α      | 0.045 | 0.046             | 0.047 | 1.14 | 1.17    | 1.20 |  |  |  |

| A1     | 0.002 | 0.004             | 0.006 | 0.05 | 0.10    | 0.15 |  |  |  |

| b      | 0.007 | 0.010             | 0.012 | 0.19 | 0.25    | 0.30 |  |  |  |

| С      | 0.004 | 0.005             | 0.006 | 0.09 | 0.13    | 0.16 |  |  |  |

| D      | 0.303 | 0.307             | 0.311 | 7.7  | 7.8     | 7.9  |  |  |  |

| E      | 0.169 | 0.173             | 0.177 | 4.3  | 4.4     | 4.5  |  |  |  |

| е      | 0     | .025 BS           | С     | C    | .65 BS0 | )    |  |  |  |

| Н      | 0.238 | 0.252             | 0.269 | 6.1  | 6.4     | 6.7  |  |  |  |

| L      | 0.020 | 0.024             | 0.030 | 0.50 | 0.60    | 0.75 |  |  |  |

| N      |       | 24                |       |      | 24      |      |  |  |  |

| α      | 0°    | 5°                | 8°    | 0°   | 5°      | 8°   |  |  |  |

| S      | 0.007 | 0.008             | 0.009 | 0.18 | 0.2     | 0.22 |  |  |  |

IN INCHES

IN MILLIMETERS