T-42-31

# QuickChip™ 7 Integrated Circuit Array

# Tektronix

Test and Measurement

The QuickChip™7 Integrated Circuit Array combines an entirely new generation polysilicon wafer fabrication process with our Quick-Custom™ Design System to produce a powerful tool for analog or mixed analog/digital applications.

Our new process (GST-1), offers the following features:

- 2x density improvement over SHPi (QC6)

- Trench isolation (poly filled)

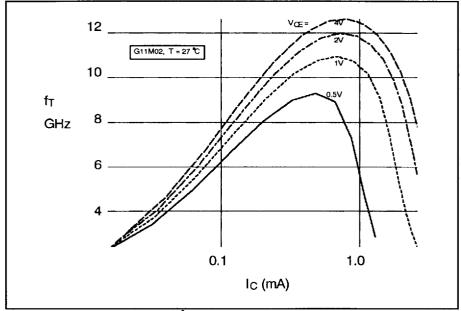

- f<sub>T</sub> > 12 GHz @ V<sub>CE</sub> = 4 V, NPN

- 200 Ω/ □ poly resistors

- 4 µm metal pitch, 2 lavers of Au

- Trimmable nichrome resistors (50 Ω/ □)

- Schottky diodes

- Low power (fr peak at 600 µA for G11M02)

QuickChip 7 is an uncommitted array of very high speed bipolar transistors, capacitors, resistors, and Schottky diodes that the analog circuit designer can quickly interconnect to meet

application requirements using the Tektronix QuickCustom Design Process. Typical applications include:

- RF amplifiers and mixers

- Sample and hold circuits

- High-speed comparators

- Voltage-controlled oscillators

- Prescalers

- High speed logic/interface functions

# **Process Description**

The QuickChip 7 IC is designed on a wafer fabrication process known as Giga-Speed Si-Bipolar Technology (GST-1). GST-1 is a selfaligned, double-polysilicon process. To isolate devices this process uses a deep trench that increases density and reduces parasitics. All devices except resistors are completely trench isolated. GST-1 has a thin base with a highly doped emitter which yields high speed with good DC parameters.

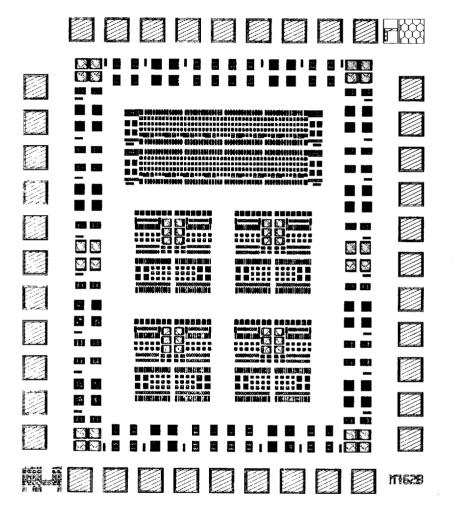

# **Chip Description**

The QuickChip 7 consists of an array that is 90 mils (2.28 mm) by 76 mils (1.93 mm). Since the GST-1 process is well suited for mixed analog/digital designs, the QuickChip 7 array is divided into a section that is optimized for analog design and a section that is optimized for digital (ECL) design. The analog section consists of 4 symmetrical macro-tiles, occupying the lower two-thirds of the central portion of the array. These 4 macro-tiles contain 208 NPN transistors, 56 PNP transistors, 32 Schottky

diodes, 24 capacitors and 848 resistors. The top third of the central portion of the array is occupied by the digital section, one large macro-tile, constructed from 8 full tiles (each sufficient to design a clocked master-slave data latch) and 4 half tiles. The digital area is designed for easy implementation of ECL logic with 200 mV to 600 mV internal logic swings. Collectively, this area contains 336 NPN transistors, 32 Schottky diodes, and 560 resistors. The periphery of the chip contains 48 large NPN transistors for I/O applications, 64 ESD diodes, and 24 [1.35 pF (max.)] capacitors. The complete array is surrounded by 40 bond pads.

### **Design Tools**

The QuickCustom approach leads smoothly through all the steps required to design an IC. The QuickChip 7 Design Guide provides the necessary information to use the process, enabling even the first-time user to complete a design with minimal one-onone coaching. The startup package includes 21/2 days of training at Tektronix which provides all the necessary design and process information plus training on our CAD tools. A library of SPICE models for the QuickChip transistors, resistors, capacitors, diodes, and bonding pads accurately predicts the speed and performance of the design. Models are available for -55 °C to 125 °C operation.

QuicKic™, a comprehensive design tool, is included with the QuickCustom start-up package. QuicKic provides schematic capture, netlist extraction, design rule checking, and a grid-based graphics editor to greatly simplify the design and layout process. Quickic can also be used to extract metal run parasitic capacitance and resistance.

| Device Type            | Name<br> | Analog<br><u>Area</u> | Digital<br>Area | Periphery<br>——— | Total |

|------------------------|----------|-----------------------|-----------------|------------------|-------|

| small NPN              | G11M02   | 0                     | 304             | 0                | 304   |

| small NPN              | G11M032  | 176                   | 16              | Ö                | 192   |

| medium NPN             | G12U05   | 32                    | 16              | Ō                | 48    |

| large NPN              | G14V102  | 0                     | 0               | 48               | 48    |

| PNP                    | PLAT     | 56                    | О               | 0                | 56    |

| Schottky diode         | DSU2     | 32                    | 32              | 0                | 64    |

| ESD diode              | DESD7    | 0                     | 0               | 64               | 64    |

| 2 kΩ resistor          | RY2KA    | 400                   | 0               | 0                | 400   |

| 2 kΩ resistor          | RY2KD    | 0                     | 464             | 0                | 464   |

| 400 $\Omega$ resistor  | RY400    | 448                   | 96              | 0                | 544   |

| MOS capacitor          | CMOS     | 24                    | 0               | 0                | 24    |

| MOS/junction capacitor | CSW      | 0                     | 0               | 24               | 24    |

| pad                    | PAD      | 0                     | 0               | 0                | 40    |

The QuickChip 7 IC Devices

f<sub>T</sub> vs. I<sub>C</sub> (G11M02), T = 27 °C

#### QuickChip™Terminology:

Tile -- an area on the array which contains various unconnected devices in a basic layout pattern. [On QuickChip 7, a full tile is  $176~\mu m$  x  $176~\mu m$ .]

**Macro-tile** -- a grouping of tiles, half tiles, and/or quarter tiles. QuickChip 7 contains a digital macro-tile and four analog macro-tiles.

Array -- a fixed configuration of macro-tiles and/or tiles, with added perimeter devices, placed in a way that is optimum for construction of integrated circuits.

| A recent addition to QuicKic     |

|----------------------------------|

| permits real-time verification   |

| between the netlist and layout.  |

| QuicKic reads the netlist and    |

| permits only the correct com-    |

| bination of devices to be inter- |

| connected on the layout. The     |

| combination of real-time         |

| Design Rule Checking and         |

| Verification has greatly in-     |

| creased the productivity of the  |

| designer and reduced develop-    |

| ment time and cost.              |

|                                  |

The startup package also includes QuERC™, a proprietary electrical rules checker which examines the DC bias conditions as provided by the circuit simulator. Using a data base of process and device limitations, QuERC identifies design problems early in the development process.

After receipt of the completed layout, Tektronix performs an extensive connectivity check between the SPICE netlist and QuicKic layout to confirm layout accuracy. Tektronix Microelectronics also performs a design rule check (DRC) to verify conformance to the layout rules.

# **Design Support**

A Product Engineer will be assigned to provide guidance through the QuickCustom design process, through prototype fabrication, and into production. Also available are Tektronix experienced designers to provide design consultation as required. (Up to eight hours of design consultation is included in the startup package.)

| <u>Parameter</u>                           | <u>Symbol</u>              | Measurement Conditions                                                                                                                   | <u>Min</u>     | <u>Max</u> | Un |

|--------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------|----|

| Collector-Base<br>Breakdown Voltage        | BV <sub>CBO</sub>          | lc=1 μA                                                                                                                                  | 12             |            | ٧  |

| Collector-Emitter<br>Punch-through Voltage | BV <sub>CES</sub>          | lc=1 μA                                                                                                                                  | 10             |            | ٧  |

| Collector-Emitter<br>Sustaining Voltage    | LV <sub>CEO</sub>          | I <sub>C</sub> =400 μA                                                                                                                   | 5              |            | ١  |

| Collector-Emitter<br>Breakdown Voltage     | BV <sub>CEO</sub>          | lc=1 μA                                                                                                                                  | 4              |            | ١  |

| Emitter-Base<br>Breakdown Voltage          | BV <sub>EBO</sub> *        | I <sub>E</sub> =1 μ <b>A</b>                                                                                                             | 4              |            | ٧  |

| Emitter-Collector<br>Punch-through Voltage | BV <sub>ECS</sub>          | I <sub>E</sub> =1 μA                                                                                                                     | 1.5            |            | ٧  |

| Collector-Substrate<br>Breakdown Voltage   | BVcs                       | l <sub>C</sub> =1 μA                                                                                                                     | 25             |            | ١  |

| Collector-Collector<br>Breakdown Voltage   | BVccs                      | l <sub>C</sub> =1 μA                                                                                                                     | 20             |            | ١  |

| Emitter-Base<br>Forward Voltage            | V <sub>BES</sub>           | l <sub>C</sub> =400 μA                                                                                                                   | 0.80           | 0.90       | ١  |

| Collector-Emitter<br>Saturation Voltage    | V <sub>CE</sub> (sat)      | I <sub>C</sub> =400 μA, I <sub>B</sub> =40 μA                                                                                            |                | 0.15       | ١  |

| Early Voltage                              | $V_{A}$                    | V <sub>BE</sub> =0.89V, V <sub>CE</sub> =2, 3V                                                                                           | 15             |            | ١  |

| DC Current Gain                            | βғ                         | V <sub>CB</sub> =2V, I <sub>C</sub> =40 μA<br>V <sub>CB</sub> =2V, I <sub>C</sub> =100 μA<br>V <sub>CB</sub> =2V, I <sub>C</sub> =400 μA | 40<br>40<br>40 |            |    |

| Collector-Emitter<br>Leakage Current       | ICEO                       | V <sub>CE</sub> =3V                                                                                                                      |                | 1          | r  |

| Emitter-Base<br>Leakage Current            | I <sub>EBO</sub>           | V <sub>EB</sub> =2.5V*                                                                                                                   |                | 50         | r  |

| Emitter Resistance                         | RE                         | l <sub>E</sub> =60, 90 μA                                                                                                                | 50             | 120        | 2  |

| Common Emitter<br>Unity Gain Frequency     | f <sub>T</sub>             | $V_{CE}$ =4 $V$ , $I_{C}$ =600 $\mu$ A                                                                                                   | 12             |            | GI |

| Voltage Mismatch                           | Δ V <sub>BE</sub><br>(3 σ) | i <sub>C</sub> = 1 mA                                                                                                                    |                | 2.5        | r  |

#### NPN Electrical Specifications (G11M02), T= 27 °C

| <u>Parameter</u> | Symbol         | Measurement Conditions | <u>Nom</u> | <u>Min</u> | <u>Max</u> | <u>Units</u> |

|------------------|----------------|------------------------|------------|------------|------------|--------------|

| Forward Diode    | VF             | I <sub>F</sub> = 75 μA | 375        |            |            | mV           |

| Voltage          |                | I <sub>F</sub> =750 μA | 458        | 300        | 550        | mV           |

| Reverse Diode    | l <sub>B</sub> | V <sub>R=</sub> 1 V    | 30         |            | 50         | пA           |

| Leakage Current  |                | V <sub>R</sub> = 3 V   | 100        |            | 200        | nΑ           |

Schottky Diode (DSU2) Electrical Specifications, T= 27 °C.

| <u>Parameter</u>                           | <u>Symbol</u>     | Measurement Conditions                           | <u>Min</u> | <u>Units</u> |

|--------------------------------------------|-------------------|--------------------------------------------------|------------|--------------|

| Collector-Emitter<br>Punch-through Voltage | BV <sub>CES</sub> | ic=1 μA                                          | 12         | ٧            |

| Emitter-Collector<br>Punch-through Voltage | BVECS             | l <sub>C</sub> =1 μA                             | 12         | ٧            |

| Collector-Base<br>Breakdown Voltage        | BV <sub>CBO</sub> | l <sub>C</sub> =1 μA                             | 12         | ٧            |

| Emitter-Base<br>Breakdown Voltage          | BV <sub>EBO</sub> | l <sub>C</sub> =1 μA                             | 12         | ٧            |

| Base-Substrate<br>Breakdown Voltage        | BV <sub>BS</sub>  | l <sub>C</sub> =1 μA                             | 25         | ٧            |

| Collector-Emitter<br>Sustaining Voltage    | LV <sub>CEO</sub> | l <sub>C</sub> =100 μA                           | 8          | ٧            |

| Early Voltage                              | VA                | V <sub>BE</sub> = -0.8 V, V <sub>CE</sub> = -3 V | 80         | ٧            |

| DC Current Gain                            | βг                | I <sub>C</sub> = 10 μA, V <sub>CB</sub> = -1 V   | 10         |              |

$I_{C}$ =200  $\mu A$ ,  $V_{CB}$ = -1 V $I_{C}$ =500  $\mu A$ ,  $V_{CB}$ = -1 V

#### Lateral PNP (PLAT) Electrical Specifications, T=27 °C

| CHARACTERISTICS          | FY400  | RY2KA  | RY2KD  | <u>NI</u>            | UNITS   |

|--------------------------|--------|--------|--------|----------------------|---------|

| Resistor Value           | 400    | 2000   | 2000   | (note a)             | Ω       |

| Sheet Resistance         | 200    | 200    | 200    | 50                   | Ω/□     |

| Tolerance                | ± 17   | ± 17   | ± 20   | ± 10<br>(note b)     | %       |

| Drawn Width              | 3.6    | 2.2    | 1.6    | 4.8 min              | μm      |

| Temperature Coefficient  | -1250  | -1250  | -1250  | <200                 | ppm/°C  |

| Extra Mask Step          | no     | no     | no     | yes                  | (n.a.)  |

| Usable as M1 Cross Under | yes    | yes    | yes    | no                   | (n.a.)  |

| Max Current              | 3.6 mA | 2.2 mA | 1.6 mA | 1 mA/ μm<br>of width | ( n.a.) |

#### Resistor Notes:

- (a) Thin film NiCr resistors can be designed for values ranging from 5 ohms to several thousand ohms.

- (b) Tolerance and matching depend on the design of specific NiCr resistors. On-chip laser trimming is available to achieve tolerances as low as  $\pm$  0.1% and matching as low as  $\pm$  0.02%.

#### **QuickChip 7 Resistors**

# **Quality Assurance**

For more than 40 years, the Tektronix commitment to excellence has earned the company a reputation for making instruments of the highest quality. The products of Tektronix Microelectronics have contributed to the performance and reliability of Tektronix instrumentation for more than 20 years.

Our goal is to ship 100 percent quality products on time--every time.

Tektronix Microelectronics' Quality Assurance program consists of quality systems and inspections designed to achieve those goals.

The program consists of:

- Documentation control system including engineering change control.

- Vendor qualification procedure including vendor audits, first article inspections, and vendor product certification.

- Statistical process control (SPC program)

- Lot traceability.

- Independent quality and reliability audits.

- Operator training and certification.

- Preventive maintenance programs.

- Static and environmental control.

- Closed loop corrective action system.

## SALES AND TECHNICAL INFORMATION

Please Contact:

Microelectronics Product Line

Tektronix, Inc.

P.O. Box 500

Mail Station 59-420

Beaverton, OR 97077

TEL: (503) 627-2515

FAX: (503) 627-5560

or your local sales representative.

Information furnished by Tektronix in this publication is believed to be accurate. Devices sold by Tektronix are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Tektronix makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringment. Tektronix makes no warranty of merchantability or fitness for any purpose.

These products are intended for use in normal commercial applications. For applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment, contact Tektronix Microelectronics for additional details

Copyright © 1992, Tektronix, Inc. All rights reserved. Printed in U.S.A. Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specification and price change privileges reserved. TEKTRONIX, TEK, TEKSPICE, QuickCustom, QuickChip, QuickTile, QuERC and QuickCi are registered trademarks. For further information contact: Tektronix, Inc., P.O. Box 500, Beaverton, OR 97077. Cable: TEKWSGT. Subsidiaries and distributors worldwide.

**Tektronjx**

Test and Measurement