# Now a product of Brooktree Corporation. Call 1-800-843-3642

#### R8069B

# Line Interface Unit (LIU)

#### INTRODUCTION

The Rockwell R8069B Line Interface Unit (LIU) is a single chip CMOS device that interfaces the Rockwell R8070 T1/CEPT PCM Transceiver or RT9170 Intelligent T1 Controller to the physical T-1/CEPT PCM30 transmission medium.

The R8069B LIU device contains analog and digital circuits which are based on CMOS technology to support the line interface function required in ISDN primary rate transmission. The R8069B provides capabilities for 4-wire transmission of image, voice, or data signals; clock extraction; line equalization; bipolar violation detection; jitter accommodation; and AIS (Blue Alarm) generation and detection. In addition, the device operates at 1.544 or 2.048 Mbit/s and meets pulse shape and jitter requirements specified by T-1 or PCM30 standards, respectively.

The R8069B is ideally suited for image, voice, or data transmission required in ISDN primary rate applications. The device is highly integrated and requires minimal external components.

Internal LIU functions allow system designers to minimize their development cost and easily implement a T-1/PCM30 physical interface to primary rate lines without concern about most of the complex details normally associated with such a design. The R8069B also provides a high level of integration which increases system reliability, reduces space and achieves higher levels of performance and quality.

#### **FEATURES**

- Compatible with T-1 (1.544 Mbit/s) DSX-1 and PCM30 (2.048 Mbit/s) standards

- Selectable T-1 and PCM30 clock rates

- Directly compatible with Rockwell R8070 T-1/CEPT PCM Transceiver, RT9170 Intelligent T1 Controller, and R8071 ISDN/DMI Link Layer Controller devices

- Meets AT&T Technical Advisory No. 34 for T-1 and CCITT Recommendation G.703 for PCM30

- Meets jitter requirements specified in AT&T Publication 62411 (Oct. 1985) for T-1 and CCITT Recommendation G.823 for PCM30

- · Phase locked loop for loop timing applications

- Incorporates a frequency discriminator in PLL circuitry to enhance frequency training and locking

- Provides line equalization for up to 660 feet of 100  $\Omega$  22-gauge plastic insulated (ABAM) cable for T-1

- Accommodates pulse shape requirements for 75  $\Omega$  and 120  $\Omega$  lines in PCM30 application and 100  $\Omega$  T-1 lines

- Intrinsic jitter less than 0.05 UI

- · Jitter attenuation roll off starts at 2 Hz

- Jitter tolerance above 0.4 UI for jitter frequency from 20 kHz to 100 kHz

- 8-bit transmitter (TX) elastic store for system-provided timing alignment

- 44-bit receiver (RX) elastic store for input jitter and wander accommodation

- Provision to bypass RX elastic store

- Master/slave timing option

- Local and remote loopback modes with automatic RCLK switching

- · AIS (Blue Alarm) generation and detection

- Bipolar violation detector

- Automatic detection of external line-rate clock (EXCLK)

- Automatic centering of phase-lock loop when timing reference is absent

- On-chip line drivers, pulse shaping, and TX equalizer

- Analog CMOS technology

- CMOS/TTL compatible inputs and outputs

- Operates from a single +5V power supply

- Packaging options

- 28-pin plastic DIP

- 28-pin CERDIP

- 44-pin PLCC

#### ORDERING INFORMATION

### INTERFACE SIGNAL DESCRIPTION

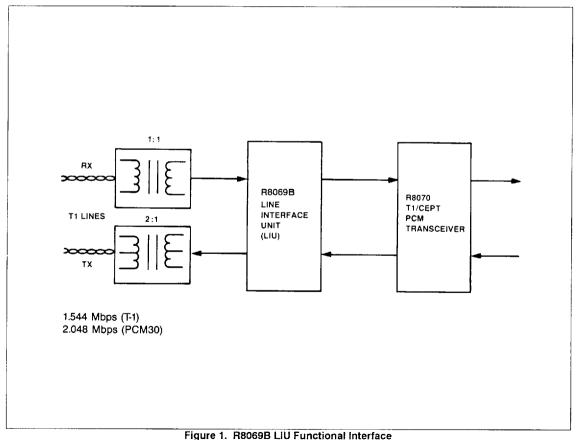

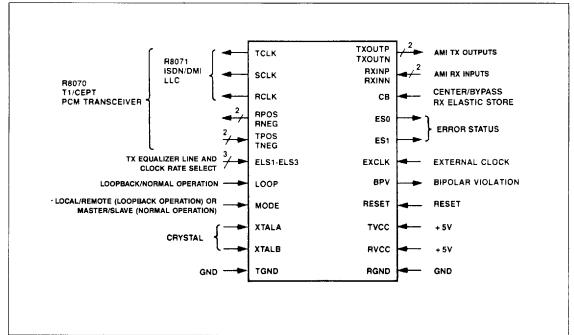

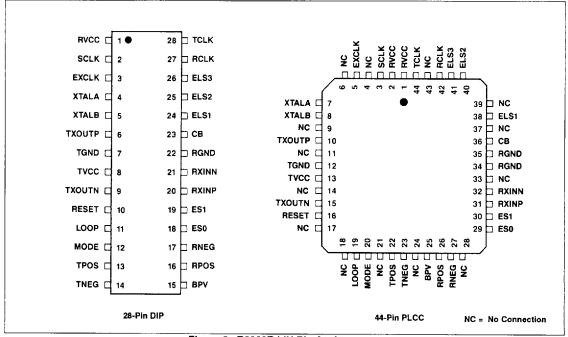

The R8069B interfaces directly to the R8070 and R8071 on one side and the DSX-1 or PCM30 demarcation point on the other, through transmit and receive transformers located external to the LIU device (Figure 1). The R8069B LIU interface signals are functionally grouped in Figure 2. Figure 3 shows the R8069B pin assignments. Table 1 describes the R8069B interface signals.

Figure 2. R8069B LIU Interface Signals

Figure 3. R8069B LIU Pin Assignments

Table 1. R8069B Interface Signal Descriptions

| Symbol         | VO. | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXINP, RXINN   | I   | Receive Data Input P, Receive Data Input N. Receive bipolar data from transmission line.  A 1:1 transformer is required on these input lines.                                                                                                                                                                                                                                                                                                                                                          |

| RPOS, RNEG     | 0   | Receive Unipolar Positive, Receive Unipolar Negative. RPOS and RNEG are the output of the received data recovered from RXINP and RXINN AMI line pulses. RPOS and RNEG have TTL levels and are alternate unipolar. (These lines can be directly connected to R8070's RPOS and RNEG inputs.) RPOS and RNEG are clocked out at the falling edge of RCLK (when elastic store bypass is enabled) or TCLK (when elastic store bypass is disabled).                                                           |

| RCLK           | 0   | Received Clock. RCLK is the recovered clock output which is used to clock the receive data outputs, RPOS and RNEG, from the receiver at its falling edge.                                                                                                                                                                                                                                                                                                                                              |

| EXCLK          | 1   | External Clock. EXCLK is a TTL level input. The clock frequency should be 1.544 MHz ± 32 ppm for T-1 applications and 2.048 MHz ± 50 ppm for PCM30 applications.                                                                                                                                                                                                                                                                                                                                       |

| СВ             | 1   | Center/Bypass Elastic Store. RX elastic store is centered on the rising edge of CB. RX elastic store is bypassed when CB is high. (Minimum pulse width is one clock cycle.)                                                                                                                                                                                                                                                                                                                            |

| BPV            | 0   | Bipolar Violation Detection. Whenever a bipolar violation on the receive data is detected, the BPV generates a positive pulse of one clock interval at the falling edge of TCLK (CB low) or RCLK (CB high).                                                                                                                                                                                                                                                                                            |

| ES0, ES1       | 0   | Error Status. The Error Status is continuously updated on the rising edge of TCLK.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -              |     | ES0 ES1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                |     | O AIS Detected. AIS is activated by detection of a string of 2316 ones with no more than one zero. AIS is deactivated when three or more zeros are detected after the AIS detection.  O 1 Loss of Signal. Activated when the input signal level drops below 0.97 volts for 175 bit times; deactivated when the input signal level rises above 0.97 volts.  O Elastic Buffer Limit. Indicates an overrun/underrun on the elastic store. It is cleared when CB or RESET is activated.  Normal Operation. |

| TPOS, TNEG     | ı   | Transmit Unipolar Positive, Transmit Unipolar Negative. TPOS and TNEG are the "unipolar paired" input for transmitted data. TPOS and TNEG must have TTL levels and must be alternate unipolar. (These lines can be directly connected to R8070 TPOS and TNEG outputs.) They are clocked in at the falling edge of TCLK or EXCLK (see Table 4). There are only three valid states for TPOS/TNEG (10, 01, 00); state 11 is not allowed.                                                                  |

| TXOUTP, TXOUTN | 0   | Transmit Data Output P, Transmit Data Output N. Transmit bipolar data to transmission line. A 1:2 step up transformer is needed at the output.                                                                                                                                                                                                                                                                                                                                                         |

| TCLK           | 0   | Transmit Clock. TCLK is the transmit clock output which is generated by the crystal based PLL2. It normally references EXCLK or the receive data input depending on mode. In the at sence of EXCLK and receive data, the TCLK reference is the on-chip crystal oscillator center frequency. (See Table 4.)                                                                                                                                                                                             |

| SCLK           | 0   | System Clock. SCLK runs at two times the clock rate of TCLK, which is required by the R8071. This output can be directly connected to the R8071 SCLK input.                                                                                                                                                                                                                                                                                                                                            |

| ELS1-ELS3      | I   | <b>Equalization Select.</b> Strap inputs that select T-1 cable length equalization or PCM30 line load impedance. (See Table 2.)                                                                                                                                                                                                                                                                                                                                                                        |

| LOOP           | I   | Loopback Select. LOOP low selects either master or slave. LOOP high selects either local or remote loopback. (See "Mode and Loop Timing" section for details.)                                                                                                                                                                                                                                                                                                                                         |

| MODE           | I   | Mode Select. Mode low selects local loopback or master timing mode. Mode high selects remote loopback or slave. (See "Mode and Loop Timing" section for details.)                                                                                                                                                                                                                                                                                                                                      |

### Table 1. R8069B Interface Signal Descriptions (Cont'd)

| 1 | Book When Book in greated the BV election toro is contared the VCO is trained to leak                                                                                                                                             |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Reset. When Reset is asserted, the RX elastic store is centered, the VCO is trained to lock to EXCLK, or the crystal-based PLL2 if EXCLK is absent. This resetting mechanism is disabled when both LOOP and MODE inputs are high. |

| 1 | XTAL Input pins. Connect an external, parallel resonant, 6.176 MHz or 8.192 MHz crystal to these pins for T-1 or PCM30 application, respectively. NOTE: Do not connect a TTL or CMOS clock source to these pins.                  |

| 1 | Transmit Line Driver Power. +5V power supply for the transmit line driver.                                                                                                                                                        |

| 1 | Transmit Line Driver Ground. Ground for the transmit line driver.                                                                                                                                                                 |

| 1 | Power. +5V power supply.                                                                                                                                                                                                          |

| 1 | Ground.                                                                                                                                                                                                                           |

|   | I<br>I<br>I<br>I                                                                                                                                                                                                                  |

#### **FUNCTIONAL DESCRIPTION**

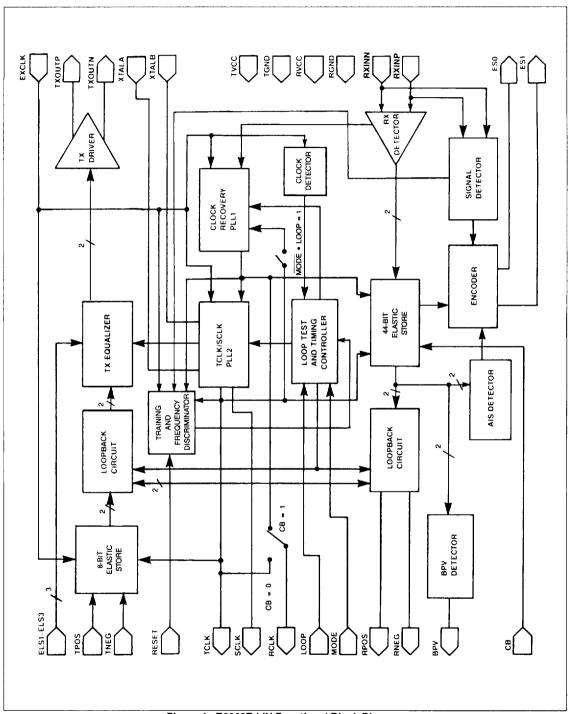

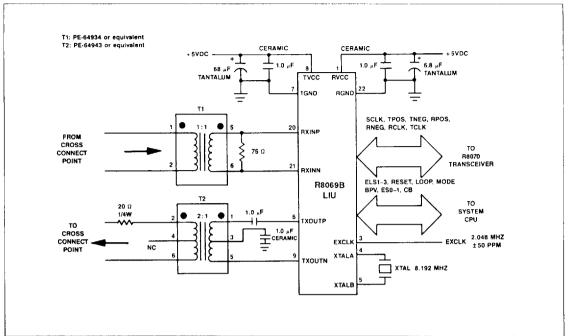

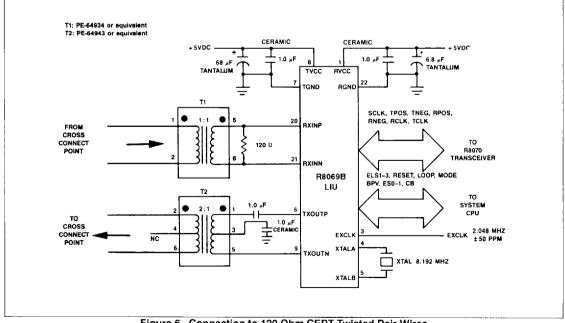

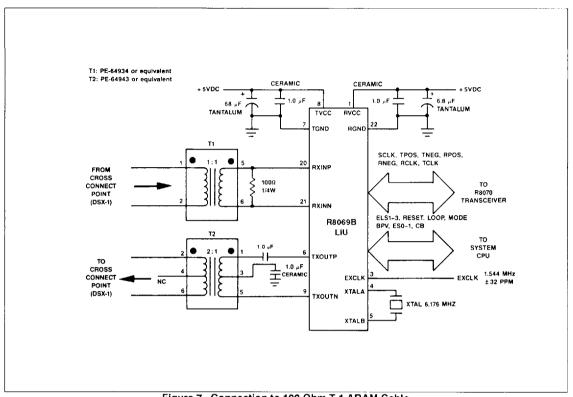

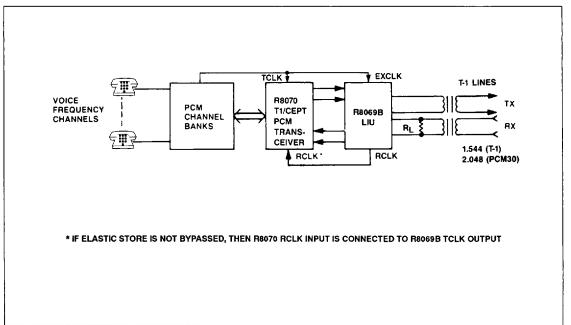

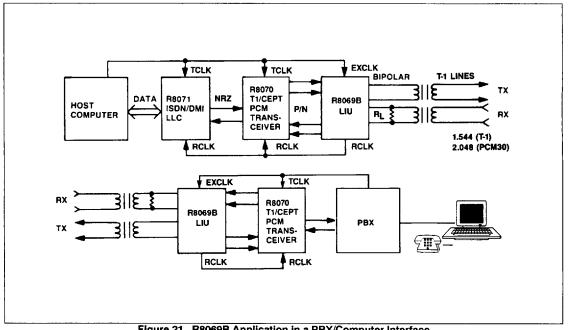

The R8069B LIU contains both analog and digital circuitry which independently process transmit and receive primary rate voice or data information. Circuitry to provide master, slave, local loopback, remote loopback, and their derivatives is also included. A simplified block diagram of the R8069B LIU is depicted in Figure 4. Typical R8069B LIU connections in CEPT and T-1 applications are shown in Figures 5, 6, and 7.

#### TRANSMIT SECTION

Unipolar transmit data (TPOS and TNEG) is clocked into the R8069B by the falling edge of TCLK or EXCLK. The transmit data passes through an 8-bit transmit elastic store buffer which can accommodate up to 6 Unit Interval (UI) peak-peak jitter (fj > 10 Hz) and wander (fj < 10 Hz). The transmit data then goes to a line equalizer for pulse shaping and conditioning. The line equalizer will equalize up to 660 feet of 100  $\Omega$  ABAM cable (22-gauge plastic insulated cable with characteristics specified in Appendix B of the AT&T Technical Reference Number 34, September 1983)\*.

Three encoded inputs, ELS1-ELS3, allow selection of cable length equalization and clock rates (Table 2). Equalization of cable length of 0-660 feet in increments of 110 feet is selectable for T-1 line. A 20  $\Omega$  resistor should be connected in series with 75 $\Omega$  coaxial cable connector (see Figure 5 and Table 2).

The equalized data is then provided to a line driver. In T-1 applications the driver can drive a twisted pair cable of up to 660 feet. The isolated pulse template at the end of the cable (at DSX-1) meets the pulse shape requirement specified by AT&T Technical Advisory No. 34. In PCM30 mode, the R8069B LIU provides a pulse shape which meets the requirements of CCITT Recommendation

G.703. The pulse shape is measured at the output of the transmit transformer. The upper and lower limits of the T-1 or PCM30 pulse template were used to qualify the pulse shape.

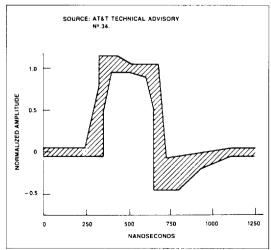

The DSX-1 pulse template for T-1 is specified by Table 3 and illustrated in Figure 8.

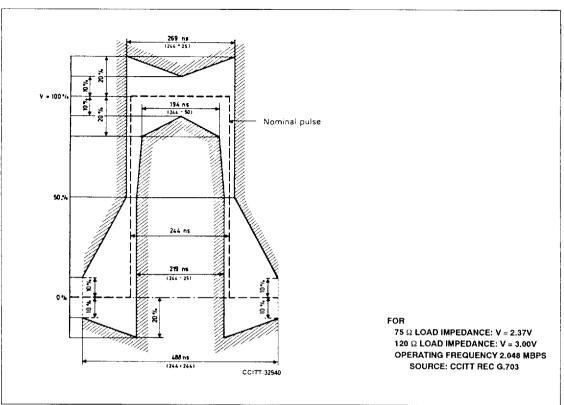

The output pulse waveform for PCM30 conforms to the template shown in Figure 9.

Table 2. ELS1 - ELS3 Encoding

| ELS3 | ELS2 | ELS1 | Cable Length/<br>Line Impedance | Clock Rate <sup>1</sup> |

|------|------|------|---------------------------------|-------------------------|

| L    | L    | L    | 0 - 110 ft                      | T-1                     |

| L    | L    | H    | 110 - 220 ft                    | T-1                     |

| L    | н    | L    | 220 - 330 ft                    | T-1                     |

| L    | Н    | Н    | 330 - 440 ft                    | T-1                     |

| Н    | L    | L    | 440 - 550 ft                    | T-1                     |

| Н    | L    | Н    | 550 - 660 ft                    | T-1                     |

| Н    | Н    | L    | 75/120 Ω <sup>2,3</sup>         | PCM30                   |

#### NOTES:

- 1. T-1 = 1.544 Mbits/s; PCM30 = 2.048 Mbits/s.

- See Figures 5 and 6.

- 3. If the selected equalization line code is ELS3 = H, ELS2 = H, and ELS1 = L, then a 20  $\Omega$  resistor is required at the line side of the transmit transformer (see Figure 5). This is the recommended mode in a 75  $\Omega$  PCM30 application to ensure that the pulse shape meets G.703.

At the customer's option, the value ELS3 = H, ELS2 = H, and ELS1 = H may be selected and the  $20\Omega$  resistor can be deleted. In this configuration, the pulse shape will normally conform to G.703, but is not guaranteed in every case.

<sup>\*</sup>The R8069B was tested using AT&T ABAM cable part no. 606-6/22 R6900.

Figure 4. R8069B LIU Functional Block Diagram

Figure 5. Connection to 75 Ohm CEPT Coax Cable

Figure 6. Connection to 120 Ohm CEPT Twisted Pair Wires

Figure 7. Connection to 100 Ohm T-1 ABAM Cable

Table 3. DSX-1 Pulse Template Corner Points (T-1)

| Ma   | ximum Curve   | Minimum Curve |                       |  |  |

|------|---------------|---------------|-----------------------|--|--|

| ns   | Normalized ns |               | Normalized<br>Voltage |  |  |

| 0    | 0.05          | 0             | -0.05                 |  |  |

| 250  | 0.05          | 350           | -0.05                 |  |  |

| 325  | 0.80          | 350           | 0.50                  |  |  |

| 325  | 1.15          | 400           | 0.95                  |  |  |

| 425  | 1.15          | 500           | 0.95                  |  |  |

| 500  | 1.05          | 600           | 0.90                  |  |  |

| 675  | 1.05          | 650           | 0.50                  |  |  |

| 725  | -0.07         | 650           | -0.45                 |  |  |

| 1100 | 0.05          | 800           | -0.45                 |  |  |

| 1250 | 0.05          | 925           | -0.20                 |  |  |

|      |               | 1100          | -0.05                 |  |  |

|      |               | 1250          | -0.05                 |  |  |

Figure 8. DSX-1 Isolated Pulse Template (T-1)

Figure 9. Isolated Pulse Template (PCM30)

# Line Interface Unit (LIU)

#### RECEIVE SECTION

On the receive side, bipolar input data (RXINP and RXINN) is converted to unipolar signal (RPOS and RNEG). Phase locked loop 1 (PLL1) is used to recover the clock from the incoming bipolar data.

A second phase locked loop (PLL2) smooths the clock signal coming from PLL1 or the EXCLK input pin, and generates both Transmit Clock (TCLK) and System Clock (SCLK). TCLK represents the base frequency (1.544 MHz or 2.048 MHz) and SCLK is twice the base frequency. TCLK and SCLK are used as transmit clocks by the R8070 and R8071, respectively.

In master mode, PLL2 locks on the EXCLK as a reference if EXCLK is present. In the absence of EXCLK, PLL2 will reference the crystal-based clock source. In slave mode, PLL2 will use the output of PLL1 as a reference.

The receive section also contains a 44-bit elastic store buffer which can accommodate up to 40 UI peak-peak litter and wander.

#### RECEIVER RESET

When the RESET input is asserted high, the clock recovery PLL1 locks to EXCLK or the crystal-based clock source for training. After RESET is switched low, PLL1 will again lock to the incoming receive data.

#### RECEIVER TRAINING MODE

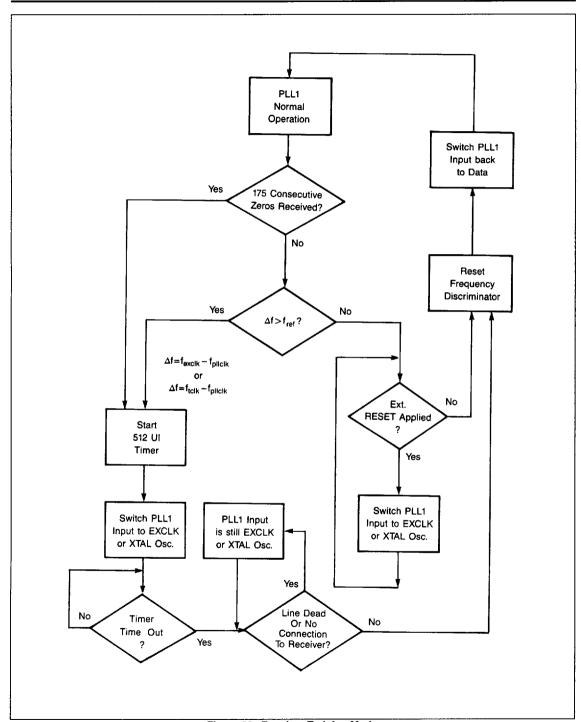

Receiver training can be initiated by any of three ways (Figure 22 on page 22):

- 1. Loss of signal (receipt of 175 consecutive zeros) triggers training for a minimum period of 512 UI; 1 UI = 648 ns (T-1) or 488 ns (PCM30). If loss of signal still persists at the end of this period, the PLL1 continues to train. Training stops as soon as the received signal is a 1 bit.

- 2. Training is activated for 512 UI when the frequency difference of PLL1 and the reference clock exceeds 38 kHz. The frequency difference is measured by a frequency discriminator. The reference clock is the external clock at EXCLK input pin or TCLK if the external clock is absent.

- 3. Training is activated by asserting the RESET input and continues as long as RESET is high.

#### **ALARM INDICATOR SIGNAL (AIS)**

Alarm indicator signal (AIS) is asserted when the receive data consisting of 2316 unframed ones and less than 2 zeroes are detected. This condition is represented in the error status by ES0=L and ES1=L.

When multiple error status occurs, only the status that has the highest priority is reported. Both Loss of Signal and AIS share the highest priority. They are mutually exclusive. Elastic Buffer overflow/underflow has lower priority than AIS or Loss of Signal.

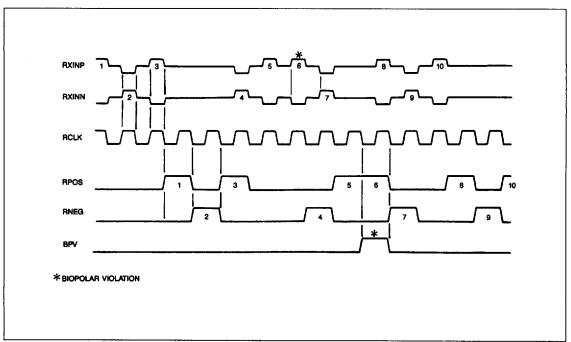

#### BIPOLAR VIOLATION

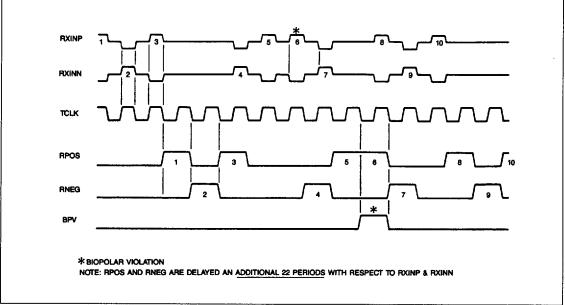

Bipolar violation is reported on the BPV output pin whenever any bipolar violations occur on the receive data. BPV generates a positive pulse of one unit interval at the falling edge of TCLK or RCLK. A unit interval is equivalent to 648 ns for T-1, or 488 ns for PCM30. (See Figures 15-18.)

#### RECEIVE ELASTIC STORE BUFFER

In order to avoid data loss due to jitter, a 44-bit elastic store is provided in the receive data path. It's function is to eliminate the effect of short term jitter resulting from transmission line impairments. The receive data is written into the elastic buffer by the Recovered Clock (RCLK) and read out from the elastic buffer by TCLK. The output of the elastic buffer drives the unipolar output signal (RPOS and RNEG).

When the receive elastic buffer is enabled (CB=L), RCLK is the same as TCLK. They will have the same phase and frequency relation. TCLK is generated from PLL2. When the receive elastic buffer is bypassed (CB=H), then RCLK is the recovered clock extracted from the receive data by PLL1, and is not in phase with TCLK. (See Figures 15 and 16.)

#### LOSS OF SIGNAL (LOS)

Loss of Signal indicates the received signal is less than 0.97 V for 175 bit times. It is represented by the Error Status output pins ES0=L and ES1=H. When Loss of Signal occurs, PLL2 uses either the external clock (EXCLK) or the crystal as an input to generate TCLK and SCLK, PLL1 locks onto EXCLK, if present, or onto TCLK. When receive data returns, PLL1 will lock back onto the receive data stream.

### **EXCLK ACTIVITY DETECTOR**

The EXCLK activity detector monitors the presence of EXCLK The absence of EXCLK is acknowledged if EXCLK has no transition for 16 consecutive TCLK periods. The EXCLK or the crystal is used as a reference by PLL2. (See Table 4.)

#### RECEIVE ONLY WITH TRANSMITTER FUNCTION DISABLED

The R8069B LIU transmitter is disabled and the TX line driver is put into high impedance ( $R_0 > 10K \Omega$ ) under the following condition:

> LOOP TPOS = Low = High MODE = High TNEG = Low RESET = High

In this mode, the receiver can be reset by asserting the MODE input low for at least 200 µs.

#### TEST MODE CONDITION

TPOS, TNEG, and RESET should not be set to high levels simultaneously because this will put the R8069B in a factory test mode.

#### MODE AND LOOP TIMING MODE

Mode and Loop modes are determined by the state of the MODE and LOOP pins. Refer to LOOP AND MODE SE-LECTION for selection details. For data alignment and clock sources, refer to Table 4.

#### MASTER TIMING MODES

#### Normal Operation without EXCLK

TCLK and SCLK reference the on-chip crystal oscillator nominal frequency while RCLK is based on TCLK (CB=0) or the recovered clock (CB=1). TPOS and TNEG are clocked in on the falling edge of TCLK. The source of TXOUTP/N is TPOS/TNEG, RPOS and RNEG are clocked out on the falling edge of RCLK. The source of RPOS/RNEG is RXINP/N.

#### Normal Operation with EXCLK

TCLK and SCLK reference EXCLK while RCLK references TCLK (CB=0) or the recovered clock (CB=1). TPOS and TNEG are clocked in on the falling edge of EXCLK. The source of TXOUTP/N is TPOS/TNEG, RPOS and RNEG are clocked out on the falling edge of RCLK. The source of RPOS/RNEG is RXINP/N.

#### Local Loopback without EXCLK

TCLK and SCLK reference the on-chip crystal oscillator nominal frequency while RCLK is based on TCLK, TPOS and TNEG are clocked in on the falling edge of TCLK. TXOUTP/N transmit all ones. RPOS and RNEG are clocked out on the falling edge of RCLK. The source of RPOS/RNEG is TPOS/TNEG.

#### Local Loopback with EXCLK

TCLK and SCLK reference EXCLK while RCLK references TCLK, TPOS and TNEG are clocked in on the falling edge of EXCLK, TXOUTP/N transmit all ones, RPOS and RNEG are clocked out on the falling edge of RCLK. The source of RPOS/RNEG is TPOS/TNEG.

#### Remote Loopback without EXCLK

TCLK and SCLK reference the on-chip crystal oscillator nominal frequency while RCLK is based on TCLK (CB=0) or the recovered clock (CB=1). TPOS and TNEG are clocked in on the falling edge of TCLK. The source of TXOUTP/N is RXINP/N. RPOS and RNEG are clocked out on the falling edge of RCLK. The source of RPOS/RNEG is RXINP/N.

#### Remote Loopback with EXCLK

TCLK and SCLK reference EXCLK while RCLK references TCLK (CB=0) or the recovered clock (CB=1). TPOS and TNEG are clocked in on the falling edge of EXCLK. The source of TXOUTP/N is RXINP/N, RPOS and RNEG are clocked out on the falling edge of RCLK. The source of RPOS/RNEG is RXINP/N.

#### SLAVE TIMING MODES

### Normal Operation without EXCLK

TCLK and SCLK reference the recovered clock while RCLK references TCLK (CB=0) or the recovered clock (CB=1). TPOS and TNEG are clocked in on the falling edge of TCLK. The source of TXOUTP/N is TPOS/TNEG. RPOS and RNEG are clocked out on the falling edge of RCLK. The source of RPOS/RNEG is RXINP/N.

#### Normal Operation with EXCLK

TCLK and SCLK reference the recovered clock while RCLK references TCLK (CB=0) or the recovered clock (CB=1). TPOS and TNEG are clocked in on the falling edge of TCLK. The source of TXOUTP/N is TPOS/TNEG. RPOS and RNEG are clocked out on the falling edge of RCLK. The source of RPOS/RNEG is RXINP/N.

Table 4. Data and Clock Sources

|                   | ĺ     |     |           | Sour    | ce of   |          |           | S    | ource of RC | CLK       |           |          |

|-------------------|-------|-----|-----------|---------|---------|----------|-----------|------|-------------|-----------|-----------|----------|

|                   |       |     |           | TCLK ar | d SCLK  |          |           |      | CB=1        | CB=1      | Source    |          |

| Timing/           | inp   | out | 1         | No Data | Data    | TPOS/    | Source    | i    | and         | and       | of        | RPOS/    |

| Operation         | Pi    | ns* | EXCLK     | on      | on      | TNEG     | of        |      | Data on     | NoData on | RPOS/     | RNEG     |

| Mode              | М     | L   | Supplied? | RXINP/N | FXINP/N | Alignmnt | TXOUTP/N  | CB=0 | RXINP/N     | PXINP/N   | RNEG      | Alignmen |

| Master            |       |     |           |         |         |          |           |      |             |           |           |          |

| Normal            | L     | L   | N         | XTAL.   | XTAL    | TOLK     | TPOS/TNEG | TCLK | PXINP/N     | TCLK      | PXINP/N   | RCLK     |

| Normai            | L     | L   | Y         | EXCLK   | EXCLK   | EXCLK    | TPOS/TNEG | TCLK | PXINP/N     | EXCLK     | PXINP/N   | RCLK     |

| Local Loopback    | L     | į H | N         | XTAL    | XTAL    | TCLK     | All Ones  | TCLK | TCLK        | TCLK      | TPOS/TNEG | RCLK     |

| Local Loopback    | L     | Н   | Y         | EXCLK   | EXCLK   | EXCLK    | All Ones  | TCLK | TCLK        | TCLK      | TPOS/TNEG | RCLK     |

| Remote Loopback   | Н     | Н   | N         | XTAL    | XTAL    | TCLK     | PXINP/N   | TCLK | RXINP/N     | TCLK      | PXINP/N   | RCLK     |

| Remote Loopback   | Н     | Н   | Y         | EXCLK   | EXCLK   | EXCLK    | PXINP/N   | TCLK | RXINP/N     | EXCLK     | RXINP/N   | RCLK     |

| Slave             |       | İ   |           |         |         |          | į         |      |             |           |           |          |

| Normal            | Н     | L   | N         | XTAL    | RXINP/N | TCLK     | TPOS/TNEG | TCLK | RXINP/N     | TCLK      | RXINP/N   | RCLK     |

| Normai            | Н     | L   | Y         | EXCLK   | RXINP/N | TCLK     | TPOS/TNEG | TCLK | PXINP/N     | EXCLK     | RXINP/N   | RCLK     |

| Local Loopback    | L     | Н   | N         | XTAL    | RXINP/N | TCLK     | All Ones  | TCLK | TCLK        | TCLK      | TPOS/TNEG | 1        |

| Local Loopback    | L     | H   | Y         | EXCLK   | RXINP/N | TCLK     | All Ones  | TCLK | TCLK        | TCLK      | TPOS/TNEG | RCLK     |

| Remote Loopback   | Н     | Н   | N         | XTAL    | RXINP/N | TCLK     | PXINP/N   | TCLK | RXINP/N     | TCLK      | RXINP/N   | RCLK     |

| Remote Loopback   | н     | Н   | Y         | EXCLK   | RXINP/N | TCLK     | PXINP/N   | TCLK | RXINP/N     | EXCLK     | RXINP/N   | RCLK     |

| * M = MODE input; | L = L | .00 | input.    |         |         |          | ·         |      |             | L         |           | L        |

# Line Interface Unit (LIU)

#### Local Loopback without EXCLK

TCLK and SCLK reference the recovered clock while RCLK references TCLK. TPOS and TNEG are clocked in on the falling edge of TCLK. TXOUTP/N transmit all ones. RPOS and RNEG are clocked out on the falling edge of RCLK. The source of RPOS/RNEG is TPOS/TNEG.

#### Local Loopback with EXCLK

TCLK and SCLK reference the recovered clock while RCLK references TCLK. TPOS and TNEG are clocked in on the falling edge of TCLK, TXOUTP/N transmit all ones. RPOS and RNEG are clocked out on the falling edge of RCLK. The source of RPOS/RNEG is TPOS/TNEG.

#### Remote Loopback without EXCLK

TCLK and SCLK are based on the recovered clock while RCLK is based on TCLK (CB=0) or the recovered clock (CB=1). TPOS and TNEG are clocked in on the falling edge of TCLK. The source of TXOUTP/N is RXINP/N. RPOS and RNEG are clocked out on the falling edge of RCLK. The source of RPOS/RNEG is RXINP/N.

#### Remote Loopback with EXCLK

TCLK and SCLK are based on the recovered clock while RCLK is based on TCLK (CB=0) or the recovered clock (CB=1). TPOS and TNEG are clocked in on the falling edge of TCLK. The source of TXOUTP/N is RXINP/N. RPOS and RNEG are clocked out on the falling edge of RCLK. The source of RPOS/RNEG is RXINP/N.

#### MODE AND LOOP SELECTION

The basic modes of operation are as follows:

| MODE | LOOP | Mode of Operation            |

|------|------|------------------------------|

| Low  | Low  | Master Normal                |

| High | Low  | Slave Normal                 |

| Low  | High | Master/Slave Local Loopback  |

| High | High | Master/Slave Remote Loopback |

MODE and LOOP signals are latched on the falling edge of EXCLK or TCLK (if no EXCLK is present) in master timing modes or on the falling edge of TCLK in slave timing

The timing mode (master or slave) must be selected before local or remote loopback is selected. When a loopback mode is selected, the R8069B remembers the timing mode (master or slave) it was last in. Care must be taken while switching from one mode to another so as not to unintentionally change the timing mode, MODE and LOOP should not both be changed during the same clock cycle when switching from a normal timing mode to a loopback mode.

**EXAMPLE 1.** You are in slave normal and you want to switch to master remote loopback. Each change lasts a minimum of one clock cycle.

| Current mode is slave normal       | MODE = H | LOOP = L |

|------------------------------------|----------|----------|

| Change to master normal            | MODE = L | LOOP = L |

| Change to master local loopback    | MODE = L | LOOP = H |

| Change to master remote loopback   | MODE = H | LOOP = H |

| Final mode is master remote loopba | ick.     |          |

**EXAMPLE 2.** You are in master normal and you want to switch to slave local loopback. Each change lasts a minimum of one clock cycle.

| Current mode is master normal       | MODE = L | L00P = L |

|-------------------------------------|----------|----------|

| Change to slave normal              | MODE = H | LOOP = L |

| Change to slave remote loopback     | MODE = H | LOOP = H |

| Change to slave local loopback      | MODE = L | LOOP = H |

| Final mode is slave local loopback. |          |          |

#### R8069 JITTER CONFORMANCE

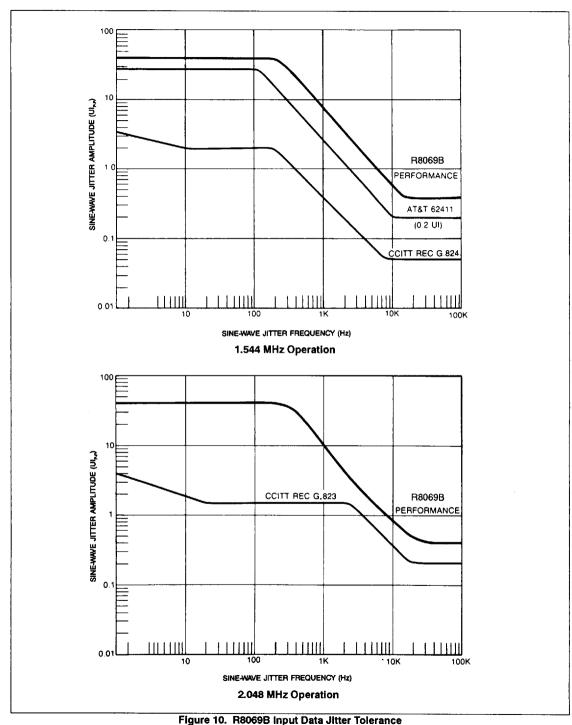

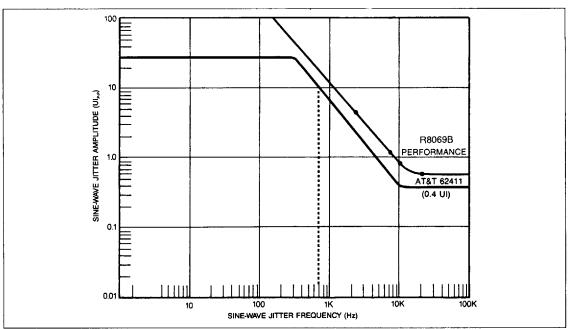

Input litter tolerance, intrinsic output litter and litter transfer function of the R8069B surpasses the requirements set forth in AT&T Pub 62411 and CCITT Recommendation G.823.

Jitter is defined as a short term phase shift of a digital signal from its ideal position in time. Wander (jitter below 10 Hz) is a long term phase shift of a digital signal which may result due to change in the propagation delay of the transmission media being used.

Input jitter tolerance is the amount of jitter that the Data Terminal Equipment (DTE) can accept in its input signal and still be able to operate with specified bit error rate (BER <10-8). The input jitter tolerance of the R8069B is shown in Figure 10. The input jitter tolerance of the R8069B PLL clock recovery circuit is shown in Figure 11.

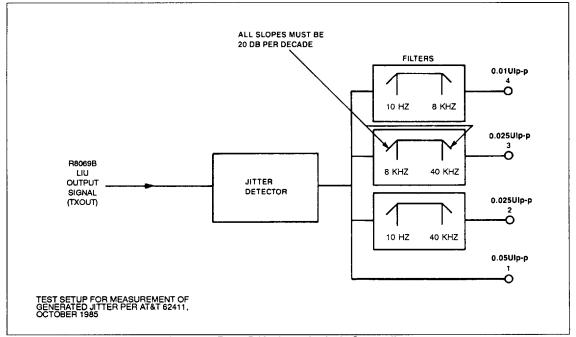

Intrinsic output jitter is the inherent jitter generated within the individual equipment when the input signal is jitter free. The R8069B's novel PLL utilizes a parallel resonant crystal in order to achieve a very low intrinsic output jitter. The maximum intrinsic output jitter is shown in Figure 12.

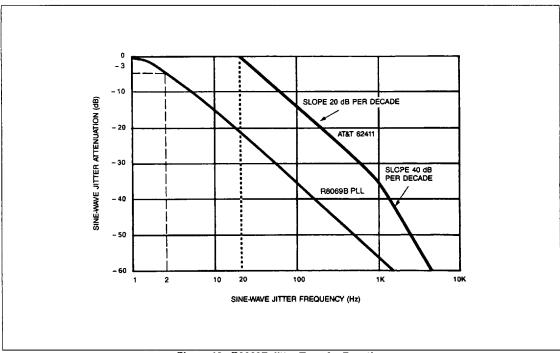

Jitter transfer function represents the amount of jitter that is carried over from the input signal to the output signal. The R8069B advanced design minimizes this transference of litter from the input signal to the output signal as depicted in Figure 13.

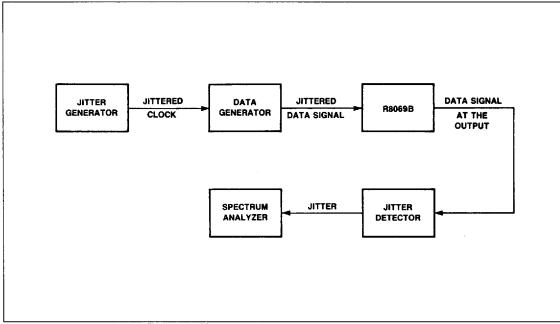

The test setup to measure the DTE jitter transfer function is shown in Figure 14.

#### RECEIVE AND TRANSMIT WAVEFORMS

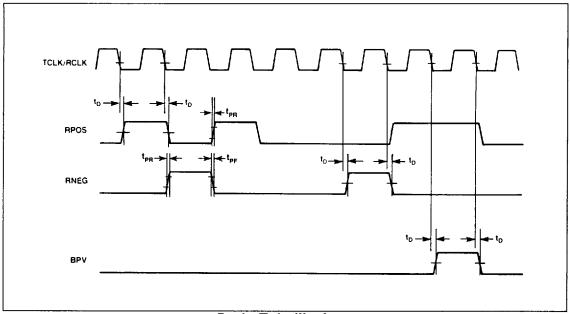

Receive waveforms with elastic store enabled and bypassed are shown in Figures 15 and 16, respectively.

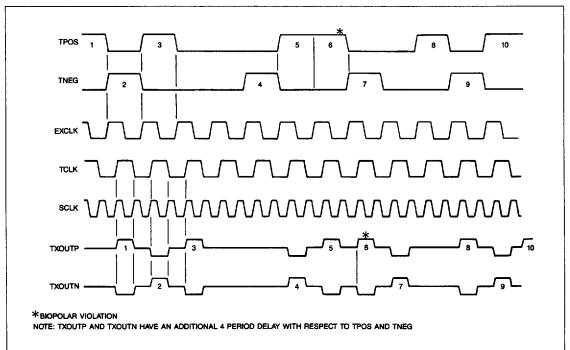

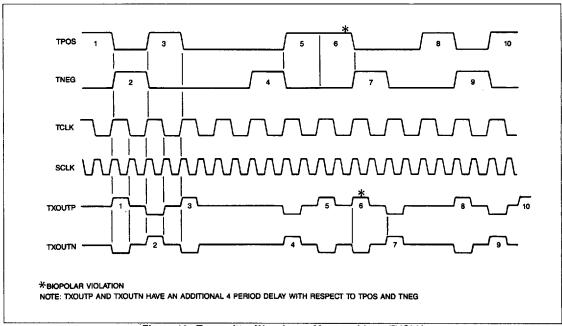

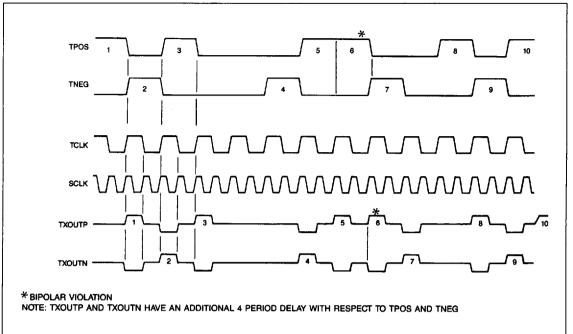

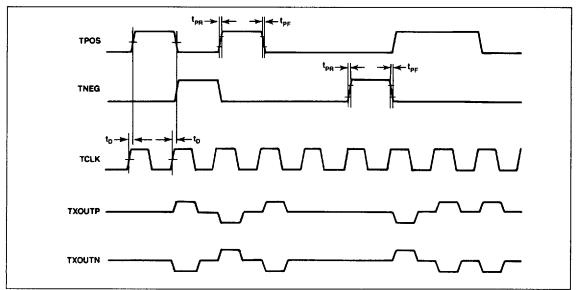

Transmit waveforms for master mode with and without EXCLK source are shown in Figures 17 and 18, respectively. Transmit waveforms for slave mode are shown in Figure 19.

R8069B

Figure 11. R8069B PLL Clock Circuit Jitter Tolerance

Figure 12. R8069B Maximum Intrinsic Output Jitter

Figure 13. R8069B Jitter Transfer Function

Figure 14. Measurement of DTE Jitter Transfer Function

Figure 15. Receive Waveforms-Elastic Store Bypass (CB=1)

Figure 16. Receive Waveforms-Elastic Store Enable (CB=0)

Figure 17. Transmitter Waveforms-Master with EXCLK

Figure 18. Transmitter Waveforms-Master without EXCLK

Figure 19. Transmitter Waveforms-Slave Mode

#### SYSTEM APPLICATIONS

The R8069B can be used in a wide variety of applications for North American T-1, European PCM30, and world-wide ISDN Primary Rate Services. PBXs, Channel Banks, Computer System Interface, Network Switches, and Multiplexers are a few of the many systems in which the R8069B can be effectively used. Figures 20 and 21 illustrate two applications.

Application Note, R8069/R8069A Interface Transformer Specifications and Connections, Order No. 340, also applies to the R8069B.

#### INTERFACE REQUIREMENTS

Table 5 defines the general R8069B interface requirements.

The recommended crystal and transformer specifications are defined in Tables 6 and 7, respectively.

Figure 20. R8069B Application PCM Channel Banks

Figure 21. R8069B Application in a PBX/Computer Interface

### Table 5. General Interface Requirements

| Characteristic                              | Value                                                                                                                                     |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Operation                                   | 4-wire full-duplex balanced lines (T-1 or PCM30) or coax cable (PCM30)                                                                    |

| Transmit Pulse Requirements                 |                                                                                                                                           |

| Transmit Level                              |                                                                                                                                           |

| 1.544 Mbps (T-1)                            | 3 V (nominal). Fits the pulse shape template in DSX-1 Interconnect Specification (T-1)                                                    |

| 2.048 Mbps (PCM30)                          | 3 V (nominal). Fits the pulse shape template in CCITT Rec. G.703.<br>2.37 V (nominal). Fits the pulse shape template in CCITT Rec. G.703. |

| Transmit Pulse Width                        |                                                                                                                                           |

| 1.544 Mbps (AT&T & CCITT)                   | 324 ns (nominal)                                                                                                                          |

| 2.048 Mbps (CCITT)                          | 244 ns (nominal)                                                                                                                          |

| Transmit Clock Accuracy                     |                                                                                                                                           |

| Meets AT&T requirement                      | 1.544 MHz ±32 ppm *                                                                                                                       |

| Meets CCITT requirement                     | 1.544 MHz ±50 ppm*                                                                                                                        |

| Meets CCITT requirement                     | 2.048 MHz ±50 ppm*                                                                                                                        |

| •                                           | * When used with a crystal and EXCLK meeting recommended specifications.                                                                  |

| Receive Clock Tolerance                     | •                                                                                                                                         |

| Meets AT&T requirement                      | 1.544 MHz ±130 ppm**                                                                                                                      |

| Meets CCITT requirement                     | 1.544 MHz ±50 ppm**                                                                                                                       |

| Meets CCITT requirement                     | 2.048 MHz ±50 ppm**                                                                                                                       |

| ·                                           | ** When used with a crystal meeting recommended specifications.                                                                           |

| Input Jitter Tolerance                      | 40 UIP.P                                                                                                                                  |

| Receiver Sensitivity                        | 10 dB below DSX-1 or G.703 specification                                                                                                  |

| Diagnostics                                 | Local and remote loopback                                                                                                                 |

| Transmitter Transformer Test Load Impedance |                                                                                                                                           |

| 1.544 Mbps (AT&T & CCITT)                   | 100 Ω resistive                                                                                                                           |

| 2.048 Mbps (CCITT)                          | 120 $\Omega$ /75 $\Omega$ resistive                                                                                                       |

| Interface to R8070/RT9170/R8071             | •                                                                                                                                         |

| Level                                       | CMOS/TTL compatible                                                                                                                       |

| Clock timing                                | Meets R8070/RT9170/R8071 timing specifications                                                                                            |

| Data from R8070 or RT9170                   | Unipolar data to be transmitted on primary rate lines (TPOS and TNEG)                                                                     |

| Data to R8070 or RT9170                     | Unipolar data received from primary rate lines (RPOS and RNEG)                                                                            |

| Clocks to R8070/RT9170/R8071                | , , , , , , , , , , , , , , , , , , , ,                                                                                                   |

| Recovered Clock                             | RCLK                                                                                                                                      |

| Transmit clock                              | TCLK                                                                                                                                      |

| System Clock                                | SCLK (= 2 x TCLK)                                                                                                                         |

# Line Interface Unit (LIU)

Table 6. Recommended Crystal Specifications

| Parameter                                        | Value              |  |  |

|--------------------------------------------------|--------------------|--|--|

| Nominal Frequency @ 25°C                         |                    |  |  |

| T-1                                              | 6.176000 MHz       |  |  |

| PCM30                                            | 8.192000 MHz       |  |  |

| Operating Temperature                            | 0°C to 70°C        |  |  |

| Storage Temperature                              | 40°C to 85°C       |  |  |

| Oscillator Mode                                  | Fundamental        |  |  |

| Resonance Mode                                   | Parallel           |  |  |

| Load Capacitance (C <sub>L</sub> )               | 14 pF (see note 2) |  |  |

| Frequency Tolerance @ 25°C                       | ± 0.001% (±10 ppm) |  |  |

| Temperature Stability @ 0°C to 70°C              | ± 0.003% (±30 ppm) |  |  |

| Pullability @ 25°C and $C_L = 9.8 pF$            | ·                  |  |  |

| T-1                                              | +200 ppm min.      |  |  |

| PCM30                                            | +120 ppm min.      |  |  |

| Pullability @ $25^{\circ}$ C and $C_L = 23.0 pF$ |                    |  |  |

| T-1                                              | –200 ppm min.      |  |  |

| PCM30                                            | -120 ppm min       |  |  |

| Maximum Drive Level                              | 2.5 mW             |  |  |

| Series Resistance                                | 50 Ω max.          |  |  |

| Maximum Aging Per Year                           | 2 ppm              |  |  |

- 1. This table is an example of typical crystal requirements for a system design with a pulling range of ± 130 ppm. For different pulling range requirements, refer to Application Note, R8069-Series Crystal Specifications, Order No. 355.

- 2. C<sub>L</sub> includes typical 3.3 pF load capacitance due to board layout, crystal lead capacitance, and other stray capacitance, i.e.,

CL = CLIU LOAD + COTHER = 10.7 pF + 3.3 pF = 14 pF

Table 7. Recommended R8069B Transformer

| Parameter             | Value             |

|-----------------------|-------------------|

| Transmit Transformer  |                   |

| Turn Ratio            | 1CT:2CT           |

| Rise/Fall Time        | 22 ns max.        |

| Serial Resistance     | 0.7 Ω max.        |

| Primary Inductance    | 1 mH min.         |

| Isolation Voltage     | 1500 Vrms         |

| Insulation Resistance | 10,000 MΩ min.    |

| Average Power Rating  | 500 mW            |

| Leakage Inductance    | 0.30 μΗ - 0.55 μΗ |

| Receive Transformer   |                   |

| Turn Ratio            | 1:1               |

| Rise/Fall Time        | 22 ns max.        |

| Serial Resistance     | 0.7 Ω max.        |

| Primary Inductance    | 1 mH min.         |

| Isolation Voltage     | 1500 Vrms         |

| Insulation Resistance | 10,000 MΩ min.    |

| Average Power Rating  | 500 mW            |

| Leakage Inductance    | 0.55 μH max,      |

Figure 22. Receiver Training Mode

# R8069B

# **SWITCHING CHARACTERISTICS - WAVEFORMS**

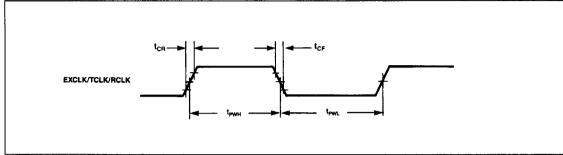

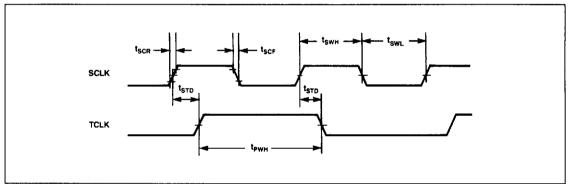

EXCLK/TCLK/RCLK Waveforms

SCLK - TCLK Relation Waveforms

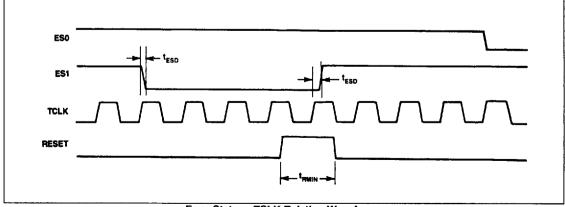

**Error Status - TCLK Relation Waveforms**

# **SWITCHING CHARACTERISTICS - WAVEFORMS (CONT'D)**

**Receive Timing Waveforms**

**Transmit Timing Waveforms**

# Line Interface Unit (LIU)

#### **SWITCHING CHARACTERISTICS**

(Vcc = 5.0 Vdc ± 5%, Vss = 0 Vdc, TA= 0°C to 70°C, unless otherwise specified)

| Parameter                             | Symbol            | Min. | Max. | Units | Notes |

|---------------------------------------|-------------------|------|------|-------|-------|

| Rise and Fall time                    |                   |      |      |       |       |

| RCLK, TCLK                            | tcR, tcF          | _    | 20   | ns    | 1     |

| SCLK                                  | tscr. tscr        | _    | 10   | ns    | 1     |

| EXCLK                                 | tcr, tcr          | _    | 30   | ns    |       |

| Rise and Fall time,                   |                   |      |      |       |       |

| TPOS, TNEG, RPOS, RNEG, BPV, ES0, ES1 | tpp, tpp          | _    | 60   | ns    |       |

| Delay Time                            |                   |      |      |       |       |

| TCLK (or RCLK) to RPOS, RNEG, BPV     | tD                |      | 80   | ns    |       |

| SCLK to TCLK                          | tstD              |      | 50   | ns    |       |

| TCLK to Error Status VALID            | tESD              |      | 80   | ns    |       |

| RESET Pulse Width                     | t <sub>RMIN</sub> | 200  | _    | μS    |       |

| T-1                                   |                   |      |      |       |       |

| Pulse Width, TCLK or RCLK Low         | tpwi              | 314  | 334  | ns    | 2     |

| Pulse Width, TCLK or RCLK High        | tpwH              | 314  | 334  | ns    | 2     |

| Pulse Width, SCLK Low                 | tswL              | 157  | 167  | ns    |       |

| Pulse Width, SCLK High                | tswn              | 157  | 167  | ns    |       |

| PCM30                                 |                   |      |      |       |       |

| Pulse Width, TCLK or RCLK Low         | tpwL              | 234  | 254  | ns    | 2     |

| Pulse Width, TCLK or RCLK High        | tpwh              | 234  | 254  | ns    | 2 2   |

| Pulse Width, SCLK or SCLK Low         | tswL              | 117  | 127  | ns    | ŀ     |

| Pulse Width, SCLK or SCLK High        | tswn              | 117  | 127  | ns    |       |

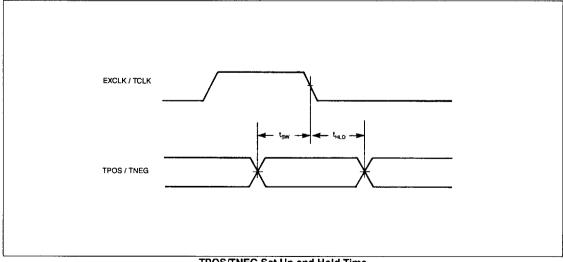

| Set Up and Hold time for EXCLK        |                   |      |      |       |       |

| TPOS, TNEG                            | tsw               | 150  |      | ns    |       |

| TPOS, TNEG                            | tHLD              | 150  | 1    | ns    |       |

- 1. TCLK, RCLK, and SCLK rise and fall times are defined as TTL levels.

- 2. The summation of tryuL and tryuH must meet the frequency specifications listed in the Interface Requirements table.

TPOS/TNEG Set Up and Hold Time

# Line Interface Unit (LIU)

#### **ABSOLUTE MAXIMUM RATINGS\***

| Symbol | Value             | Units |  |

|--------|-------------------|-------|--|

| Vcc    | -0.3 to +7.0      | Vdc   |  |

| Vin    | -0.3 to Vcc + 0.3 | Vdc   |  |

| TA     | 0 to +70          | °C    |  |

| TSTG   | -55 to +150       | °C    |  |

|        | Vcc<br>Vin<br>Ta  | Vcc   |  |

\*NOTE: Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the other sections of this document is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# ELECTRICAL OPERATING CHARACTERISTICS<sup>1</sup>

(Vcc = 5.0 Vdc ±5%, Vss = 0 Vdc, TA = 0°C to 70°C unless otherwise specified)

| Parameter                      | Symbol          | Min. | Тур. | Max.     | Units | Test Condition                    |

|--------------------------------|-----------------|------|------|----------|-------|-----------------------------------|

| Input Low Voltage              | VIL             | -0.3 | _    | +0.8     | V     |                                   |

| Input High Voltage             | V <sub>IH</sub> | +2.0 | _    | VCC +0.3 | ٧     |                                   |

| Output Low Voltage             | VoL             | _    | _    | 0.4      | V     | 1 <sub>LOAD</sub> = 1.6 mA        |

| Output High Voltage            |                 |      |      |          |       |                                   |

| TTL                            | Vor             | 2.4  | _    | _        | _     | I <sub>LOAD</sub> = -100 μA       |

| CMOS                           | _               | 3.5  | _    | _        | -     | $I_{LOAD} = -100 \mu A$           |

| Output Low Current             | loL             | +1.6 | _    | -        | mA    | VoL = 0.4V                        |

| Output High Current            | Тон             | -100 | -    | _        | μΑ    | V <sub>OH</sub> = 3.5V            |

| Input Capacitance              | CiN             | _    | -    | 5        | рF    |                                   |

| Power Dissipation <sup>2</sup> | PD              |      |      |          | mW    |                                   |

| T-1 Mode                       | _               |      |      |          |       |                                   |

| Transmit Random Data           |                 |      |      |          |       |                                   |

| 330 ft.                        |                 | _    | 270  | 305      |       |                                   |

| 655 ft.                        |                 | _    | 280  | 360      |       |                                   |

| Transmit All Ones              |                 |      |      |          |       |                                   |

| 330 ft.                        |                 | _    | 350  | 430      |       |                                   |

| 655 ft.                        |                 | _    | 410  | 480      |       |                                   |

| PCM30 Mode                     |                 |      |      |          |       |                                   |

| Transmit Random Data           |                 | _    | 240  | 280      |       |                                   |

| Transmit All Ones              |                 | _    | 310  | 360      |       |                                   |

| Power Consumption <sup>2</sup> | Pc              |      |      |          | mW    |                                   |

| T-1 Mode                       |                 |      |      |          |       |                                   |

| Transmit Random Data           |                 |      |      |          |       |                                   |

| 330 ft.                        | ļ               | _    | 300  | 375      |       |                                   |

| 655 ft.                        |                 | _    | 340  | 410      |       |                                   |

| Transmit All Ones              | İ               |      |      |          |       |                                   |

| 330 ft.                        |                 | _    | 420  | 500      |       |                                   |

| 655 ft.                        |                 | _    | 500  | 570      |       |                                   |

| PCM30 Mode                     |                 |      |      |          |       |                                   |

| Transmit Random Data           |                 | _    | 260  | 300      |       |                                   |

| Transmit All Ones              |                 | _    | 350  | 400      |       |                                   |

| Parametric Tests               |                 |      |      |          |       |                                   |

| Input High Current             | Тін             | -    | _    | 20       | μΑ    | Vcc = max., V <sub>IH</sub> = 2.0 |

| Input Low Current              | l IL            | -    |      | 20       | μΑ    | Vcc = max., V <sub>IL</sub> = 0.8 |

Notes: 1. Applies to all signals except TXOUTP, TXOUTN, RXINP and RXINN.

2. Power Consumption = Power dissipated in the device plus power delivered to the transmission line.

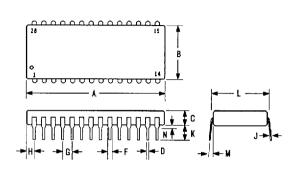

# PACKAGE DIMENSIONS

|        | Millir    | neters   | Inc       | hes   |  |

|--------|-----------|----------|-----------|-------|--|

| Dim.   | Min.      | Max.     | Min.      | Max.  |  |

| Α      | 36.58     | 37.08    | 1.440     | 1.460 |  |

| В      | 13.46     | 13.97    | 0.530     | 0.550 |  |

| С      | 3.56      | 4.06     | 0.140     | 0.160 |  |

| D      | 0.38      | 0.53     | 0.015     | 0.021 |  |

| F      | 1.40      | 1.65     | 0.055     | 0.065 |  |

| G      | 2.54 BSC  |          | 0.100 BSC |       |  |

| Н      | 1.65      | 2.16     | 0.065     | 0.085 |  |

| J      | 0.20      | 0.30     | 0.008     | 0.012 |  |

| K      | 3.05      | 3.56     | 0.120     | 0.140 |  |

| L      | 15.24 BSC |          | 0.600 BSC |       |  |

| М      | 7*        | 10*      | 7*        | 10°   |  |

| N      | 0.51      | 1.02     | 0.020     | 0.040 |  |

| Ref: I | D28P/G    | P00-D136 |           |       |  |

28-Pin Plastic DIP

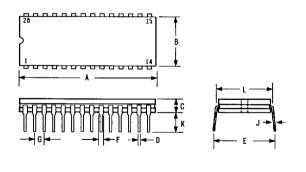

|        | Millir    | neters   | Incl      | nes   |

|--------|-----------|----------|-----------|-------|

| Dim.   | Min.      | Max.     | Min.      | Max.  |

| Α      | 36.32     | 37.34    | 1.430     | 1.470 |

| В      | 12.95     | 13.46    | 0.510     | 0.530 |

| С      | 3.68      | 4.19     | 0.145     | 0.165 |

| D      | 0.41      | 0.51     | 0.016     | 0.020 |

| E      | 16.26     | 17.27    | 0.640     | 0.680 |

| F      | 1.27      | 1.52     | 0.050     | 0.060 |

| G      | 2.54 BSC  |          | 0.100 BSC |       |

| J      | 0.20      | 0.30     | 0.008     | 0.012 |

| K      | 4.19      | 4.95     | 0.165     | 0.195 |

| L      | 15.24 BSC |          | 0.600 BSC |       |

| М      | 0°        | 10°      | 0"        | 10°   |

| Ref: F | PD28S/G   | P00-D310 |           |       |

28-Pin CERDIP

# Line Interface Unit (LIU)

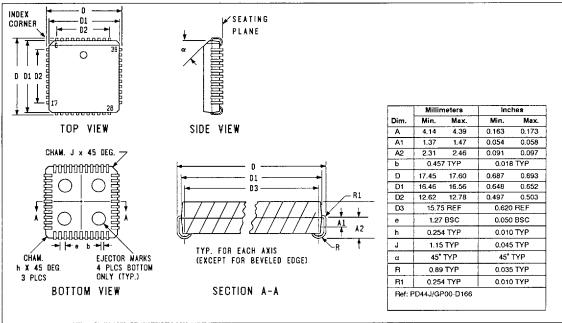

44-Pin PLCC

Information furnished by Rockwell International Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Rockwell International for its use, nor any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Rockwell International other than for circuitry embodied in Rockwell products. Rockwell International reserves the right to change circuitry at any time without notice. This document is subject to change without notice.

#### **ROCKWELL COMMUNICATION SYSTEMS** DIGITAL COMMUNICATIONS DIVISION REGIONAL SALES OFFICES

#### Headquarters

Digital Communications Division Rockwell International

(Physical Address) 4311 Jamboree Road Newport Beach, CA 92660-3095

### (Mailing Address) P.O. Box C Newport Beach, CA 92658-8902

(714) 833-4800 (800) 422-4230 (In CA) (800) 854-8099 (Outside CA) FAX: (714) 833-4078 or (714) 833-4391 TWX: (910) 591-1698

TLX: 170653 **United States**

Digital Communications Division Rockwell International 4311 Jamboree Road Suite 501-301 Newport Beach, CA 92660-3095 (714) 833-4655 FAX: (714) 833-6898

Digital Communications Division Rockwell International 2525 Meridian Parkway Suite 270 Durham, NC 27713 (919) 544-0087 FAX: (919) 544-1009

Rockwell International 9700 Koger Blvd. Suite 202 St. Petersburg, FL 33702 (813) 577-4750 FAX: (813) 577-1495

Digital Communications Division Rockwell International 2001 N. Collins Blvd. Suite 103 Richardson, TX 75080 (214) 996-6500 FAX: (214) 996-7812 TWX or TLX: (650) 227-9516

Digital Communications Division Rockwell International 1480 Renaissance Drive Suite 203 Park Ridge, IL 60068 (708) 297-8862 FAX: (708) 297-3230

Digital Communications Division Rockwell International 5001-B Greentree Executive Campus Route 73 Mariton, NJ 08053 (609) 596-0090 FAX: (609) 596-5681

#### U.S./E. Canada

Digital Communications Division Rockwell International 239 Littleton Boad Westford, MA 01886 (508) 692-7660 FAX: (508) 692-8185 TLX (MCI) 6502512464

U.S./W. Canada Digital Communications Division Rockwell International 3600 Pruneridge Avenue Suite 100 Santa Clara, CA 95051 (408) 249-9696 FAX: (408) 249-8518

Japan

Digital Communications Division

Rockwell International Japan Co., Ltd.

Sogo Hanzomon Bldg., 8F

Kojimachi 1-chome, Chiyoda-ku 7, Kojimachi 1-chome, Chiy Tokyo, Japan 102 (011-81-3) 3-265-8808 FAX: (011-81-3) 3-263-0639 TLX: J22198

Rockwell International 3600 Pruneridge Avenue Suite 100 Santa Clara, CA 95051 (408) 249-7112 FAX: (408) 249-7113

Digital Communications Division Rockwell International 30-332 Rutland Road Box Hill, Victoria 3128 Australia (61-3) 890-6999 FAX: (61-3) 898-6427 TLX: AA30450

Digital Communications Division Rockwell International Rm. 608 Leema Bldg. 146-1 Soosong-Dong Chongro-Ku K.P.O. Box 527 Seoul, Korea (Dent 553) (82-2) 720-7157 FAX: (82-2) 736-9124 TLX: RCIIK22710

Digital Communications Division Rockwell International Room 2808 International Trade Building 333 Keelung Road, Section 1 Taipei, Taiwan 10548, R.O.C. (886-2) 720-0282 FAX: (886-2) 757-6760 TLX: 26049 ENTTPE

Digital Communications Division Rockwell International GmbH Fraunhoferstrasse 11b D-8033 Muenchen-Martinsrie West Germany (49-89) 857-8016 FAX: (49-89) 857 57 93 TLX: 521-2650 rimd d

United Kingdom Digital Communications Division Rockwell International Ltd. Central House 3, Lampton Road Hounslow, Middlesex TW3 1HY England (44-81) 577-1034 FAX: (44-81) 570-0758

Digital Communications Division Rockwell International Tour GAN, 16 Place de l'Iris Cedex 13 92082 Paris La Defense 2. France (33-1) 49-06-39-80 FAX: (33-1) 49-06-39-90

South/Central America Digital Communications Division Rockwell International 4311 Jamboree Road P.O. Box C, MS 501-315 Newport Beach, CA 92660-3095 (714) 833-4532 FAX: (714) 833-4078 TWX: (910) 591-1698

Digital Communications Division Rockwell International Southwest Sales Office 4311 Jamboree Road Suite 501-301 Newport Beach, CA 92660 (714) 833-4655 FAX: (714) 833-6898