# 82258 ADVANCED DIRECT MEMORY ACCESS COPROCESSOR (ADMA)

- High Performance 16 Bit DMA Coprocessor for the 80386, 80286 and 80186 Families

- 8 MByte/sec Maximum Transfer Rate in 8 MHz 80286 Systems

- Four Independently Programmable Channels

- Multiplexor Channel Capability to Support Up to 32 Subchannels

- On Chip Bus Interface for the Whole 8086 Architecture

- **80286**

- --- 80186/188

- **--- 8086/88**

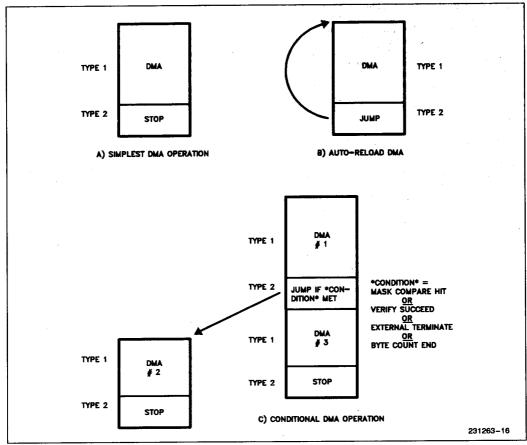

- Command Chaining for CPU Independent Processing

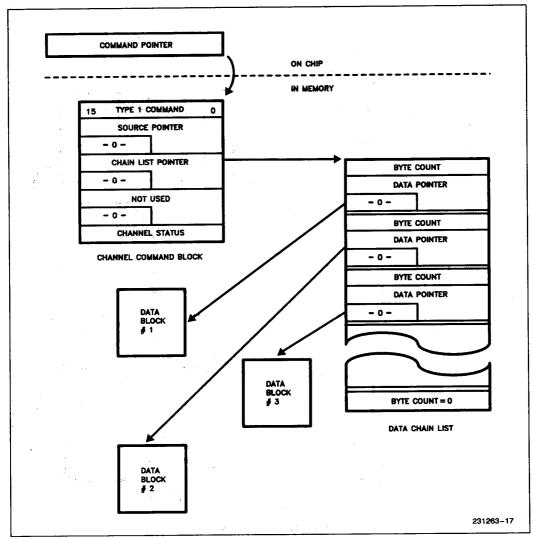

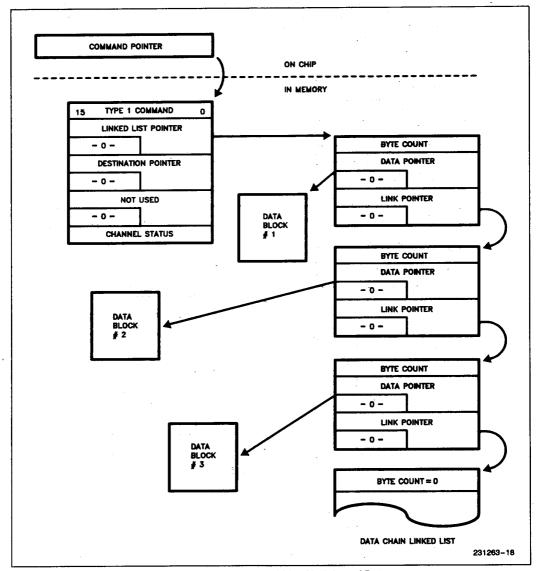

- Automatic Data Chaining for Gathering and Scattering of Data Blocks

- 16 MByte Addressing Range

- 16 MByte Block Transfer Capability

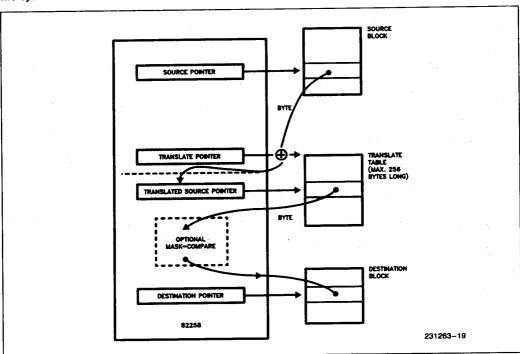

- "On the Fly" Compare, Translate and Verify Operations

- Automatic Assembly/Disassembly of Data

- **Programmable Bus Loading**

- 6 and 8 MHz Speed Selections

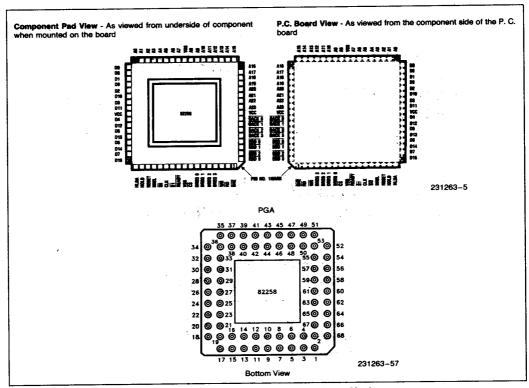

- Available in 68-Pin LCC and PGA Packages

(See Packaging Spec. Order #231369)

# INTRODUCTION

Intel's 82258, Advanced Direct Memory Access Coprocessor is a high performance, 16 bit DMA processor optimized for the 80286, 80186 and the 8086 families of CPUs and compatible with 80386 CPU. It has on-chip bus interface for the whole 8086 family architecture. Four high speed, independently programmable DMA channels can achieve a maximum cumulative transfer rate of 8 MByte/sec in an 8 MHz 8086/80186 systems. Channel 3 can be used as a Multiplexor channel, whereby, it supports 32 subchannels. This flexibility allows one to use a single DMA channel to handle a large number of slow and medium speed I/O devices. Advanced capabilities like Command and Data chaining and "On the fly" operations allow the 82258 to remove the I/O management load from the processor. The 82258 addresses the full 80286 CPU memory (16 MB for 80286), thus simplifying the system design. Automatic assembly/disassembly of data allows 16 bit processors to interface with common 8 bit peripherals and vice-versa. Remote mode of operation, where the 82258 has its own resident bus, allows modular system design. The 82258 complements the high performance, multitasking capabilities of the 80286.

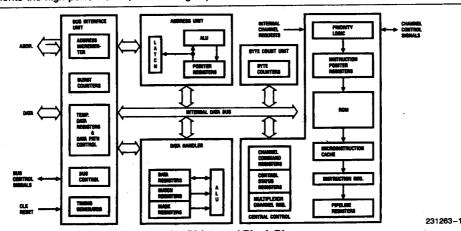

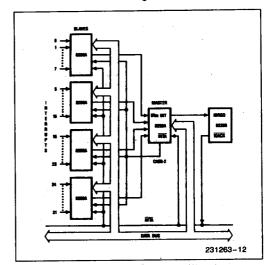

Figure 1. 82258 Internal Block Diagram

November 1987 Order Number: 231263-004

### **FABRICATION**

The 82258 is a 68 pin device, fabricated in Intel HMOS II technology. It is packaged in JEDEC type A hermetic leadless chip carrier and pin grid array.

# PIN DEFINITIONS AND FUNCTIONS

The 82258 has four operational modes

- 286

- 186—for the 80186/88 and the 8086/88 (Min. mode) CPUs

- 8086-for the 8086/88 (Max. mode) CPUs

- Remote

Pins of the 82258 have different definitions for different modes. 286 and remote modes have the same non-multiplexed bus structure and similar pin descriptions. Similarly, the 186 and the 8086 modes have multiplexed bus and similar pin description.

#### PINNING IN THE 286 MODE

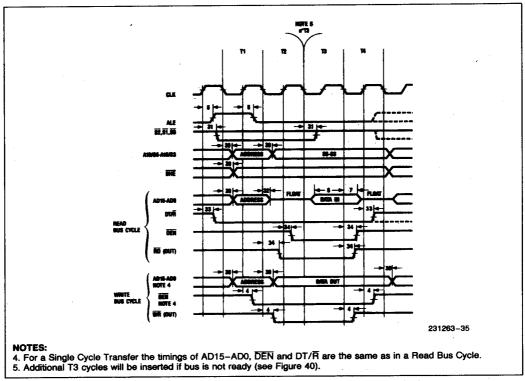

In the 286 mode, the bus signals and the bus timings of the 82258 are the same as those of the 80286 processor. The processor can access the internal registers of the 82258 and these accesses must be supported by the bus signals. Therfore, some of the bus control signals are bidirectional and some additional bus control signals are necessary.

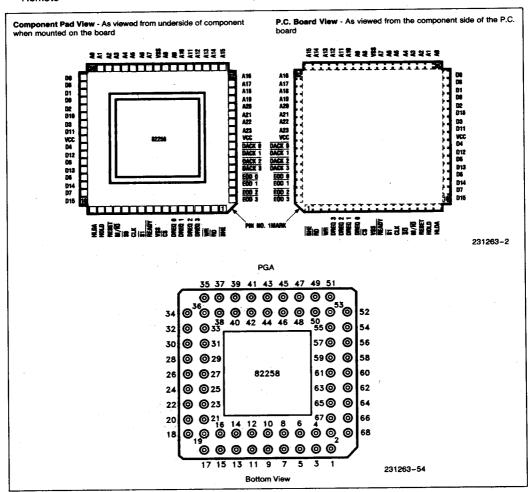

Figure 2. Pin Configuration in 286 Mode

Table 1. Pin Description for the 288 Mode (Also Contains Pins Identical in Other Modes)

| Table       |                                 |        | ING 255 MOC     | HE (AISO CO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | mains Pin   | ns Identical in Other Modes)                                            |  |

|-------------|---------------------------------|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------|--|

|             | Pin                             |        | Identical       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                                                                         |  |

| Symbol      | Type<br>input (i)<br>Output (0) | Number | in<br>Ali Modes | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |                                                                         |  |

| BHE         | 1/0                             | 1      | YES             | BUS HIGH ENABLE indicates transfer of data on the up byte of the data bus, D15-D8. Eight bit devices assigned the upper byte of the data bus would normally use BHE condition chip select function. BHE is active LOW and floats to Tri-State OFF when the 82258 does not own the bus.  BHE and A0 Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                                                                         |  |

|             |                                 |        |                 | BHE<br>Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A0<br>Value | Function                                                                |  |

|             |                                 |        |                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0           | Word Transfer (D15-D0) Byte Transfer on upper half of data bus (D15-D8) |  |

|             |                                 |        |                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0           | Byte Transfer on lower half of data<br>bus (D7-D0)                      |  |

|             |                                 |        |                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1           | Odd addressed byte on 8 bit<br>bus (D7-D0)                              |  |

| RD .        | l                               | 2      | NO              | READ command in conjunction with chip select (CS) enables reading out of the 82258 register, addressed by the address lines A7-A0. RD is an active LOW signal and is asynchronous to the 82258 clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |                                                                         |  |

| WR          | l                               | 3      | NO .            | WRITE command along with CS is used for writing into the 82258 registers. Wh is an active LOW signal and is asynchronous to the 82258 clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |                                                                         |  |

| DREQ3-DREQ0 |                                 | 4-7    | YES             | DMA REQUEST input signals are used for externally synchronized DMA transfers. If channel 3 is used as a Multiplexor channel, DREQ3 is defined as I/O Request (IOREQ) signal. These signals are active HIGH signals and are asynchronous to the 82258 clock. Unused DREQn lines should not be left floating, but should be tied inactive to VSS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                                                                         |  |

| CS          | I                               | 8      | NO              | CHIP SELECT is used to enable a processor to access the 82258 registers. This access is additionally controlled either by bus status signals or by the Read or Write command signals. CS is an active LOW signal, asynchronous to the 82258 clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |                                                                         |  |

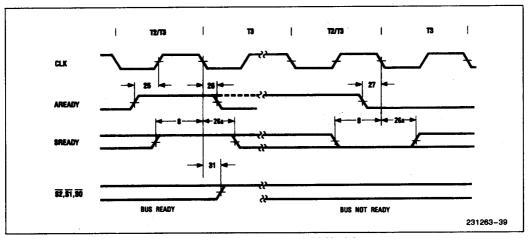

| READY       | I                               | 10     | NO              | BUS READY terminates a bus cycle. Bus cycles are extended without limit until terminated by an active READY. READY is an active LOW, synchronous input, requiring set up and hold times relative to system clock to be met for correct operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |                                                                         |  |

| S1, S0      | 1/0                             | 11,13  | YES             | BUS CYCLE STATUS signals control the support circuitry. The beginning of a bus cycle is indicated by \$\overline{S1}\$, or \$\overline{S0}\$, or both going active. The termination of a bus cycle is indicated by all the status signals going inactive in the 186 mode or the bus ready (READY) going active in the 286 mode. Both \$\overline{S0}\$ & \$\overline{S1}\$ are active LOW signals. \$\overline{S0}\$, \$\overline{S1}\$ along with \$\overline{S2}\$ (in the 186 mode) or M/\$\overline{IO}\$ (in the 286 mode) define the type of bus cycle. \$\overline{S2}\$ and M/\$\overline{IO}\$ have the same meaning but, in the 186 mode \$\overline{S2}\$ signal can be active only when at least one of \$\overline{S1}\$ and \$\overline{S0}\$ is active, whereas in the 286 mode the M/\$\overline{IO}\$ signal is valid with the address on address lines. |             |                                                                         |  |

Table 1. Pin Description for the 286 Mode (Also Contains Pins Identical in Other Modes) (Continued)

|        | Pin                             |                | Identical       |                                                                                                                                                                                                                                         |                              |                         |                                                                                        |  |

|--------|---------------------------------|----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------|----------------------------------------------------------------------------------------|--|

| Symbol | Type<br>Input (I)<br>Output (O) | Number         | In<br>All Modes |                                                                                                                                                                                                                                         |                              |                         |                                                                                        |  |

|        |                                 |                |                 |                                                                                                                                                                                                                                         | The 82258<br>82258 Loc       | Bus Cycle<br>al Bus Mas | Status Definitions<br>ster, All Signals (O))                                           |  |

|        |                                 | 1              | 1 4             | M/IO<br>or \$2                                                                                                                                                                                                                          | <u>\$1</u>                   | <u>50</u>               | Bus Cycle Initiated                                                                    |  |

|        |                                 | . •            |                 | 0                                                                                                                                                                                                                                       | 0                            | 0                       | Read I/O-Vector<br>(For Multiplexor channel)                                           |  |

|        | •                               |                |                 | 0                                                                                                                                                                                                                                       | 0                            | 1                       | Read from I/O space                                                                    |  |

|        |                                 |                |                 | o                                                                                                                                                                                                                                       | 1                            | Ó                       | Write into I/O space                                                                   |  |

|        |                                 |                |                 | 0                                                                                                                                                                                                                                       | 1                            | 1                       | None. (Does not occur in the 186 mode).                                                |  |

|        | 1                               | ļ <sup>*</sup> | 1               | 1 1                                                                                                                                                                                                                                     | 0                            | 0                       | None. (Does not occur)                                                                 |  |

| :      | 1                               | 1              | · ·             | 1                                                                                                                                                                                                                                       | . 0                          | 1                       | Read from memory space                                                                 |  |

|        | 1                               | 1              | 1               | ' '                                                                                                                                                                                                                                     | 1                            | Ö                       | Write into memory space                                                                |  |

|        | -                               |                |                 | 1                                                                                                                                                                                                                                       | 1                            | 1                       | None; not a bus cycle                                                                  |  |

| y tr   |                                 |                |                 | 1                                                                                                                                                                                                                                       |                              |                         | aster of the local bus, the<br>s for detection of                                      |  |

|        | ·                               |                | 1               |                                                                                                                                                                                                                                         | ous access                   |                         |                                                                                        |  |

|        | 1                               |                |                 | '                                                                                                                                                                                                                                       |                              |                         |                                                                                        |  |

| **     |                                 |                | ,               | ln ln                                                                                                                                                                                                                                   | terpretatio                  | on of the S<br>by the   | tatus and CS Signals<br>82258                                                          |  |

|        |                                 |                |                 |                                                                                                                                                                                                                                         | (822                         |                         | All Signais (I))                                                                       |  |

|        |                                 |                |                 | ĊS                                                                                                                                                                                                                                      | <u>\$1</u>                   | <u>\$0</u>              | Interpretation                                                                         |  |

|        |                                 | -              |                 | 1                                                                                                                                                                                                                                       | X                            | X                       | 82258 not selected<br>(No action)                                                      |  |

|        | ]                               |                |                 | 0                                                                                                                                                                                                                                       | 0                            | 0                       | No 82258 access<br>(No action)                                                         |  |

|        | 1                               |                |                 | 0                                                                                                                                                                                                                                       | 0                            | 1 1                     | Read from an 82258 register                                                            |  |

|        |                                 |                |                 | 0                                                                                                                                                                                                                                       | 1                            | 0                       | Write into an 82258 register                                                           |  |

|        | 1                               |                |                 | ō                                                                                                                                                                                                                                       | 1                            | 1                       | Not a bus cycle*                                                                       |  |

|        |                                 |                |                 | activated.                                                                                                                                                                                                                              |                              | 3 monitors              | synchronous access is<br>RD and WR signals for<br>access.                              |  |

| CLK    | 1                               | 12             | NO              | SYSTEM CLOCK provides the fundamental system timing, is divided by two to generate the 82258 internal clock. CLK an active HIGH signal which can be connected directly to the 82284 CLK output. The internal divide-by-two circuitry is |                              |                         |                                                                                        |  |

|        |                                 |                |                 | HIGH transition                                                                                                                                                                                                                         | nsition on the<br>on the Sta | ne RESET<br>tus Input S | ock generator by a LOW to input, or by first HIGH to LOW or \$1 after RESET.           |  |

| M/IO   | 0                               | 14             | NO              | I/O space                                                                                                                                                                                                                               | addresse                     | s.                      | ishes between memory and                                                               |  |

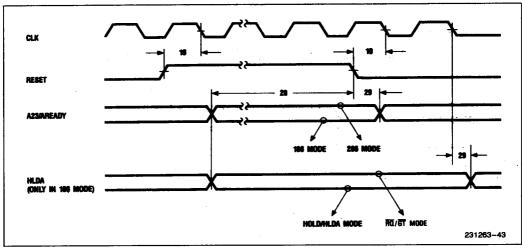

| RESET  | 1                               | 15             | YES             | is an activ                                                                                                                                                                                                                             | /e HIGH siç                  | nal and m               | 258 to the initial state. RESET ust be synchronous to the ctivated for at least 16 CLK |  |

Table 1. Pin Description for the 286 Mode (Also Contains Pins Identical in Other Modes) (Continued)

| 1,500           | Pi                                     |                 | Identical       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-----------------|----------------------------------------|-----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol          | Type<br>Input (I) Number<br>Output (O) |                 | in<br>All Modes | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

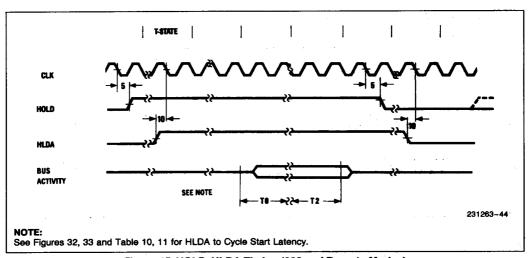

| HOLD<br>HLDA    | 0<br>1                                 | 16<br>17        | NO              | BUS HOLD REQUEST AND HOLD ACKNOWLEDGE control ownership of the local 82258 bus. When active,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                 |                                        |                 |                 | HOLD indicates a request for the control of the local bus. HOLD goes inactive when the 82258 relinquishes the bus. HLDA, when active, indicates that the 82258 can acquire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                 |                                        |                 |                 | the control of the bus. When HLDA goes inactive, the 82258 must relinquish the bus at the end of its current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                 | -                                      | -               |                 | cycle. HLDA may be asynchronous to the system clock.<br>Both HOLD and HLDA are active HIGH signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| D15-D0          | 1/0                                    | 18-25,<br>27-34 | NO              | DATA BUS is the bidirectional 16 bit bus. For use with an 8 bit bus, only the lower 8 data lines D0-D7 are relevant. The data bus is active HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| A0-A7           | 1/0                                    | 35-42           | NO              | ADDRESS LINES A0-A7 are the lower 8 address lines for DMA transfers. They are also used to input the register address when the processor accesses an 82258 register. All lines are active HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| A8-A23          | 0                                      | 44-59           | NO .            | ADDRESS LINES A8-A23 form the remainder of the 82258 address bus. Address bus is active HIGH. Pln A21 must have a pull-up resistor (n 10k Ω) connected to it to ensure that it is high during reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

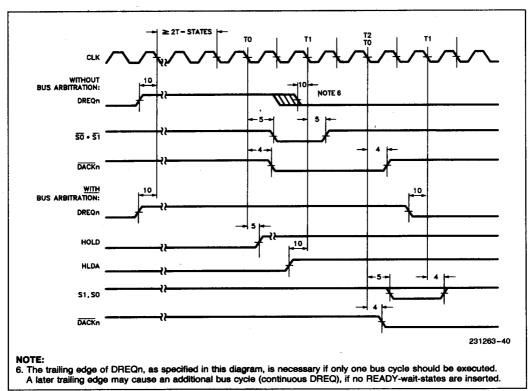

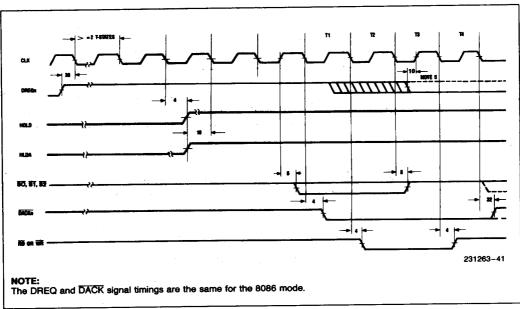

| DACKO-DACK3     | 0                                      | 61-64           | YES             | DMA ACKNOWLEDGE signal acknowledges the requests of the corresponding DREQ signal. DACKi goes active when the requested transfers are performed on the channel i in response to a DREQi. If channel 3 is in the multiplexor mode, DACK3 is defined as I/O acknowledge (IOACK). These signals are active LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

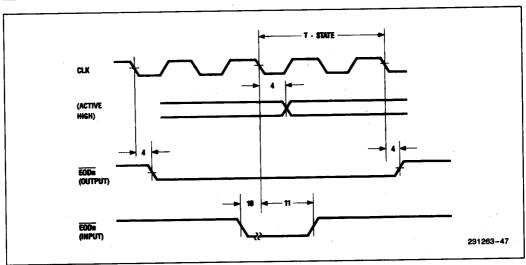

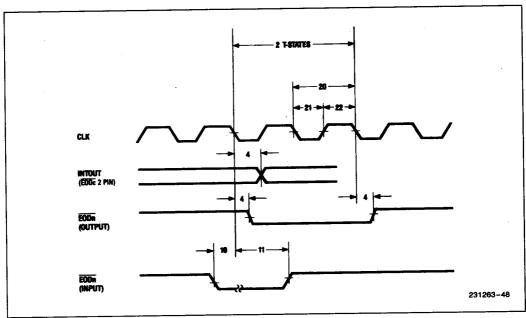

| EODO-EOD3       | 1/0                                    | 65-68           | YES             | END OF DMA signals are open drain drivers with internal high impedance pull up resistors (an external pull-up resistor is required) and can be used as quasi-bi-directional lines. These signals are active LOW.  As OUTPUTs the signals are activated (if enabled) for two T-STATE cycles at the end of the DMA transfer of the corresponding channel or they are activated under program control (End of DMA output or interrupt output). EODs acts as "End of DMA" level triggered INPUTs if the signals are held high internally but forced low by the external circuitry for at least 250 ns. The current transfer is aborted and the 82258 continues with the next command. EOD2 can also be used as a common active high interrupt signal (INTOUT) for all four channels. In this mode, this signal is a push-pull output and not an open drain output. Other EODi pins may still be used in their regular I/O mode. |  |  |  |

| V <sub>SS</sub> | 1                                      | 9, 43           | YES             | SYSTEM GROUND: 0 Volt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| V <sub>CC</sub> | i                                      | 26, 60          | YES             | SYSTEM POWER: +5V Power Supply Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

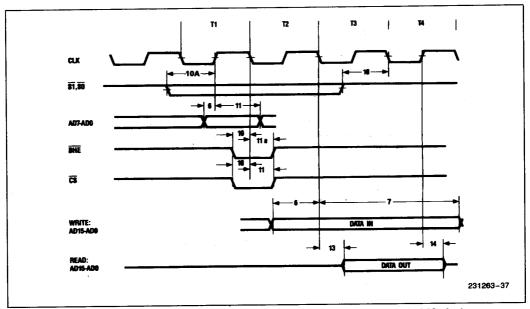

#### PINNING IN THE 186 MODE

The 80186 has a multiplexed bus structure. Therefore, many 82258 pins have different meaning in the 186 mode than in the 286 mode. Since the 80186 has 20 address lines compared to 24 for the 80286, the 4 extra lines are used to generate additional bus control signals. The following table gives the details of pins having different meaning in the 186 mode compared to the 286 mode:

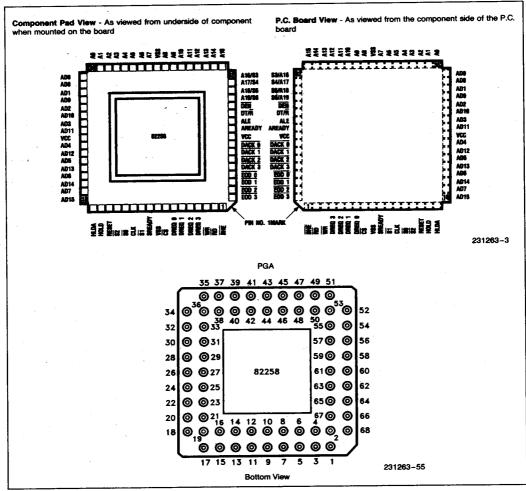

Figure 3. Pin Configuration in the 186 Mode

Table 2. Changes in Pin Description in the 186 Mode: (Compared to the 286 Mode)

|                             | Pir                             | )                                |                                                                                                                                                                                                                                                                          |                                                                                                                                                        |                                                                                                                                                                                  |  |  |  |  |

|-----------------------------|---------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol                      | Type<br>Input (i)<br>Output (O) |                                  | Functions                                                                                                                                                                                                                                                                |                                                                                                                                                        |                                                                                                                                                                                  |  |  |  |  |

| RD, WR                      | 1/0                             | 2, 3                             | READ, WRITE In the 186 mode, the RD & WR pins are used additionally as output pins to support the 80186 or the 8086 minimum systems. These signals are active LOW.                                                                                                       |                                                                                                                                                        |                                                                                                                                                                                  |  |  |  |  |

| ALE                         | 0                               | 58                               | the address inforn                                                                                                                                                                                                                                                       | ADDRESS LATCH ENABLE signal provides a strobe to separate the address information on the multiplexed address-data lines. ALE is an active HIGH signal. |                                                                                                                                                                                  |  |  |  |  |

| DEN                         | 0 ·                             | 56                               | <b>DATA ENABLE</b> s<br>8286/8287. <b>DEN</b>                                                                                                                                                                                                                            |                                                                                                                                                        | enabling the data transceiver,<br>/ signal.                                                                                                                                      |  |  |  |  |

| DT/Ā                        | 0                               | 57                               | DATA TRANSMIT/RECEIVE signal controls the direction of data flow through the external data bus transceiver, depending on whether a read, or a write bus cycle is performed. This pin must have a pullup resistor connected to it to ensure that it is high during reset. |                                                                                                                                                        |                                                                                                                                                                                  |  |  |  |  |

| SREADY                      |                                 | 10                               | externally. Use of specification by el                                                                                                                                                                                                                                   | this pin permits<br>iminating the clo                                                                                                                  | gnal must be synchronized<br>a relaxed system and timing<br>ock phase, required for resolving<br>DY input. SREADY is an active                                                   |  |  |  |  |

| CLK                         | 1                               | 12                               | SYSTEM CLOCK input gets a prescaled signal from the 186 clock (CLKOUT) or the 8086 clock (50% duty cycle for 186 and 33% duty cycle for 8086). No internal prescaling is done. CLK is an active HIGH signal.                                                             |                                                                                                                                                        |                                                                                                                                                                                  |  |  |  |  |

| <u>\$2</u>                  | 0                               | 14                               | STATUS SIGNAL along with \$\overline{50}\$ and \$\overline{51}\$ provides the bus cycle description (for details see 286 mode pin description of \$\overline{50}\$ and \$\overline{51}\$).                                                                               |                                                                                                                                                        |                                                                                                                                                                                  |  |  |  |  |

| AD0-AD15<br>A0-A7<br>A8-A15 | 1/0<br>1/0<br>0                 | 18-25<br>27-34<br>35-42<br>44-51 | ADDRESS/DATA BUS signals AD0-AD15 contain multiplexed lower address and data information. Also, the demultiplexed address information is available on address pins A0-A15.                                                                                               |                                                                                                                                                        |                                                                                                                                                                                  |  |  |  |  |

| A16/S3-A19/S6               | 0                               | 52-55                            | information on the<br>Signals S5 and S6<br>cycle. During an a<br>low. Low S6 implie                                                                                                                                                                                      | bus cycle. These provide information bus cycle, as a processor bus                                                                                     | ultiplexed with additional status<br>se pins are active HIGH.<br>ation on the status of the bus<br>S6 is always high and S5 always<br>us cycle.<br>el number for the running bus |  |  |  |  |

|                             |                                 |                                  | S4                                                                                                                                                                                                                                                                       | S3                                                                                                                                                     | Channel Number                                                                                                                                                                   |  |  |  |  |

|                             |                                 |                                  | 0<br>0<br>1<br>1                                                                                                                                                                                                                                                         | 0<br>1<br>0<br>1                                                                                                                                       | 0<br>1<br>2<br>3                                                                                                                                                                 |  |  |  |  |

| AREADY                      | I                               | 59                               | ASYNCHRONOU<br>The rising edge is                                                                                                                                                                                                                                        | S READY is an internally synchter the 82258 int                                                                                                        | asynchronous bus ready signal.<br>ronised. During reset, AREADY<br>to the 186 mode. AREADY is an                                                                                 |  |  |  |  |

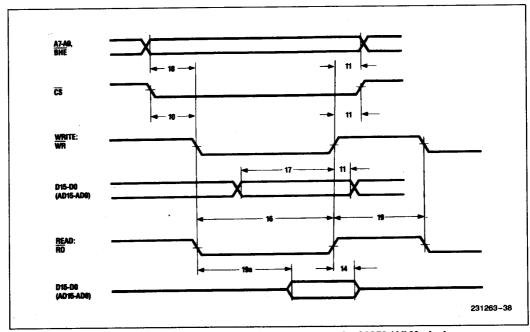

# PINNING FOR THE 8086 MODE

For the 8086 MIN configuration the pinning is identical to the 186 mode. For the 8086 MAX configuration, the bus arbitration is done via the RQ/GT protocol. Otherwise, the function of pins is identical to the 186 mode.

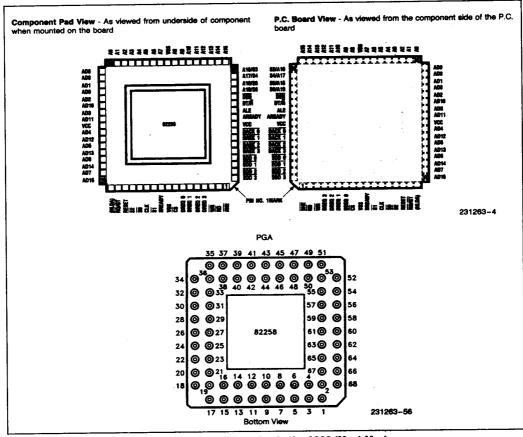

Figure 4. Pin Configuration in the 8086 (Max) Mode

Table 3. Changes in Pin Description in the 8086 (Max) Mode (Compared to the 186 Mode)

|        | Pir                         | 1  | ·                                                                                                                                                                                                  |  |  |

|--------|-----------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol | Input (I) Number Output (O) |    | Functions                                                                                                                                                                                          |  |  |

| RQ/GT  |                             |    | REQUEST/GRANT implements a one line communication protocol to arbitrate the use of the system bus; normally done via HOLD/HLDA. RQ/GT is an active LOW signal having an internal pull-up resistor. |  |  |

| HLDA   | 1                           | 17 | HOLD ACKNOWLEDGE has no meaning in the 8086 (Max) mode. It should be tied high for mode recognition during reset.                                                                                  |  |  |

#### PINNING IN THE REMOTE MODE

In the remote mode, most of the signals have the same function as in the 286 mode. Exceptions are noted in the following table:

Figure 5. Pin Configuration in Remote Mode

Table 4 Changes in Pin Description in the Remote Mode (Compared to the 286 Mode)

|              | Pin                             |          |                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|--------------|---------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol       | Type<br>Input (I)<br>Output (O) | Number   | Functions                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

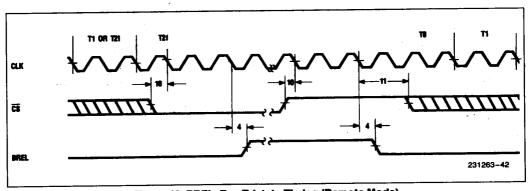

| CS           | 1                               | 8        | CHIP SELECT has two functions in the remote mode. As in the 286 mode, CS enables access to the 82258 internal registers. In addition CS works as an Access Request Input. When forced LOW, it signals to the 82258 that another bus master needs access to the local bus of the 82258. The 82258 releases the bus as soon as possible and signals it to the CPU by activating BREL (Bus Release) output. CS is an active LOW signal. |  |  |  |

| BREL         | 0                               | 14       | BUS RELEASE signal is used to indicate when the 82258 releases control of the resident bus.                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| HOLD<br>HLDA | 0                               | 16<br>17 | HOLD & HOLD ACKNOWLEDGE signals are used only for access to the system bus. They are connected to the bus arbiter (i.e., 82289). Resident bus accesses are directly executed without the HOLD/HLDA sequence.                                                                                                                                                                                                                         |  |  |  |

# **FUNCTIONAL DESCRIPTION**

The 82258 is an advanced DMA coprocessor for the 8086 family architecture. In addition to providing high speed DMA transfers (8 MByte/sec in an 8 MHz 80286 and 4 MByte/sec in 8 MHz 80186/86 systems), the 82258 takes I/O processing load off the CPU, thus improving overall system performance. The 82258 has advanced features not found in the previous generation DMA controllers: multiple-xor channel, command & data chaining and 'on the fly' data manipulation operations.

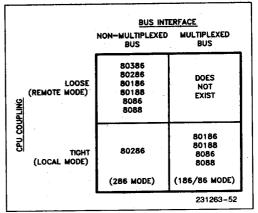

#### MODES OF OPERATION

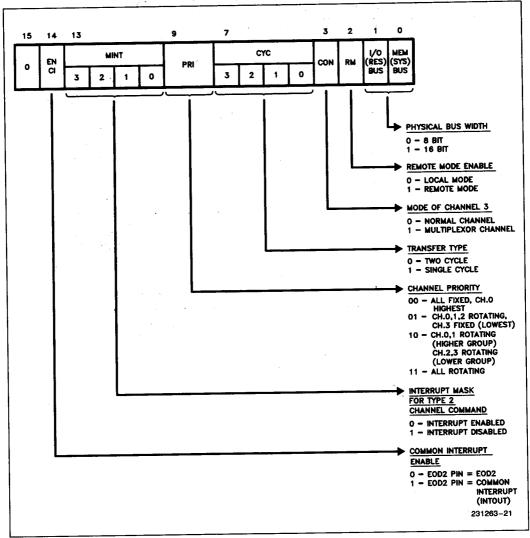

The 82258 has a number of different modes of operation based upon its coupling with the CPU (tight or loose) and its adaptive on-chip bus interface (the 286 bus or the 186 bus).

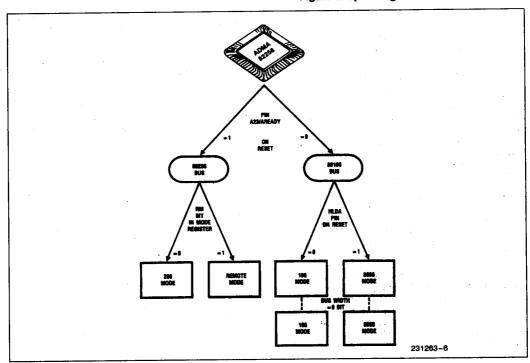

Figure 6 shows the different operating modes of the 82258 and the CPUs it can interface with in those modes. Figure 7 shows how to configure the 82258 into these different modes.

#### LOCAL MODE

In this mode the 82258 shares the local bus and all the support/control devices with the CPU. Because of its on-chip bus interface, the 82258 can be directly coupled to the whole 8086 family of microprocessors.

Figure 6. Operating Modes for the 82258

Figure 7. Selecting Modes of Operation

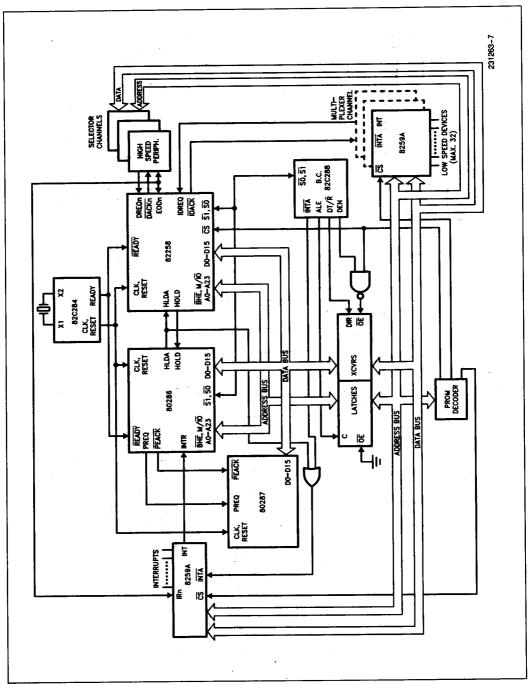

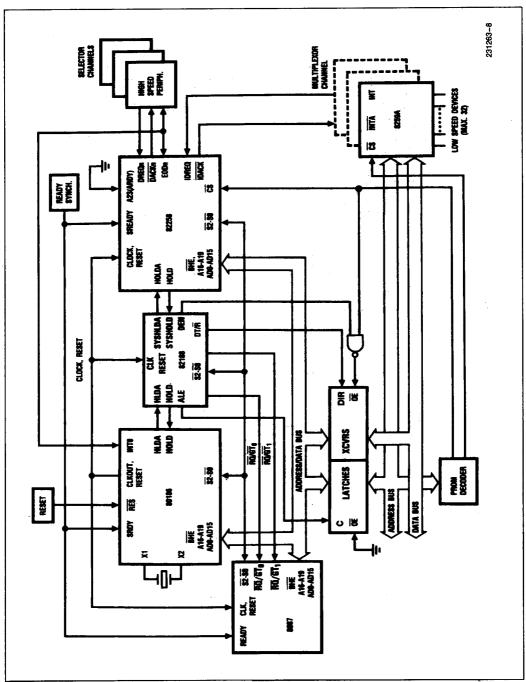

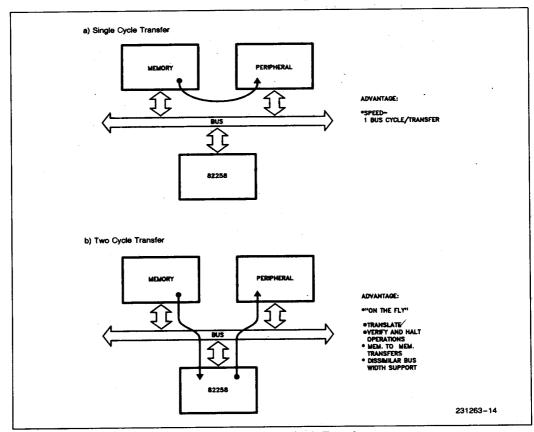

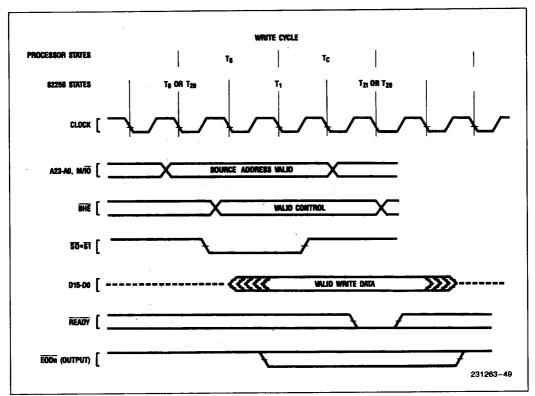

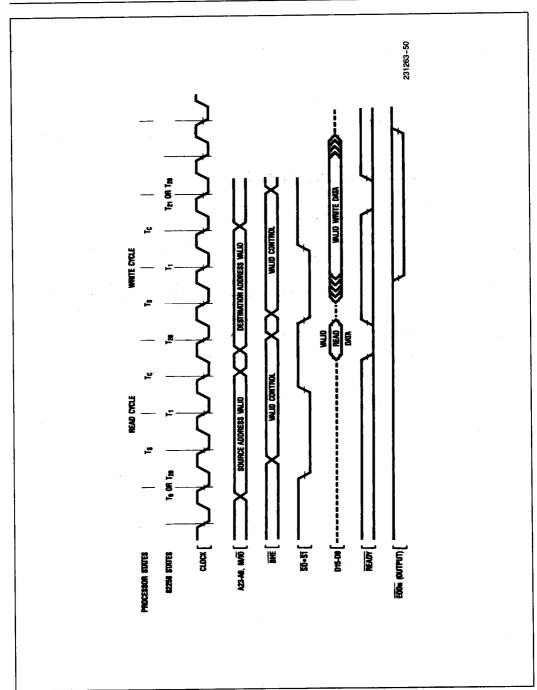

#### 286 System

The configuration in Figure 8 shows the 82258 in the local mode (286 mode) in an 80286 system which includes the Numeric Processor Extension, 80287. The 286 mode is selected during reset (Figure 7). In this mode the 82258 supports the non-multiplexed, pipelined 286 bus. The DMA coprocessor resides on the processor's local bus (physical pins of the 80286) and shares all the support circuits: latches, tranceivers, bus controller and arbiter, clock generator etc. By residing on the 286 bus, the 82258 achieves maximum data transfer rate; up to 8 MByte/sec at 8 MHz for single cycle transfer. HOLD/ HLDA protocol is used for bus exchange between the 80286 and the 82258. The 82258 can be programmed to handle both internal and external terminate conditions. Internal termination is programmed in the command block (in type 2 command as explained later). External termination is handled by the EOD (end of DMA) pins if they are enabled. Interrupts for the CPU are handled by an interrupt controller (e.g. 8259A) which receives the end of DMA pins (EOD 0-3) as interrupts. The multiplexor channel uses external 8259As to prioritize and arbitrate service requests between peripherals (Figure 13).

To link this system to the MULTIBUS® bus architecture another set of latches, tranceivers, bus controllers and a bus arbiter (i.e., 82289) as shown in Figure 11 (for remote mode configuration) are needed.

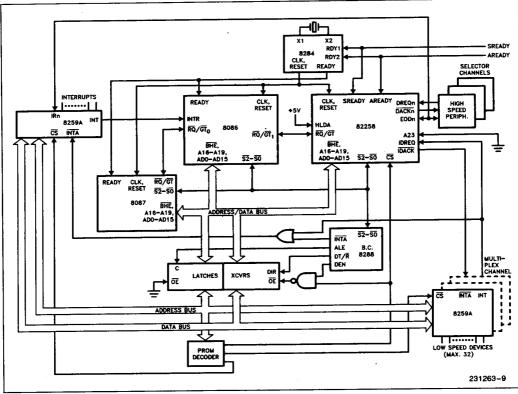

#### 186/188 (8086/8088 Min) Systems

The 82258 can be configured into the 186 mode during reset (Figure 7). In this mode it supports the 80186 and the 8086 (Min) processors. It can be programmed to support the 80188 and the 8088 (Min) by programming the bus width in General Mode Register (GMR). Figure 9 shows the 82258 used in an 80186 system containing the 8087 numeric coprocessor. This system uses the 8086 bipolar support components: latches, transceivers and the bus controller (82188) links the 80186 to the 8087. The 82188 is also used to support the 82258, since the 80186 has only one set of bus exchange signals (HOLD/HLDA). An interrupt controller (8259A) processes the EOD signals for the CPU.

In the 186 mode, the 82258 directly supports the 80186/ 8086 bus with 16 address bits internally multiplexed into the data lines (AD15-AD0). The address pins A19-A16 are multiplexed with the status lines S6-S3. The address pins A22-A20 (in the 286 mode) are used to generate the control signals ALE,  $\overline{\rm DEN}$  and  $\overline{\rm DT/R}$  (in the 186 mode). The A23 pin (in the 286 mode) serves as an asynchronous ready input AREADY (in the 186 mode). As a master in the 186

mode, the 82258 offers address lines A15-A0 as latched outputs and shares all the 186/8086 support components with the processor.

也是一个人,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们就是一个人的,我们

### 8086/88 Systems

The 82258 is configured into the 8086 mode during reset (Figure 7). In this mode the 82258 supports 8086/88 in the maximum mode and uses the RQ/GT protocol for the processor - DMA coprocesor bus exchange. The 8087 can be supported in the system without requiring the integrated bus controller, 82188. To support the 8088 system in the maximum mode, the General Mode Register is programmed for 8 bit bus width. Figure 10 shows the 82258 in an 8086 system containing the 8087. The system configuration is very similar to the 80186 system in Figure 9.

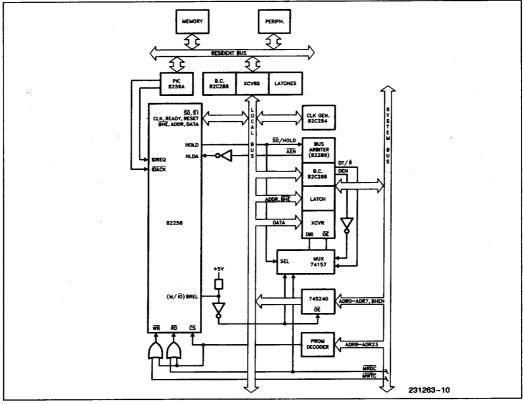

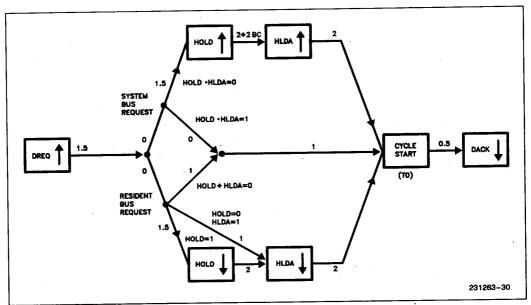

#### REMOTE MODE

The 82258 is configured to be in the Remote Mode (Figure 7) by programming the General Mode Register (RM bit), after putting the 82258 in the 286 mode during the reset. The 82258 has the bus timings and signals compatible to the 286 bus.

In the remote mode, the ADMA can access two 16 MByte address spaces normally called the resident space and the system space. The ADMA does not distinguish between accessing an I/O device and accessing a memory in the remote mode, so either peripheral or memory can belong to either of the two spaces.

In the remote mode, the 82258 is the sole local bus (resident bus) master and interfaces to the processor through the system bus (using a bus arbiter). Therefore, the 82258 can work in parallel with the processor. The remote mode is useful for a modular I/O subsystem.

Figure 11 shows the 82258 configured in the remote mode of operation. The peripherals interface to the 82258 on the resident bus. The resident bus components are similar to the ones used for the 286 system. Additional support components are used to interface the 82258 to a system bus e.g. the MULTIBUS. The 82258 communicates with the CPU (80286) over the system bus.

Since the 82258 is the only master of the local/resident bus, it can start the local bus cycles without any bus arbitration. For system bus accesses, a dead-lock can arise if:

- The 82258 occupies the local bus to gain access to the system bus and

- The CPU (80286) occupies the system bus to gain access to the 82258 (through its local bus)

Figure 8. 80286 in an 80286 System 3-93

Figure 9. 82258 in an 80186 System 3-94

Figure 10. 82258 in an iAPX 86 System

To prevent this deadlock, for the system bus accesses the 82258 does not occupy the local bus until it has the system bus. Therefore, in the remote mode, the 82258 initiates all system bus accesses (and only these) through the HOLD/HLDA protocol. The local bus arbitration (for the CPU) is done through the  $\overline{\text{CS}}$  and the BREL lines.

#### **COMMUNICATION MECHANISMS**

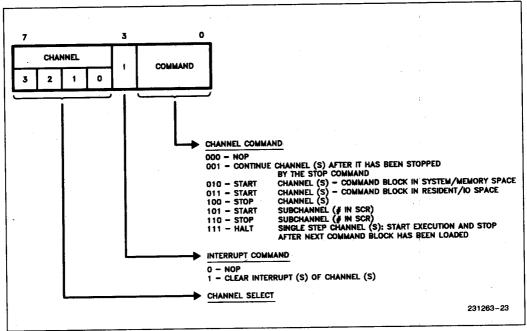

#### CPU → 82258 COMMUNICATION

Communication from the CPU to the 82258 is two-fold:

- Some 82258 registers receive the main commands from the CPU, through the slave interface of the 82258. Access to the 82258 is either synchronous (using CS, S1, S0) or asynchronous (using CS, RD, WR; S1 = S2 = 1).

- Most of the data is transferred via the control space in the memory in terms of organization blocks e.g. command blocks and multiplexor ta-

ble. Control space can lie in the memory space or the memory mapped I/O space (system or resident space for the remote mode) and can be dynamically changed with every start channel command.

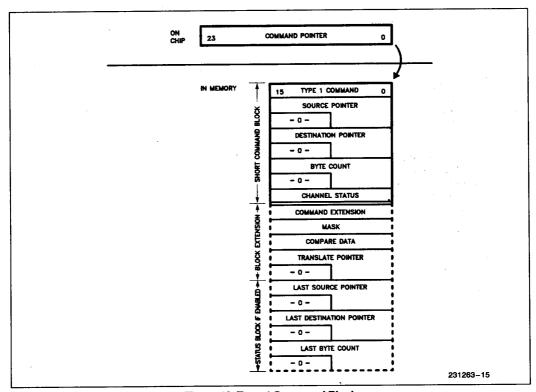

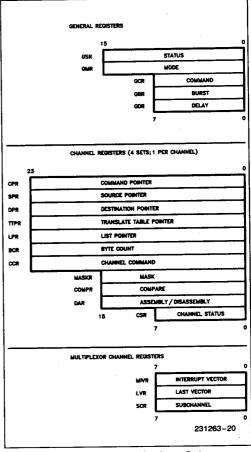

The CPU communicates with the 82258 by depositing data in the memory and into the on-chip registers of the 82258. The CPU can access the 82258 general registers and status registers, and can start a channel by writing the proper command to the general command register (GCR). The 82258 will then read the data from the memory command block and set itself up.

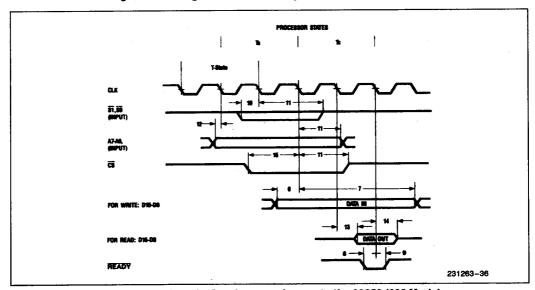

#### Slave Interface

The slave interface of the 82258 is used by the CPU to access the 82258 internal registers. Although most of the CPU to 82258 communication is done through memory based data blocks, some direct accesses to the 82258 registers are necessary. For example, during the initialization phase the general

Figure 11. 82258 in Remote Mode

mode register (GMR) must be written to set up the 82258 or, to start a channel the command pointer registor (CPR) and the general command register (GCR) must be loaded. During the system debugging phase, access to the 82258 internal registers is very important.

The slave interface is enabled by the  $\overline{\text{CS}}$  input and consists of the following lines:

ST, SO —Status Lines (inputs)

RD, WR —Control Lines (inputs)

A7-A0 —Register Address (inputs)

D15-D0 —Data Lines (inputs/outputs)-(for the 286 and the remote modes)

AD15-AD0 —Address/Data Lines (inputs/outputs)-(for the 186 and 8086 modes)

In the 286 mode and the 186/86 mode, two types of accesses are possible:

- synchronous access through the status lines SI and SO

- Asynchronous access using RD and WR

The register address must be supplied on the address pins A7-A0, except for the synchronous access in the 186/86 mode. Address data lines AD7-AD0 are used for the register address information in case of a synchronous access in the 186/86 mode.

In the remote mode, a synchronous access is not possible as the 82258 has to release its local bus to enable the CPU to access its registers. On receiving an access request (CS input asserted), the 82258 releases the local bus as soon as possible and signals it by asserting the BREL line. Only then, can the CPU access the 82258 registers.

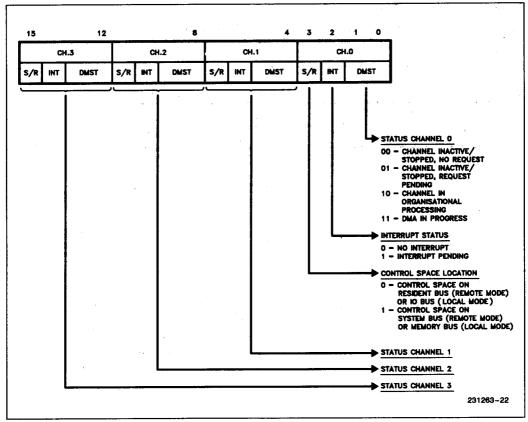

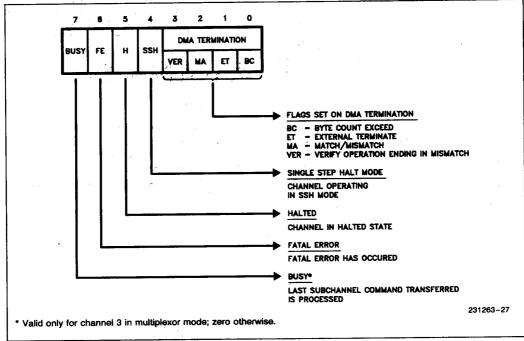

### 82258 → CPU COMMUNICATION

The 82258 to the CPU communication is also two-fold:

Hardware based communication, using one or more EOD lines as interrupt request lines to the CPU. The CPU can then read the status registers

(and the interrupt vector register for the multiplexor channel) and service the interrupt.

— Control space based communication: At the end of a DMA transfer, the 82258 writes the contents of the appropriate channel status register into the channel command block. Additionally, it may transfer some other information (e.g. the updated source pointer) into the command status block.

The 82258 updates its internal registers (e.g. the channel command pointer, the general status register etc.) for any CPU access.

#### 82258 — PERIPHERAL COMMUNICATION

The DMA interface of the 82258 is used for its communication with the peripherals. It consists of three signal lines:

DREQ —DMA Request

DACK —DMA Acknowledge

EOD -End of DMA

DREQ and DACK control the externally synchronized DMA transfers. A burst of data is transferred for a continuous DMA request, as long as the request signal is active.

EOD lines, which are quasi-bidirectional, enhance the 82258—Peripheral communication link. First these can be used as inputs to the 82258 to receive an asynchronous external terminate signal to terminate a running DMA. As outputs, they can be used to interrupt the CPU and/or to signal a specific status to the peripheral (e.g. transfer aborted or, end of a block or, send/receive next block..). In addition, the EOD output of channel 2 can be used as a collective interrupt output (INTOUT) for all the DMA channels while the other three EOD lines retain their normal function.

An EOD output signal can be generated synchronous to a synchronising device at the last data transfer or, synchronous to the internal clock at the last destination cycle. An EOD can also be generated asynchronously through a Type 2 command.

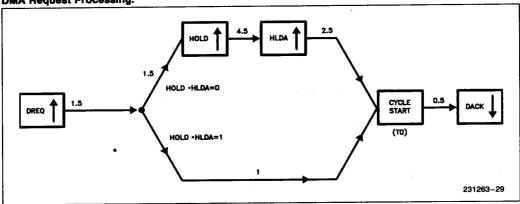

#### **BUS ARBITRATION**

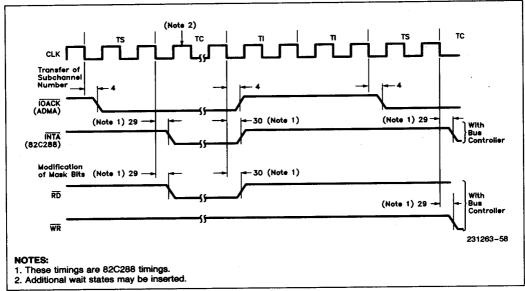

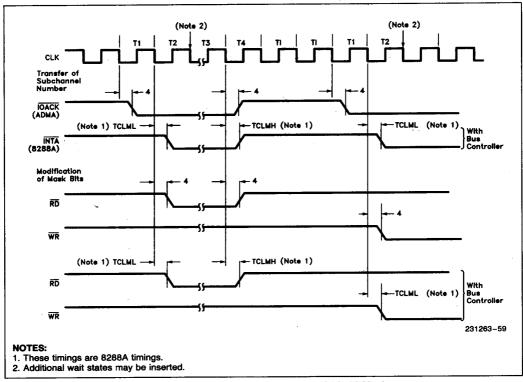

#### **HOLD/HLDA Sequence**

These signals are used for the bus arbitration in the 286 mode and the 186/88 (8086/88 Min.) mode. Whenever the 82258 needs the bus, it activates the HOLD signal and the processor surrenders the local bus as soon as possible by asserting HLDA. The 82258 performs the transfer and switches the HOLD to low. The processor takes the bus and switches

the HLDA to low. To force the 82258 to surrender the bus, the HLDA must be set to low. The 82258 will release the bus after the currently running bus cycle or the unseparable bus cycles. Unseparable bus cycles are:

- The two IO acknowledge bus cycles for the 8259A PIC.

- Word transfers on odd boundary addresses, realised by two bus cycles where each transfer is a byte.

- Fetch of 24 bit address pointers out of the memory or restore of the pointers.

- Read- modify- write the 8259A mask registers.

The 82258 signals the surrendering of the bus by floating the bus and removing the HOLD signal. If requests for bus cycles are present, the HOLD will go active after a delay of two T-states.

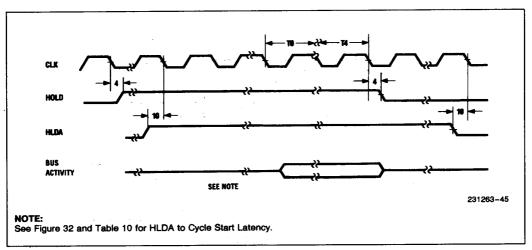

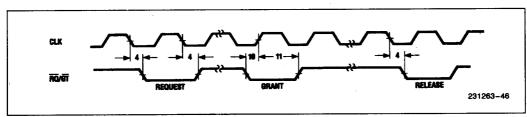

#### RQ/GT Sequence

RQ/GT protocol is used for the 8086/88 (Max.) Mode. The 82258 requests the bus by sending a request pulse of one CLK period length, via the RQ/GT signal, to the processor. The processor acknowledges it with a pulse on the same line. Then the 82258 controls the bus. When surrendering the bus, it sends a release pulse on the RQ/GT line.

#### **CS/BREL Sequence**

This is used in the remote mode along with the HOLD/HLDA signals. HOLD/HLDA are used for system bus arbitration and CS/BREL for local bus arbitration (to allow the CPU to access the 82258 registers or the resident bus). The CPU asserts the CS signal to ask for the local bus and the 82258 releases the bus as soon as possible by activating BREL. After the CPU has completed its access, it should set CS high. The 82258 deactivates BREL and proceeds with its own bus cycles on the local bus.

#### NOTE:

When the 82258 is not in possession of the bus, all output signals are tristated except the following:

HOLD (except in the RQ/GT protocol), DACK0-DACK3, EOD0-EOD3,

BREL (remote mode) and ALE (186 mode)

#### CHANNEL CONFIGURATION

The 82258 has four independently programmable DMA channels with their own register sets. All channels can be used as high speed selector channels for achieving maximum transfer rate or channel 3 can be used as a multiplexor channel to allow the 82258 to interface to a large number of I/O devices.

Figure 12. 82258 Channel Configuration

The selector channels support synchronised and non synchronised transfers as well as advanced features like single cycle transfer, command and data chaining. Channel switching imposes no performance penalty on the 82258. Programmable priority schemes allow flexible multiple channel processing.

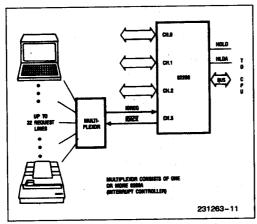

#### **MULTIPLEXOR CHANNEL**

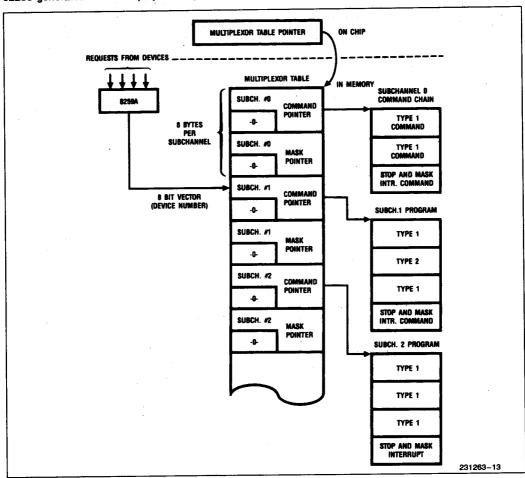

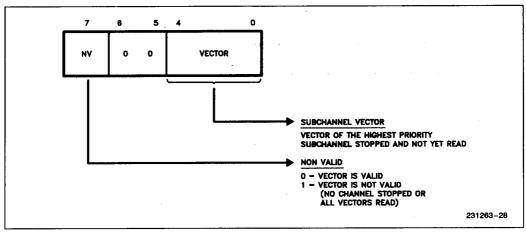

Channel 3 of the 82258 can also be operated as a multiplexor channel supporting up to 32 subchannels. External 8259As are used to arbitrate and prioritize channel requests (Figure 13). Multiplexor channel allows command chaining but data chaining is not supported.

As a multiplexor channel, channel 3 uses an external multiplexor table (MT) in the memory to store separate command pointers and, the PIC (8259A) mask register locations for each device in that channel. Each entry in the MT consists of 8 bytes; the first 4 give the command pointer for the subchannel and the second 4 the address of the mask register of the 8259A for that subchannel (Figure 14).

After an I/O request from the 8259A, the 82258 fetches an 8 bit vector (device number) from the interrupt controller (by the INT/INTA mechanism), left shifts it by three and, uses that as an offset into the multiplexor table with that entry pointing to the current subchannel command block. The 8259A should be programmed for AEOI mode.

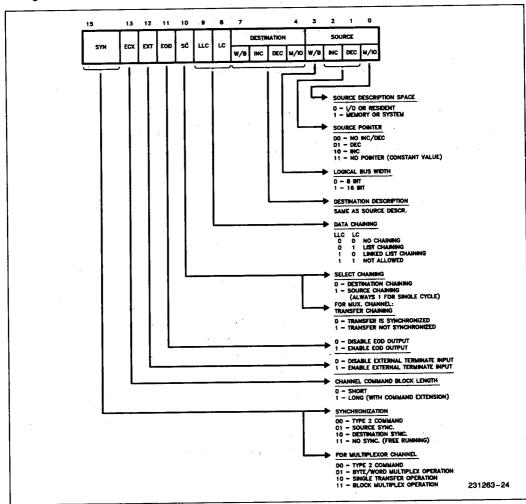

Each subchannel can have a subchannel program or a command chain. The command chain must be terminated by a stop and mask command (as opposed to a stop command for a selector channel). Three kinds of data transfers are possible:

Byte/Word Multiplex:

One byte/word is transferred per request. The source/destination pointer and the byte count fields of the command block are updated. The command pointer is not advanced until the block transfer is terminated. Maximum cumulative data transfer rate of 275K Bytes/sec can be achieved for the channel.

Single Transfer: Similar to the byte/word multplex. But, the command pointer is advanced after each transfer, thus, executing command chaining.

Figure 13. Multiplexor Configuration

Block Multiplex The whole command block is ex-Transfer:

ecuted and a block transfer made upon receiving a request. Such transfer is necessarily free running or non-synchronized and is carried out at a maximum speed of 4 MByte/sec in an 8 MHz 80286 system. After termination, the command pointer is advanced (command chaining).

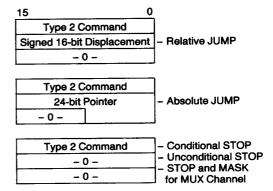

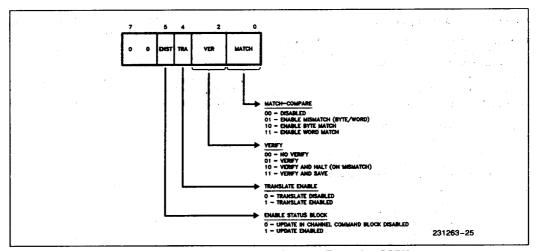

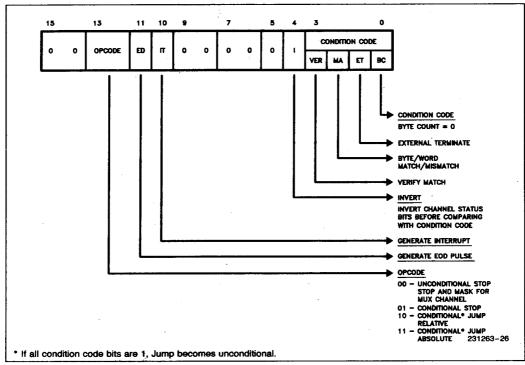

The type 2 commands have the same function as for the selector channels (Table 6). A subchannel is stopped with a stop and mask command which must occur at the end of a command block chain. The 82258 generates the interrupt (INTOUT) or EOD, if