## R96EFX

MONOFAX Modems

# R96EFX 9600 bps MONOFAX® Modem with Error Detection

## INTRODUCTION

The Rockwell R96EFX MONOFAX modem is a synchronous 9600 bits per second (bps) half-duplex modem with error detection. The modem is housed in a single VLSI device package.

The modem can operate over the public switched telephone network (PSTN) through line terminations provided by a data access arrangement (DAA).

The R96EFX is designed for use in Group 3 and Group 2 facsimile machines.

The modem satisfies the requirements specified in CCITT recommendations V.29, V.27 ter, V.21 Channel 2, T.3, and T.4, and meets the binary signaling requirements of T.30.

The modem can operate at 9600, 7200, 4800, 2400, or 300 bps, and also includes the V.27 ter short training sequence option.

The modem can also perform HDLC framing according to T.30 at 9600, 7200, 4800, 2400, or 300 bps.

The voice mode allows the host computer to efficiently transmit and receive audio signals and messages.

The modem includes three programmable tone detectors which operate concurrently with the V.21 channel 2, Group 2, and voice mode receivers.

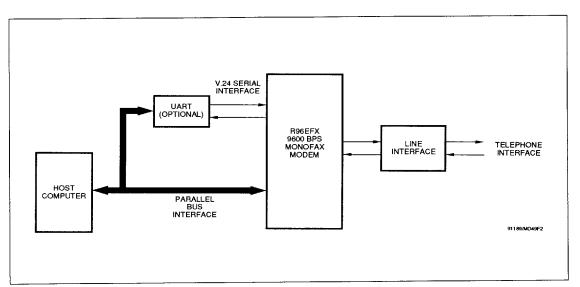

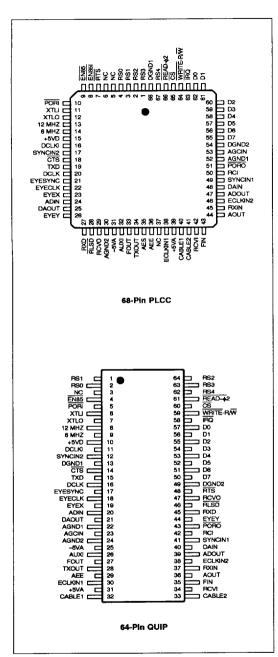

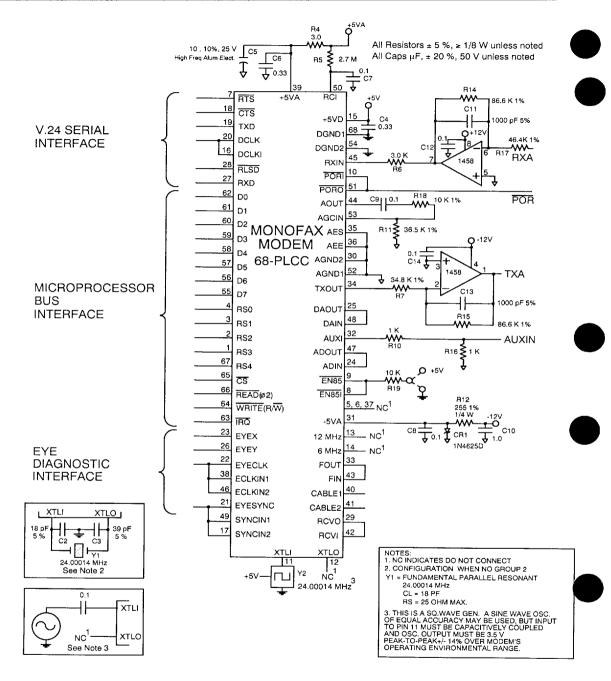

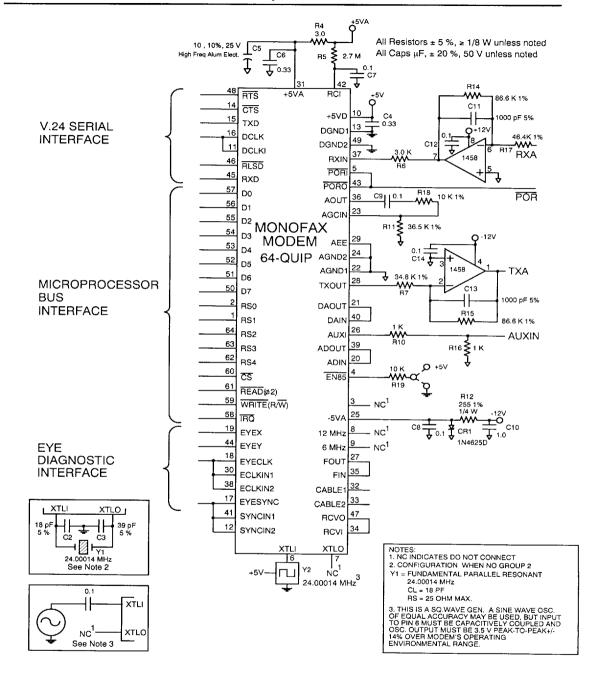

The modem is available in either a 68-pin plastic leaded chip carrier (PLCC) package or a 64-pin quad in-line package (QUIP). Figure 1 shows the modem in the PLCC. The general modem interface is illustrated in Figure 2.

Additional modem information is described in the 9600 bps MONOFAX Modem Designer's Guide (Order No. 820).

MONOFAX is a registered trademark of Rockwell International

#### **FEATURES**

- Group 3 and Group 2 facsimile transmission/ reception

- CCITT V.29, V.27 ter, T.30, V.21 Channel 2 (FSK), T.3, T.4

- HDLC Framing at all speeds

- V.27 ter short train

- · Voice mode transmission/reception

- Half-duplex (2-Wire)

- · Concurrent FSK and tone reception

- Maximum transmit level: 0 dBm programmable to –15 dBm

- Receive dynamic range: 0 dBm to –43 dBm

- Programmable dual tone generation

- Programmable tone detection

- Programmable turn-on and turn-off thresholds

- Programmable interface memory interrupt

- Diagnostic capability

- Allows telephone line quality monitoring

- Equalization

- Automatic adaptive

- Selectable compromise cable

- DTE interface: two alternate ports

- Selectable microprocessor bus (6500 or 8085)

- CCITT V.24 (EIA-232-D compatible) interface

- TTL and CMOS compatible

- Low power consumption: 370 mW (typical)

- Single Package

- 68-pin PLCC

- 64-pin QUIP

- Compatible with R144EFX, R96MFX, R96DFX, and R96VFX modems

Document No. 29200N49

**Data Sheet**

Order No. MD49 Rev. 4, June 1991

Figure 1. R96EFX MONOFAX Modem in 68-Pin PLCC

Figure 2. R96EFX MONOFAX Modem General Interface

## R96EFX

# 9600 bps MONOFAX Modem with Error Detection

## **TECHNICAL SPECIFICATIONS**

## Configurations, Signaling Rates And Data Rates

The selectable modem configurations, along with the corresponding signaling (baud) rates and data rates, are listed in Table 1.

#### **Tone Generation**

The modem can generate voice-band single or dual tones from 0 Hz to 4800 Hz with a resolution of 0.15 Hz and an accuracy of 0.01%. Tones over 3000 Hz are attenuated. Dual tone generation allows the modem to operate as a programmable DTMF dialer.

#### Data Encoding

The data encoding conforms to CCITT recommendations V.29, V.27 ter, V.21 Channel 2, and T.3.

## **Automatic Adaptive Equalizer**

An adaptive equalizer in V.29 and V.27 ter modes compensates for transmission line amplitude and group delay distortion.

## Compromise Cable Equalizers

Compromise equalization can improve performance when operating over low quality lines. Equalizer characteristics for cable lengths of 0, 1.8, 3.6, or 7.2 km are selectable by two hardware input pins (see CABLE1 and CABLE2 signal description in Table 9). The selected filter operates in both transmit and receive paths.

#### Transmitted Data Spectrum

The transmitted data spectrum is shaped in the baseband by an excess bandwidth finite impulse response (FIR) filter with the following characteristics:

When operating at 2400 baud, the transmitted spectrum is shaped by a square root of 20% raised cosine filter.

When operating at 1600 baud, the transmitted spectrum is shaped by a square root of 50% raised cosine filter.

When operating at 1200 baud, the transmitted spectrum is shaped by a square root of 90% raised cosine filter.

The transmit spectrum characteristics assume that the cable equalizers are disabled.

The out-of-band transmitter energy levels in the 4 kHz – 50 kHz frequency range are below –55.0 dBm.

#### **Turn-on Sequence**

Transmitter turn-on sequence times are shown in Table 2.

## Turn-off Sequence

For V.27 ter, the turn-off sequence consists of approximately 10 ms of remaining data and scrambled ones at 1200 baud or approximately 7 ms of data and scrambled ones at 1600 baud followed by a 20 ms period of no transmitted energy.

For V.29, the turn-off sequence consists of approximately 5 ms of remaining data and scrambled ones followed by a 20 ms period of no transmitted energy.

In V.21, the transmitter turns off within 7 ms after  $\overline{\text{RTS}}$  goes false.

In Group 2, the transmitter turns off within 200  $\mu s$  after  $\overline{RTS}$  goes false.

When operating in parallel data mode, the turn-off sequence may be extended by 8 bit times.

When HDLC is selected, the turn-off sequence may be extended by more than 8 bit times,

Table 2. Turn-On Sequence Times

|                               | RTS On to                             | CTS On                               |

|-------------------------------|---------------------------------------|--------------------------------------|

| Configuration                 | Echo<br>Protector<br>Tone<br>Disabled | Echo<br>Protector<br>Tone<br>Enabled |

| V.29 (All Speeds)             | 253 ms                                | 441 ms                               |

| V.27 ter 4800 bps Long Train  | 708 ms                                | 915 m                                |

| V.27 ter 4800 bps Short Train | 50 ms                                 | 257 ms                               |

| V.27 ter 2400 bps Long Train  | 943 ms                                | 1150 ms                              |

| V.27 ter 2400 bps Short Train | 67 ms                                 | 274 ms                               |

| V.21 channel 2 300 bps        | ≤14 ms                                | ≤14 m                                |

| Group 2                       | ≤400 μs                               | ≤400 แร                              |

Table 1. Configurations, Signaling Rates and Data Rates

|          |                                                       |                                                                              | c.) Symbol                                                                            | Points                                                                                     |

|----------|-------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| A 1700   | 9600                                                  | 2400                                                                         | 4                                                                                     | 16                                                                                         |

| A 1700   | 7200                                                  | 2400                                                                         | 3                                                                                     | 8                                                                                          |

| A 1700   | 4800                                                  | 2400                                                                         | 2                                                                                     | 4                                                                                          |

| SK 1800  | 4800                                                  | 1600                                                                         | 3                                                                                     | 8                                                                                          |

| K 1800   | 2400                                                  | 1200                                                                         | 2                                                                                     | 4                                                                                          |

| 1650,1   | 850 300                                               | 300                                                                          | 1                                                                                     | 1 -                                                                                        |

| MPM 2100 | _                                                     | _                                                                            | _                                                                                     | _                                                                                          |

|          | M 1700<br>SK 1800<br>SK 1800<br>( 1650,1<br>MMPM 2100 | M 1700 4800<br>SK 1800 4800<br>SK 1800 2400<br>( 1650,1850 300<br>MPM 2100 — | M 1700 4800 2400 SK 1800 4800 1600 SK 1800 2400 1200 C 1650,1850 300 300 MPM 2100 – – | M 1700 4800 2400 2 SK 1800 4800 1600 3 SK 1800 2400 1200 2 C 1650,1850 300 300 1 MMPM 2100 |

MD49C1

3

Frequency Shift Keying Vestigial Sideband Amplitude Modulation - Phase Modulation

## R96EFX

## 9600 bps MONOFAX Modem with Error Detection

#### Transmit Level

The transmitter output level is programmable in the DSP RAM from 0 dBm to -15.0 dBm and is accurate to  $\pm$  1.0 dBm. The modem adjusts the output level by digitally scaling the output to the transmitter's digital-to-analog converter.

## Scrambler/Descrambler

The modem incorporates a self-synchronizing scrambler/descrambler in accordance with V.29 or V.27 ter recommendations, depending on the selected configuration.

## Receive Dynamic Range

The receiver satisfies PSTN performance requirements for received line signal levels from 0 dBm to -43 dBm measured at the Receiver Analog Input (RXA) input. An external input buffer and filter must be supplied between RXA and RXIN.

The default values of the programmable Received Line Signal Detector (RLSD) turn-on and turn-off threshold levels are -43 dBm and -48 dBm, respectively. The RLSD threshold levels can be programmed over the following range:

Turn on: -10 dBm to -47 dBm Turn off: -10 dBm to -52 dBm

## **Receiver Timing**

The timing recovery circuit can track a  $\pm$  0.01% frequency error in the associated transmit timing source.

## **Carrier Recovery**

The carrier recovery circuit can track a ± 7 Hz frequency offset in the received carrier.

## Clamping

Received  $\underline{\text{Data}}$  (RXD) is clamped to a constant mark whenever  $\overline{\text{RLSD}}$  is off.

#### Tone Detectors

Tone detectors 1 and 2 operate in all non-high speed receive modes. Tone detector 3 operates in all receive modes. The tone detectors can also operate as one 12th order filter (see 12TH bit in Table 10).

The filter coefficients of each filter are host programmable in RAM. The output of the tone detector filter goes to an energy detector. (See 9600 bps MONOFAX Modem Designer's Guide.)

## Voice Mode

The voice mode enables the host to efficiently transmit and receive audio signals and messages. In this mode, the host can directly access modem analog-to-digital (A/D) and digital-to-analog (D/A) converters. Incoming analog voice signals can then be converted to digital format and digital signals can be converted to analog voice output.

## **General Specifications**

The modem power and environmental requirements are shown in Tables 3 and 4, respectively.

Table 3. Power Requirements

| Voltage     | Current (Typ.)<br>@ 25°C | Current (Max.)<br>@ 0°C |

|-------------|--------------------------|-------------------------|

| +5 VDC ±5%  | 60 mA                    | 64 mA                   |

| - 5 VDC ±5% | 14 mA                    | 16 mA                   |

Note: Input voltage ripple ≤ 0.1 volts peak-to-peak. The amplitude of any frequency between 20 kHz and 150 kHz must be less than 500 μV peak.

Table 4. Environmental Requirements

| Parameter                                       | Specification                                                                                                                                  |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Temperature Operating Storage Relative Humidity | 0°C to 70°C (32 °F to 158°F) -55°C to 125°C (-67°F to 257°F) Up to 90% noncondensing, or a wet bulb temperature up to 35°C, whichever is less. |

## HARDWARE INTERFACE SIGNALS

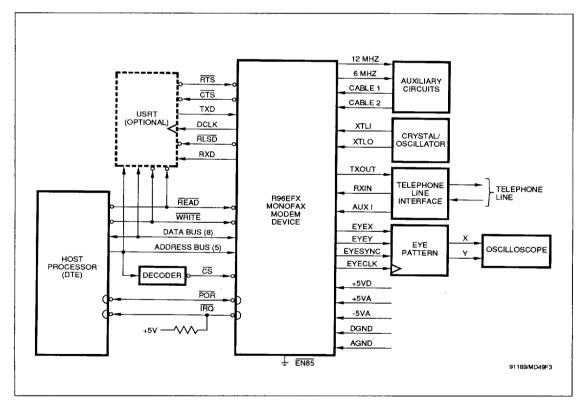

The modem functional hardware interface signals are shown in Figure 3. In this diagram, any point that is active when exhibiting the relatively more negative voltage of a two-voltage system (e.g., 0 VDC for TTL or -12 VDC for EIA-232-D) is called active low and is represented by a small circle at the signal point. Active low signals are overscored (e.g., POR).

Edge-triggered clocks are indicated by a small triangle (e.g., DCLK).

Open-collector (open-source or open-drain) outputs are denoted by small half circle (e.g., signal IRQ).

A clock intended to activate logic on its rising edge (low-tohigh transition) is called active low, while a clock intended to activate logic on its falling edge (high-to-low transition) is called active high. When a clock input is associated with a small circle, the input activates on a falling edge. If no circle is shown, the input activates on a rising edge.

The modem pin assignments are shown in Figure 4. The pin assignments are listed by pin number in Table 5.

The hardware interconnect signals shown in Figure 3 are listed by functional group in Table 6. The digital and analog signal interface characteristics are defined in Table 7 and Table 8, respectively. The hardware interface signals are defined in Table 9.

Figure 3. R96EFX Modem Functional Interconnect Signals

MD49C2

5

Figure 4. R96EFX Modem Pin Assignments

Table 5. R96EFX Modem Pin Assignments

| l able 5                  |                           | em Pin Assignmer  |                |

|---------------------------|---------------------------|-------------------|----------------|

| 68-Pin PLCC<br>Pin Number | 64-Pin QUIP<br>Pin Number | Signal<br>Name    | I/O<br>Type    |

| 3                         | 1                         | RS1               | IA.            |

| 4 5                       | 2                         | RS0<br>NC         | IA             |

| 6                         | 3                         | NC_               |                |

| 8                         | _                         | EN851             | R              |

| 9                         | 4                         | EN85<br>PORI      | R<br>ID        |

| 10<br>11                  | 5<br>1 6                  | XTLI              | R              |

| 12                        | 7                         | XTLO              | R              |

| 13                        | 8                         | 12 MHZ            | OD             |

| 14<br>15                  | 9                         | 6 MHZ<br>+5VD     | OD<br>PWR      |

| 16                        | 11                        | DCLKI             | R              |

| 17                        | 12                        | SYNCIN2           | R              |

| 68<br>18                  | 13<br>14                  | DGND1<br>CTS      | GND<br>OA      |

| 19                        | 15                        | TXD               | ΙΑ             |

| 20                        | 16                        | DCLK              | OA             |

| 21<br>22                  | 17<br>18                  | EYESYNC<br>EYECLK | OA<br>OA       |

| 23                        | 19                        | EYEX              | OA<br>OA       |

| 24                        | 20                        | ADIN              | R              |

| 25                        | 21                        | DAOUT             | R              |

| 52<br>53                  | 22<br>23                  | AGND1<br>AGCIN    | GND<br>R       |

| 30                        | 24                        | AGND2             | GND            |

| 31                        | 25                        | -5VA              | PWR            |

| 32<br>33                  | 26<br>27                  | AUXI<br>FOUT      | AC<br>R        |

| 34                        | 28                        | TXOUT             | ÄA             |

| 35                        |                           | AES               | R              |

| 36<br>37                  | 29                        | AEE<br>NC         | R              |

| 38                        | 30                        | ECLKIN1           | R              |

| 39                        | 31                        | +5VA              | PWR            |

| 40<br>41                  | 32<br>33                  | CABLE1<br>CABLE2  | iB<br>IB       |

| 42                        | 34                        | RCVI              | Ř              |

| 43                        | 35                        | FIN               | R              |

| 44<br>45                  | 36<br>37                  | AOUT<br>RXIN      | R<br>AB        |

| 46                        | 38                        | ECLKIN2           | R              |

| 47                        | 39                        | ADOUT             | R              |

| 48                        | 40                        | DAIN<br>SYNCIN1   | R              |

| 49<br>50                  | 41<br>42                  | RCI               | R              |

| 51                        | 43                        | PORO              | OE             |

| 26                        | 44                        | EYEY              | OA<br>OA       |

| 27<br>28                  | 45<br>46                  | RXD<br>RLSD       | OA<br>OA       |

| 29                        | 47                        | <u>RCV</u> O      | R              |

| 7                         | 48                        | RTS               | IA             |

| 54<br>55                  | 49<br>50                  | DGND2<br>D7       | GND<br>IA/OB   |

| 56                        | 51                        | D6                | IA/OB          |

| 57                        | 52                        | D5                | IA/OB<br>IA/OB |

| 58<br>59                  | 53<br>54                  | D4<br>D3          | IA/OB          |

| 60                        | 55                        | D2                | IA/OB          |

| 61                        | 56                        | D1                | IA/OB          |

| 62<br>63                  | 57<br>58                  | IRQ               | IA/OB<br>OC    |

| 64                        | 59                        | WRITE-P/W         | IA.            |

| 65                        | 60                        | <del>CS</del>     | IA             |

| 66<br>67                  | 61<br>62                  | READ-             | IA<br>IA       |

| 1 1                       | 63                        | RS3               | IA             |

| 2                         | 64                        | RS2               | ΪA             |

Notes: 1. NC = No connection, leave pin disconnected (open).

I/O Type: Digital signals: see Table 7;

Analog signals: see Table 8.

Required overhead connection; do not connect to host equipment.

Table 6. Modem Hardware Interface Signals

| Name               | Type       | Description                                 |

|--------------------|------------|---------------------------------------------|

| Overhead Signa     | ls         |                                             |

| XTLI               | R          | Connect to Crystal                          |

| XTLO               | R          | Connect to Crystal                          |

| PORO               | OE         | Power-On-Reset Output                       |

| PORI               | ID.        | Power-On-Reset Input                        |

| +5VD               | PWR        | Connect to Digital +5V Power                |

| +5VA               | PWR        | Connect to Analog +5V Power                 |

| -5VA               | PWR        | Connect to Analog -5V Power                 |

| DGND1              | GND        | Connect to Digital Ground                   |

| DGND2              | GND        | Connect to Digital Ground                   |

| AGND1              | GND        | Connect to Analog Ground                    |

| AGND2              | GND        | Connect to Analog Ground                    |

| Microprocessor     | Bus Interi | ace                                         |

| D7                 | IA/OB      | Data Bus Line 7                             |

| D6                 | IA/OB      | Data Bus Line 6                             |

| D5                 | IA/OB      | Data Bus Line 5                             |

| D4                 | IA/OB      | Data Bus Line 4                             |

| D3                 | IA/OB      | Data Bus Line 3                             |

| D2                 | IA/OB      | Data Bus Line 2                             |

| D1                 | IA/OB      | Data Bus Line 1                             |

| D0                 | IA/OB      | Data Bus Line 0                             |

| RS4                | IA         | Register Select 4                           |

| RS3                | IA         | Register Select 3                           |

| RS2                | IA         | Register Select 2                           |

| RS1                | IA         | Register Select 1                           |

| RS0                | IA         | Register Select 0                           |

| CS_                | IA         | Chip Select                                 |

| READ-\$2_          | IA         | Read Enable (808X), \$\psi_2\$ Clock (65XX) |

| WRITE-R/W          | IA         | Write Enable (808X), R/W (65XX)             |

| IRQ                | OC_        | Interrupt Request                           |

| V.24 Serial Interf |            |                                             |

| TXD                | IA         | Transmit Data                               |

| RXD                | OA         | Received Data                               |

| RTS                | IA         | Request to Send                             |

| CTS                | OA         | Clear to Send                               |

| RLSD               | OA         | Received Line Signal Detected               |

| DCLK               | OA         | Transmit and Receive Data Clock             |

| Auxiliary Signals  | •          |                                             |

| EN85               | R          | Enable 85 Bus                               |

| CABLE1             | IB         | Cable Select 1                              |

| CABLE2             | IB         | Cable Select 2                              |

| 12 MHZ             | OD         | 12 MHz Output                               |

| 6 MHZ              | OD         | 6 MHz Output                                |

Table 6. Modem Hardware Interface Signals (Cont'd)

| Name          | Type         | Description                             |

|---------------|--------------|-----------------------------------------|

| Analog Signa  | 8            |                                         |

| TXOUT         | AA           | Connect to Smoothing Filter Input       |

| RXIN          | AB           | Connect to Anti-aliasing Filter Output  |

| AUXI          | AC           | Auxiliary Analog Input                  |

| Eye Diagnosti | c Interface  |                                         |

| EYEX          | OA           | Serial Eye Pattern X Output             |

| EYEY          | OA           | Serial Eye Pattern Y Output             |

| EYECLK        | OA           | Serial Eye Pattern Clock                |

| EYESYNC       | OA           | Serial Eye Pattern Strobe               |

| Modem Interc  | onnect       |                                         |

| DCLKI         | R            | Connect to DCLK                         |

| ECLKIN1       | R            | Connect to EYECLK                       |

| ECLKIN2       | R            | Connect to EYECLK                       |

| SYNCIN1       | R            | Connect to EYESYNC                      |

| SYNCIN2       | R            | Connect to EYESYNC                      |

| RCVI          | R            | Connect to RCVO                         |

| RCVO          | R            | Mode Select Output                      |

| ADIN          | R            | Connect to ADOUT                        |

| ADOUT         | R            | ADC Output                              |

| DAIN          | R            | Connect to DAOUT                        |

| <u>DAOU</u> T | R            | DAC/AGC Output                          |

| EN85I         | R            | Connect to EN85 <sup>4</sup>            |

| AEE           | R            | Connect to Analog Ground                |

| AES           | R            | Connect to Analog Ground <sup>4</sup>   |

| AGCIN         | R            | AGC Input                               |

| AOUT          | R            | Smoothing Filter Output                 |

| FIN           | R            | Connect to FOUT                         |

| FOUT          | R            | Smoothing Filter Output                 |

| RCI           | R            | RC Junction for POR Time Constant       |

| Notes:        |              |                                         |

|               |              | are described in Table 7.               |

|               |              | are described in Table 8.               |

|               |              | overhead connection; no connection to   |

| h             | ost equipme  | nt.                                     |

|               | nused inputs | tied to +5V or ground require individua |

| •             |              | 03131013.                               |

| 4. P          | LCC only.    |                                         |

Table 7. Digital Interface Characteristics

| Parameter              | Symbol          | Min.     | Тур. | Max. | Units | Test Conditions                                       |

|------------------------|-----------------|----------|------|------|-------|-------------------------------------------------------|

| Input High Voltage     | ViH             |          |      |      | Vdc   |                                                       |

| Types IA and IB        |                 | 2.0      | -    | Vcc  |       |                                                       |

| Type ID                |                 | 0.8(Vcc) | _    | Vcc  |       |                                                       |

| Input High Current     | lin.            | - 1      |      | 40   | μА    | V <sub>CC</sub> = 5.25 V, V <sub>IN</sub> = 5.25 V    |

| Type IB                |                 |          |      |      | ,     |                                                       |

| Input Low Voltage      | VIL             | -0.3     |      | 0.8  | Vdc   |                                                       |

| Input Low Current      | I <sub>IL</sub> | _        | _    | -400 | μА    | V <sub>CC</sub> = 5.25 V                              |

| Type IB                | 1               |          |      |      | 1     |                                                       |

| Input Leakage Current  | IIN             | _        |      | ±2.5 | μА    | V <sub>IN</sub> = 0 to +5 V, V <sub>CC</sub> = 5.25 V |

| Types IA and ID        |                 |          |      |      | ,     |                                                       |

| Output High Voltage    | VoH             |          |      |      | Vdc   |                                                       |

| Types OA and OB        |                 | 3.5      | -    | -    | 1     | I <sub>LOAD</sub> = - 100 μA                          |

| Type OE                |                 | 2.4      | _    | _    |       | ILOAD = -40 µA                                        |

| Output High Current    | Іон             | - 1      | _    | -0.1 | mA    |                                                       |

| Type OD                |                 |          |      |      |       |                                                       |

| Output Low Voltage     | Vol             |          |      |      | Vdc   |                                                       |

| Types OA and OC        |                 | -        | _    | 0.4  |       | ILOAD = 1.6 mA                                        |

| Type OB                |                 | - 1      | _    | 0.4  | 1     | I <sub>LOAD</sub> = 0.8 mA                            |

| Type OE                |                 | -        |      | 0.4  |       | I <sub>LOAD</sub> = 0.4 mA                            |

| Output Low Current     | lau             | -        | -    | 100  | μA    |                                                       |

| Type OD                | 1               |          |      |      |       |                                                       |

| Output Leakage Current | ILO             | -        | -    | ±10  | μA    | V <sub>IN</sub> = 0.4 to V <sub>CC</sub> -1           |

| Types OA and OB        |                 |          |      |      |       |                                                       |

| Capacitive Load        | CL              |          |      |      | pF    |                                                       |

| Types IA and ID        |                 | _        | 5    | -    |       |                                                       |

| Type IB                |                 | -        | 20   | _    |       |                                                       |

| Capacitive Drive       | CD              |          |      |      | pF    |                                                       |

| Types OA, OB, and OC   |                 | -        | 100  | _    |       |                                                       |

| Type OD                |                 | -        | 50   | _    |       |                                                       |

| Circuit Type           |                 |          |      |      |       |                                                       |

| Type IA                |                 |          |      | 1    |       | TTL                                                   |

| Type IB                |                 |          |      | i    |       | TTL with pull-up                                      |

| Type ID                |                 |          |      |      |       | POR                                                   |

| Types OA and OB        |                 |          |      |      |       | TTL with 3-state                                      |

| Type OC and OE         |                 |          |      | 1    |       | Open drain                                            |

| Type OD                |                 |          |      |      |       | Clock                                                 |

| Power Dissipation      | Po              | -        | 370  | 420  | mW    | Vcc = 5.0 V @ 25°C for Pp typ.                        |

|                        |                 |          |      | 1    |       | voc = 5.25 V @ 0°C for Pp max                         |

Table 8. Analog Interface Characteristics

| Name  | Туре | Characteristic                          |

|-------|------|-----------------------------------------|

| TXOUT | AA   | Maximum output:                         |

|       |      | ±3.03 volts                             |

|       | ì    | Minimum load:                           |

|       | 1    | 10K Ω                                   |

|       | İ    | Smoothing filter transfer function:     |

|       | 1    | 28735.63/(s + 11547.34)                 |

| RXIN  | AB   | Input impedance:                        |

|       | 1    | > 1M Ω                                  |

|       |      | Anti-aliasing filter transfer function: |

|       |      | 21551.72/(s + 11547.34)                 |

| AUXI  | AC   | Maximum input frequency:                |

|       | i    | 4800 Hz                                 |

|       | 1    | Input Impedance:                        |

|       |      | ` > 1M Ω                                |

|       | 1    | Gain to TXOUT:                          |

|       |      | 0 dBm ±1 dB                             |

Table 9. Hardware Interface Signal Definitions

| Label           | I/O Type | Signal/Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |          | OVERHEAD SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XTLI<br>XTLO    | 0        | Crystal In and Crystal Out. The DSP must be connected to an external crystal circuit consisting of a 24.00014 MHz crystal and two capacitors, or a square wave generator/sine wave oscillator (see Figures 6 and 7).                                                                                                                                                                                                                                                                                                                                                                                                      |

| PORI<br>PORO    | ID<br>OE | Power-On-Reset Input.  Power-On-Reset Output. The PORI and PORO pins should be connected together to form a bidirectional POR signal. When power is applied to the modem, the modem pulses (POR) within 350 ms. The modem is ready to use 15 ms after the low-to-high transition of POR. The POR sequence is reinitiated any time the + 5V supply drops below + 3.5V for more than 15 ms, or an external device drives POR low for at least 3 µs. POR is not pulsed low by the modem when the POR sequence is initiated externally. The POR sequence initializes the modem interface memory (Table 10) to default values. |

| +5VD            | PWR      | + 5V Digital Supply. +5VD must be connected to +5V ± 5%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| +5VA            | PWR      | + 5V Analog Supply. +5VA must be connected to +5V ± 5%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| –5VA            | PWR      | <b>–5V Analog Supply.</b> –5VA must be connected to −5V ± 5%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DGND1,<br>DGND2 | GND      | Digital Ground. DGND1 and DGND2 must be connected to digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AGND1,<br>AGND2 | GND      | Analog Ground. AGND1 and AGND2 must be connected to analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |          | MICROPROCESSOR BUS INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 |          | Address, data, control, and interrupt hardware interface signals allow modem connection to an 8085 or 6500 bus compatible microprocessor. With the addition of external logic, the interface can be made compatible with a wide variety of other microprocessors, such as the 8080 or 68000.                                                                                                                                                                                                                                                                                                                              |

|                 |          | The microprocessor interface allows a microprocessor to change modern configuration, read or write channel and diagnostic data, and supervise modern operation by writing control bits and reading status bits.                                                                                                                                                                                                                                                                                                                                                                                                           |

|                 |          | Note that the modem should not be continuously selected for read operation. Also, read or write operations should be delayed by at least 334 ns from a preceding write cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| D0-D7           | IA/OB    | Data Lines. Eight bidirectional data lines (D0-D7) provide parallel transfer of data between the host and the modern. The most significant bit is D7. Data direction is controlled by the Read Enable (READ-\$42) and Write Enable (WRITE-R/W) signals.                                                                                                                                                                                                                                                                                                                                                                   |

|                 |          | During a read cycle, data from the DSP interface memory register is gated onto the data bus by means of three-state drivers in the DSP. These drivers force the data lines high for a one bit, or low for a zero bit. When not being read, the three-state drivers assume their high-impedance (off) state.                                                                                                                                                                                                                                                                                                               |

|                 |          | During a write cycle, data from the data bus is copied into the selected DSP interface memory register, with high and low bus levels representing one and zero bit states, respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RS0-RS4         | IA       | Register Select Lines. The five active high Register Select inputs (RS0-RS4) address interface memory registers within the DSP when $\overline{\text{CS}}$ is low. These lines are typically connected to address lines A0-A4.                                                                                                                                                                                                                                                                                                                                                                                            |

|                 |          | When selected by $\overline{\text{CS}}$ low, the DSP decodes RS0 through RS4 to address one of 32 8-bit internal interface memory registers (00-1F). The most significant address bit is RS4 while the least significant address bit is RS0. The selected register can be read from, or written into, via the 8-bit parallel data bus (D0-D7).                                                                                                                                                                                                                                                                            |

Table 9. Hardware Interface Signal Definitions (Cont'd)

| <del>cs</del>          | I        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>~</b>               | IA       | Chip Select. The active low $\overline{\text{CS}}$ input selects and enables the modem DSP for parallel data transfer between the DSP and the host over the microprocessor bus.                                                                                                                                                                                                                                                                                                                                                                                          |

|                        |          | The $\overline{\text{CS}}$ input line is typically connected to address line A5 through a decoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| READ-¢2 _<br>WRITE-R/W | IA<br>IA | Read Enable—\$\phi_2. When \overline{\text{EN85}} is low (8085 bus selected), reading or writing is controlled by the host pulsing either \overline{\text{READ}} or \overline{\text{WRITE}} input low, respectively, during the microprocessor bus access cycle.                                                                                                                                                                                                                                                                                                         |

| ĪRQ                    | oc       | Interrupt Request. $\overline{IRQ}$ interrupt request output may be connected to the host processor interrupt request input in order to interrupt host program execution for immediate modem service. The $\overline{IRQ}$ output can be enabled in DSP interface memory to indicate immediate change of conditions in the modem. The use of $\overline{IRQ}$ is optional depending upon modem application.                                                                                                                                                              |

|                        |          | The $\overline{\text{IRQ}}$ output structure is an open-drain field-effect-transistor (FET). The $\overline{\text{IRQ}}$ output can be wire-ORed with other $\overline{\text{IRQ}}$ lines in the application system. Any of these sources can drive the host interrupt input low, and the host inte <u>rrupt</u> servicing process normally continues until all interrupt requests have been serviced (i.e., all IRQ lines have returned high).                                                                                                                          |

|                        |          | Because of the open-drain structure of $\overline{IRQ}$ , an external pull-up resistor to $+5V$ is required at some point on the $\overline{IRQ}$ line. The resistor value should be small enough to pull the $\overline{IRQ}$ line high when all $\overline{IRQ}$ drivers are off (i.e., it must overcome the leakage currents). The resistor value should be large enough to limit the driver sink current to a level acceptable to each driver. If only the modern $\overline{IRQ}$ output is used, a resistor value of 5.6K ohms $\pm 20\%$ , 0.25 W, is sufficient. |

|                        |          | V.24 SERIAL INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                        |          | Seven pins provide timing, data, and control signals for implementing a CCITT Recommendation V.24 compatible serial interface. These signals are TTL compatible in order to drive the short wire lengths and circuits normally found within stand-alone modem enclosures or equipment cabinets. For driving longer cables, these signals can be easily converted to EIA-232-D voltage levels.                                                                                                                                                                            |

| TXD                    | IA       | <b>Transmit Data.</b> The modem obtains serial data to be transmitted from the local DTE on the Transmit Data (TXD) input in serial data mode (selected by PDM bit in interface memory), or from the interface memory Transmit Data Register (DBUFF) in parallel data mode (selected by PDM bit).                                                                                                                                                                                                                                                                        |

| RXD                    | OA       | Received Data. The modem presents received serial data to the local DTE on the Received Data (RXD) output and to the interface memory Receive Data Register (DBUFF) in both serial and parallel data modes.                                                                                                                                                                                                                                                                                                                                                              |

| RTS                    | IA       | Request to Send. The active low $\overline{\text{RTS}}$ input allows the modem to transmit data present at TXD in the serial data mode or in DBUFF in the parallel data mode when $\overline{\text{CTS}}$ becomes active.                                                                                                                                                                                                                                                                                                                                                |

|                        |          | The $\overline{\text{RTS}}$ hardware control input is logically ORed with the RTSP bit (Table 10) by the modern to form the resultant control signal.                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 9. Hardware Interface Signal Definitions (Cont'd)

| Label                | I/O Type | Signal/Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTS                  | OA       | Clear To Send. CTS active indicates to the local DTE that the training sequence has beer completed and any data present at the TXD input in the serial data mode or in DBUFF in the paralle data mode will be transmitted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                      |          | CTS response times from RTS are shown in Table 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                      |          | The CTS hardware status output parallels the operation of the CTSP bit (Table 10).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RLSD                 | OA       | Received Line Signal Detector. For V.29 and V.27 ter; RLSD goes active at the end of the training sequence. If energy is above the turn-on threshold and training is not detected, the RLSD off-to-or response time is 804 baud times. The RLSD on-to-off time is 35±5ms for V.29 or 11.6 ± 5 ms for V.27 ter. The RLSD on-to-off time ensures that all valid data bits have appeared on RXD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                      |          | The RLSD programmable threshold levels default to -43 dBm for off-to-on and to -48 dBm for on-to-off. A minimum hysteresis of 2 dBm exists between the actual off-to-on and on-to-off transition levels. The threshold level and hysteresis are measured with an unmodulated 2100 Hz tone applied to the Receiver Analog (RXA) input. Note that performance may be degraded when the received signal level is less than -43 dBm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DCLK                 | OA       | Data Clock. The modern outputs a single mode-dependent synchronous data clock (DCLK) for USRT timing. The DCLK frequency is 9600, 7200, 4800, 2400, or 300 Hz (± 0.01%) with a duty cycle of 50 ± 1% except in Group 2. In Group 2, the DCLK frequency is 10368 Hz (± 5 ppm) when using a precision oscillator (see Figures 6 and 7).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                      | !        | Transmit Data (TXD) must be stable during the one microsecond period immediately preceding the rising edge of DCLK and following the rising edge of DCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                      |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                      |          | AUXILIARY SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| EN85                 | I        | Enable 85 Bus. The EN85 input selects the modern microprocessor bus compatibility. When EN85 is low, the modern can interface directly to an 8085 compatible microprocessor bus using READ and WRITE. When EN85 is high, the modern can interface directly to a 6500 compatible microprocessor bus using \$2 and R/W. In the 6500 configuration, the READ input becomes \$2 and the WRITE input becomes R/W. This selection is performed only during initialization, i.e., when power is turned on owhen POR is activated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |