# Multi-Level E<sup>2</sup>PLDs

### **FEATURES**

- 600-800 Gate Equivalent Logic Complexity

- Industry-Standard Data I/O ABEL<sup>TM</sup> PLD Design Tool Compatibility

- Advanced ERASIC Architecture

- True gate array style logic integration

- From 1 to 42 internal logic levels without using a pin

- Eliminates 2-level logic restriction of conventional PLDs

- 10 Buriable JK/T/D Flip-Flops

- Flip-flops may be connected to any logic level

- 2 term-controlled 4-bit input latches

- 64-way Programmable I/O Macrocell

- 2-Micron E<sup>2</sup>CMOS Technology

- Electrically Erasable and Programmable

Reprogrammable 10,000 times (min.)

- Reprogrammable in plastic packages

- Reprogramming time less than 5 seconds, including erase and verify

- 100% Factory Tested

- Security Plus Provides Design Security Plus 100%

Verification Capability

- High Performance

- 35ns Maximum One-level Propagation Delay

- 50ns Maximum Two-level Propagation Delay

- --- 15ns Maximum Internal Propagation Delay Per Level

- Low Power

- 20mA current for typical designs at 10MHz

- Uses power only for logic used

- Pin-compatible with 24-pin PAL® Devices

- Windowless 24-pin 300-mil DIP

- TTL and CMOS Compatible Inputs and Outputs

- 8mA/4mA Output Sink and Source Capability

- Programmable on Conventional PLD Programmers

- 5V Operation

### PIN CONFIGURATION

28 Pin PLCC 24 Pin Skinny DIP Type "P3" Package Type "D" Package 3555 5555 CLK/I 23 1/00 lo 11 d 3 22 1/01 21 1/02 25 1/O<sub>2</sub> 24 1/O<sub>3</sub> 23 1/O<sub>4</sub> 22 1/O<sub>5</sub> 21 1/O<sub>6</sub> 12 4 NC |3 |4 NC |5 <u>6</u> 13 5 20 1/03 19 1/04 14 6 9 7 18 1/05 15 I<sub>6</sub> 17 1/06 16 □в 16 1/07 17 **[**] 9 21 21 21 21 21 21 lg 10 15 1/Oa 14 1/09 19 11 13 OE 1/ GND 112

### **PIN NAMES**

| lol9<br>I/Ool/O9<br>OE/I | Inputs Inputs/Outputs Output Enable/Input |

|--------------------------|-------------------------------------------|

| CLK/I                    | Clock/Input                               |

#### **APPLICATIONS**

- Programmable replacement for conventional logic families

- -LSTTL, ALS, CMOS

- Fast-turnaround, low-risk gate array alternative

- Low-power, high-functionality alternative to existing Programmable Logic Devices. One device may replace 3-4 PALs.

### DESCRIPTION

The ERASIC XL78C800 is an electrically-reprogrammable CMOS ASIC component with multi-level logic capabilities. Designed to integrate a wide variety of user-defined logic functions onto a single package, this fast-turnaround ASIC device is an ideal choice when time-to-market, board space and power are at a premium.

The XL78C800 features an equivalent gate complexity of 600-800 gates packaged in a space-saving 300-mil 24-pin package. Fabricated using EXEL's high-performance double-metal E<sup>2</sup>-CMOS process, the XL78C800 typically requires a supply current of less than 20mA and may be electrically erased and programmed in less than five seconds total.

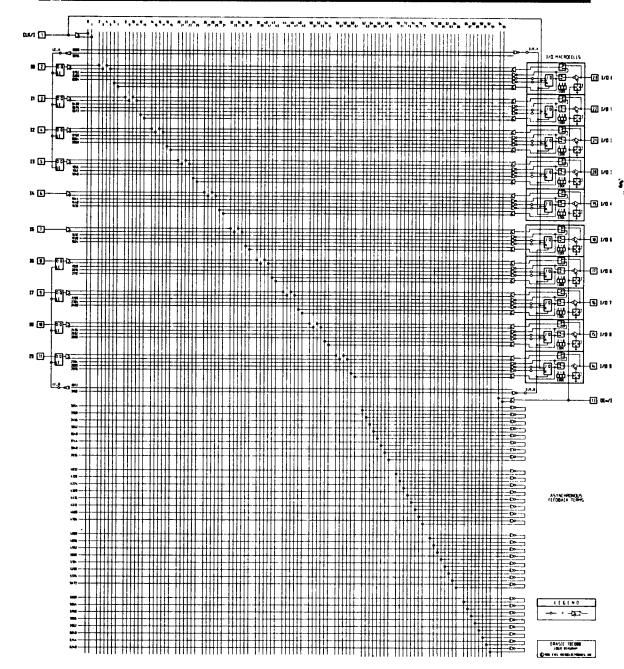

FIGURE 2. ERASIC XL78C800 LOGIC DIAGRAM

### **ERASIC XL78C800**

The ERASIC XL78C800 is an advanced electricallyreprogrammable ASIC component designed for integration of complex user-defined logic. The XL78C800 offers multi-level logic and buriable JK Flip-Flops, thereby enhancing logic design options, increasing integration and maximizing performance.

### **Architectural Overview**

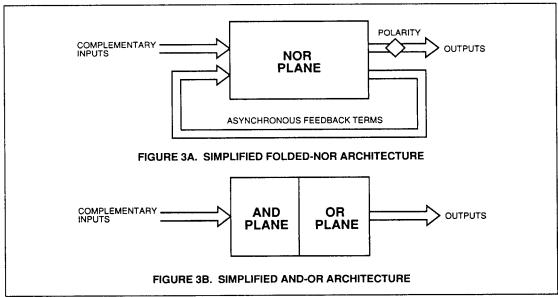

At the heart of the ERASIC XL78C800's multi-level capabilities is the Folded-NOR architecture. This architecture, consisting of a single programmable NOR plane, can generate N internal levels of logic with N passes through the NOR plane. The folded terms, called asynchronous feedback terms, act as both array outputs and inputs, and are used to generate the multiple internal logic levels. The XL78C800 implements all combinatorial logic by using one or more NOR functions along with programmable input and output polarity.

# Advantages of Multi-Level Logic

- increases design flexibility

- increases integration

- allows TTL-type design

- higher PLD utilization

- eliminates unnecessary I/O delays

- enhances design security

# **ERASIC XL78C800 ARCHITECTURE**

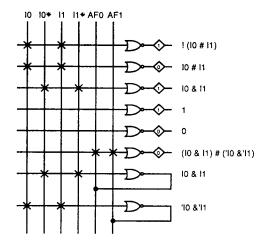

The diagram in Figure 2 illustrates the key elements of the ERASIC XL78C800 architecture. The electrically-erasable NOR array consists of 96 inputs (vertical columns) by 66 terms (horizontal rows). Each term generates a NOR function of its enabled input lines. Inputs can be selectively enabled by programming the E<sup>2</sup>PROM memory cell at the associated intersection. Each term, by selecting proper input and output polarity, can be made to operate logically (via DeMorgan's Theorem) as any 1-Level Boolean function, hence the name 'term,' not 'product term.'

Since each term can generate a generic one-level function, multi-level logic is generated simply by cascading multiple terms. The bottom-most 32 terms of the logic diagram are dedicated to this purpose. These asynchronous feedback terms feed back their output into the array as input, and allow creation of sum-of-products, product-of-sum, or higher-complexity multi-level logic functions.

The asynchronous feedback terms feed back only the NOR sense of their output and do not provide programmable output polarity. This is sufficient since next-level asynchronous logic functions which would require the OR output are easily transformed to eliminate this requirement. This transformation process is performed automatically by EXEL's AdET 1.0 software.

5-7

# Logic Diagram Functionality

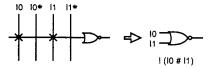

The XL78C800 logic diagram describes logic functionality in a manner similar to conventional PLD logic diagrams. An 'X' drawn at an intersection of term and input lines indicates that the input is enabled for that term. Since the XL78C800 is NOR-based, the inputs represent inputs to a NOR gate.

Addition of Polarity Control Elements (PCEs) and asynchronous feedbacks completes the basic set of array logic operators.

#### I/O MACROCELL ARCHITECTURE

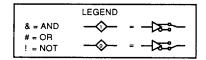

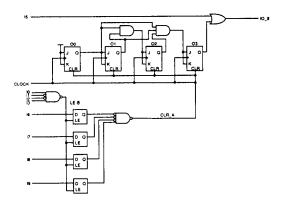

The XL78C800's ten I/O Macrocells form an integral part of the device's logic capabilities. The three terms feeding the I/O Macrocell are called the J, K and O terms. J and K terms feed the JK Flip-Flop, while the O term is used for asynchronous output and/or asynchronous feedback. By providing dual synchronous and asynchronous logic paths, the XL78C800 allows the Filp-Flop to be used even if the I/O pin is used as an asynchronous input or output.

The I/O Macrocell architecture is detailed in Figure 4. In addition to the JK Flip-Flop, its major components are three programmable multiplexers and three polarity control elements. Each Macrocell may be independently configured via six architecture fuses. Three of the fuses set the state of the Polarity Control Elements, which are shown as diamonds. The PCE's act as inverters if their fuses are programmed to a "0," and as non-inverting buffers if programmed to a "1."

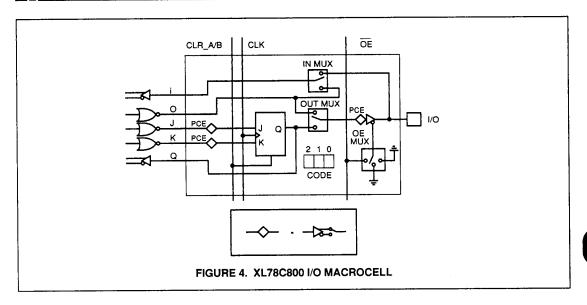

#### CONFIGURING THE I/O MACROCELLS

The remaining three architecture fuses C0, C1 and C2, set the state of the three multiplexers. The Out Mux selects either the O term or the Flip-Flop Q signal for output to the pin. The In Mux selects either the O term or the pin as an array input. The OE Mux selects either the OE input (pin 13), a fixed 0, or a fixed 1 as the output driver enable. The C2, C1 and C0 fuses are logically decoded into the four required Mux control signals, allowing the Macrocells to be configured simply by selecting a 3-bit code. The eight Macrocell configurations and their fuse codes are summarized below and illustrated in Figure 5. Note the availability of the 0 term as an additional asynchronous feedback in many of the configurations.

### I/O Macrocell Fuse Codes

| CONFIGURATION                                                                                                                            | CODE [C2, C1, C0]                                           |

|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| O Term Output O Term 3-State Output Q Output Q 3-State Output Pad Input Pad Input/O Term 3-State C Pad Input/Q 3-State Output No Connect | 011<br>111<br>010<br>110<br>000<br>0utput 101<br>100<br>001 |

The  $\overline{\text{OE}}$  input pin is used as the Output Enable for Macrocell configurations with 3-State Outputs. When asserted,  $\overline{\text{OE}}$  enables the selected outputs; when negated,  $\overline{\text{OE}}$  disables the selected outputs (Hi-Z).  $\overline{\text{OE}}$  has no effect on Macrocells in other configurations.

### JK FLIP-FLOP OPERATION

The JK Flip-Flop is positive-edge triggered. The J and K inputs are driven by the J and K Terms, whose polarity is configured via two polarity control elements. The Q output is unconditionally fed back into the array and may additionally drive the pad via the programmable output driver. All Flip-Flops are initialized at power-up with Q set to 0. In addition, two asynchronous clear terms can be used to clear the Flip-Flops during logic operation. CLR\_A clears the Flip-Flops within Macro-cells 0 through 4, while CLR\_B clears the Flip-Flops within Macrocells 5 through 9.

### JK Flip-Flop Operation

| J | K                     | CLK                   | Q      |                                             |

|---|-----------------------|-----------------------|--------|---------------------------------------------|

| X | ×                     | Х                     | 0      |                                             |

| 0 | 0                     | Ť                     | hold   |                                             |

| 0 | 1                     | 1                     | 0      |                                             |

| 1 | 0                     | 1                     | 1      |                                             |

| 1 | 1                     | 1                     | toggle |                                             |

|   | X<br>0<br>0<br>1<br>1 | X X 0 0 0 1 1 1 0 1 1 |        | X X X 0<br>0 0 ↑ hold<br>0 1 ↑ 0<br>1 0 ↑ 1 |

The JK Flip-Flop can easily emulate either a D or T Flip-Flop. For a D Flip-Flop, the J and K inputs are supplied with the D and  $\overline{D}$  values respectively. Similarly, for a T Flip-Flop, the J and K inputs are both supplied with the T input value. The JK-to-D translation is done automatically in the AdET 1.0 design tool software.

# TERM-CONTROLLED INPUT LATCHES

Inputs I0..I3 and I6..I9 serve as latchable 4-bit input ports. The latching of these ports is controlled by the LE\_A and LE\_B Terms, respectively. When LE is LOW, the latches are transparent and the Q outputs asynchronously follow the D inputs. When LE goes HIGH, data at the D inputs will be retained at the Q outputs until LE returns LOW.

The Latchable Input Ports are designed to provide a "snapshot" capability for asynchronously changing input signals that must be sensed at a particular point in time. The ports contain specially designed latches which quickly resolve the input levels when LE is asserted, providing unconditional stability regardless of the input signal characteristics.

Each LE Term has programmable polarity via a Polarity Control Element. Additionally, if a Latchable Input Port is not required for a particular design, it can be made permanently transparent by programming its LE Term to a fixed LOW. Input latches are not cleared at power-up.

### **SECURITYPLUS SYSTEM**

The XL78C800 incorporates an advanced design security system which offers a high-level of design copy-protection while maintaining 100% programming verification. SecurityPlus can be enabled by setting a special security electron design of the logic configuration from being read out or from being

modified via additional programming. Only a complete erasure will disable the security. In addition, the XL78C800's E<sup>2</sup>PROM technology eliminates the possibility of reverse-engineering via optical inspection, since programming does not create the blown fuses of bipolar fuse-link PLDs.

The SecurityPlus system is not activated until the first power-up following programming of the security bit. This allows the entire device, including the security bit itself, to be read out and verified as long as Vcc is maintained.

#### **REGISTER PRELOAD**

The XL78C800 incorporates an externally controlled preload function. Raising the CLOCK input to 12V causes any currently enabled outputs to be disabled. A preload value can then be placed on the I/O pins and will be preloaded into the JK Filp-Flops in the I/O Macrocells at the next rising edge of the clock. Thereafter, the device will return to normal operation.

### **ERASIC DESIGN TOOLS**

Logic designs using the ERASIC XL78C800 can be created with the AdET 1.0 programmable logic development software. AdET is available from EXEL Microelectronics.

### **ERASIC PROGRAMMING TOOLS**

The ERASIC XL78C800 may be programmed via industrystandard PLD programmers such as those offered by DATA I/O. The Data I/O Generic PLD adapter (Version 3) is required for the XL78C800.

EXEL also offers an ERASIC programming system for IBM-PC, XT, AT and compatibles and Sun Workstations. For further information please contact EXEL directly.

#### LOGIC DESIGN WITH THE ERASIC XL78C800

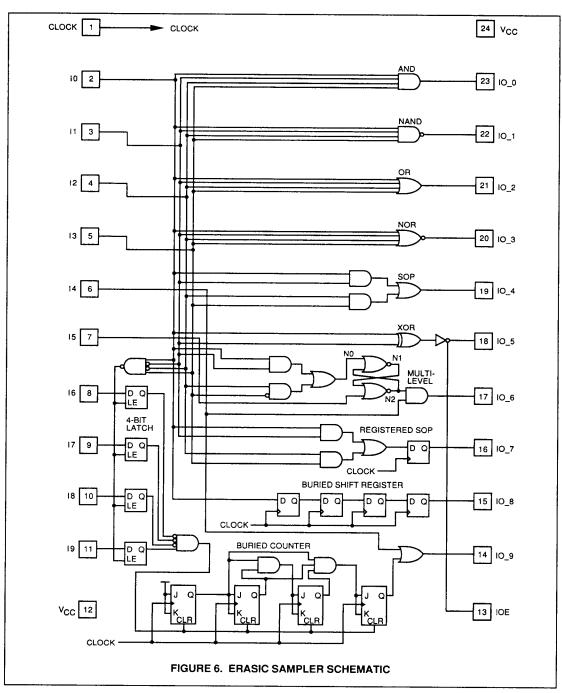

Logic design techniques for the ERASIC XL78C800 are illustrated in the 'ERASIC Sampler' circuit of Figure 6. This single-chip design contains numerous circuits ranging in complexity, and is shown in AdET form, along with schematics for reference.

#### One-Level Logic

The first Sampler circuit is a basic 4-input AND gate, in which IO\_0 is the AND of I0..I3. The AdET notation for this circuit is simply:

Thus, pin 23 (which has been named IO\_0) will be an AND function of pins 2, 3, 4 and 5 (which have been named 10, 11, 12, and 13). That is all that's needed, as polarity and I/O Macrocell architecture are derived automatically in the design software.

For those unfamiliar with AdET notation, the symbology is as follows:

& = AND

# = OR

! = NOT

\$ = XOR

"comment" or /\* comment \*/

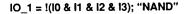

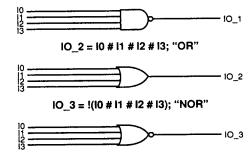

The next three circuits are similar, except they perform the NAND, OR and NOR functions, and are output on I0\_1..I0\_3. Like the AND, these one-level functions require a single term for implementation.

### **Two-Level Logic**

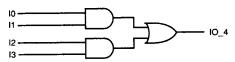

For two-level Sum-of-Products (SOP) functions, one enters equations as with conventional two-level PLDs.

AdET automatically assign asynchronous feedbacks to achieve this two-level function. Feedbacks generate the first-level product terms. These terms are then summed by the 0 term and output to the pin. Much like conventional AND-OR PLDs, the default implementation for complex logic functions in the XL78C800 is minimized sum-of-products. That is, if one defines an output pin as a function of various input pins, and that function is not a one-level

5-12

function (i.e. AND, NAND, OR, NOR), the function will be implemented as a two-level sum-of-products.

A Sum-of-Products function with an active-LOW output (AND-NOR) can be implemented by using the '!'operator on the left-hand side of the equation.

This function is the logical complement of previous activehigh SOP function, being identical in implementation except for a complemented output polarity fuse. The Sampler design uses the active-high SOP function.

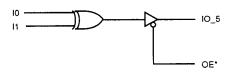

Another useful two-level function is the Exclusive-OR, which is described using the convenient XOR operator:

The XOR function is automatically implemented in sum-of-products form, in this case !IO & II # IO & !I1.

If  $IO_5$  is to be enabled only when the  $\overline{OE}$  pin is brought LOW, and three-stated otherwise, one adds the statement:

Enable

$$IO_5 = \overline{OE}$$

;

IO\_5 is now enabled only when the  $\overline{OE}$  signal is a 1. The fact that the  $\overline{OE}$  pin is active-LOW is handled in the pin declaration by the '!' preceding the ' $\overline{OE}$ ', allowing  $\overline{OE}$  to be treated as an active-HIGH signal. (Note the distinction between pin and signal.) Any or all I/O pins can made three-state and/or bidirectional using this technique.

#### **Multi-Level Logic**

There are many circuits which are impossible or inefficient to implement in two or fewer levels of logic. In many cases, these circuits can be constructed using multi-level logic. Multi-level logic is logic composed of a variety of levels and interconnected in non-sequential fashion. Multi-level logic need not be a specific number of levels (e.g. two-level) and

it need not be interconnected in a pre-determined, sequential fashion (e.g. AND->OR->AND->OR). It is, in effect, random-logic as applied to PLDs.

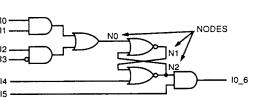

Construction of multi-level logic circuits relies on the concept of nodes. Nodes are like pins, but are buried inside the device. Nodes can be given names, assigned logic functions and then used in the definition of other nodes or pins. This allows familiar PLD logic constructs to be cascaded and or interconnected in virtually any way. In addition, logic signals not needed outside the chip can stay inside, where they avoid delay and pin-usage. As an example, consider the asynchronous Set-Reset latch circuit below. Here, a cross-coupled pair of NORs is cleared when 14 is HIGH, and set when 10 and 11 are HIGH or 12 and 13 are HIGH and LOW respectively. IO\_6 then outputs the latch value, asynchronously conditioned by I5. Describing this circuit requires three nodes, arbitrarily named N0, N1 and N2.

Node names are assigned in the AdET declaration section in a manner similar to pin name assignment. As is evident in the example circuit, multi-level logic is as easy to implement as fixed two-level logic, yet facilitates design of gate array and TTL-type circuits.

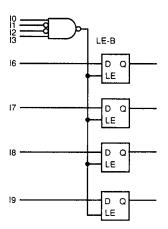

### Input Latches

To demonstrate the use of the input latches, the Sampler adds input latches to inputs I6..I9. The latch-enable term named LE\_B controls the latching, and is set into action via the statement:

LE B = !(10 & !11 & !12 & 13);

Thus, when I0...I3 are in the 1001 state, LE\_B will be LOW and I6...I9 will asynchronously flow through the latches. When they are not in this state, I6...I9 will be latched. LE\_B is used, in effect, as a LOW-going write strobe. Such latch constructs are especially useful when a byte or nibble needs to be latched from a data bus. Input latches are also useful in creating pipelined synchronous systems.

The input latches are defaulted to a fixed non-latching state. They are activated only when the LE terms are defined in the equation section. LE\_A, for instance is not defined in the equation section, making I0..13 unlatched by default.

The latches are used as part of the last Sampler circuit, and are diagrammed again in that circuit.

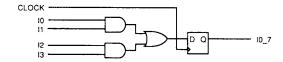

# Synchronous Logic

Synchronous logic design using the XL78C800's JK flipflops is illustrated in three circuits. The first circuit is a registered 2-level logic function, employing an AdET notation identical to that used with conventional registered AND-OR PLDS.

$$IO_7 := (I0 \& I1) # (I2 \& I3);$$

This is the implied synchronous notation of AdET, where the ':=' operator signifies that IO\_7 will be a registered function of the inputs on the right-side of the equation. The design software automatically configures the JK flip-flop as a D type, and sets the I/O Macrocell to the Q-Output configuration.

For reference, all XL78C800 flip-flops are clocked by pin 1 and are positive-edge triggered. They are cleared at power-up, and can be asynchronously cleared thereafter using the CLR\_A or CLR\_B terms. As with the Latch-Enable terms, the Clear terms are defaulted to a fixed inactive state when not assigned equations.

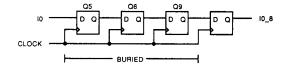

The second synchronous circuit is a 'buried' 4-bit shift register. It is so named because the flip-flops (except the last stage), are buried within the device, not requiring the use of any pins. Again, simple D flip-flops are used, but in this case, because they are buried, node names are used to identify the first three flip-flops. They are named Q5, Q6 and Q9, with the last stage outputting to the pin named IO\_8. Note that because the flip-flop of I/O Macrocell 7 is used in the previous circuit, the shift register goes around that macrocell. Note also that flip-flops Q5..Q9 are cleared only a power-up, since CLR\_B is defaulted to the inactive state.

Q5 := 10; "shift register stage 1" Q6 := Q5; "shift register stage 2" Q9 := Q6; "shift register stage 3"

IO\_8 := Q9; "shift register stage 4, output to pin"

The third and final synchronous circuit is a divide-by-16 circuit, featuring a buried 4-bit synchronous up-counter with an asynchronous 'force-HIGH' on the output. This circuit generates a frequency 1/16th that of the system clock (pin 1) on pin 14. The design uses JK flip-flops, which are assigned nodes names Q0 through Q3. The flip-flops are asynchronously cleared at power-up, or when the 4-bit latch of I6..I9 contains the nibble '0001.'

| [Q0.J] :: | = 1;            | "counter stage 1" |

|-----------|-----------------|-------------------|

| [Q0.K] :: | = 1;            | •                 |

| [Q1.J] :: | = Q0;           | "counter stage 2" |

| [Q1.K] :: | = Q0;           | _                 |

| [Q2.J] :: | = Q0 & Q1;      | "counter stage 3" |

| [Q2.K]:   | = Q0 & Q1;      | _                 |

| [Q3.J] :: | = Q0 & Q1 & Q2; | "counter stage 4" |

| [Q3.K]::  | = Q0 & Q1 & Q2; |                   |

$IO_9 = Q3 # 15;$   $Cir_A = !!6 & !!7 & !!8 & !9;$

# "OR gate to output pin

The J and K nodes of the flip-flop are identified using the .J and .K suffixes to the node name. Conceptually the JK flip-flop is given a node name, and then the J and K inputs of the flip-flop are individually identified via the suffixes. Even though J and K inputs themselves are not synchronous, AdET syntax requires them to be assigned functions using the ':= ' operator. If the flip-flop node name is given an equation directly (no suffixes), the flip-flop will be implemented as the default D type, as in the previous shift-register circuit.

#### Adet Design File Description

As with any computer language, the AdET language requires certain constructs to occur in certain places. These constructs are highlighted in the ERASIC Sampler AdET design file (Figure 8). At the top are the module statement, a design title, the device name (what the JEDEC file will be called), and the device type. Following that are the pin and node name assignments. Each pin and node is assigned a unique, unchanging number. (Pin and node numbers for the ERASIC XL78C800 are detailed in Figure 7.) These numbers are then used to give the various entities names particular to the user-design. (In the Sampler, for instance, pin 1 is given the name 'Clock,' while node 49 is given the name 'NO.') Thereafter comes the EQUATION section, with the various Sampler circuits described, followed by the keyword END, completing the design.

### **Additional AdET Techniques**

In addition to the equation-oriented design of the Sampler, AdET offers high-level constructs such as truth tables and state machines. With these constructs, only the 'what' of the design need be described, with the 'how' left to the software. High-level constructs allow logic functions to be treated as black boxes, with the derivation of the boxes' internal gate-level implementations left to AdET. The ERASIC XL78C800 fully supports all AdET high-level constructs. Additionally, it enhances the usefulness of such constructs, since it allows more of them to be placed on the same PLD, and lets them be interconnected in ways not before possible. More information on using high-level AdET design techniques is contained in the AdET manual.

# Flip-Flops

Q0,Q1,Q2,Q3,Q4 node 47,45,43,41,39; Q5,Q6,Q7,Q8,Q9 node 37,35,33,31,29;

## Asynchronous Feedback Terms

AF00,AF01,AF02,AF03 node 49,50,51,52; AF04,AF05,AF06,AF07 node 53,54,55,56; AF08,AF09,AF10,AF11 node 57,58,59,60; AF12,AF13,AF14,AF15 node 61,62,63,64; AF16,AF17,AF18,AF19 node 65,66,67,68; 69,70,71,72; AF20,AF21,AF22,AF23 node AF24,AF25,AF26,AF27 node 73,74,75,76; 77.78.79.80: AF28,AF29,AF30,AF31 node

#### **Control Terms**

CLR\_A,CLR\_B node 27,28; LE A,LE\_B node 25,26;

**Note:** Flip-Flops Q0...Q9 are in Macrocells 0..9, respectively. Asynchronous feedback term AF00 is the topmost. AF31 the bottom-most.

FIGURE 7. XL78C800 INTERNAL NODE IDENTIFICATION IN AdET

```

module ERASIC_Sampler:

title 'ERASIC Sampler Design

Design uses one 780800 and contains various circuits which

illustrate ABEL design techniques.

Erich Goetting

EXEL Microelectronics, Inc.

Sampler device 'XL78C800';

"pin declarations"

Clock

pin 1:

10,11,12,13

14,15

14,17,18,19

pin 2,3,4,5;

pin 4,7;

pin 8,4,10,11;

"latchable inouts"

"latchable inputs"

10_0, 10_1

10_2, 10_3

10_4, 10_5

10_4, 10_7

10_8, 10_9

pin 23,22;

pin 21,20;

pin 19,18;

pin 17,14;

pin 15,14;

"input/output pins"

!OE

pin 13:

"putput enable"

"node declarations"

00,01,02,03,04

node 47,45,43,41,39; "flip-flops"

node 37,35,33,31,29;

NO,N1,N2

Clr_A,Clr_B

LE_A,LE_B

node 49,50,51; "for multi-level circuit"

node 27,28; "flip-flop clear terms"

node 25,26; "latch enable terms"

equations

"one-level circuits"

10_0 - 10 & 11 & 12 & 13 ;

10_1 = 1(10 & 11 & 12 & 13);

"NAND"

10_2 - 10 + 11 + 12 + 13 ;

"OR"

10_3 = 111 = 131;

"NOR"

"two-level circuits"

10_4 = (10 & 11) = (12 & 13); "Sum-of-Products"

10_5 = 10 % 11;

Enable 10_5 = 0E;

"XOR"

"make XOR output three-state

"multi-level sissuit"

NO = ([0 & [1] # ([2 & ([3)];

NI = ((NO # N2);

NZ = (([4 # N1);

10_4 = (3 & NZ;

"SR latch Set Function"

"SR latch NOR gate 1"

"SR latch NOR gate 2"

"input latches"

LE_8 - 1(10 & !!! & !!2 & !3);

"synchronous circuits"

"registered 2-level function"

10_7 := (10 & 11) # (72 & 13);

"buried 4-bit shift register"

" shift register stage !"

" shift register stage 2"

" shift register stage 3"

" shift register stage 4, output to pin"

05 := 10;

06 := 05;

09 := 06;

10_8 := 09;

"divide-by-16 circuit"

[00.X] := 1;

[00.K] := 1;

[00.K] := 00;

[01.K] := 00;

[02.X] := 00 & 01;

[02.K] := 00 & 01 & 02;

[03.K] := 00 & 01 & 02;

[03.K] := 00 & 01 & 02;

"counter stage 1"

"counter stage 2"

"counter stage 3"

"Counter stace 4"

ID_9 = 03 0 IS; "OR gate to output pin" Cir_A = 116 & 117 & 110 & 19;

FIGURE 8. ERASIC SAMPLER AdET DESIGN FILE

```

5-16

#### XL78C800 PROGRAMMING

The XL78C800's CMOS E<sup>2</sup>PROM technology provides the highest level of PLD programming features currently available. Electrically-erasable technology offers 100% testability and high-speed reprogrammability in plastic packages. As a result, users can perform a single incoming test procedure on these devices, regardless of their final logic configuration.

The XL78C800 employs a special ruggedized E<sup>2</sup>PROM cell configuration, allowing it to be reprogrammed a minimum of 10,000 times, with a logic retention period of 10 years.

The XL78C800 can be erased, programmed, and verified in less than five seconds. Since all pins are used for logic functions, the XL78C800 uses the presence of Vpp on pin 6 (PMODE) to place the device into programming mode. Once in this mode, erase, programming, and verify operations are controlled via standard TTL-level signals.

FIGURE 9. XL78C800 PIN CONFIGURATION IN PROGRAMMING MODE

#### PROGRAMMING MODE PIN FUNCTIONALITY

| Name         | Туре | Pin(s)    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|--------------|------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PMODE        | ı    | 6         | Programming Mode. Raising this input to VPP volts places the device in the programming mode, thereby activating the pin functionality described below. If this input is below 6.0 volts, the device is in the logic mode.                                                                                                                                                                                                                                                                                      |  |  |

| A0A3<br>A4A7 | 1    | 25<br>811 | Address Inputs. Addresses used to select both the column and row address of all programmable cells.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| CAS          | 4    | 14        | olumn Address Strobe. When asserted, this pin latches the current A0-A7 values into the Column ddress Register, thereby selecting the column to be programmed or read. It must be asserted for the uration of any operation requiring a specific column address. When negated, CAS causes the output the Column Address Register to asynchronously follow the A0-A7 values.                                                                                                                                    |  |  |

| DS           | ı    | 22        | Data Strobe. A LOW-HIGH-LOW transition of this pin latches the value of the Din pin into the Row Data Latch whose address is concurrently specified on A0-A7.                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Din          | ı    | 23        | Data Input. Data input for device programming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Dout         | 0    | 13        | Data Output. Data output for device programming verification. Valid except when WR is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| ERASE        | ŧ    | 1         | Write mode select and data latch clear. This pin has two functions. The first function is to condition the operation of the WR pin. If this pin is HIGH while WR is asserted, the chip will be unconditionally erased. If this pin is LOW while the WR pin is asserted, the data stored in the 66 Data Latches is written into the currently specified column. The second function is to clear the data latches. Whenever this pin is brought HIGH all 66 data latches will be cleared to the logic "0" state. |  |  |

| WR           | ı    | 21        | Write. A LOW-HIGH-LOW pulse on this input causes the E <sup>2</sup> cells to be written, as conditioned by the state of the ERASE pin,                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Vcc          | 1    | 24        | +5V Power Supply. Vcc must be supplied during programming mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| GND          | ı    | 12        | Signal and Power Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

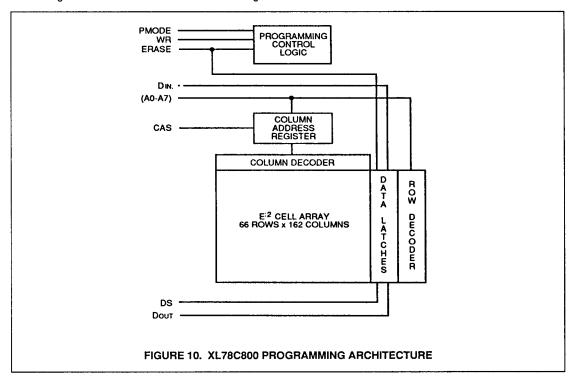

#### XL78C800 PROGRAMMING-MODE ARCHITECTURE

Referring to Figure 10, the primary programming-mode feature of the XL78C800 is the E<sup>2</sup> cell array. This single array stores all information defining the logic configuration of the device. The array is organized as a matrix of 66 rows by 162 columns. The 66 rows correspond to the 66 Terms in the array. The 162 columns are comprised of the 96 array input lines of the logic diagram, the architecture column, and 65 hidden 'don't care' columns. The 'don't care' columns do not appear in the logic diagram.

The address inputs,  $A_0$ - $A_7$ , are used to specify the unique Column-Row address pair of each  $E^2$  cell. Cells are accessed on a column-major basis. The Column Address is applied first and latched into the Column Address Register via the CAS input. The Column Address Register, in turn, selects one of the 162 columns via the Column Decoder. Following Column Address latching, Row Addresses applied to  $A_0$ - $A_7$  will asynchronously select  $E^2$  cell addresses within the selected column.

Writing to the  $E^2$  cells of a particular column is accomplished by first latching the Column Address, then strobing data into the 66 Data Latches, and then transferring the data values to the  $E^2$  cells in the column. The Data Latches store a single bit for each of the 66-rows. Before writing new

data, the Data Latches must be cleared by strobing the ERASE input. This action sets all latches to a logic "0." Each latch is written by applying the data to the Din input, applying its Row Address to Ao-A7 and strobing the DS input. The Data Latches can be written in any order. Data Latches not written will default to a "0." Once a Data Latch is set to a "1," it can only be reset to a "0" via the ERASE strobe. When all 66 latches contain the desired data, the data is written to the E² cells of the selected column by pulsing the WR pin while holding ERASE at a logic "0." Columns having identical logic values for all 66 Data Latches may be written without re-entering the Data Latch values.

The 65 'don't care' columns are programmed with the NAND of the corresponding input columns, as defined in the Input Address section. A row in a don't care column is programmed to a "0" if all corresponding inputs are programmed to a "1," the logical don't care state.

Reading of the array is accomplished in a manner similar to writing. First, the ERASE pin must be strobed HIGH to enable readout. The column address is then applied and latched. Thereafter, the state of any E<sup>2</sup> cell within the selected column is presented asynchronously on the Dout pin.

5-18

\$8A

# XL78C800 EE-FUSE ADDRESSES

# **Input Addresses**

Input Name -> Column Address (HEX)

| CLK CLK - 10 10 10 10 10 10 10 11 11 11 11 11 11 | \$33B \$4433670124567AB4567ABBEF89A89CF23CDEDEDEDEF3067012 | 5 *  <br> 6 *  <br> 7 7'  <br> 7 7 7 7 7 8  <br> 8 *  <br> 8 *  <br> 8 *  <br> 9 * | \$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$ | AFO \$40 AF0— \$41 AF1 \$3A AF1— \$3B AF2— \$39 AF3 \$34 AF3— \$35 AF4 \$2E AF4— \$2F AF5— \$2D AF6— \$29 AF7— \$23 AF8— \$21 AF9— \$1C AF9— \$1D AF10— \$17 AF11— \$15 AF12— \$11 AF13— \$0A AF13— \$08 AF14— \$09 AF14— \$09 AF15— \$05 | AF16<br>AF17<br>AF17<br>AF18<br>AF19<br>AF20<br>AF21<br>AF21<br>AF22<br>AF23<br>AF24<br>AF25<br>AF26<br>AF27<br>AF27<br>AF28<br>AF29<br>AF30<br>AF30<br>AF31<br>AF31<br>OE |

|--------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

\$8B \$88 \$89 \$84 \$85 \$96 \$97 0 \$94 \$95 \$90 \$91 \$A2 \$A3 3 \$AO \$A1 \$9C \$9D \$AE \$AF \$AC \$AD \$A8 \$A9 \$BA 8 \$BB \$B8 9 \$B9 \$B4 \$B5 \$C0 \$C1 \$BD \$BC

\$BE

PIDCTS

Legend: XX is true input, XX\* is false input, XX— is don't care input.

#### **Term Addresses**

Term Name ->Row Address (HEX)

| CLR A | \$1F | O5    | \$41 | AF0   | \$14 | AF17 | \$3B |

|-------|------|-------|------|-------|------|------|------|

| LE_Ā  | \$20 | J5    | \$2C | AF1   | \$13 | AF18 | \$3A |

| 00    | \$04 | K5    | \$2B | AF2   | \$12 | AF19 | \$39 |

| J0    | \$1D | O6    | \$40 | AF3   | \$11 | AF20 | \$38 |

| K0    | \$1E | J6    | \$2A | AF4   | \$10 | AF21 | \$37 |

| O1    | \$03 | K6    | \$29 | AF5   | \$0F | AF22 | \$36 |

| J1    | \$1B | 07    | \$3F | AF6   | \$0E | AF23 | \$35 |

| K1    | \$1C | J7    | \$28 | AF7   | \$0D | AF24 | \$34 |

| O2    | \$02 | K7    | \$27 | AF8   | \$0C | AF25 | \$33 |

| J2    | \$19 | O8    | \$3E | AF9   | \$0B | AF26 | \$32 |

| K2    | \$1A | J8    | \$26 | AF10  | \$0A | AF27 | \$31 |

| O3    | \$01 | K8    | \$25 | AF11  | \$09 | AF28 | \$30 |

| J3    | \$17 | O9    | \$3D | AF12  | \$08 | AF29 | \$2F |

| K3    | \$18 | J9    | \$24 | AF13  | \$07 | AF30 | \$2E |

| O4    | \$00 | K9    | \$23 | AF14  | \$06 | AF31 | \$2D |

| J4    | \$15 | LE_B  | \$21 | AF1 5 | \$05 |      |      |

| K4    | \$16 | CLR_B | \$22 | AF16  | \$3C |      |      |

### ARCHITECTURE FUSE ADDRESSES

All Architecture Information is accessed via Columns \$D0 and \$D1, with \$D0 containing the TRUE information and \$D1 containing the complement information. The row addresses of the architecture and polarity bits within these columns are given below.

| O,J,K Polarity, | C2,C1,C0 for Mcell 0 | \$04,\$1D,\$IE,          | \$13,\$12,\$11 |

|-----------------|----------------------|--------------------------|----------------|

| O,J,K Polarity, | C2,C1,C0 for Mcell 1 | \$03,\$1B,\$1C,          | \$10,\$0F,\$0E |

| O,J,K Polarity, | C2,C1,C0 for Mcell 2 | \$02,\$19,\$1 <b>A</b> , | \$0D,\$0C,\$0B |

| O,J,K Polarity, | C2,C1,C0 for Mcell 3 | \$01,\$17,\$18,          | \$0A,\$09,\$08 |

| O,J,K Polarity, | C2,C1,C0 for Mcell 4 | \$00,\$15,\$16,          | \$07,\$06,\$05 |

| O,J,K Polarity, | C2,C1,C0 for Mcell 5 | \$41,\$2C,\$2B,          | \$3C,\$3B,\$3A |

| O,J,K Polarity, | C2,C1,C0 for Mcell 6 | \$40,\$2A,\$29,          | \$39,\$38,\$37 |

| O,J,K Polarity, | C2,C1,C0 for Mcell 7 | \$3F,\$28,\$27,          | \$36,\$35,\$34 |

| O,J,K Polarity, | C2,C1,C0 for Mcell 8 | \$3E,\$26,\$25,          | \$33,\$32,\$31 |

| O,J,K Polarity, | C2,C1,C0 for Mcell 9 | \$3D,\$24,\$23,          | \$30,\$2F,\$2E |

| CLR_A,CLR_B,    | LE_A,LE_B            | \$1F,\$22,               | \$20,\$21      |

|                 |                      |                          |                |

Security Fuse \$2D (column \$00 only)

#### Note

[1] No E2 Cells are present at the following silicon addresses, and therefore these addresses will always read as a "1":

- 1. Column: D0 Row: 14

- 2. Column: D1 Row: 14

- 3. Column: D1 Row: 2D

### PROGRAMMING PROCEDURES

Programming and verification of the XL78C800 can be accomplished using the following procedures:

- 1. Enter Programming Mode

- 2. Chip Erase

- 3. Chip-Erase Verify

- 4. Column Write

- 5. Column Read (verification)

- 6. Exit Programming Mode

All procedures except 'Enter Programming Mode' must be performed while in Programming Mode. All Programming Mode control inputs (i.e. ERASE, CAS, DS, and WR) are defaulted to a negated state (OV) unless otherwise stated. The term 'strobe' is used to signify a negated-asserted-negated transition of a pin which is in the negated state. Unless otherwise stated, strobe is 10 microseconds in duration.

## **Enter Programming Mode**

The chip is put into programming mode as follows:

- 1. Vcc = 4.75 to 5.25V

- 2. Delay = tpmp

- 3. PMODE = VPP

- 4. Delay = tcpp

## Chip Erase

Before the chip can be programmed with a new logic configuration, it must be erased to return all E<sup>2</sup> cells to their unprogrammed state. The chip is erased as follows:

- 1. ERASE = VIH

- 2. Strobe WR for 1/2\*twse

- 3. Exit Programming Mode

- 4. Delay trec

- 5. Enter Programming Mode

- 6. ERASE = VIH

- 7. Strobe WR for 1/2\*twee

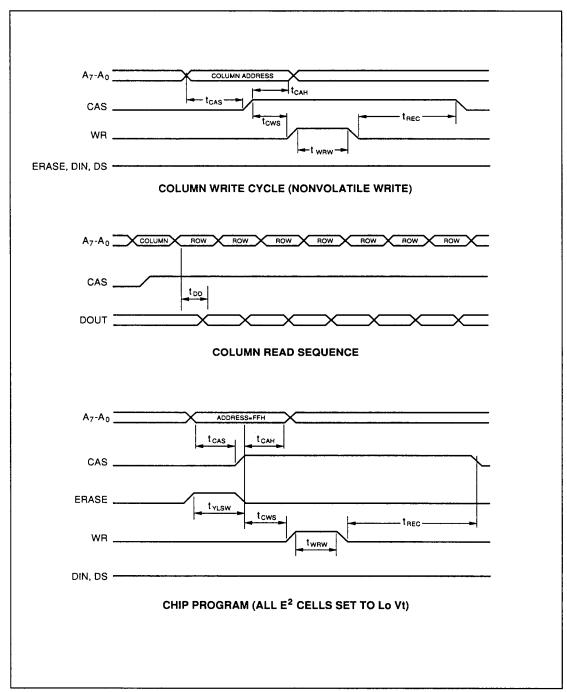

#### Chip-Erase Verify

The All-Ones condition of an erased XL78C800 may be verified as follows:

- Set address [A7:AO] = FF (hex)

- 2. Strobe Erase

- 3. Delay toed

- 4. If Dout = ViH, then device is erased

#### Column Write

The Erasic device is programmed by a sequence of write operations. All columns must be correctly programmed for

the device to function correctly. Each of the 162 columns in the device is written as follows:

- 1 . Set address [A7: A0] = Column Address

- Assert CAS to latch address into Column Address Register

- Strobe ERASE for tyLsw to clear Data Latches

—this may be done concurrently with Step 2.

- 4. For each Row from 00 (hex) to 41 (hex):

- a. Set address [A7:A0] = Row Address

- b. Din = Data

- c. Strobe DS to latch data

- 5. Strobe WR for twnw

- 6. Delay trec

- 7. Negate CAS

#### Column Read

Programming of the device should be verified to assure proper device operation. All columns must be programmed before verification. Each of the 162 columns in the chip is verified as follows:

- 1. Set address [A7:A0] = Column Address

- Assert CAS to latch address into Column Address Register

- 3. Strobe ERASE

- 4. For each row from 00 (hex) to 41 (hex):

- a Set address [A7:A0] = Row Address

- b. Delay too

- c. Read Dout

- d. Verify if Dout = Data

# **Exit Programming Mode**

Following Chip Erase, Chip Programming and Verification, the chip must be powered down in the following sequence.

- ALL Control and Address pins brought to 0V This excludes PMODE, Vcc and OE (see Note)

- 2. PMODE = 0V

- 3. Delay tems

- 4. OE, Vcc = 0V

At all subsequent power-ups, all logic, architecture and security features will be activated.

NOTE: When PMODE is made inactive, the I/O Macrocells will again drive the pins in accordance with the configuration present at power up. In accordance with the programming procedures specified here, this will be the completely erased configuration, in which all I/O's will be in the 3-state output mode controlled by the  $\overline{OE}$  pin.

Logic contention should be avoided at the D<sub>IN</sub>, D<sub>S</sub>, WR, and CAS during the period after which PMODE has been deactivated and Vcc is still active.

# XL78C800 JEDEC FILE INFORMATION

Figure 11 illustrates a sample JEDEC Fuse Map for XL78C800. Each row in the Fuse Map corresponds to a Term in the logic diagram. The first 66 rows correspond to the main NOR array, with each row representing a Term. The total number of fuses in this section is 66 x 96 = 6336 fuses, with JEDEC addresses ranging from 0000 to 6335.

The 65 Architecture Fuses begin at fuse number 6336. Each I/O Macrocell is described by 6 Architecture Fuses (O polarity, J Polarity, K Polarity, C2, C1, and C0). Thereafter, four fuses describe the CLR\_B, LE\_A and LE\_B Polarity control. The optional Security Fuse feature may be described in the "G" field.

| 111011 | (O, J, and K Polarity, C2, C1, C0 for I/O Macrocell 0) |

|--------|--------------------------------------------------------|

| :      |                                                        |

| :      |                                                        |

| 001011 | (O, J, and K Polarity, C2, C1, C0 for I/O Macrocell 9) |

| 1000*  | (CLR_A, CLR_B, LE_A, and LE_B<br>Polarity)             |

|        |                                                        |

G0\* (Security Enabled)

Architecture Fuse Detail

```

AdET 1.00 - JEDEC 3

JEDEC File For: x178c800

30-Oct-90 11:54 AM

i Design uses one 78C800 and contains various

I circuits which illustrate ABEL design techniques

1 Gabriel Jordan, RXEL Microelectropics

N Number of pins*

N Number of fuses*

OP6400*

N Fuse RAM Data*

L0384

DARO.

L0672

1.1056

1 1248

L1440

1.1632

1.1824

1.2016

L2112

1.2208

1.2304

L2400

L2496

L2592

L2688

1.2880

1 3072

1.3264

1 3456

1.3552

L3936

1.4032

L4224

1.4512

1.4704

L4896

L4992

1.5184

1.5376

1.5568

1.5760

1.5952

L6048

1.6144

1.6240

1.6336

111011*

1.6342

000011*

011011*

1.6354

111011*

1.6360

1.6366

0011111*

1.6372

1010111

1.6378

101010*

1.6390 001011*

1.6396 1000*

```

PLD 5 P'DCTS

FIGURE 11. SAMPLE JEDEC FUSE MAP

A0B2

### **ELECTRICAL SPECIFICATIONS**

# **ABSOLUTE MAXIMUM RATINGS (Notes 1, 2)**

| Ambient Temperature Under Bias                  | 55°C to +125°C  |

|-------------------------------------------------|-----------------|

| Storage Temperature                             | -65°C to +150°C |

| Voltage on Any Pin (Except Pins 1, 6)* (Note 2) | -0.5V to +7.0V  |

| Programming Mode Pin Voltage (Pin 6)*           | 0.5V to +21.25V |

| Preload Voltage (Pin 1)*                        | -0.5V to +13.0V |

| DC Output Current                               | 50mA            |

| *With respect to ground                         |                 |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions indicated in the operational sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS (Notes 3, 8, 10)

$T_A = 0^{\circ}C \text{ to } +70^{\circ}C, V_{CC} = 5.0V \pm 5\%$

|        |                                   | Test                                                      | Device   |       |          |          |          |

|--------|-----------------------------------|-----------------------------------------------------------|----------|-------|----------|----------|----------|

| Symbol | Parameter                         | Condition                                                 | Grades   | Min.  | Тур.     | Max.     | Unit     |

| VIL    | Input Low Voltage                 |                                                           |          | -0.5  |          | 0.8      | V        |

| VIH    | Input High Voltage                |                                                           |          | 2.0   |          | Vcc      | ٧        |

| lOL    | Output Low Current                | VOL = 0.5V                                                |          | 12    | 16       |          | mA       |

| ЮН     | Output High Current               | VOH = 2.4V                                                |          | -4    | -8       |          | mA       |

| ЮН     | Input Leakage Current-High        | VIN = VCC                                                 |          |       |          | 10       | μА       |

| IJĽ    | Input Leakage Current-Low         | VIN = 0V                                                  | -        |       |          | -10      | μА       |

| 1LO    | Output Leakage Current, 3-state   | VO = 0 to VCC                                             |          | -10   |          | 10       | μA       |

| ICC    | Power Supply Current              | VIN < 0.2V or<br>VIN > (VCC-0.2V)<br>fCLK = 0 Hz to 10MHz | -35, -45 |       | 17<br>15 | 35<br>30 | mA<br>mA |

| VPP    | Programming Mode Voltage on PMode | (Pin 6)                                                   |          | 20.75 | 21       | 21.25    | ٧        |

| lpp    | Programming Supply Current        |                                                           |          |       |          | 1.0      | mA       |

| VPL    | Preload Mode Voltage on Pin 1     |                                                           |          | 11    | 12       | 13       | ٧        |

| IPL    | Preload Supply Current            |                                                           |          |       |          | 1.0      | mA       |

# CAPACITANCE

|        |                       |      | tic DIP/Pi<br>Package | LCC  | _    | eramic Si<br>zed Pack |      |      |

|--------|-----------------------|------|-----------------------|------|------|-----------------------|------|------|

| Symbol | Parameter             | Min. | Тур.                  | Max. | Min. | Тур.                  | Max. | Unit |

| CIN    | Input Pin Capacitance |      | 4                     | 6    |      | 5                     | 7    | рF   |

| CID    | I/O Pin Capacitance   |      | 4                     | 6    |      | 5                     | 7    | рF   |

| CCLK   | Clock Pin Capacitance |      | 5                     | 7    |      | 6                     | 8    | pF   |

XL78C800-35

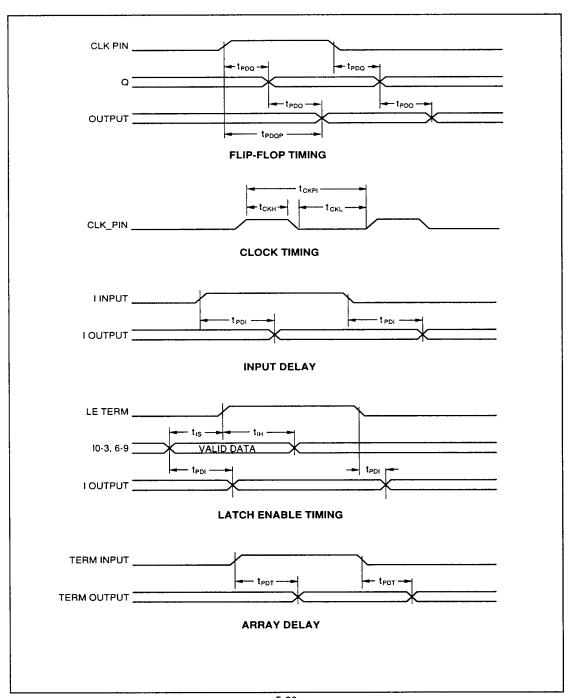

AC ELECTRICAL CHARACTERISTICS-LOGIC MODE (Notes 4, 5, 6)

|        | Parameter                                                                       | LIMITS |      |      |      |  |

|--------|---------------------------------------------------------------------------------|--------|------|------|------|--|

| Symbol |                                                                                 | Min.   | Тур. | Max. | Unit |  |

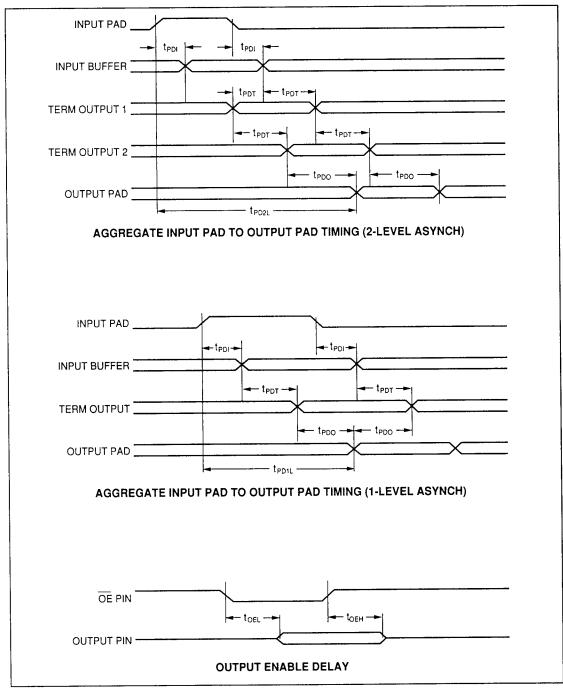

| AGGRE  | GATE TIMINGS                                                                    |        |      |      |      |  |

| tPD1L  | Input Pad to Output Pad Delay, One Level Asynchronous (tPDI + tPDT + tPDO)      |        |      | 35   | ns   |  |

| tPD2L  | Input Pad to Output Pad Delay, Two Level Asynchronous<br>(IPDI + 2*IPDT + IPDO) |        |      | 55   | ns   |  |

| tOEL   | OE* Pin LOW to Output LOW-Z                                                     |        |      | 15   | ns   |  |

| tOEH   | OE* Pin HIGH to Output HIGH-Z                                                   |        |      | 15   | ns   |  |

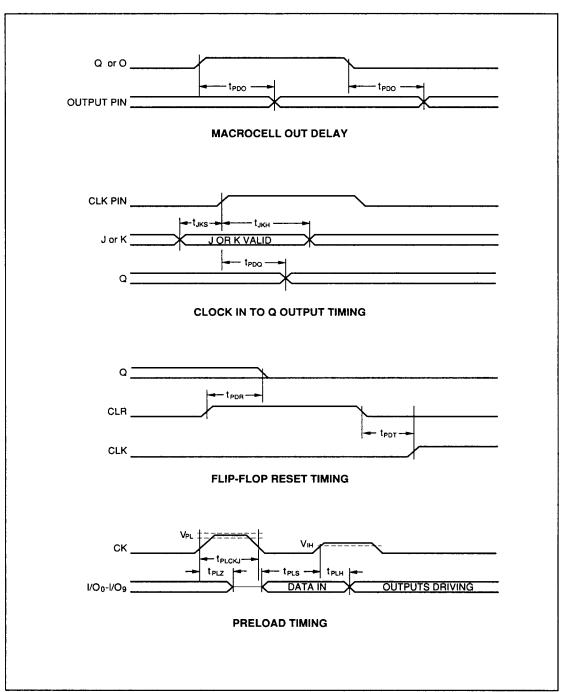

| tPDQP  | CLK Input Pad to Q Output at I/O Pad (IPDQ + IPDO)                              |        |      | 25   | ns   |  |

| tCKL   | Clock LOW Time                                                                  | 20     |      |      | ns   |  |

| tCKH   | Clock HIGH Time                                                                 | 20     |      |      | ns   |  |

| tCKRF  | Clock Rise and Fall Time                                                        |        |      | 5    | ns   |  |

| tCKP1  | Clock Period (1 Level State Machine)                                            | 50     |      |      | ns   |  |

| tCLK1  | Clock Frequency (1 Level State Machine)                                         |        |      | 20.0 | ns   |  |

| tCKP2  | Clock Period (2 Level State Machine)                                            | 70     |      |      | ns   |  |

| ICLK2  | Clock Frequency (2 Level State Machine)                                         |        |      | 14.2 | ns   |  |

PLD **5** P'DCTS

# **COMPONENT TIMINGS**

# Input Timing

| tPDI | Input Buffer or Transparent Latch (LE negated) Delay |  | 5 | ns |

|------|------------------------------------------------------|--|---|----|

| tis  | Latch Input Set-up Time to LE Term Asserted          |  | 5 | ns |

| tιн  | Latch Input Hold Time from LE Term Asserted          |  | 0 | ns |

# **Term Timing**

| I toot | Term Input to Output Delay |     |   | ا مم |      |

|--------|----------------------------|-----|---|------|------|

| I tPDT | Term Input to Output Delay | l t | 4 | 20   | ns i |

|        |                            |     |   |      |      |

|        |                            |     |   |      |      |

# I/O Macrocell Timing

| tPDIO . | Input Buffer Delay                          |    | 5  | ns |

|---------|---------------------------------------------|----|----|----|

| †PDO    | Output Buffer Delay                         |    | 10 | ns |

| tiks    | J and K Input Set-up Time to Clock Pin HIGH |    | 5  | ns |

| tJKH    | J and K Input Hold Time from Clock Pin HIGH | 0  | `  | ns |

| tPDQ    | Q Output Delay from Clock Pin HIGH          |    | 15 | ns |

| tPDR    | CLR Term Asserted to Q≃O Delay              |    | 5  | ns |

| tar     | CLR Term Negated Before Clock Pin HIGH      |    | 5  | ns |

| tCLR    | Clear Term Pulse Width (Note 9)             | 20 |    | ns |

# **Register Preload Timing**

| †PLÇKH | Preload Clock (Clock = VPL) HIGH Time             | 100 |    | ns |

|--------|---------------------------------------------------|-----|----|----|

| tPLZ   | Preload Clock HIGH to Outputs in HIGH-Z           |     | 50 | ns |

| tPLS   | Preload Data on I/O Pin Set-up Time to Clock HIGH | 20  |    | ns |

| tPLH   | Preload Data on I/O Pin Hold Time from Clock HIGH | 5   | 15 | ns |

# Power-up Timing (Note 7)

|        |                              | <br> |   |      |

|--------|------------------------------|------|---|------|

| tINIT  | Power-up Initialization Time |      | 5 | ms   |

| -11411 |                              |      |   | 1113 |

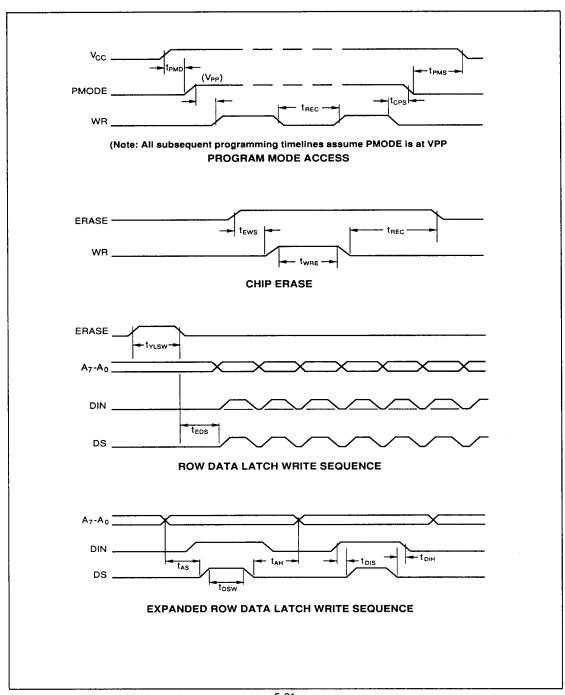

# AC ELECTRICAL CHARACTERISTICS-PROGRAMMING MODE (Note 8)

|        |           | XL78C800<br>LIMITS |      |      |      |

|--------|-----------|--------------------|------|------|------|

| Symbol | Parameter | Min.               | Тур. | Max. | Unit |

# **Program Mode Access**

| tPMD | VCC Active to PMODE Active             | 5   | ms |

|------|----------------------------------------|-----|----|

| tCPD | PMODE Active to any Control Pin Active | 5   | ms |

| tREC | WR LOW to Any Input Change             | 1 1 | ms |

| tCPS | Control Pin Deactive to PMODE Deactive | 1   | ms |

| tPMS | PMODE Deactive to VCC Deactive         | 1   | ms |

# **Chip Erase**

| tEWS | ERASE Set-up Time to WR Rising Edge | 200 |     | ns |

|------|-------------------------------------|-----|-----|----|

| tDED | Chip Erase Verify to Output Valid   |     | 200 | ns |

| tWRE | WR Pulse Width for Chip Erase       | 100 |     | ms |

| TREC | WR LOW to Any Input Change          | 1   |     | ms |

# Row Data Latch Write Sequence

| tylsw | ERASE Pulse Width for Clearing Data Latches | 100 | ns |

|-------|---------------------------------------------|-----|----|

| tEDS  | ERASE LOW to DS HIGH                        | 100 | ns |

| tAS   | Row Address Set-up Time to DS Rising Edge   | 100 | ns |

| †AH   | Row Address Hold Time from DS Falling Edge  | 100 | ns |

| tDIS  | DIN Set-up Time to DS Pulse Rising Edge     | 100 | ns |

| †DIH  | DIN Hold Time from DS Pulse Falling Edge    | 100 | ns |

| tDSW  | DS Pulse Width                              | 100 | ns |

# Column Write Cycle

| tCAS | Column Address Set-up Time to CAS Rising Edge | 100 |  | ns |

|------|-----------------------------------------------|-----|--|----|

| tcws | CAS Set-up Time to WR Rising Edge             | 100 |  | ns |

| twrw | WR Pulse Width for Program                    | 10  |  | ms |

| tREC | WR LOW to Any Input Change                    | 1   |  | ms |

## Column Read Sequence

|        |                                    | 1 1 | 000 | 1 1    |

|--------|------------------------------------|-----|-----|--------|

| I tob  | Data Output Valid from Row Address | 1 1 | 200 | l ns l |

| יטטי ו | Data Colpor rane non-rich riches   | 1 1 |     | 1 1    |

|        |                                    |     |     |        |

# **Power-up Timing**

| tini   | т   | Power-up Init Time |      | ] | 5 | ms |

|--------|-----|--------------------|------|---|---|----|

| -11.41 | ' i | <b>-</b>           | <br> |   |   |    |

#### NOTES:

- Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. These are stress ratings

only and functional operation of the device at these or any other conditions above those indicated in the Electrical Characteristics section of

this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- This product includes circuitry specifically designed for the protection of its internal devices from damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying any voltage larger than the rated maxima.

- All voltages are referenced to ground (GND). Parameters are valid over the specified temperature and operating supply ranges. Typical values are at 25°C, typical supply voltage and typical processing parameters.

- 4. The Aggregate Timing data specifies input pad to output pad delay paths for common end-user designs. Timing is characterized independently for the Input, Term, and I/O Macrocell circuits to allow the timing characteristics of arbitrary user-circuits to be ascertained. Because of the internal nature of these circuits, their propagation delays are not directly tested, but are guaranteed via pad-to-pad delay testing methodologies.

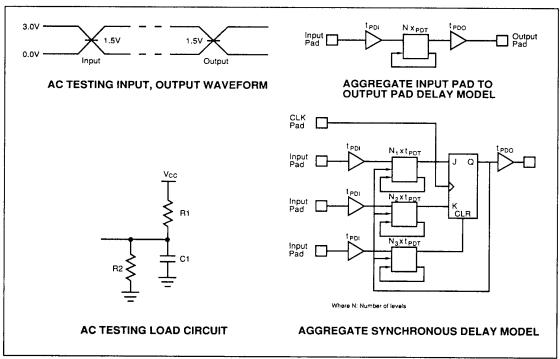

- For AC testing, input signal levels are 0.0V and 3.0V with a transition time of 6ns maximum. All time measurements are referenced at input and output voltages of 1.5V.

- 6. Delay times specified include delays through inverters, programmable inverters and multiplexers where appropriate.

- 7. Initialization occurs automatically at device power-up. Proper initialization requires a monotonic rise of Vcc from a voltage of 0.25V or less to the specified minimum Vcc voltage. Power-up initialization Time (tintr) is with respect to the point at which Vcc first reaches the specified minimum voltage. During the initialization period, all outputs are unconditionally placed in a high impedance state and logic operation is suspended. Once initialized, the chip will not reinitialize for Vcc of 3V or greater.

- Programming mode voltage on PMODE Pin (6) = Vpp. Programming parameters are valid at temperatures of +5°C to +45°C, and at Vcc levels

of 4.75 to 5.25V.

- 9. Minimum Clear Pulse width is always less than a one-level logic delay. Thus, one-level pulse generators can be used to clear the flip-flops.

- 10. Maximum supply current specifications are based on test designs using all 66 terms, with a minimum of 46 terms in the LOW state at all times. Because terms which are unused or are in the HIGH state do not use current, designs which use fewer terms or which have fewer terms simultaneously LOW than the test circuit will have a lower maximum current.

PLD 5 P'DCTS

5-28