96D 00184 D 7-5/-/5

# **RICOH**

## Microelectronic Specification

## RP2X04

THERMAL HEAD DRIVER WITH LATCH RESET AND ENABLE

#### **GENERAL DESCRIPTION**

The RP2X04 is a thermal head and LED driving IC with 16-bit S/P shift register. It is provided with serial input function and parallel output function with high breakdown voltage.

The RP2X04 has such functions as RESET, LATCH and ENABLE, and is able to operate clear, hold, inhibit, etc, of parallel output data.

As it has a common clock terminal and a serial output terminal, the cascade connection, too, is possible, resulting in diversity in use, extensibility in function and easiness in increasing bit.

The RP2X04 operates from a 5V single power supply as in the case of TTL, and its inputs and outputs are compatible with TTL.

#### # FEATURES

- Thermal head driver with 16-bit S/P shift register

- RESET, LATCH and ENABLE functions of the parallel output data

- High breakdown voltage ..... Drain breakdown voltage: 20.5V (Max)

- ◆ Large output current ..... Sink current : 60mA/Pin

- High operating frequency ..... 3MHz (Max)

- Low power dissipation ---- 30mW (Max) (NOTE: This value does not include power dissipation of Open Drain Tr.)

- 28-pin plastic DIL package

- Nch. Si gate MOS construction

## **APPLICATIONS**

The RP2X04 in itself is what was developed for the purpose of driving the thermal head, but it can be used also for driving small power lamps such as LED, etc., and in addition, for driving the data

series-parallel converter. It has, therefore, wide range of application fields including peripheral equipment of microcomputer, various equipment, etc.

■ PIN CONFIGURATION (Top view)

96D 00185 D

T-51-15

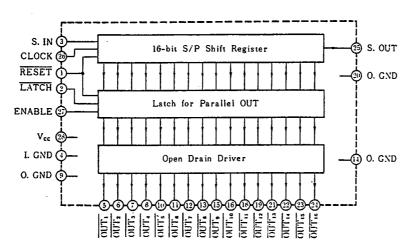

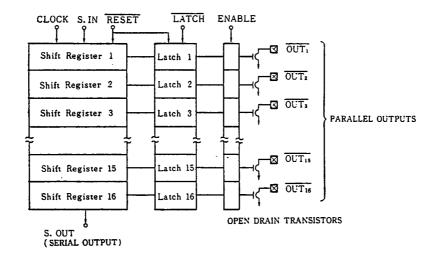

#### **■ BLOCK DIAGRAM**

NOTE: The GND for open drain transistors is provided separately from that (I. GND) for the logic circuit because it should allow large current to flow.

#### ■ ABSOLUTE MAXIMUM RATINGS (Ta=25°C)

| Symbol         | Parameters                       | Measuring Conditions | Rated Values | Unit |

|----------------|----------------------------------|----------------------|--------------|------|

| VTE            | Pin Voltage                      | GND=0V               | -0.5~7       | V    |

| Vor            | Open Drain Breakup (NOTE)        | GND=0V               | 21.0         | V    |

| Ip             | Drain Current                    |                      | 80           | mA   |

| P <sub>d</sub> | Maximum Power Dissipation        |                      | 600          | mW   |

| Торг           | Operating Ambient<br>Temperature |                      | 0~70         | ٣    |

| Tsug           | Storage Ambient<br>Temperature   |                      | -40~125      | ᠸ    |

NOTE: Open Drain Breakdown Voltage means voltage that can be applied to the parallel output terminal.

#### ■ RECOMMENDED OPERATING CONDITIONS (Unless Specified: Ta=0~70°C)

| Symbol         | Parameters           | Ra  | Rating Value |      |        |  |

|----------------|----------------------|-----|--------------|------|--------|--|

| Symbol         | rarameters           | Min | Тур          | Max  | Unit   |  |

| Vcc            | Power Supply Voltage | 4.5 | 5.0          | 5.5  | V      |  |

| fcx            | Clock Frequency      | DC  | 1.0          | 3.0  | MHz    |  |

| Vot            | Open Drain Breakup   |     |              | 20.5 | V      |  |

| l <sub>o</sub> | Drain Current        |     |              | 60   | mA/pin |  |

96D 00186 D T-51-15

#### ■ ELECTRICAL CHARACTERISTICS

$\bullet$  DC ELECTRICAL CHARACTERISTICS (Unless Specified : Ta=0~70°C, V\_{cc}=5V  $\pm 10\%$ )

| Symbol          | Parameters                           | Measuring Conditions              | Specified Value |     |         | 77   |                         |

|-----------------|--------------------------------------|-----------------------------------|-----------------|-----|---------|------|-------------------------|

|                 |                                      |                                   | Min             | Тур | Max     | Unit | Remarks                 |

| Vil             | "L" Input Voltage                    |                                   | -0.5            |     | 0.8     | ٧    |                         |

| V <sub>IH</sub> | "H" Input Voltage                    |                                   | 2.0             |     | Vcc+0.5 | V    |                         |

| Voli            | "L" Output Voltage                   | I <sub>ot</sub> = 1.6mA           |                 |     | 0.4     | V    | pin 25                  |

| VoH             | "H" Output Voltage                   | $l_{OH} = -100 \mu A$             | 2.4             |     |         | ٧    | 1                       |

| Volz            | "L" Output Voltage                   | 0.1V < Vol < 0.5V                 | 0.1             |     | 0.5     | ٧    | pin 5~8                 |

| Vor             | Open Drain Breakdown Voltage         | I <sub>oz</sub> < 100μ A          | <u> </u>        |     | 20.5    | V    | pin 10~13               |

| I <sub>D</sub>  | Drain Current                        | 0.1V < Vol < 0.5V                 |                 |     | 60      | mΑ   | pin 15. 16. 18. I       |

| IOLK            | Output Leak Current                  | $V_{o\tau} = 20.5 V$              | 1               |     | ±100    | μA   | pin 21~24               |

| IILK            | Input Leak Current                   | 0≤V <sub>1</sub> ≤V <sub>cc</sub> |                 |     | ± 10    | μA   |                         |

| I <sub>tL</sub> | Input Current                        | $0 \le V_1 \le V_{cc}$            |                 |     | -100    | μA   |                         |

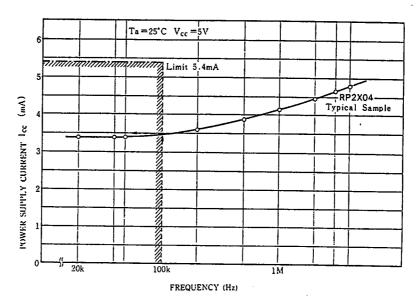

| Icc             | V <sub>cc</sub> Power Supply Current | 0≤V₁≤Vcc                          |                 |     | 5.4     | mA   | lcs<br>≤100k times/sec. |

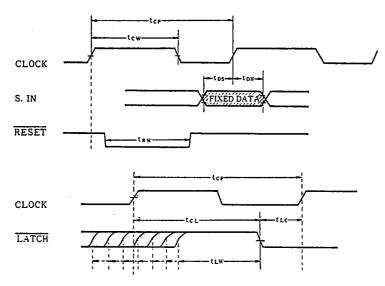

#### • AC OPERATING CONDITIONS (Unless Specified : Ta=0-70°C, $V_{cc}=5V\pm10\%$ )

| Symbol          | Parameters        | Measuring Conditions | Spe | cified V    | alue    | Unit | Remarks |

|-----------------|-------------------|----------------------|-----|-------------|---------|------|---------|

|                 |                   |                      | Min | Typ         | Max     |      |         |

| ter             | Clock Cycle       |                      | 330 | 1000        | DC      | ns   |         |

| t <sub>cw</sub> | Clock Pulse Width |                      | 100 | 600         | tcp-150 | ns   |         |

| tos             | Data Set-up Time  |                      | 60  |             |         | ns   |         |

| t <sub>DH</sub> | Data Hold Time    |                      | 35  |             |         | ns   |         |

| t <sub>RW</sub> | Reset Pulse Width |                      | 200 |             |         | ns   |         |

| t <sub>LW</sub> | Latch Pulse Width |                      | 230 |             |         | ns   |         |

| tcL             | Clock-Latch Time  |                      | 300 | <del></del> |         | ns   |         |

| tic             | Latch-Clock Time  |                      | -15 |             |         | ns   |         |

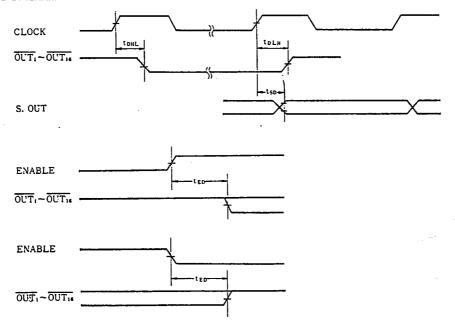

### $\bullet$ AC ELECTRICAL CHARACTERISTICS (Unless specified : Ta = 0 ~ 70 °C, V\_{cc} = 5 V $\pm 10\%$ )

| Symbol           | Parameters                       | Measuring Conditions | Specified Value |     |     | Unit | Remarks |

|------------------|----------------------------------|----------------------|-----------------|-----|-----|------|---------|

|                  |                                  |                      | Min             | Тур | Max | Unit | Kemarks |

| t <sub>DHL</sub> | Turn-on Delay Time               | VoL=0.5V no load     |                 |     | 10  | μs   |         |

| t <sub>DLH</sub> | Turn-off Delay Time              | Von=6V no load       |                 |     | 10  | μS   |         |

| t <sub>so</sub>  | Series Output Data Delay<br>Time | C <sub>L</sub> =25pF | 40              |     | 250 | ns   | -       |

| ten              | Enable Signal Delay Time         |                      |                 |     | 10  | μS   |         |

96D 00187 D

T-51-15

#### **■ INPUT DATA TIMING DIAGRAM**

#### **■ TIMING DIAGRAM**

96D 00188 T-51-15

#### ■ DEPENDENCY OF Icc OPERATING FREQUENCY

#### **EXPLANATION ON PIN FUNCTIONS**

| Pin Name        | Pin Number                                                              | I/O | Functions                                                                                                                                                                           |

|-----------------|-------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET           | 1                                                                       | I   | Shift Register and Latch data are reset (LOW) by making this pin at LOW by means of Reset input. It is connected internally to $V_{cc}$ through Pull-up resistor.                   |

| LATCH           | 2                                                                       |     | Latch command input for the parallel output data. The parallel output is latched by making this pin at LOW. It is connected internally to V <sub>cc</sub> through Pull-up resistor. |

| S.IN            | 3                                                                       | I,  | Serial input of 16-bit S/P Shift register                                                                                                                                           |

| I.GND           | 4                                                                       | I   | INPUT GND GND of Logic Circuits                                                                                                                                                     |

| <u>OUT</u> 1~16 | OUT 1-14 5. 6. 7. 8, 10. 11<br>12. 13, 15. 16. 18, 19<br>21. 22, 23, 24 |     | Open Drain Giant Transistor Parallel Output.  (Each pin can be applied with high voltage of 20.5V at maximum and large current of 60mA/pin at maximum.)                             |

| S.OUT           | 25                                                                      | 0   | Serial data output                                                                                                                                                                  |

| CLOCK           | 26                                                                      | 1   | Clock Input                                                                                                                                                                         |

| ENABLE          | LE 27                                                                   |     | When this pin is High, the parallel output is possible. It is internally pulled up to V <sub>cc</sub> .                                                                             |

| Vcc             | 28                                                                      |     | +5V Power Supply                                                                                                                                                                    |

| O.GND           | 9. 14. 20                                                               |     | GND (0V) for the parallel output driver                                                                                                                                             |

NOTE: The GND for open drain transistors is provided reparately from that (1 GND) for the logic circuit because large current flows in it.

96D 00189 D

T-51-15

#### **EXPLANATION ON INTERNAL FUNCTION**

The RP2X04 consists of the 16-bit shift register with S/P conversion function and the open drain driver unit for parallel output.

The data that was put in through S.IN terminal is 16-bit shifted, and then put out from S.OUT in synchronization with rise-up of CLOCK.

When the ENABLE terminal and the LATCH terminal are at HIGH level, output is put out in parallel, too. In case of holding the parallel output

data independently of CLOCK, all that is necessary is to make the LATCH terminal to the LOW level. For resetting each bit, the RESET terminal is made at the LOW level. In this case, the open drain driver is in the state of OFF. When the ENABLE terminal is at the LOW level, all the open drain driver terminals get in the state of OFF, while the information in the shift register is kept as it is.

96D 00190 D

T-51-15

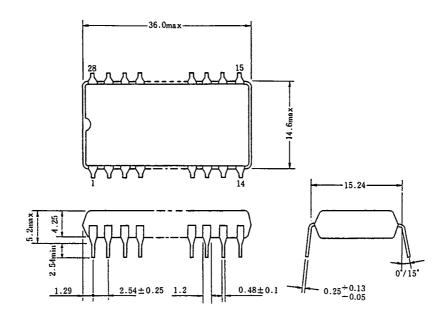

#### ■ 28-PIN PLASTIC DIL PACKAGE (EXTERNAL VIEW)(Unit: mm)

RICOH CORP, ELECTRONIC 96 DE 7744690 0000191 0

7744690 RICOH CORP, ELECTRONIC 96D 00191 D

T-51-15