# ATTL7542 Tip Ring Access Switch

#### **Features**

- Small size/surface-mount packaging

- Monolithic IC reliability

- Clean, bounce-free switching

- Low, matched ON-resistance

- Built-in current limiting, thermal shutdown, and SLIC protection

- Very low power consumption

- No EMI

### **Applications**

- Central office

- DLC

- PBX

# Description

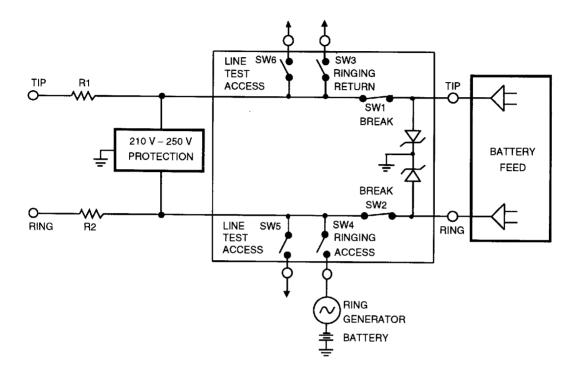

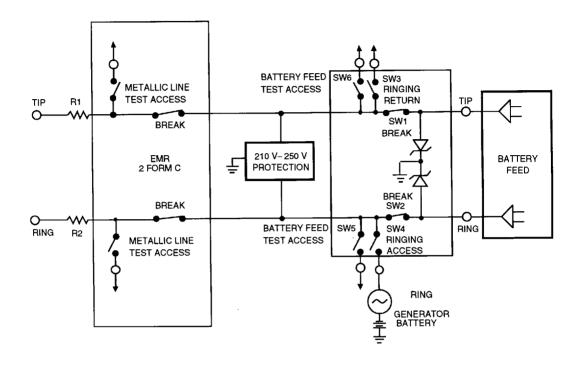

The ATTL7542 Tip Ring Access Switch (TRAS) is a monolithic integrated circuit that contains six solid-state relay contacts designed to replace electromechanical relays (EMR) in central office and digital loop carrier analog line-card applications. Through application of appropriate control signals to two logic level inputs, the idle or talk state, power ring and line test access states are achievable via the TRAS IC. With the addition of a single 2 Form C EMR and associated controls (Figure 9), the ringing-generator test access states and battery-feed test access are realized.

The line break switch pair is a linear switch that has exceptionally low ON-resistance and an excellent ON-resistance matching characteristic. The ringing access switch has a breakdown voltage rating >450 V, which is sufficiently high enough to prevent breakdown (i.e., passing the transient on to the ringing generator) in the presence of a transient fault condition.

Incorporated into the TRAS is a foldover type SLIC protection circuit that limits the voltage seen by the battery feed and shunts currents to a ground device during a fault condition. Thus, the TRAS eliminates the need for a separate SLIC protection device.

To protect the TRAS from an overvoltage fault condition, use of a secondary protector is required. The secondary protector must limit the voltage applied to the TRAS to <250 V. Use of a foldback or crowbar type secondary protector is recommended. The line break switch pair and access switches (except those connected to the ringing generator) have a current-limit feature that will limit the current through the switch in the presence of a transient fault condition.

Also incorporated into the TRAS is a thermal shutdown circuit that will cause the chip to shutdown (all switches off) when excessive power dissipation, such as what is encountered in the presence of an extended power cross, causes the chip temperature to rise above a given threshold. With the proper design of SLIC circuitry, proper selection of secondary protector, and series resistors, the TRAS will meet appropriate regulatory agency requirements.

The TRAS requires 5 V, battery voltage, and ground to operate. The TRAS device is packaged in a 16-pin, plastic SOG package (ATTL7542AAE/BAE).

### Pin Information

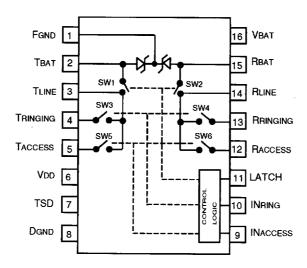

Figure 1. 16-Pin, Plastic SOG

Table 1. Pin Descriptions

| Pin | Symbol   | Description                                                                                                                                                                                       | Pin | Symbol    | Description                                       |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|---------------------------------------------------|

| 1   | FGnd     | Fault ground.                                                                                                                                                                                     | 16  | VBAT      | Battery voltage.                                  |

| 2   | Тват     | Connect to TIP on SLIC side.                                                                                                                                                                      | 15  | RBAT      | Connect to RING on SLIC side.                     |

| 3   | TLINE    | Connect to TIP on line side.                                                                                                                                                                      | 14  | RLINE     | Connect to RING on line side.                     |

| 4   | TRINGING | Connect to return ground for ringing generator.                                                                                                                                                   | 13  | RRINGING  | Connect to ringing generator.                     |

| 5   | TACCESS  | Test access.                                                                                                                                                                                      | 12  | RACCESS   | Test access.                                      |

| 6   | VDD      | +5 V supply.                                                                                                                                                                                      | 11  | LATCH     | Data input control, active-high, transparent low. |

| 7   | TSD      | Temperature shutdown output flag will read +5 V when the device is in its operational mode and 0 V in the thermal shutdown mode. To disable the thermal shutdown mechanism, tie this pin to +5 V. | 10  | INRINGING | Logic level switch input control                  |

| 8   | DGnd     | Digital ground.                                                                                                                                                                                   | 9   | INACCESS  | Logic level switch input control.                 |

### **Electrical Characteristics**

Ta --40 °C to +85 °C, unless otherwise specified.

Minimum and maximum values are testing requirements. Typical values are characteristics of the device and are the result of engineering evaluations. Typical values are for information purposes only and are not part of the testing requirements.

**Table 2. Power Supply Specifications**

| Parameter         | Power Supply, VDD | Power Supply, VBAT |

|-------------------|-------------------|--------------------|

| Nominal Voltage   | +5 V              | -48 V/-60 V*       |

| Voltage Tolerance | ±0.5 V            | ±20%               |

<sup>\*</sup> Choice of SLIC protection circuit trigger voltage is determined by the maximum voltage of VBAT. See SLIC Protection Circuit section for details.

Table 3. Break Switch, 1and 2

| Parameter                    | Test Condition                                                                     | Measure                      | Min | Тур  | Max | Unit |

|------------------------------|------------------------------------------------------------------------------------|------------------------------|-----|------|-----|------|

| Off-state Leakage<br>Current | Vswitch (differential) = -320 V to Gnd<br>Vswitch (differential) = -60 V to +260 V | Iswitch                      | _   | _    | 1   | μA   |

| ON Resistance                | Iswitch (on) = $\pm 10$ mA, $\pm 40$ mA                                            | Δ Von                        |     | 15 * | 28  | Ω    |

| ON-resistance Match          | Per ON-resistance Test<br>Condition of SW3, SW4                                    | Magnitude<br>Ron SW3—Ron SW4 | 1   |      | 1   | Ω    |

| Current Limit                | Vswitch (on) = ±10 V                                                               | Iswitch                      | 80  |      | 220 | mA   |

| Isolation                    | Vswitch (both poles) = ±320 V<br>Logic Inputs = GND                                | Iswitch                      | _   | _    | 1   | μА   |

| dv/dt Sensitivity*           |                                                                                    | _                            | _   | 200  |     | V/μs |

<sup>\*</sup> At 25 °C.

### **Electrical Characteristics** (continued)

Table 4. Ringing Return Switch 3

| Parameter                      | Test Condition                                                                     | Measure | Min | Тур | Max | Unit |

|--------------------------------|------------------------------------------------------------------------------------|---------|-----|-----|-----|------|

| Off-state Leakage<br>Current   | Vswitch (differential) = -320 V to Gnd<br>Vswitch (differential) = -60 V to +260 V | Iswitch |     |     | 1   | μΑ   |

| ON Resistance                  | Iswitch (on) = $\pm 5$ mA, $\pm 10$ mA                                             | Δ Von   | _   | 50* | 100 | Ω    |

| Current Limit                  | Vswitch (on) = ±50 V                                                               | Iswitch | 200 | 1   | 400 | mA   |

| Isolation                      | Vswitch = ±320 V<br>Logic Inputs = GND                                             | Iswitch | _   | _   | 1   | μА   |

| dv/dt Sensitivity <sup>†</sup> | _                                                                                  |         |     | 200 | _   | V/μs |

<sup>\*</sup> At 25 °C.

AT&T Microelectronics 4-175

<sup>&</sup>lt;sup>†</sup> Applied voltage is 100 Vpp square wave at 100 Hz.

<sup>&</sup>lt;sup>†</sup> Applied voltage is 100 Vpp square wave at 100 Hz.

### **Electrical Characteristics** (continued)

Table 5. Ringing Switch 4

| Parameter                 | Test Condition                                                                         | Measure | Min | Тур | Max | Unit |

|---------------------------|----------------------------------------------------------------------------------------|---------|-----|-----|-----|------|

| Off-state Leakage Current | Vswitch (differential) = +260 V to -190 V<br>Vswitch (differential) = -260 V to +190 V | Iswitch |     | _   | 1   | μА   |

| ON Resistance             | Iswitch (on) = ±70 mA, ±80 mA                                                          | Δ Von   | 1 — |     | 10  | Ω    |

| ON Voltage                | Iswitch (on) = ±1 mA                                                                   | Vos     | 1 — |     | 3   | V    |

| ON Voltage (Vos)          | Iswitch (on) = ±1 mA                                                                   | Vos     | l — | -   | 3   | ٧    |

| Isolation                 | Vswitch = ±320 V<br>Logic Inputs = GND                                                 | Iswitch | -   | —   | 1   | μΑ   |

| Surge Current             |                                                                                        | _       | _   | _   | 2   | Α    |

| Release Current           | _                                                                                      | _       | 100 | _   | 500 | μА   |

| dv/dt Sensitivity †       |                                                                                        |         |     | 200 | _   | V/μs |

<sup>\*</sup> At 25 °C

Table 6. Test Out Switch, 5 and 6

| Parameter                      | Test Condition                                                                     | Measure | Min      | Тур | Max | Unit |

|--------------------------------|------------------------------------------------------------------------------------|---------|----------|-----|-----|------|

| Off-state Leakage Current      | Vswitch (differential) = -320 V to GND<br>Vswitch (differential) = -60 V to +260 V | Iswitch | -        | _   | 1   | μА   |

| ON Resistance                  | Iswitch (on) = ±5 mA to 10 mA                                                      | Δ Von   | <b>—</b> | 30* | 65  | Ω    |

| Current Limit                  | Vswitch (on) = ±50 V                                                               | Iswitch | 100      | _   | 220 | mA   |

| Isolation                      | Vswitch (both poles) = ±320 V<br>Logic Inputs = GND                                | Iswitch | _        | _   | 1   | μΑ   |

| dv/dt Sensitivity <sup>†</sup> | _                                                                                  |         | <b>—</b> | 200 | _   | V/µs |

<sup>\*</sup> At 25 °C.

**Table 7. Additional Electrical Characteristics**

| Parameter                                       | Test Condition                                                                  | Measure   | Min | Тур      | Max | Unit |

|-------------------------------------------------|---------------------------------------------------------------------------------|-----------|-----|----------|-----|------|

| Digital Input Characteristics:                  |                                                                                 |           |     | <u> </u> |     |      |

| Input Low Voltage                               | _                                                                               | _         | l — | <u> </u> | 1.5 | V    |

| Input High Voltage                              | _                                                                               | _         | 3.5 |          | _   | ٧    |

| Input Leakage Current (High)                    | $V_{DD} = 5.5 \text{ V}, V_{BAT} = -58 \text{ V},$ $V_{Ogicin} = 5 \text{ V}$   | llogicin  | _   | _        | 1   | μА   |

| Input Leakage Current (Low)                     | $V_{DD} = 5.5 \text{ V}, V_{BAT} = -58 \text{ V},$ $V_{Ogicin} = 0 \text{ V}$   | llogicin  | -   |          | 1   | μА   |

| Power Requirements:                             |                                                                                 |           |     |          |     |      |

| Power Dissipation                               | $V_{DD} = 5.5 \text{ V}, V_{BAT} = -58 \text{ V},$ $Idle \text{ or Talk State}$ | IDD, IBAT | _   | 15*      | 70  | mW   |

| VDD Current                                     | VDD = 5.5 V, VBAT = -58 V,<br>Idle or Talk State                                | loo       | _   | 0.25*    | 2   | mA   |

| VBAT Current                                    | $V_{DD} = 5.5 \text{ V}, V_{BAT} = -58 \text{ V},$ Idle or Talk State           | Іват      | _   | 0.25*    | 1   | mA   |

| Temperature Shutdown Requirements: <sup>†</sup> |                                                                                 |           |     |          |     |      |

| Shutdown Activation Temperature                 | <u> </u>                                                                        | _         | 110 | 125      | 150 | °C   |

| Shutdown Circuit Hysteresis                     | _                                                                               | _         | 10  |          | 25  | °C   |

<sup>\*</sup> At 25 °C.

4-176

<sup>&</sup>lt;sup>†</sup> Applied voltage is 100 Vpp square wave at 100 Hz.

$<sup>^\</sup>dagger$  Applied voltage is 100 Vpp square wave at 100 Hz.

<sup>&</sup>lt;sup>†</sup> Temperature shutdown flag (TSD) will be high during normal operation and low during temperature shutdown state.

### **Zero Cross Current Turn Off**

The ring access switch (SW4) is designed to turn off on a zero current cross. This switch requires a current zero cross at the battery voltage to turn off. Switch 4 (SW4) will remain in the ON state (regardless of logic input) until a current zero cross. Therefore, to ensure proper operation, switch 4 should be connected to the ringing generator (via proper impedance).

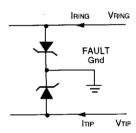

#### **SLIC Protection Circuit**

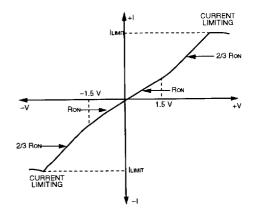

The SLIC protection circuit, shown in Figure 3 as two zener diodes, is included in the ATTL7542 TRAS IC device to protect the battery feed from fault-induced overvoltage situations. With this feature, the only secondary protection required on the line card is the 210 V—250 V protector on the loop side of the solid-state relay. The battery feed is protected by a combination of the current limit in the SLIC break switches (SW3 and SW4) and the SLIC protection circuit.

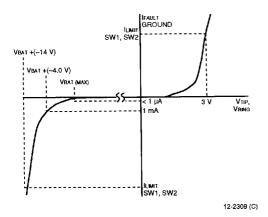

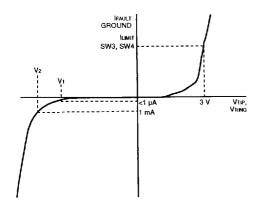

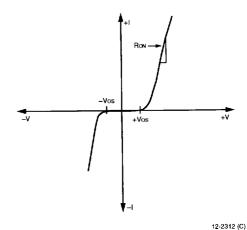

In reality, this circuit consists of MOSFET transistors that are turned on when the voltage at the battery feed is more negative than the battery or more negative than an internal zener diode reference (clamp voltage). For positive fault conditions, the protection circuit will conduct when the battery feed exceeds one diode drop. The characteristics of the protection circuit are shown in Figures 4 and 5.

Two different clamp voltages are available for the ATTL7542 TRAS IC device. The first alpha character after the numerical device identifier designates the clamp voltage version. The A character designate is intended for a battery voltage of  $-48~V \pm 20\%$  and, the B character designate is intended for battery voltages of  $60~V \pm 20\%$ . Tables 6 and 7 give the specifications for the leakage at the maximum battery voltage (58~V or -72~V), the voltage at which 1 mA is conducted, and the voltage at which the clamp circuit conducts the maximum dc current that can be carried by switches 1 or 2 (ILIMIT SW1, SW2).

The following information shown in Tables 8 and 9 is referenced in Figures 4 and 5.

Compilation of this data was over the full temperature range (-40 °C to +85 °C).

Figure 2. SLIC Protection Circuit

# **SLIC Protection Circuit** (continued)

Table 8. SLIC Protection Circuitry Options (ATTL7542AAE)

|                                                    |                      |        |                                    | Measure        |     |      |

|----------------------------------------------------|----------------------|--------|------------------------------------|----------------|-----|------|

| Apply                                              | Condition            | Figure | Parameter                          | Min            | Max | Unit |

| RBAT = VBAT<br>TBAT = VBAT                         | Vbat = -58 V         | 4      | IFAULTGROUND                       | _              | 1   | μΑ   |

| FAULTGROUND = -1 mA                                | Vbat = -58 V         | 4      | TBAT<br>RBAT                       | VBAT + (-4 V)  | -   | ٧    |

| IFAULTGROUND = -ILimit<br>SW1, SW2                 | Vbat = -58 V         | 4      | Tbat<br>Rbat                       | VBAT + (-14 V) | _   | ٧    |

| IFAULTGROUND = +ILIMIT<br>SW1, SW2                 | Vbat = -58 V         | 4      | TBAT<br>RBAT                       | _              | 3   | ٧    |

| Тват = -60 V (V1 Fig 5)<br>Rват = -60 V (V1 Fig 5) | VBAT = No Connection | 5      | FAULTGROUND                        | 1              | 1   | μА   |

| FAULTGROUND = -1 mA                                | VBAT = No Connection | 5      | Тват (V2 Fig 5)<br>Rват (V2 Fig 5) | -70            | _   | ٧    |

| IFAULTGROUND = + Limit<br>SW1, SW2                 | VBAT = No Connection | 5      | <del>_</del>                       |                | 3   | ٧    |

Table 9. SLIC Protection Circuitry Options (ATTL7542BAE)

|                                                    |                      |        |                                    | Measure        | ,   |      |

|----------------------------------------------------|----------------------|--------|------------------------------------|----------------|-----|------|

| Apply                                              | Condition            | Figure | Parameter                          | Min            | Max | Unit |

| RBAT = VBAT<br>TBAT = VBAT                         | Vbat = -72 V         | 4      | FAULTGROUND                        | _              | 1   | μΑ   |

| IFAULTGROUND = −1 mA                               | VBAT = -72 V         | 4      | T <sub>BAT</sub><br>RBAT           | VBAT + (-4 V)  | _   | ٧    |

| IFAULTGROUND = -ILImit<br>SW1, SW2                 | VBAT = -72 V         | 4      | TBAT<br>RBAT                       | VBAT + (-14 V) | _   | ٧    |

| IFAULTGROUND = +ILimit<br>SW1, SW2                 | VBAT = −72 V         | 4      | TBAT<br>RBAT                       |                | 3   | ٧    |

| Тват = -77 V (V1 Fig 5)<br>Rват = -77 V (V1 Fig 5) | VBAT = No Connection | 5      | FAULTGROUND                        | 1              | 1   | μА   |

| FAULTGROUND = -1 mA                                | VBAT = No Connection | 5      | Тват (V2 Fig 5)<br>Rват (V2 Fig 5) | -87            | _   | ٧    |

| IFAULTGROUND = +ILimit<br>SW1, SW2                 | VBAT = No Connection | 5      |                                    |                | 3   | ٧    |

# **Typical Performance Characteristics**

Figure 3. Characteristics of ATTL7542 (VBAT Present)

Figure 4. Characteristics of ATTL7542 (VBAT Not Present)

Figure 5. Switch 1-3, 5, 6

Figure 6. Switch 4

4-179

# **Application**

Figure 7. Typical TRAS Application, Idle or Talk State Shown

Table 10. Truth Table

| lı   | nput   |        | Switches |        | State Description     |

|------|--------|--------|----------|--------|-----------------------|

| Ring | Access | SW 1/2 | SW 3/4   | SW 5/6 |                       |

| Low  | Low    | Closed | Open     | Open   | Idle or talking state |

| Low  | High   | Open   | Open     | Closed | Line test state       |

| High | Low    | Open   | Closed   | Open   | Power ringing state   |

| High | High   | Open   | Open     | Open   | All off               |

# **Application**

Figure 8. Typical TRAS Application with Metallic Test-in Access, Idle or Talk State Shown

Table 11. Truth Table

|      |        | TRAS   |         |        |       | EMR          |                 |                               |

|------|--------|--------|---------|--------|-------|--------------|-----------------|-------------------------------|

| li   | nput   |        | Switche | s      | Input | Swi          | itches          | State Description             |

| Ring | Access | SW 1/2 | SW 3/4  | SW 5/6 | EMR   | EMR<br>Break | EMR Test-<br>in |                               |

| Low  | Low    | Closed | Open    | Open   | Low   | Closed       | Open            | Idle or talking state         |

| Low  | High   | Open   | Open    | Closed | Low   | Closed       | Open            | Line test state               |

| Low  | Low    | Closed | Open    | Open   | High  | Open         | Closed          | Battery feed test state       |

| High | Low    | Open   | Closed  | Open   | Low   | Closed       | Open            | Power ringing state           |

| High | Low    | Open   | Closed  | Open   | High  | Open         | Closed          | Ringing generator test state* |

| High | High   | Open   | Open    | Open   | Low   | Closed       | Open            | All off                       |

<sup>\*</sup> Power ringing appears at test node.

# **Outline Drawings**

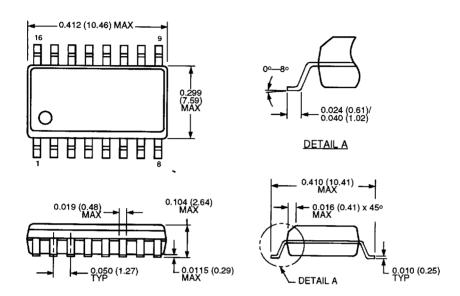

Dimensions are in inches and (millimeters).

### 16-Pin, Plastic SOG

# **Packaging and Ordering Information**

Throughout this section the following abbreviations are used:

DIP — Dual in-line package; SOG — Small-outline gull wing; SOJ — Small-outline J-lead; SONB — Small-outline narrow body; PLCC — Plastic leaded chip carrier.

| Device Code     | Package Type                 | Temperature      |

|-----------------|------------------------------|------------------|

| ATTL7551AP      | 44-Pin PLCC                  | -40 °C to +85 °C |

| ATTL7551AF      | 24-Pin DIP                   | –40 °C to +85 °C |

| ATTL7554AP      | 44-Pin PLCC                  | –40 °C to +85 °C |

| ATTL7556AAU     | 32-Pin PLCC                  | -40 °C to +85 °C |

| ATTL7557AAU     | 32-11111200                  |                  |

| ATTL7561AP      | 44-Pin PLCC                  | –40 °C to +85 °C |

| ATTL7564AP      | 44-1111 200                  |                  |

| ATTL7581AC/BC   | 16-Pin DIP                   | -40 °C to +85 °C |

| ATTL7581AAE/BAE | 16-Pin Plastic SOG           | -40 °C to +85 °C |

| ATTL7582AE/BE   | 16-Pin Plastic DIP           | -40 °C to +85 °C |

| ATTL7582AAE/BAE | 16-Pin Plastic SOG           | -40 °C to +85 °C |

| ATTL7583AF/BF   | 24-Pin Plastic DIP (600 mil) | –40 °C to +85 °C |

| ATTL7583ACG/BCG | 24-Pin Plastic DIP (300 mil) | -40 °C to +85 °C |

| ATTL7583AAJ/BAJ | 28-Pin Plastic SOG           | -40 °C to +85 °C |

| ATTL7590AAF     | 14-Pin                       | -40 °C to +85 °C |

| ATTL7591AB      | 8-Pin, DIP                   | -40 °C to +85 °C |

| ATTL7591AS      | 8-Pin, SONB                  | -40 °C to +85 °C |

| LB1011AB        | 8-Pin, DIP                   | –20 °C to +70 °C |

| LB1013AD        | 18-Pin, DIP                  | -25 °C to +85 °C |

| LB1060AB        | 8-Pin, DIP                   | -40 °C to +65 °C |

| LB1201AB        | 8-Pin, DIP                   | -40 °C to +85 °C |

| LB1201AS        | 8-Pin, SONB                  | –40 °C to +85 °C |

| LB1208AAJ       | 28-pin SOG                   | -40 °C to +85 °C |

| LB1276AP        | 44-Pin PLCC                  | -40 °C to +85 °C |

| LB1276AF        | 24-Pin DIP                   | –40 °C to +85 °C |

| LB1356AF        | 24-Pin DIP                   | -40 °C to +85 °C |

| LH1263AR        | 20-Pin Plastic DIP           | -40 °C to +85 °C |

| LH1571AB        | 8-pin Plastic DIP            | -40 °C to +85 °C |

| LH1571AAC       | 8-pin SOG                    | -40 °C to +85 °C |

| T - 7503 EL     | 20-Pin, SOJ                  | -40 °C to +85 °C |

| T - 7503 1EC    | 20-Pin, SOJ                  | 0 °C to 70 °C    |

| T - 7504 PL     | 28-Pin, DIP                  | -40 °C to +85 °C |

| T - 7504 ML     | 28-Pin, PLCC                 | -40 °C to +85 °C |

| T - 5504 PL     | 28-Pin, DIP                  | -40 °C to +85 °C |

| T - 5504 ML     | 28-Pin, PLCC                 | -40 °C to +85 °C |

| T - 7513B EE    | 20-Pin, SOJ                  | -40 °C to +85 °C |

| T - 7513B PE    | 20-Pin, DIP                  | -40 °C to +85 °C |

| T - 7517A EE    | 16-Pin, DIP                  | -40 °C to +85 °C |

| T - 7517A PE    | 16-Pin, SOJ                  | –40 °C to +85 °C |

| T - 7548 ME2    | 28-Pin, PLCC                 | 0 °C to 85 °C    |

| T - 7570 ML2    | 28-Pin, PLCC                 | -40 °C to +85 °C |