### SN74ALVC16269 12-BIT TO 24-BIT REGISTERED BUS TRANSCEIVER WITH 3-STATE OUTPUTS

SCAS417 - OCTOBER 1993 - REVISED MARCH 1994

- EPIC™ (Enhanced-Performance Implanted CMOS) Submicron Process

- Member of the Texas Instruments Widebus™ Family

- Supports Unregulated Battery Operation Down to 2.7 V

- Typical V<sub>OLP</sub> (Output Ground Bounce)

< 0.8 V at V<sub>CC</sub> = 3.3 V, T<sub>A</sub> = 25°C

- Typical V<sub>OHV</sub> (Output V<sub>CC</sub> Overshoot)

2 V at V<sub>CC</sub> = 3.3 V, T<sub>A</sub> = 25°C

- Bus-Hold On Data Inputs Eliminates the Need for External Pullup/Pulldown Resistors

- Packaged in Plastic Shrink Small-Outline (DL) and Thin Shrink Small-Outline (DGG) Packages

#### description

The SN74ALVC16269 is a 12-bit to 24-bit registered bus exchanger, which is intended for applications where two separate ports must be multiplexed onto, or demultiplexed from, a single port. It is particularly suitable as an interface between sync DRAMs and high-speed microprocessors. The SN74ALVC16269 is designed specifically for low-voltage (3.3 V) VCC operation

Data is stored in the internal B-port registers on the low-to-high transition of the clock (CLK) input, provided that the appropriate CLKENA inputs are low. Proper control of these inputs allows two sequential 12-bit words to be presented as a 24-bit word on the B port. For data transfer in the B-to-A direction, a single storage register is provided. The select (SEL) line selects 1B or 2B data for the A outputs. The register on the A output permits the fastest possible data transfer, thus extending the period that the data will be valid on the bus. The control pins are registered so that all transactions are synchronous with the clock. Data flow is controlled by the active-low output enables (OEA, OEB1, OEB2).

# DGG OR DL PACKAGE (TOP VIEW)

|      | $\overline{}$ |   |    |                 |

|------|---------------|---|----|-----------------|

| OEA  | 1             | U | 56 | OEB2            |

| OEB1 |               |   |    | CLKENA2         |

| 2B3  |               |   |    | 2B4             |

| GND  |               |   |    | GND             |

| 2B2  |               |   |    | 2B5             |

| 2B1  |               |   |    | 2B6             |

| Vcc  |               |   |    | V <sub>CC</sub> |

| A1   | <b>1</b>      |   | 49 | 2B7             |

| A2   |               |   | 48 | 2B8             |

| A3   | 10            |   | 47 | 2B9             |

| GND  |               |   |    | GND             |

|      | 12            |   |    | 2B10            |

|      | 13            |   |    | 2B11            |

| A6   |               |   |    | 2B12            |

|      | 15            |   | 42 | 1B12            |

| A8   |               |   |    | 1B11            |

| A9   |               |   | 40 | 1B10            |

| GND  |               |   | 39 | GND             |

| A10  |               |   | 38 | 1B9             |

| A11  |               |   |    | 1B8             |

| A12  | _             |   |    | 1B7             |

| Vcc  |               |   |    | v <sub>cc</sub> |

| 1B1  |               |   |    | 1B6             |

| 1B2  |               |   |    | 1B5             |

| GND  |               |   | 32 | GND             |

| 1B3  |               |   |    | 1B4             |

| NC   |               |   | 30 | CLKENA1         |

| SEL  |               |   |    | CLK             |

|      |               |   |    |                 |

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

The SN74ALVC16269 is available in TI's shrink small-outline (DL) and thin shrink small-outline (DGG) packages, which provide twice the I/O pin count and functionality of standard small-outline packages in the same printed-circuit-board area.

The SN74ALVC16269 is characterized for operation from -40°C to 85°C.

EPIC and Widebus are trademarks of Texas Instruments Incorporated.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas instruments reserves the right to change or discontinue these products without notice.

Copyright @ 1994, Texas Instruments Incorporated

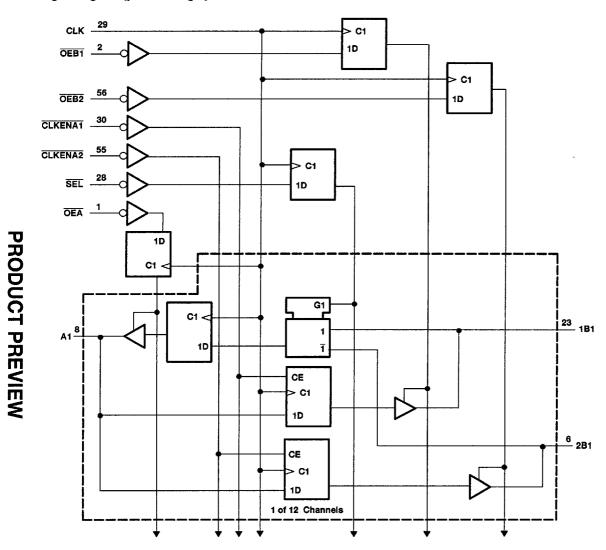

#### logic diagram (positive logic)

## SN74ALVC16269 12-BIT TO 24-BIT REGISTERED BUS TRANSCEIVER WITH 3-STATE OUTPUTS

SCAS417 - OCTOBER 1993 - REVISED MARCH 1994

#### **Function Tables**

#### **OUTPUT-ENABLE TABLE**

| INPUTS |             |   | OUTPUTS |        |  |

|--------|-------------|---|---------|--------|--|

| CLK    | CLK OEA OEB |   | Α       | 1B, 2B |  |

| 1      | Н           | Н | Z       | Z      |  |

| 1      | Н           | L | z       | Active |  |

| 1      | L           | Н | Active  | Z      |  |

| 1      | L           | L | Active  | Active |  |

#### A-TO-B STORAGE TABLE (OEB = L)

| INPUTS  |         |     |   | OUTPUTS           |                   |  |

|---------|---------|-----|---|-------------------|-------------------|--|

| CLKENA1 | CLKENA2 | CLK | Α | 18                | 2B                |  |

| Н       | Н       | Х   | Х | 1B <sub>0</sub> † | 2B <sub>0</sub> † |  |

| L       | Х       | 1   | L | L                 | X                 |  |

| L       | X       | 1   | Н | н                 | Х                 |  |

| х       | L       | 1   | L | ×                 | L                 |  |

| Х       | L       | 1   | Н | ×                 | Н                 |  |

#### B-TO-A STORAGE TABLE (OEA = L)

|     | INPUTS |    |    |                                      |  |

|-----|--------|----|----|--------------------------------------|--|

| CLK | SEL    | 1B | 2B | A                                    |  |

| Х   | Н      | Х  | Х  | A <sub>0</sub> †<br>A <sub>0</sub> † |  |

| x   | L      | Χ  | Х  | A <sub>0</sub> †                     |  |

| 1   | н      | L  | X  | L                                    |  |

| 1   | Н      | н  | X  | н                                    |  |

| 1   | L      | Χ  | L  | L                                    |  |

| 1   | L      | Χ  | Н  | н                                    |  |

<sup>†</sup> Output level before the indicated steady-state input conditions were established.

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)‡

| Supply voltage range, V <sub>CC</sub>                                                           | 0.5 V to 4.6 V                   |

|-------------------------------------------------------------------------------------------------|----------------------------------|

| Input voltage range, V <sub>I</sub> (except I/O ports) (see Note 1)                             |                                  |

| Input voltage range, V <sub>I</sub> (I/O ports) (see Notes 1 and 2)                             | 0.5 V to V <sub>CC</sub> + 0.5 V |

| Output voltage range, VO (see Notes 1 and 2)                                                    | 0.5 V to V <sub>CC</sub> + 0.5 V |

| Input clamp current, $I_{IK}(V_I < 0)$                                                          | –50 mA                           |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> ) | ±50 mA                           |

| Continuous output current, $I_O$ ( $V_O = 0$ to $V_{CC}$ )                                      | ±50 mA                           |

| Continuous current through V <sub>CC</sub> or GND                                               | ±100 mA                          |

| Maximum power dissipation at $T_A = 55$ °C (in still air) (see N                                | lote 3): DGG package 1 W         |

|                                                                                                 | DL package 1.4 W                 |

| Storage temperature range                                                                       |                                  |

<sup>‡</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils.

For more information, refer to the Package Thermal Considerations application note.

NOTES: 1. The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

<sup>2.</sup> The input and output positive voltage ratings may be exceeded up to 4.6 V if the input and output clamp-current ratings are observed.

# SN74ALVC16269 12-BIT TO 24-BIT REGISTERED BUS TRANSCEIVER WITH 3-STATE OUTPUTS SCAS417 - OCTOBER 1993 - REVISED MARCH 1994

#### recommended operating conditions

|                 |                                    |                                  | MIN | MAX | UNIT |  |

|-----------------|------------------------------------|----------------------------------|-----|-----|------|--|

| VCC             | Supply voltage                     | age                              |     |     | V    |  |

| VIH             | High-level input voltage           | V <sub>CC</sub> = 2.7 V to 3.6 V | 2   |     | V    |  |

| ۷ <sub>IL</sub> | Low-level input voltage            | V <sub>CC</sub> = 2.7 V to 3.6 V |     | 8.0 | V    |  |

| Vi              | Input voltage                      |                                  |     | Vcc | ٧    |  |

| ٧o              | Output voltage                     |                                  |     | VCC | V    |  |

| ЮН              | High-level output current .        | V <sub>CC</sub> = 2.7 V          |     | -12 | mA   |  |

|                 |                                    | V <sub>CC</sub> = 3 V            |     | -24 | IIIA |  |

| lOL             | t and land antend arrespond        | V <sub>CC</sub> = 2.7 V          |     | 12  | mA   |  |

|                 | Low-level output current           | V <sub>CC</sub> = 3 V            |     | 24  | IIIA |  |

| Δt/Δν           | Input transition rise or fall rate |                                  | 0   | 10  | ns/V |  |

| TA              | Operating free-air temperature     |                                  | -40 | 85  | ္င   |  |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PAF            | RAMETER   | TEST CONDITIONS                                                                                              | v <sub>cc</sub> † | MIN                 | MAX  | UNIT |  |

|----------------|-----------|--------------------------------------------------------------------------------------------------------------|-------------------|---------------------|------|------|--|

|                |           | I <sub>OH</sub> = -100 μA                                                                                    | MIN to MAX        | V <sub>CC</sub> -0. | .2   |      |  |

|                |           | 10                                                                                                           | 2.7 V             | 2.2                 |      | ٧    |  |

| ∨он            |           | $l_{OH} = -12 \text{ mA}$                                                                                    | 3 V               | 2.4                 |      |      |  |

|                |           | I <sub>OH</sub> = -24 mA                                                                                     | 3 V               | 2                   |      |      |  |

|                |           | I <sub>OL</sub> = 100 μA                                                                                     | MIN to MAX        | MIN to MAX (        |      | 2    |  |

| VOL            |           | I <sub>OL</sub> = 12 mA                                                                                      | 2.7 V             |                     | 0.4  | ٧    |  |

|                |           | I <sub>OL</sub> = 24 mA                                                                                      | 3 V               |                     | 0.55 | İ    |  |

| l <sub>l</sub> | Inputs    | V <sub>I</sub> = V <sub>CC</sub> or GND                                                                      | 3.6 V             |                     | ±5   | μА   |  |

| 1              | Data pins | V <sub>I</sub> = 0.8 V                                                                                       | 3 V               | 75                  |      | μА   |  |

| l(hold)        |           | V <sub>1</sub> = 2 V                                                                                         | 3 V               | -75                 |      |      |  |

| loz            |           | V <sub>O</sub> = V <sub>CC</sub> or GND                                                                      | 3.6 V             |                     | ±10  | μA   |  |

| Icc            |           | $V_1 = V_{CC}$ or GND, $I_O = 0$                                                                             | 3.6 V             |                     | 40   | μА   |  |

| ΔICC           |           | V <sub>CC</sub> = 3 V to 3.6 V, One input at V <sub>CC</sub> - 0.6 V, Other inputs at V <sub>CC</sub> or GND |                   |                     | 750  | μА   |  |

| Ci             |           | V <sub>I</sub> = V <sub>CC</sub> or GND                                                                      | 3.3 V             |                     |      | рF   |  |

| Cio            |           | V <sub>O</sub> = V <sub>CC</sub> or GND                                                                      | 3.3 V             |                     |      | pF   |  |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate values under recommended operating conditions.