# silicon systems®

# SSI 32H567 Servo Demodulator

June, 1989

### **DESCRIPTION**

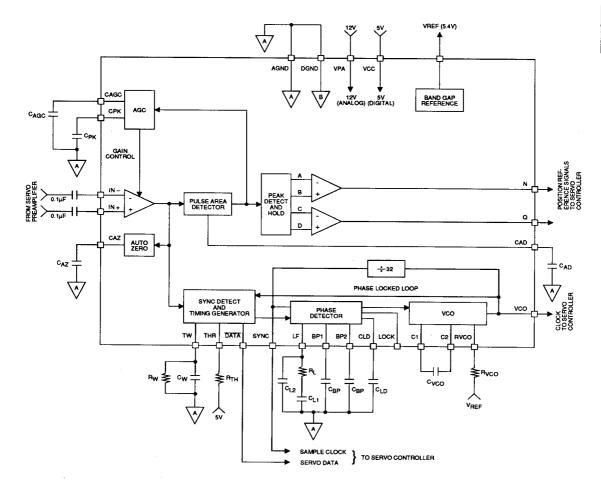

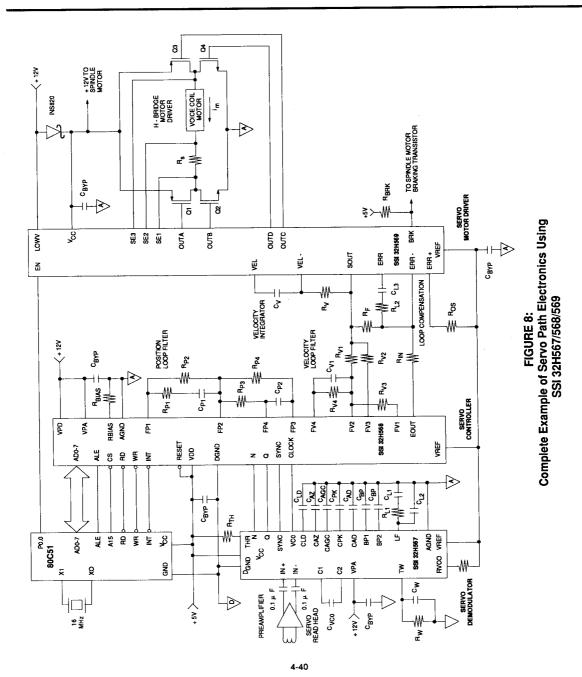

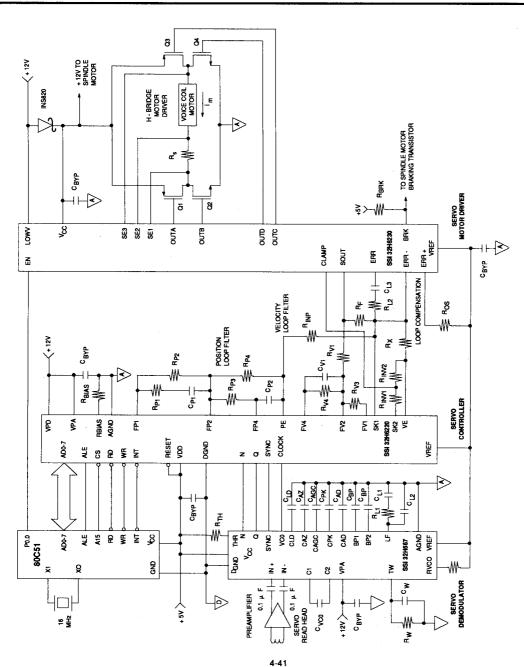

The SSI 32H567 Servo Demodulator is a bipolar device intended for use in Winchester disk drives with dedicated surface head positioning systems. It processes a di-bit quadrature pattern read from the servo surface by a preamplifier, such as the SSI 32H101 or SSI 32H116, and generates normal and quadrature (N and Q) position reference signals. These signals provide the servo controller with position error feedback. A complete position control system can be realized with the SSI 32H567 and its companion devices, the SSI 32H568 Servo Controller and SSI 32H569 Servo Motor Driver.

The SSI 32H567 incorporates an input amplifier with automatic gain control and offset cancellation, a phase locked loop and sync separator to recover timing information, and pulse area detectors to recover the position information embedded in a di-bit quadrature servo pattern. In addition, a bandgap voltage generator provides an analog reference level for the entire servo electronics path. External components are used to set the operating characteristics of the SSI 32H567, such as AGC response, VCO center frequency, PLL re-

sponse and sync separator threshold. Its high performance analog/digital circuitry is capable of supporting servo frame rates of up to 500 KHz.

### **FEATURES**

- Servo signal demodulation for Winchester disk drives with dedicated surface head positioning systems

- Supports industry standard di-bit quadrature servo pattern with frame rates up to 500 KHz

- N, Q outputs convey track crossing and position error information

- Pulse area detection technique for superior noise immunity

- PLL for timing recovery and synchronization

- Adjustable sync separator threshold

- · Auto-zeroing AGC input amplifier

- Precision bandgap voltage reference output

- Advanced bipolar process dissipates less than 850 mW (5V, 12V)

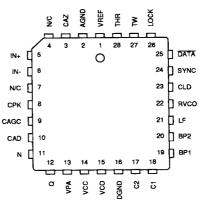

- Available in 28-pin PLCC, DIP, SO packages

#

### **FUNCTIONAL DESCRIPTION**

(Refer to block diagram, and typical application, Fig.2)

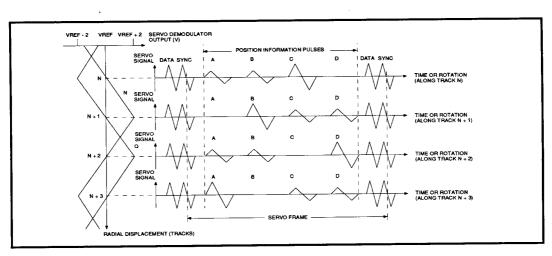

The SSI 32H567 processes servo position information which is read from a dedicated surface by a pre-amplifier. The servo information must conform to the 'di-bit quadrature' pattern which is illustrated in Figure 3. Servo frames, consisting of data and sync pulses followed by four information pulses (A, B, C, D) are prerecorded along each track of the servo surface. All the servo frames on an individual track are identical, but in the radial direction four different frame types are encountered, with every fourth track being identical. The N signal generated by the SSI 32H567 is proportional to the difference in sizes of pulses A and B, while the Q signal is proportional to the difference between pulses C and D. When the read head is off track, the read signal is effectively a linear interpolation between the prerecorded information of two adjacent tracks, making it possible to sense the head displacement exactly.

The SSI 32H567 has a differential input amplifier which incorporates offset voltage cancellation and automatic gain control. An external read preamplifier must provide a differential input signal of 23 to 400 mV peak to peak from the servo read head. This signal is applied to a pulse area detector whose output is proportional to the area under the positive half of the input pulse. The external capacitor Cap integrates the incoming pulses while they are positive, and is discharged when they go negative. This area detection technique provides improved noise immunity over voltage detection.

An AGC circuit adjusts the input gain so that the maximum pulse area detector output is 2V peak. The AGC circuit incorporates a peak detector which stores the maximum pulse area signal on the external capacitor Cpk. This signal is compared to an internal amplitude reference and the input amplifier gain is adjusted until they are equal. The capacitor CAGC determines the response time of the gain control circuit. An offset cancellation circuit, whose response is set with the external capacitor CAZ, ensures that the average level at the differential amplifier output is zero.

All internal analog signals are referenced to a 5.4V bandgap reference voltage. This level is available at the VREF output, which is capable of supplying 10 mA to the rest of the servo path electronics.

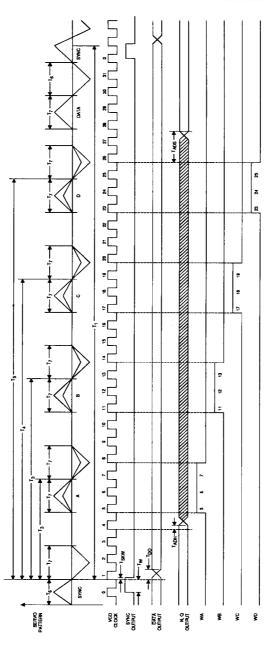

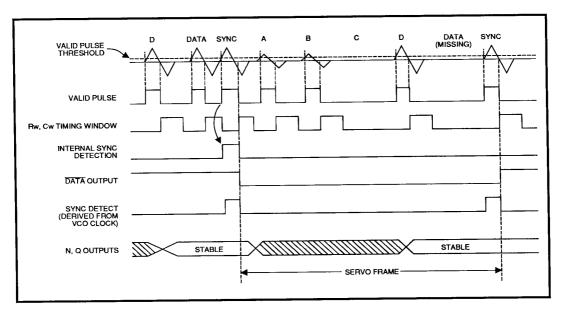

In a standard servo frame, the data and sync pulses are more closely spaced than the information pulses (A-D).

This allows the sync detect circuit to recover the SYNC pulses. A threshold, which is defined as percentage of the peak signal at the output of the AGC amplifier, is set externally with RTH. Pulses which exceed this threshold are defined as valid pulses (ie. potentially SYNC or DATA). As illustrated in Figure 5, at the end of the positive going half of a valid pulse, a window set by Rw and Cw is opened. If a second valid pulse occurs within this window, it is recognized as a SYNC pulse. This pulse becomes the input signal to a phase locked loop whose VCO clock frequency is 32 times the SYNC frequency (servo frame rate). The DATA output pin is low whenever a SYNC pulse is detected. The example illustrated in Figure 5 includes the case of a missing DATA pulse. The SYNC clock output, which marks the start of a new servo frame, is derived from the VCO output so that the clock continues to run when a data pulse is missing. Absolute positioning information such as track 0 and guardband flags may be encoded on the servo surface by the omission of data pulses.

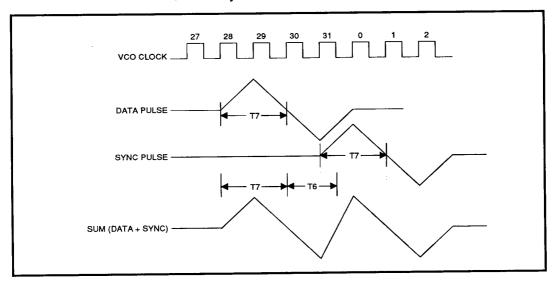

To generate the servo pattern shown in the timing diagram, Fig. 4, the DATA and SYNC pulses must be written to overlap as shown in Fig. 6.

The phase detector compares the detected sync pulses with the SYNC output. A current pulse proportional to the phase error is applied to an external loop filter network connected to the LF pin, to generate the VCO control voltage. If improved power supply rejection is required, bypassing may be provided at pins BP1 and BP2. The VCO center frequency is determined by the external components Rvco and Cvco.

A lock detect circuit measures the phase difference between the detected sync pulses and the sync output. When this difference exceeds half of a VCO clock cycle, a pulse of discharge current is applied to CLD. Otherwise a pulse of charging current is applied to CLD.

A clamp circuit limits the swing of the CLD pin and also insures that a small amount of hysteresis is present. When the voltage on CLD falls below the upper clamp level by more than the "lock margin," the LOCK output transistor is turned on. Likewise, when the voltage on CLD rises above the lower clamp level by more than the "unlock margin," the LOCK output transistor is turned off.

Internal timing windows are generated from the recovered SYNC pulse and VCO clock. These windows, WA, WB, WC, and WD, in Figure 4, enable the integra-

### FUNCTIONAL DESCRIPTION (Continued)

tion of the A, B, C, D pulses, respectively. Four peak detectors at the output of the pulse area detector are enabled in succession to capture the A, B, C and D information pulses, and the N and Q analog outputs are formed by differencing adjacent pulses. These outputs change during a servo frame and only become valid

after the D pulse has been detected. N and Q should be sampled by the servo controller on the next falling edge of the SYNC output clock.

An example of an entire servo path implemented with the SSI 32H567 and its companion devices, the SSI 32H568 and SSI 32H569, is shown in Figure 8.

FIGURE 2: Typical Application

0689

4-29

### PIN DESCRIPTION

### **POWER**

| NAME | TYPE | DESCRIPTION                                                                         |

|------|------|-------------------------------------------------------------------------------------|

| VREF | 0    | REFERENCE VOLTAGE - 5.4V output. All analog signals are referenced to this voltage. |

| AGND | -    | ANALOG GROUND                                                                       |

| VPA  | -    | ANALOG SUPPLY - 12V power supply.                                                   |

| VCC  | -    | DIGITAL SUPPLY - 5V power supply.                                                   |

| DGND | -    | DIGITAL GROUND                                                                      |

### INPUT AMPLIFIER

| NAME | TYPE | DESCRIPTION                                                                                                                                                         |

|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAZ  | -    | AUTOZERO CAPACITOR - A capacitor which sets the response of the input amplifier offset cancellation circuit should be connected between this pin and analog ground. |

| IN + | I    | NON-INVERTING INPUT - AGC input amplifier connection. The non-<br>inverting output of the differential servo pre-amplifier should be AC<br>coupled to this pin.     |

| IN - | I    | INVERTING INPUT - AGC input amplifier connection. The inverting output of the differential servo pre-amplifier should be AC coupled to this pin.                    |

| СРК  | -    | PEAK HOLD CAPACITOR - A capacitor which is used by the peak detector of the AGC circuitry must be connected between this pin and analog ground.                     |

| CAGC | -    | AGC CAPACITOR - A capacitor which sets the AGC attack and decay times must be connected between this pin and analog ground.                                         |

### **TIMING RECOVERY**

| NAME    | TYPE | DESCRIPTION                                                                                                                                                 |

|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vco     | 0    | VCO OUTPUT - TTL compatible digital clock which is 32 times the sync frequency (servo frame rate).                                                          |

| C2,C1   | -    | VCO CAPACITOR - Connection points for a capacitor which sets the VCO center frequency in conjunction with an external resistor connected to RVCO.           |

| BP1,BP2 | -    | PLL BYPASS - Bypass capacitors may be connected between these pins and analog ground to provide additional power supply rejection in the phase locked loop. |

4-30 0689

### TIMING RECOVERY (Continued)

| NAME | TYPE | DESCRIPTION                                                                                                                                                                                              |  |  |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LF   | -    | PHASE LOCKED LOOP FILTER - An external RC network which sets the PLL loop characteristics must be connected between this pin and analog ground.                                                          |  |  |

| RVCO | -    | VCO RESISTOR - Connection for a resistor which sets the VCO cente frequency, in conjunction with the capacitor between pins C1 and C2 The resistor must be connectedbetween this pin and the VREF output |  |  |

| SYNC | 0    | SYNC OUTPUT - TTL compatible digital clock whose falling edge indicates the presence of valid analog signals on the N and Q outputs. There is one SYNC cycle per servo frame.                            |  |  |

| DATA | 0    | DATA OUTPUT - Active low TTL compatible digital output that indicates the presence of a data pulse in the servo frame. This signal is updated on the falling edge of the SYNC output.                    |  |  |

| TW   | -    | TIMING WINDOW - A resistor and capacitor must be connected in parallel between this pin and analog ground to set a timing window which is used in detecting SYNC pulses.                                 |  |  |

| THR  | -    | PULSE THRESHOLD - A resistor which sets a threshold for SYNC and DATA pulse detection must be connected between this pin and VCC (digital 5V supply).                                                    |  |  |

| CLD  | -    | LOCK DETECT CAPACITOR - The value of this capacitor determines how quickly the LOCK output responds.                                                                                                     |  |  |

| LOCK | 0    | LOCK OUTPUT - An open collector output that indicates the lock status of the PLL.                                                                                                                        |  |  |

### **POSITION INFORMATION**

| NAME | TYPE | DESCRIPTION                                                                                                                                                                                                         |

|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAD  | -    | AREA DETECTOR CAPACITOR - A capacitor, which forms an integrator to sense the pulse area of the servo position signals, must be connected between this point and analog ground.                                     |

| N    | 0    | N OUTPUT - This sampled analog signal is the normal position reference output. N is referenced to VREF and is periodic in radial displacement, with a period of 4 tracks.                                           |

| Q    | 0    | Q OUTPUT - This sampled analog signal is the quadrature position reference output. Q is referenced to VREF and is periodic in radial displacement, with a period of 4 tracks. It is 90 degrees out of phase with N. |

### **ELECTRICAL SPECIFICATIONS**

### **ABSOLUTE MAXIMUM RATINGS**

(Maximum limits indicates where permanent device damage occurs. Continuous operation at these limits is not intended and should be limited to those conditions specified in the DC operating characteristics.)

| PARAMETER               | CONDITIONS       | MIN  | TYP | MAX     | UNITS |

|-------------------------|------------------|------|-----|---------|-------|

| VCC voltage             |                  | 0    |     | 8       | ٧     |

| VPA voltage             |                  | 0    |     | 16      | V     |

| Voltage on PLL inputs   |                  | -0.5 |     | VCC+0.5 | V     |

| Voltage on other inputs |                  | 0    |     | 14      | V     |

| Storage Temp.           |                  | -45  |     | 160     | °C    |

| Solder Temp.            | 10 sec. duration |      |     | 260     | °C    |

# RECOMMENDED OPERATION CONDITIONS (Unless otherwise noted, the following conditions are valid throughout this document.)

| PARAMETER               | CONDITIONS | MIN  | TYP | MAX  | UNITS |

|-------------------------|------------|------|-----|------|-------|

| VPA, analog supply      |            | 10.8 | 12  | 13.2 | ٧     |

| Supply noise            | F<1 MHz    |      |     | 0.1  | Vp-p  |

| VCC, digital supply     |            | 4.75 | 5   | 5.25 | V     |

| Ta, ambient temperature |            | 0    |     | 70   | °C    |

### DC CHARACTERISTICS

| PARAMETER                          | CONDITIONS  | MIN | TYP | MAX | UNITS |

|------------------------------------|-------------|-----|-----|-----|-------|

| IPA, VPA current                   |             |     |     | 50  | mA    |

| ICC, VCC current                   |             |     |     | 52  | mA    |

| VOH, digital output high           | IOH <40 μA  | 2.4 |     |     | V     |

| VOL, digital output low            | IOL <1.6 mA |     |     | 0.4 | V     |

| IREF, VREF output current capacity |             | 10  |     |     | mA    |

| VREF output voltage                | IREF <10 mA | 5.1 | 5.4 | 5.7 | V     |

### **ELECTRICAL SPECIFICATIONS (Continued)**

### **AC CHARACTERISTICS**

| PARAMETER                 | CONDITIONS                                                                    | MIN | TYP        | MAX | UNITS  |

|---------------------------|-------------------------------------------------------------------------------|-----|------------|-----|--------|

| VREF output impedance     | IOUT = 0-10 mA<br>1 μF bypass to AGND<br>Frequency<15MHz                      |     |            | 7   | Ω      |

| N, Q outputs              |                                                                               | •   |            |     |        |

| Output impedance          | F = 1 MHz                                                                     |     |            | 100 | Ω      |

| Load resistance           | To VREF                                                                       | 10  |            |     | ΚΩ     |

| Load capacitance          |                                                                               |     |            | 50  | pF     |

| Peak output voltage       | Referenced to VREF<br>23-400 mVp-p differential                               | 1.8 | 2          | 2.2 | ٧      |

| Offset voltage            |                                                                               |     |            | 10  | mV     |

| Input amplifier           |                                                                               |     |            |     |        |

| Input resistance          |                                                                               | 5   |            |     | ΚΩ     |

| Input resistance mismatch |                                                                               |     |            | 1   | %      |

| Input capacitance         |                                                                               |     |            | 20  | pF     |

| Bandwidth                 |                                                                               | 10  | 20         | -   | MHz    |

| Input referred noise      | 10 Hz <f<40 mhz<="" td=""><td></td><td>30</td><td></td><td>nV/√Hz</td></f<40> |     | 30         |     | nV/√Hz |

| CMRR                      | F<1MHz                                                                        | 60  |            |     | dB     |

| PSRR                      | F<0.5MHz                                                                      | 45  |            |     | dB     |

| AGC dynamic range         | Cad(pF)=720/fvco(MHz)                                                         | 26  |            |     | dB     |

| AGC headroom              |                                                                               | 2   |            |     | dB     |

| AGC bandwidth             | Open loop unity gain<br>Cagc=0.04 μF<br>Cpκ=1500 pF                           | 5   |            | 15  | KHz    |

| Autozero pole             | Caz in µF                                                                     |     | 220/Caz    |     | Hz     |

| SYNC detector             | •                                                                             | 1   |            |     |        |

| Timing window             | Rw in Ω, Cw in pF                                                             | 0   | .4(Rw • Cv | v)  | s      |

| Valid pulse threshold     | Rтн in KΩ (% of full scale)                                                   |     | 55/RTH     |     | %      |

| LOCK Detector             |                                                                               |     |            |     |        |

| CLD up current            | RVCO = 11K ± 1%                                                               | 0.7 |            | 3   | μΑ     |

| CLD down current          | RVCO = 11K ± 1%                                                               | 3   |            | 10  | μΑ     |

| CLD lock margin           |                                                                               | 0.7 |            | 1.3 | >      |

| CLD unlock marign         |                                                                               | 0.7 |            | 1.3 | ٧      |

| CLD hysteresis            |                                                                               | 0.1 |            | 0.4 | >      |

### AC CHARACTERISTICS (Continued)

| PARAMETER                  | CONDITIONS                           | MIN | TYP        | MAX   | UNITS     |

|----------------------------|--------------------------------------|-----|------------|-------|-----------|

| Phase locked loop          |                                      |     |            |       |           |

| Capture range              |                                      | 20  |            |       | %         |

| VCO phase shift            | Missing DATA pulse                   |     |            | 0.005 | rad/frame |

| VCO phase delay            | Relative to sync pulse zero crossing |     |            | 30    | ns        |

| VCO center frequency range |                                      | 4   |            | 16    | MHz       |

| Center frequency error     | Cvco, Rvco 1%                        |     |            | 15    | %         |

| VCO gain                   | fvco in Hz                           |     | 10.47 fvcd | )     | rad/s/V   |

| Phase detector gain        |                                      |     | 15.92      |       | uA/rad    |

### **TIMING CHARACTERISTICS**

(Digital output load capacitance CI<15 pF, VCO frequency fvco <16 MHz, timing measurements for digital signals are measured at 1.3V, unless otherwise noted.)

| PARAMETER                         | CONDITIONS | MIN | TYP | MAX | UNITS |

|-----------------------------------|------------|-----|-----|-----|-------|

| TDD, data delay                   |            |     |     | 20  | ns    |

| TW, sync pulse width              |            | 40  |     |     | ns    |

| TSKW, SYNC to VCO skew            |            | 0   |     | 40  | ns    |

| SYNC fall time                    |            | 15  |     |     | ns    |

| TADS, N or Q<br>output setup time |            | 260 |     |     | ns    |

| TADH, N or Q<br>output hold time  |            | 0   |     |     | ns    |

| T1 accuracy, T1-32/fvco           |            | -8  |     | 8   | ns    |

| T2 accuracy, T2-6/fvco            |            | -4  |     | 4   | ns    |

| T3 accuracy, T3-12/fvco           |            | -4  |     | 4   | ns    |

| T4 accuracy, T4-18/fvco           |            | -4  |     | 4   | ns    |

| T5 accuracy, T5-24/fvco           |            | -4  |     | 4   | ns    |

| T6 accuracy, T6-1.5/fvco          |            | -5  |     | 10  | ns    |

| T7 accuracy, T7-2/fvco            |            | -5  |     | 10  | ns    |

### **APPLICATIONS INFORMATION**

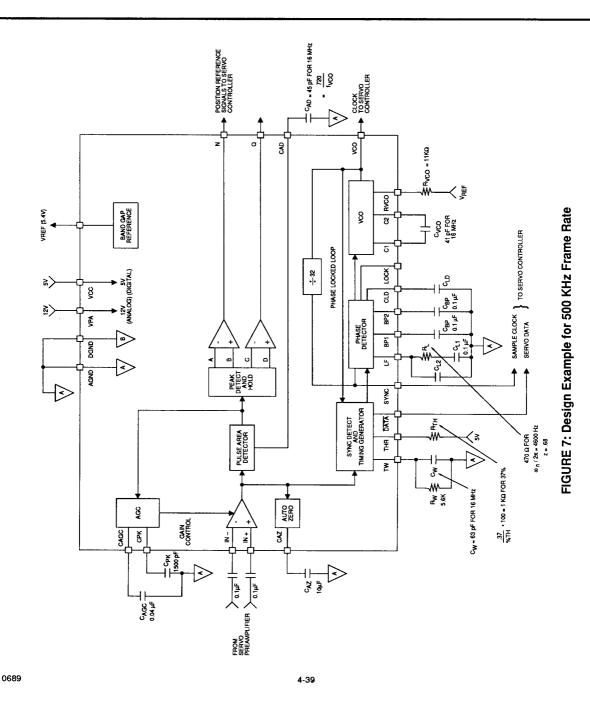

A typical SSI 32H567 application is shown in Figure 2. The selection criteria for the external components shown are discussed below.

#### **INPUT AMPLIFIER**

The autozero circuit is effectively a high pass filter, whose pole frequency is given by:

$$f_{AZ} = \frac{220}{C_{AZ}(\mu F)} Hz$$

With a value of 10  $\mu$ F for CAz, the autozero circuit's corner frequency will be 22 Hz. This is sufficient for DC offset rejection and it will not interfere with the servo signal.

The AGC response may be characterized in terms of the open loop unity gain bandwidth of its control loop. The nominal value for this loop is set by CAGC as follows:

$$f_{BW} = \frac{390}{C_{AGC}(\mu F)} Hz$$

For a nominal bandwidth of 10 kHz, Cagc should be 0.039  $\mu$ F. With a 1% capacitor, the variation in actual bandwidth will be +/- 50% due to the tolerance of internal components. The AGC peak detector capacitor should always be set to 1500 pF. This represents a reasonable tradeoff between leakage current tolerance and storage aperture time.

The pulse area detector storage capacitor must be chosen to keep the AGC circuit operating within its linear range. Its value is related to the VCO frequency as follows:

$$C_{AD} = \frac{720}{f_{VCO}(MHz)} pF$$

, where  $f_{VCO}$  is the VCO freq.

Larger values for CAD are required with lower VCO frequencies in order to maintain constant signal levels within the device, since the integration time is increased.

### SYNC DETECTOR

Two sync detector parameters may be adjusted with external components. The first is the valid pulse threshold. The threshold is expressed as a percentage of a full scale pulse (since the sync detector follows the AGC and input amplitude variations are removed). The threshold is determined with resistor RTH as follows:

Threshold =

$$\frac{0.37}{R_{TH}(K\Omega)} \cdot 100(\%)$$

For example, a value of RTH = 1  $K\Omega$  sets the valid pulse threshold at 37% of full scale. This prevents false triggering on noisy signals, but does not unduly shorten the sync pulse.

A timing window is used to detect sync pulses, since the sync and data pulses are more closely spaced than any other pulses in a valid servo signal. The delay from the zero crossing of the data pulse to the leading edge of the sync pulse is 1.5 cycles of the VCO clock. The next most closely spaced pulses (which must be rejected by the sync detect circuit) are separated by 3 VCO cycles. Thus the timing window should be set for 2.25 cycles of the VCO clock, to allow reliable detection of the sync pulse. The timing window is determined as follows:

Window =

$$0.4 (R_w \cdot C_w)(s)$$

The resistor Rw should always be set to 5.6 K $\Omega$ , which means that for a 2.25 cycle window, Cw is given by:

$$C_W = \frac{1000}{f_{VCO}(MHz)} pF$$

For a 16 MHz clock, Cw should be chosen as 63 pF.

### LOCK DETECTOR

The LOCK detector behavior is controlled by the value of CLD. A value too small will be prone to unlock prematurely and give false warnings to the system. A typical value for CLD is 0.01  $\mu$ F.

### **APPLICATIONS INFORMATION (Continued)**

#### PHASE LOCKED LOOP

The VCO center frequency is determined by Rvco and Cvco. Rvco should always be set to 11 K $\Omega\pm$ 1%. Cvco may then be chosen by:

$$C_{VCO} = \frac{830}{f_{VCO}} - 10.6 \, pF,$$

where fvco is the desired center frequency in MHz.

For fvco = 16 MHz, Cvco = 41 pF and for fvco = 4 MHz, Cvco = 200 pF. If 1% tolerance external components are used, the VCO absolute frequency accuracy will be 15%. The VCO output frequency is related to the control voltage at the loop filter pin, VLF, as follows:

$$\frac{10}{f_{VCO}}$$

= 1 + 1.667 ( V<sub>LF</sub> - V<sub>LFBAS</sub>)

This means that the VCO gain, Ko, is given by:

$$K_0 = 2 \cdot \pi \cdot f_{VCO}(Hz) \cdot 1.667 \text{ rad/s/V}$$

The phase detector is a digitally controlled charge pump, which injects a current into the loop filter whose average value is proportional to the phase error. The detector gain, Kd, is fixed at  $15.92\,\mu\text{A/rad}$ . If a loop filter consisting of a series resistor and capacitor is used, as shown in Figure 2, the phase locked loop becomes a second order system with the following transfer function:

$$\frac{\text{phase error}}{\text{input phase}}(s) = \frac{(s/\omega n)^2}{1 + 2 \cdot z \cdot s/\omega n + (s/\omega n)}$$

where:

$$\omega$$

n ( natural freq. ) =  $\sqrt{((K_d \cdot K_0/(32 \cdot C_{L1})))}$  rad/s

z (damping factor) =

$$0.5 \cdot R_L \cdot C_{L1} \cdot \omega n$$

As an example, the values for Cvco, RL and CL are derived for a system with the following specifications:

$$f_{VCO} = 16 \text{ MHz } \omega n (2 \cdot \pi) = 4600 \text{ Hz } z = 0.68$$

$$C_{VCO} = \frac{830}{f_{VCO}} - 10.6 = 41 \text{ pF}$$

$$C_{L1} = \frac{K_d K_0}{32 \cdot \omega n^2} = \frac{(15.92 \cdot 10e - 6) (10.47 \cdot 1/vco)}{32 (2 \cdot \pi \cdot 4600)^2} = 0.1 \,\mu F$$

$$R_L = \frac{2 \cdot z}{C_{L1} \cdot \omega n} = 470 \,\Omega$$

FIGURE 3: Pre-recorded Servo Signal and Servo Demodulator Output vs. Radial Displacement

0689

4-37

FIGURE 5 : Sync and DATA Pulse Detection

FIGURE 6 : Servo Writer Data-Sync Pulse Generation

FIGURE 9: Complete Example of Servo Path Electronics Using SSI 32H567/6220/6230 Chip Set

Powered by ICminer.com Electronic-Library Service CopyRight 2003

(TOP VIEW)

28-Pin PLCC

### ORDERING INFORMATION

| PART DESCRIPTION              | ORDER NO.     | PKG. MARK |  |  |

|-------------------------------|---------------|-----------|--|--|

| SSI 32H567, Servo Demodulator |               |           |  |  |

| 28-Pin DIP                    | SSI 32H567-CP | 32H567-CP |  |  |

| 28-Pin PLCC                   | SSI 32H567-CH | 32H567-CH |  |  |

| 28-Pin SO                     | SSI 32H567-CL | 32H567-CL |  |  |

No responsibility is assumed by SSi for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of SSi. SSi reserves the right to make changes in specifications at any time without notice.