# **Preliminary Data**

May 1993

### DESCRIPTION

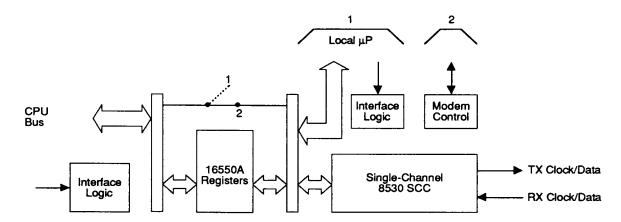

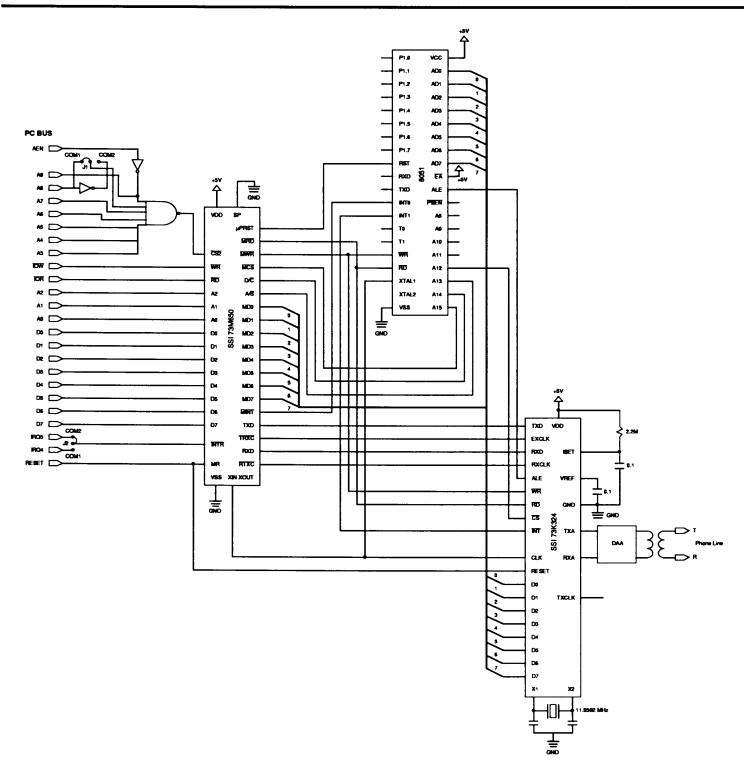

The SSI 73M650 Serial Packet Controller (SPC) is a multifunction synchronous/asynchronous communications IC that simplifies synchronous communications interface to a standard PC peripheral bus. The SPC consists of the control and FIFO registers of a 16550A UART combined with one channel of an 8530 SCC. It operates in two basic configurations.

The Dual-Processor configuration has two parallel interface ports, one for connection to a CPU and the other to a local protocol controller. The local controller can then use the SCC block for synchronous or asynchronous protocols.

The Single-Processor configuration can be used in either a Mailbox or Non-mailbox mode. The Mailbox mode uses the same internal configuration as Dual-Processor, but all registers are accessible through only one hardware port. This allows the CPU to replace the function of the local controller while the SPC maintains the standard asynchronous interface. In the Non-mailbox mode, the SPC is simply a 16550A and one channel of an 8530 in the same package. The user may select either the 16550A block or the 8530 block.

### **FEATURES**

- Register compatibility with 16550A UART

- Functional superset of a single channel 8530 SCC

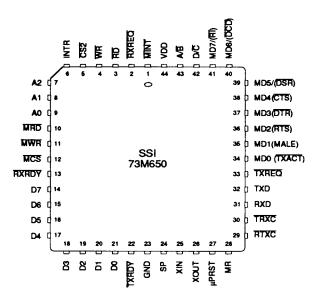

- DMA signals available in 44-pin package

- NRZ, NRZI, FM and Manchester encode and decode

- 32-bit CRC for V.42 compatibility

- 3 or 16 byte Rx and Tx FIFOs for SCC reduces interrupt overhead

- External devices can be mapped into PC I/O space

- Static design with Oscillator Disable for low power standby operation

- Clock pre-divide to allow input of higher frequency processor clocks

- 16-byte UART receive FIFO always active to reduce CPU overhead

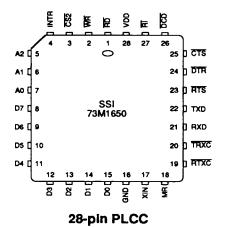

- Space-saving 28-pin version (73M1650)

- Bus timing compatible with PCMCIA Release 2

#### **BLOCK DIAGRAM**

- 1) Dual Processor Only

- 2) Single Processor Only

0593 - rev.

### **FUNCTIONAL DESCRIPTION**

The SSI 73M650 Serial Packet Controller (SPC) simplifies high speed packetized serial communications in the PS/2 or PC bus environment.

### **FUNCTIONAL BLOCKS**

The SPC is configured as two main blocks: the 16550A Main Processor UART Register block which facilitates interface to software packages written for 16450/16550A UARTs, and a Serial Communication Controller block (SCC) which is an enhanced version of one channel of an 8530.

### 16550A UART Register Block

The UART Register block is hardware- and register-compatible to a 16550A UART and will run most existing software packages. Additional bits to control power down and other features are available through a special hardware mode called Single-Chip-Select (SINGLECS).

A distinct feature of the 73M650 is the accessibility of all these registers to a second processor through Channel-Bin the Dual-Processor configuration. The local processor can then modify these registers and the data FIFOs to perform compression and/or error correction (such as V.42bis) at a very high speed. This is not currently possible using standard products.

The scratchpad register, acting as a Mailbox, allows communication between the CPU and a local processor or microcontroller.

#### **SCC Block**

The SCC block implements the operation of one-channel (channel A) of an 8530 SCC. Some improvements in the 73M650 over the 8530 may require modifications to be made to the software currently available for the 8530.

The SCC block performs asynchronous data transfer and packetized synchronous protocols such as Monosync, Bisync, HDLC and SDLC. Included in this block are a baud rate generator, a Digital Phase Locked Loop (DPLL) for clock recovery, and a three-byte FIFO in the SCC transmit and receive path. The SCC block has NRZ, NRZI, FM and Manchester data encoding and supports a 32-bit CRC, useful in the V.42bis error correction standard.

The SPC can operate at up to 6 Mbit/s data rate. The crystal rate may be as high as 20 MHz with an internal programmable prescaler.

#### **REGISTER SETS**

The SSI 73M650 SPC contains three register sets:

### **Main Processor UART Registers**

This register set is virtually identical to a 16550A register set. In a special hardware mode called Single-Chip-Select (SINGLECS), additional bits are introduced into these registers.

#### **Channel A Registers**

This register set is similar to 8530 Channel A registers and controls the asynchronous and synchronous serial port.

### **Channel B Registers**

This register set allows for access by a second processor or software package to the main processor 16550A data. An additional register contains a clock prescaler and oscillator shut down.

#### **PRODUCT CONFIGURATIONS**

The SPC is used in either single- or dual-processor environments with different applications as follows:

- When a local processor is available for high speed packetized applications, the Dual-Processor configuration is selected by tying the SP pin to GND. In this configuration the local processor and the CPU use separate hardware pins to access the SPC. The 16550A and SCC blocks are accessed independently.

- 2. When no local processor is needed, the SPC is used in the Single-Processor configuration and the SP pin is connected to +5V.

For maximum functionality, the SPC can operate in a unique register access arrangement called Single-Chip-Select (SINGLECS). This is the <u>only</u> operating mode for the 28-pin version (73M1650), and <u>can</u> be selected in 40- and 44-pin versions by tying the <u>CS2</u> and <u>MCS</u> pins together.

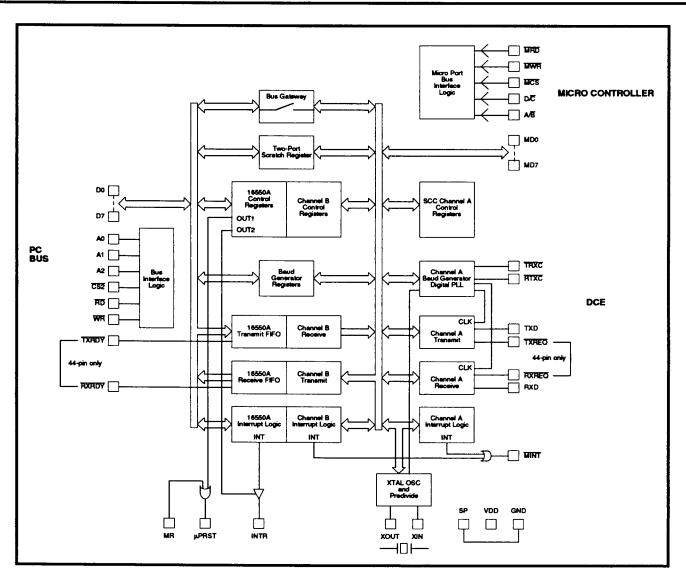

### **Dual-Processor Configuration**

When the SP pin is connected to GND, the SPC is put into the Dual-Processor configuration. In this configuration, the main CPU and local processor use separate address, data and control pins to access the SPC. The 16550A registers are controlled by the CPU. Some of these registers are accessible to a local processor via Channel B through separate pins. The local processor uses Channel A for serial data transfer.

Upon any change in the 16550A register contents and FIFOs status, an interrupt can be generated to notify the local processor that the CPU has accessed the SPC.

Note that in Dual-Processor configuration the Modem Control and Status signals (RTS, CTS, etc.) are available to the main CPU via the 16550A registers.

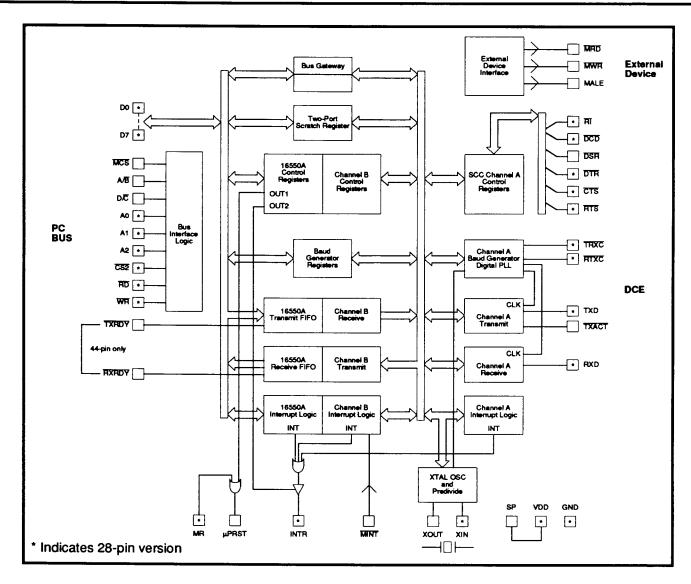

### Single-Processor Configuration

When the SP pin is connected to +5V, the SPC operates in the Single-Processor configuration. The CPU has access to all of the registers in the SPC using one data bus (D0-D7), one read strobe ( $\overline{RD}$ ) and one write strobe ( $\overline{WR}$ ). The address and chip select pins may be connected in the following ways:

- When maximum firmware compatibility to 16550A/ 8530 operation is desired, the main CPU accesses different registers as follows:

- a. CS2, A0-A2 to access main port 16550A registers.

- b. MCS, A/B, D/C to access Channel A and Channel B.

- 2. When maximum functionality is desired, the CS2 and MCS pins are tied together to take the SPC into (the Single-Chip-Select (SINGLECS) mode. In this (mode, which is the only operating mode for the 28-pin version (73M1650), new bits are added to the 16550A registers to allow for the following features:

- a. Transmit FIFO trigger level control.

- b. DMA TXRDY and RXRDY status bits.

- Programmable access to the three register sets using bits 7, 6 of 16550A IER (REGSEL1, REGSEL0 bits).

- d. Access to an external device by setting both REGSEL1 and REGSEL0 bits. In this unique application of the 73M650, proper signals to access a multiplexed address/data bus component (ALE, MRD, MWR) are generated allowing access to the external device in two cycles. This application greatly simplifies the required hardware for interface of PC bus to a local device.

### Mailbox Mode

When the PE bit (bit 7 of Channel B, CCR) is set, the CPU can independently access the 16550A and SCC blocks. The SPC has the same internal set-up as the Dual-Processor configuration, however the hardware access to different registers is through only one data bus. The SCC block is now accessible to the CPU.

This allows the user to develop software drivers for the CPU to access and modify the data transmitted or received by a standard software package. This feature is useful in multi-tasking environments.

An interrupt can be sent to the CPU to invoke the operation of the auxiliary software package whenever data is transferred by the main processor. The auxiliary software package can then read the data FIFOs, modify the data by compression or error correction and transmit the new data using the SCC block.

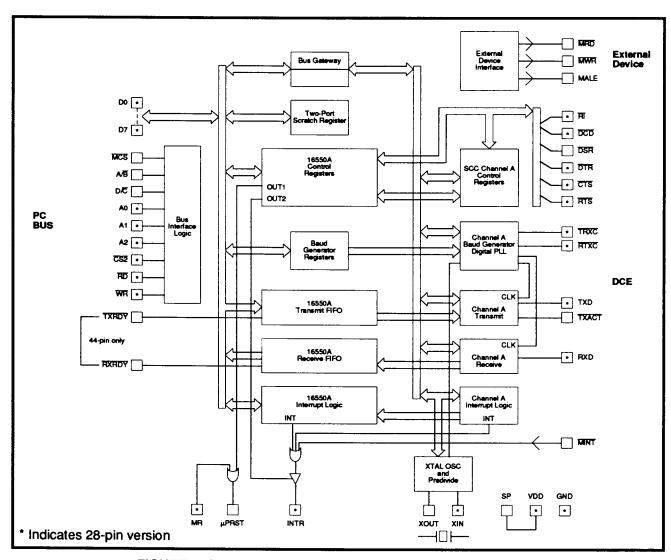

#### Non-mailbox Mode

When the PE bit (bit 7 of Channel B, CCR) is cleared, the main CPU can access either the 16550A or SCC block. The SPC effectively behaves as either a 16550A or a single-channel 8530 in the same package, always operating as the block (16550A or 8530) that was last accessed.

# FEATURES COMPARISION BETWEEN SERIAL PACKET CONTROLLER (SSI 73M650) AND SERIAL COMMUNICATIONS CONTROLLER (SCC)

SCC

### **CAPABILITIES**

- Two independent full-duplex channels

- PCLK clock required for operation

- Synchronous/Isosynchronous data rates:

- Up to 1/4 PCLK (i.e., 2.5 Mbit/s) maximum data rate with 10 MHz PCLK using an external phase lock loop for clock recovery

- Up to 625 kBit/s with a 10 MHz clock rate. Up to 500 kBit/s with a 8 MHz clock rate (FM encoding using a digital phase lock loop)

- Up to 372.5 kBit/s with a 10 MHz clock rate.

Up to 250 kBit/s with a 8 MHz clock rate (NRZI encoding using a digital phase locked loop)

- Asynchronous capabilities:

- 5, 6, 7, or 8 bits per character

- 1, 1.5, or 2 stop bits

- Odd, even, or no parity

- Multiples of 1, 16, 32, 64 of clock

- Break generation and detection

- Parity, overrun and frame error detection

- Byte oriented synchronous capabilities:

- Internal or external character synchronization

- 1 or 2 synchronization capabilities

- Automatic cyclic redundancy check generation and detection

. One full dupley

**CAPABILITIES**

- One full-duplex channel

- Two emulation modes 73M550, 8530

- Single- or Dual-Processor supported

- · Fully static operation, no clocks required

SSI 73M650

- Clock turn-off through register set for very low power standby operation

- Synchronous/Isynchronous data rates:

- Up to 1 time CLK (i.e., 6 Mbit/s) maximum data rate using an external phase lock loop for clock recovery

- Up to 1250 kBit/s with a 20 MHz clock rate. (FM encoding using a digital phase lock loop)

- Up to 625 kBit/s with a 20 MHz clock rate. (NRZI encoding using a digital phase locked loop)

- Asynchronous capabilities:

- 5, 6, 7, or 8 bits per character

- 1, 1.5, or 2 stop bits

- Odd, even, or no parity

- Multiples of 1, 16, 32, 64 of clock

- Break generation and detection

- Parity, overrun and frame error detection

- · Byte oriented synchronous capabilities:

- Internal or external character synchronization

- 1 or 2 synchronization capabilities

- Automatic cyclic redundancy check generation and detection

# SCC

### SDLC/HDLC capabilities:

- Abort sequence generation and checking

- Automatic zero insertion and deletion

- Automatic flag insertion between messages

- Address field recognition

- I-field residue handing, no direct valid bit count recognition

- Automatic 16-bit cyclic redundancy generation in idle flag mode only

- Automatic CRC detection

- SDLC loop mode with EOP recognition/loop entry and exit

### Data Buffering:

- Receiver contains a 3 byte FIFO plus receiver shift register

- Transmitter contains a 1 byte FIFO plus transmit shift register

### Data Encoding:

- NRZ, NRZI, or FM encoding/decoding

- Manchester decoding only

### SSI 73M650

### · SDLC/HDLC capabilities:

- Abort sequence generation and checking

- Automatic zero insertion and deletion

- Automatic flag insertion between messages

- Address field recognition

- I-field residue handing, indicates directly a valid bit count

- Automatic 16 SDLC, 32 V.42bis bit cyclic redundancy generation/detection

- SDLC loop mode with EOP recognition/loop entry and exit

### Data Buffering:

#### Single Processor -

- Receiver contains a 16 byte FIFO plus receiver shift register

- Transmitter contains a 16 byte FIFO plus transmit shift register

### **Dual Processor --**

- Receiver contains a 3 byte FIFO plus receiver shift register

- Transmitter contains a 3 byte FIFO plus transmit shift register

### Data Encoding:

- NRZ, NRZI, or FM encoding/decoding

- Automatic manchester decoding and encoding for fiber optics

### Automatic Controls:

- Automatic transmitter control

- Fully automatic SDLC transmission in mark idle

- Automatic transmitter control for common transmitter bus configuration in single processor

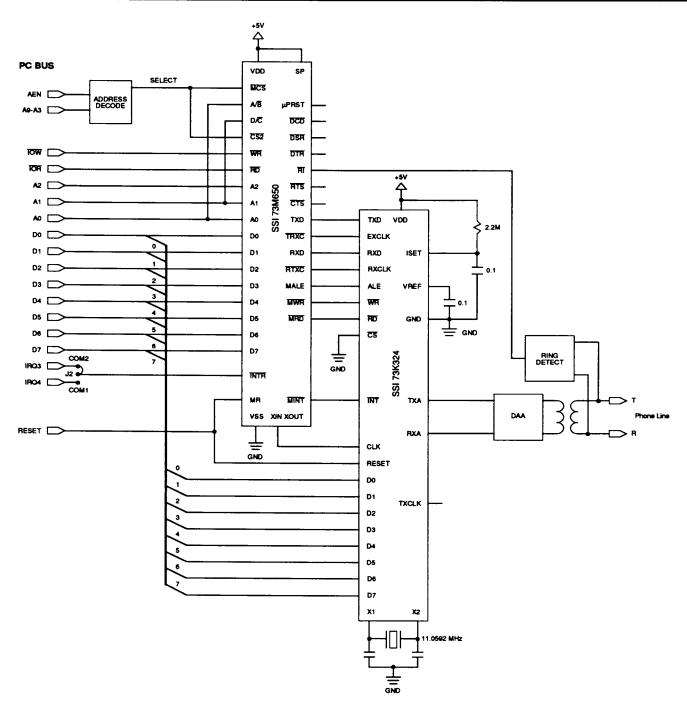

FIGURE 1: Dual-Processor Block Diagram

(Not Available on 28-Pin version)

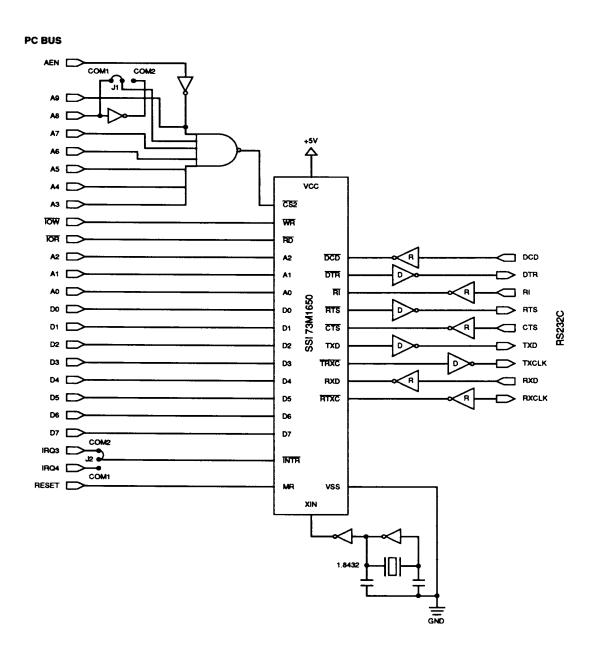

FIGURE 2: Single-Processor Mailbox Mode Block Diagram

FIGURE 3: Single-Processor Non-Mailbox Mode Block Diagram

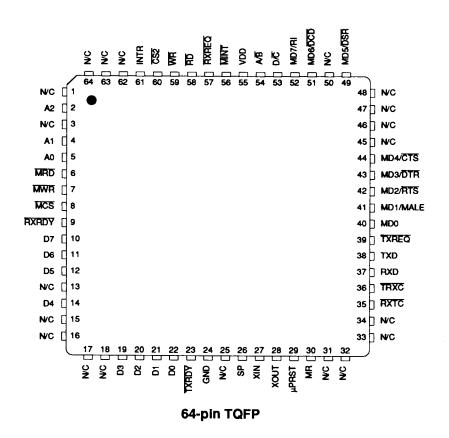

# **PIN DESCRIPTION**

Pins marked by \* are available in 28-pin version (73M1650).

| NAME   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD *  | 1    | +5V Supply, ±10%. Bypass with a .1 μF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND *  |      | System Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SP     | 1    | Single-Processor Mode Select. When high, selects Single-Processor mode. When low, selects Dual-Processor mode.                                                                                                                                                                                                                                                                                                                                                                                      |

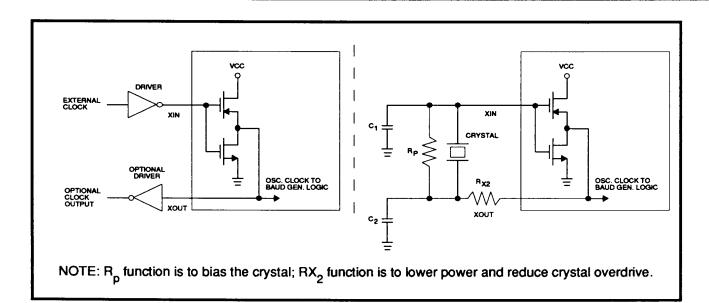

| XIN *  | l    | Crystal/Clock Input. When a crystal is used for the time base, it is connected between this pin and XOUT. When an external clock is used, this pin requires a TTL logic level signal at maximum frequency of 20 MHz. By programming the 4-bit prescaler (bits 0, 1, 2, 3 of Channel B CCR), the external clock frequency can be adjusted to supply the required internal clock.                                                                                                                     |

| XOUT   | 1/0  | Crystal output. When a crystal is used for the time base, it is connected between this pin and XIN.                                                                                                                                                                                                                                                                                                                                                                                                 |

| MR *   |      | Master Reset. When high, internal registers are initialized. This signal should be brought low for the normal operation of the SPC. A high on MR generates a high on the μPRST pin.                                                                                                                                                                                                                                                                                                                 |

| μPRST  | 0    | Local Microprocessor Reset. This signal follows the state of MR signal and is used to reset a local microprocessor. Programming the μPRST bit (bit 2 of 16550A MCR) to a high will also generate an active high signal on this pin.                                                                                                                                                                                                                                                                 |

| TXD •  | 0    | Serial Transmit Data. The serial data is updated on the rising edge of the internal transmit clock. The source of transmit clock is either an inverted version of the TRXC/RTXC pins signal or the output of Baud Rate Generator or the DPLL.                                                                                                                                                                                                                                                       |

| TRXC * | I/O  | Synchronized Clock. The function of this pin is controlled by the TRXCO/I bit (bit 2 of Channel A WR11). If the TRXCO/I bit is set, this pin is an output clock whose rising edge can be used to sample TXD signal. When the source of the transmit clock is selected to be this pin by programming bits 4, 3 of Port-A WR11 to 01, the serial transmit data (TXD) pin is updated on the falling edge of this signal. If the TRXCO/I bit is cleared, this pin functions as an input transmit clock. |

| RXD *  | l    | Serial Receive Data. Serial data is sampled on the falling edge of the internal receive clock. The source of the receive clock is either an inverted version of the TRXC/RTXC pins signal or the output of Baud Rate Generator or the DPLL.                                                                                                                                                                                                                                                         |

# PIN DESCRIPTION (Continued)

Pins marked by \* are available in 28-pin version (73M1650).

| NAME   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTXC * | I    | Synchronized Receive Clock. When an external receive clock source is selected by clearing bits 4, 3 of Channel A WR11, the data on the RXD pin is sampled on the rising edge of this signal. The received clock may also be supplied by the TRXC pin, Baud Rate Generator or the DPLL, in which case this pin has no function. In comparison with the 8530, this pin has no accommodation for an external crystal to supply the receive clock.                                                                                                                                                                                                                                                                                           |

| TXRDY  | Ο    | DMA Transmit Request. Available on the 44-pin version only; shows the status of the 16550A transmit FIFO. In the non-FIFO or 16450 mode (bit 0 FCR cleared) or when no DMA is selected (bit 3 FCR cleared), TXRDY goes active low when there is no character in the transmit FIFO and returns high when the first character is loaded into the FIFO. In the FIFO mode (bit 0 FCR set) and when DMA is selected (bit 3 FCR set), TXRDY goes active low as the transmit FIFO trigger level is reached and goes inactive high when the FIFO is completely full. If the Silicon Systems enhancement mode is not selected (bit 5 IER cleared), TXRDY goes active when the FIFO is not full. This is equivalent to a FIFO trigger level of 15. |

| RXRDY  | 0    | DMA Receive Ready. Available on the 44-pin version only; shows the status of the 16550A receive FIFO. In the non-FIFO or 16450 mode (bit 0 FCR cleared) or when no DMA is selected (bit 3 FCR cleared), this signal goes active low when there is at least one character in the receive FIFO. It returns inactive high when there are no more characters in the receive FIFO. In the FIFO mode (bit 0 FCR set) and DMA operation (bit 3 FCR set), this signal goes active low as the receive FIFO trigger level is reached or timeout is occurred. RXRDY returns to the inactive high level when there are no characters in the receive FIFO.                                                                                            |

| TXREQ  | 0    | DMA Transmit Request. Available on the 44-pin version only; shows the status of the 8530 three-byte transmit FIFO. TXREQ goes active low when the transmit FIFO is empty. It goes high when the FIFO is not empty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RXREQ  | 0    | DMA Receive Request. Available on the 44-pin version only; shows the status of the 8530 three-byte receive FIFO. RXREQ goes active low when data is available in the receive FIFO. It goes inactive high when the receive FIFO is completely empty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# Main processor 16550A port:

Function and timing of these pins are similar to 16550A.

| NAME    | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                   |

|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D7 * | I/O  | Data Bus. This bus provides bi-directional communication between the SPC and the main CPU. In Dual-Processor mode, the 16550A registers are accessed by this bus. In the Single-Processor mode; 16550A registers, Channel A and Channel B registers are accessed by this bus. |

## PIN DESCRIPTION (Continued)

Main processor 16550A port: (Continued)

Function and timing of these pins are similar to 16550A.

Pins marked by \* are available in 28-pin version (73M1650).

| NAME  |   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                          |

|-------|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A2 | * | -    | Register Select Address. These signals determine the address of the 16550A register to be accessed. Eight registers are selected when DLAB bit (bit 7 of 16550A LCR) is low or upon reset. Two additional registers are accessed when DLAB is set high.                                                                              |

| CS2   | • | -    | Chip Select, Main port. When low while $\overline{RD}$ or $\overline{WR}$ are low, allows reading or writing of the registers. In the Dual-Processor mode only the 16550A registers are accessed using this pin. In the Single-Processor mode, 16550A port as well as Channel A and Channel B registers are accessed using this pin. |

| RD    | * | I    | Read Strobe. When low while $\overline{\text{CS2}}$ is low, the contents of the register addressed by A0-A2 or A/ $\overline{\text{B}}$ ,D/ $\overline{\text{C}}$ may be read to the D0-D7 data bus.                                                                                                                                 |

| WR    | • | 1    | Write Strobe. When low while $\overline{CS2}$ is low, the contents of the D0-D7 data bus are written to the register selected by A0-A2 or A/ $\overline{B}$ ,D/ $\overline{C}$ on the rising edge of this signal. No change is made to the register which is marked to be READ-ONLY.                                                 |

| INTR  | • | 1    | Interrupt, High-impedance. This pin goes high whenever attention is requested from the main CPU. Clearing the E1 bit (bit 3 of 16550A MCR), places this pin in a high impedance state, allowing multiple ICs to share one CPU interrupt signal.                                                                                      |

### Channel A and Channel B in Dual-Processor Configuration:

Pins marked by # have a different function in the Single-Processor configuration.

| NAME    | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MD0-7 # | I/O  | Data Bus, Local Processor: Allows access to Channel A and Channel B. This bus is controlled by the local processor.                                                                                                                                                                                                                                                                               |

| A∕B     | l    | Port Select Address: Controlled by the local processor. When high selects Channel A (USART) to transmit and receive data serially. When low allows access of the local processor to the main port (16550A) registers through Channel B.                                                                                                                                                           |

| D/C     | 1    | Command or Data Select Address: When low, a command register within Channel A or Channel B is selected. Command registers are selected in two cycles: the register address is first written into the lower four bits of command register, and the desired data is subsequently written to the selected command register. When high, the serial transmit/receive data is transferred in one cycle. |

| MCS #   | 1    | Chip Select, Local Processor: In combination with the MRD and MWR; allows access to Channel A and Channel B registers.                                                                                                                                                                                                                                                                            |

### PIN DESCRIPTION (Continued)

Channel A and Channel B in Dual-Processor Configuration: (Continued)

Pins marked by \* are available in 28-pin version (73M1650).

Pins marked by # have a different function in the Single-Processor configuration.

| NAME |   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MRD  | # | _    | Read Strobe, Local Processor. When low while $\overline{\text{MCS}}$ is low, the contents of the selected register in Channel A or Channel B is transferred to the data bus. The serial data register (D/ $\overline{\text{C}}$ high) can be read in one cycle. When reading the command register (D/ $\overline{\text{C}}$ low), the command register address is determined by bits 0, 1, 2, 3 of WR0. To read a new command register a write cycle to WR0 to change the register address should be done prior to the read cycle.                           |

| MWR  | # | -    | Write Strobe, Local Processor. When low while $\overline{MCS}$ is low, contents of the data bus is written into the selected register in Channel A or Channel B if the register is not marked READ-ONLY. Writing into the serial data register (D/ $\overline{C}$ high) can be done in one cycle. When writing the command register (D/ $\overline{C}$ low), The command register address is determined by bits 0, 1, 2, 3 of WR0. To write to a new command register, a write cycle to change the register address should be done prior to the write cycle. |

| MINT | # | 0    | Interrupt, Local Processor, Weak Pullup. When low, notify the local processor an unmasked interrupt event occurred, caused by either an access to the 73M550 register set by the main CPU or by an unmasked interrupt occurring in the SCC. A 10K pullup resistor should be utilized between this pin and the VCC pin to provide a fast rise time at the end of interrupt. This high impedance state allows multiple ICs to share one CPU interrupt signal.                                                                                                  |

# **Channel A and Channel B in Single-Processor Configuration:**

Pins marked by \* are available in 28-pin version (73M1650).

Pins marked by # have a different function in the Dual-Processor configuration.

| NAME  | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| A/B I |      | Channel Select Address. When high, selects Channel A (USART) transmit and receive data serially. When low, allows access to the Ma Processor (16550A) registers through Channel B. This signal is only use when the MCS is low.                                                                                                                                                                                                                                 |  |  |  |  |

| D/C   | 1    | Command or Data Address Select. When low, a command register within Channel A or Channel B is selected. Individual registers are selected in two cycles: The address of the register is first written into the lower four bits of the command register then desired data is subsequently read from or written into the command register. When high, the serial transmit/receive data is transferred in one cycle. This signal is only used when the MCS is low. |  |  |  |  |

# PIN DESCRIPTION (Continued)

Channel A and Channel B in Single-Processor Configuration: (Continued)

Pins marked by \* are available in 28-pin version (73M1650).

Pins marked by # have a different function in the **Dual-Processor** configuration.

| NAME |    | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCS  | #  |      | Chip select, Channel A and Channel B. Access to the SPC registers is controlled by this signal and CS2. When these signals are not tied together and individually controlled, the last block selected (16550A or Channel A/B) controls the operation of the serial port. When this signal is tied to CS2, The SPC is put into the Single-Chip-Select (SINGLECS) mode and access to the registers is controlled by two bits in the 16550A IER register (REGSEL1, REGSEL0). Setting REGSEL1 bit enables access to an external device in two cycles.In the SINGLECS mode, new bits are introduced in the Main Processor 16550A registers, allowing additional features. |

| MALE | #  | 0    | External Device ALE. When in the Single-Chip-Select (SINGLECS) mode and RSEL1 bit is set, this signal is used by the external device to latch the address of its registers. MALE is an inverted version of the WRB signal in the first cycle of an external device access. Data is transferred to the external device in the subsequent cycle using the MWR or MRD signal. When not in the SINGLECS mode, this pin remains high.                                                                                                                                                                                                                                     |

| MWR  | #  | 0    | External Device Write Strobe. When in the Single-Chip-Select (SINGLECS) mode and RSEL1 bit is set, this signal follows the WR signal issued by the main processor in the second cycle of an external device access. Data present on the main processor data bus (D0-D7) can be written into the external device. When not in SINGLECS mode, this pin remains high.                                                                                                                                                                                                                                                                                                   |

| MRD  | #  | 0    | External Device Read Strobe. When in the Single-Chip-Select (SINGLECS) mode and RSEL1 bit is set, this signal follows the RD signal issued by the main processor in the second cycle of an external device access. Data can be read from the external device to the main processor data bus (D0-D7). When not in the SINGLECS mode, this pin remains high.                                                                                                                                                                                                                                                                                                           |

| MINT | #  |      | External Device Interrupt. When in the Single-Chip-Select (SINGLECS) mode, a low level on this pin generates an interrupt to the main processor on the INTR pin if enabled by the software. When not in the SINGLECS mode, this pin is ignored.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RTS  | *# | 0    | Request To Send. This signal shows that a DCE (modem) is ready to send the data. It is controlled by the RTS bit (bit 1 of 16550A MCR or bit 1, Port-A WR8). Setting the RTS bit results in a low level on this pin. Clearing the RTS bit would result in this pin going high immediately when the Auto Enable feature is not active. When the Auto Enable feature is active (bit 5, WR3 set), this pin goes high only after RTS bit is cleared and transmitter register is empty.                                                                                                                                                                                   |

# PIN DESCRIPTION (Continued)

Channel A and Channel B in Single-Processor Configuration: (Continued)

Pins marked by \* are available in 28-pin version (73M1650).

Pins marked by # have a different function in the Dual-Processor configuration.

| NAME  |    | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTS   | *# |      | Clear To Send. This signal is used in DCE (modem) handshaking to show that the DCE has established the communication and data may be transferred to DCE. This input is Schmitt triggered and inverted and its status is reflected in the CTS bit (bit 4 of 16550A MSR and bit 5, Channel A RR0). If the Auto Enable feature is active (bit 5, WR3 set), data is automatically transmitted when this pin is low. If the Auto Enable is not selected this pin can be used as a general purpose input. The DCTS bit (bit 0 of 16550A MSR) is set when a change in the CTS logic level is detected, and it can generate an interrupt. |

| DTR   | *# | 0    | Data Terminal Ready. This signal is used in DCE (modem) handshaking to signify that the SPC is ready to communicate. This pin is a complement of DTR bit (bit 0 of 16550A MCR and bit 7, Channel A WR5). This pin can be used as a general purpose output pin.                                                                                                                                                                                                                                                                                                                                                                    |

| DSR   | #  | 1    | Data Set Ready. This signal is used in the DCE (modem) handshaking to indicate that the DCE is ready to communicate. This input is Schmitt triggered and inverted and its status is reflected in the DSR bit (bit 5 of 16550AMSR or bit 5, of Channel ARR10). This pin can be used as a general purpose input pin. Bit DDSR (bit 1 of 16550AMSR) is set when a change in DSR logic level is detected, and it can generate an interrupt.                                                                                                                                                                                           |

| DCD   |    | -    | Data Carrier Detect. A DCE (modem) status input indicates that the DCE has detected the carrier signal on the medium (telephone line). This input is Schmitt triggered and inverted and its status is reflected in the DCD bit (bit 7 of 16550A MSR and bit 3, Channel A RR0). If the Auto Enable feature is active (bit 5, Channel A WR3 set), a low level on DCD automatically activates the receiver circuity. When the Auto Enable is not selected this pin can be used as a general purpose input pin. Bit DDCD (bit 3 of 16550A MSR) is set when a change in DCD level is detected, and it can generate an interrupt.       |

| RI    | *# | -    | Ring Indicator. A DCE (modem) status input indicating the presence of ringing voltage on the telephone line. This input is Schmitt triggered and inverted and its status is reflected in the RI bit (bit 6 of 16550A MSR and bit 0, Channel A RR10). This input can be used as a general purpose input pin. The TERI bit (bit 2 of 16550A MSR) is set when a high-to-low transition is detected on this pin, and it can generate an interrupt to the main processor.                                                                                                                                                              |

| TXACT | #  | 0    | Transmitter Active. When low, this pin indicates the transmitter is currently transmitting active data. This pin is asserted just before the transmitter becomes active and is negated when the transmitter becomes active and is negated when the transmitter idles. This pin may be utilized to externally gate the transmit pin onto a transmit buss shared by multiple ICs.                                                                                                                                                                                                                                                   |

|                                                    |          |               |                                      |                       |                                      | DATA BIT NUM                         | IBER                      |                                  |                               |                               |

|----------------------------------------------------|----------|---------------|--------------------------------------|-----------------------|--------------------------------------|--------------------------------------|---------------------------|----------------------------------|-------------------------------|-------------------------------|

| REGISTI                                            | REGISTER |               | D7                                   | D6                    | D5                                   | D4                                   | D3                        | D2                               | D1                            | DO                            |

| Receiver<br>Buffer<br>Register<br>(Read<br>only)   | RBR      | 0<br>DLAB = 0 | Bit 7<br>(MSB)                       | Bit 6                 | Bit 5                                | Bit 4                                | Bit 3                     | Bit 2                            | Bit 1                         | Bit 0<br>(LSB)                |

| Transmit<br>Holding<br>Register<br>(Write<br>only) | THR      | 0<br>DLAB = 0 | Bit 7<br>(MSB)                       | Bit 6                 | Bit 5                                | Bit 4                                | Bit 3                     | Bit 2                            | Bit 1                         | Bit 0<br>(LSB)                |

| interrupt<br>Enable<br>Register                    | IER      | 1<br>DLAB = 0 | REGSEL1<br>(SINGLECS)                | REGSELO<br>(SINGLECS) | SSi<br>Enable<br>(SINGLECS)          | 0                                    | Enable<br>Modem<br>Status | Enable<br>Receiver<br>Status     | Enable<br>THRE                | Enable<br>RDA                 |

| interrupt<br>ID<br>Register<br>(Read<br>only)      | liR      | 2             | FIFOs<br>Enabled                     | FIFOs<br>Enabled      | RxRDY<br>(SSI Enable)                | TxRDY Interrupt<br>(SSi Enable) ID 2 |                           | Interrupt<br>ID 1                | Interrupt<br>ID 0             | Interrupt<br>Pending          |

| FIFO<br>Control<br>Register<br>(Write<br>only)     | FCR      | 2             | RCVR<br>Trigger<br>1                 | RCVR<br>Trigger<br>0  | XMIT<br>Trigger<br>1<br>(SSi Enable) | XMIT<br>Trigger<br>0<br>(SSi Enable) | DMA<br>Mode<br>Select     | XMIT<br>FIFO<br>Reset            | RCVR<br>FIFO<br>Reset         | FIFO<br>Enable                |

| Line<br>Control<br>Register                        | LCR      | 3             | Divisor<br>Latch<br>Access<br>(DLAB) | Set<br>Break          | Stick<br>Parity                      | Even<br>Parity                       | Parity<br>Enable          | Number<br>Stop                   | Word<br>Length<br>Select<br>1 | Word<br>Length<br>Select<br>0 |

| Modem<br>Control<br>Register                       | MCR      | 4<br>REGSEL≖0 | 0                                    | o                     | 0 0 Loop Enable Interrupt            |                                      |                           | μPRST                            | RTS                           | DTR                           |

| Line<br>Status<br>Register                         | LSR      | 5<br>REGSEL=0 | Error in<br>Receive<br>FIFO          | Transmit<br>Empty     | Transmit<br>Holding<br>Empty         | Break<br>Interrupt<br>(BI)           | Framing<br>Error<br>(FE)  | Parity<br>Error<br>(PE)          | Overrrun<br>Error<br>(OE)     | Data<br>Ready<br>(DR)         |

| Modem<br>Status<br>Register                        | MSR      | 6<br>REGSEL=0 | DCD                                  | RI                    | DSR                                  | стѕ                                  | Delta<br>DCD<br>(DDCD)    | Trailing<br>Edge<br>RI<br>(TERI) | Delta<br>DSR<br>(DDSR)        | Delta<br>CTS<br>(DCTS)        |

| Scratch<br>Register                                | SCR      | 7<br>REGSEL≖0 | Bit 7                                | Bit 6                 | Bit 5                                | Bit 4                                | Bit 3                     | Bit 2                            | Bit 1                         | Bit 0                         |

| Divisor<br>Latch<br>(LS)                           | DLL      | 0<br>DLAB = 1 | Bit 7                                | Bit 6                 | Bit 5                                | Bit 4                                | Bit 3                     | Bit 2                            | Bit 1                         | Bit O                         |

| Divisor<br>Latch<br>(MS)                           | DLM      | 1<br>DLAB = 1 | Bit 15                               | Bit 14                | Bit 13                               | Bit 12                               | Bit 11                    | Bit 10                           | Bit 9                         | Bit 8                         |

**TABLE 1: Main Port 16550A UART Registers**

|                                                 |          |                                                       |                                            |              | <u></u>                                     | DATA                                | A BIT NUMBER                     |                                    |                                                 | -                                               |

|-------------------------------------------------|----------|-------------------------------------------------------|--------------------------------------------|--------------|---------------------------------------------|-------------------------------------|----------------------------------|------------------------------------|-------------------------------------------------|-------------------------------------------------|

| REGISTE                                         | REGISTER |                                                       | D7                                         | D6           | D5                                          | D4                                  | D3                               | D2                                 | D1                                              | DO                                              |

| UART<br>Command<br>Register<br>(Write only)     | UCR      | D/C=0<br>A/B=0<br>ONECS =1:<br>D/C=0 A3=1<br>RGSEL0=1 | 0                                          | 0            | 0                                           | 0                                   | Register<br>Select<br>3          | Register<br>Select<br>2            | Register<br>Select<br>1                         | Register<br>Select<br>0                         |

| Receiver<br>Buffer<br>Register<br>(Read only)   | RBR      | 8<br>or<br>D/C=1<br>A/B=0                             | Bit 7<br>(MSB)                             | Bit 6        | Bit 5                                       | Bit 4                               | Bit 3                            | Bit 2                              | Bit 1                                           | Bit 0<br>(LSB)                                  |

| Transmit<br>Holding<br>Register<br>(Write only) | THR      | 8<br>or<br>D/C=1<br>A/B=0                             | Bit 7<br>(MSB)                             | Bit 6        | Bit 5                                       | Bit 4                               | Bit 3                            | Bit 2                              | Bit 1                                           | Bit 0<br>(LSB)                                  |

| Interrupt<br>Enable<br>Register                 | IER      | 1                                                     | 0                                          | 0            | 0                                           | Enable<br>External<br>INT<br>(SP=1) | Enable<br>MCRVSCR<br>Status      | Enable<br>Divisor<br>LCR<br>Status | Enable<br>THRE                                  | Enable<br>RDA/OE                                |

| interrupt<br>ID<br>Register<br>(Read only)      | HR       | 2                                                     | 0                                          | 0            | o                                           | 0                                   | 0                                | Interrupt<br>ID 2                  | Interrupt<br>ID 1                               | Interrupt<br>ID 0                               |

| Line<br>Control<br>Register<br>(Read only)      | LCR      | 3                                                     | 0                                          | Set<br>Break | Stick<br>Parity                             | Even<br>Parity                      | Parity<br>Enable                 | Number<br>Stop                     | Word<br>Length<br>Select<br>1                   | Word<br>Length<br>Select<br>0                   |

| Modern<br>Control<br>Register<br>(Reed only)    | MCR      | 4                                                     | Delta<br>MCR                               | 0            | 0                                           | Loop                                | 0                                | 0                                  | RTS                                             | DTR                                             |

| Line<br>Status<br>Register                      | LSR      | 5                                                     | 0                                          | 0            | Transmit<br>Holding<br>Ready<br>(Read only) | Channel B<br>Tx Transmit<br>Break   | Channel B<br>Tx Framing<br>Error | Channel 8<br>Tx Parity<br>Error    | Channel B<br>Rx Overrun<br>Error<br>(Read only) | Channel B<br>Rx Data<br>Ready<br>(Read<br>only) |

| Modern<br>Status<br>Register<br>(Read/Write)    | MSR      | 6                                                     | DCD                                        | RI           | DSR                                         | стѕ                                 | 0                                | 0                                  | 0                                               | 0                                               |

| Scratch<br>Register                             | SCR      | 7                                                     | Bit 7                                      | Bit 6        | Bit 5                                       | Bit 4                               | Bit 3                            | Bit 2                              | Bit 1                                           | Bit 0                                           |

| Divisor<br>Latch<br>(LS)<br>(Read only)         | DLL      | 9                                                     | Bit 7                                      | Bit 6        | Bit 5                                       | Bit 4                               | Bat 3                            | Bit 2                              | Bit 1                                           | Bit O                                           |

| Divisor<br>Latch<br>(MS)<br>(Read only)         | DLM      | 10                                                    | Bit 15                                     | Bit 14       | Bit 13                                      | Bit 12                              | Bit 11                           | Bit 10                             | Bit 9                                           | Bit 8                                           |

| Configure<br>Control<br>Register                | CCR      | 11                                                    | 16550<br>A<br>Paraliel<br>Enable<br>(SP=1) | 0            | 0                                           | OSC<br>OFF                          | Divisor<br>Prescale<br>3         | Divisor<br>Prescale<br>2           | Divisor<br>Prescale<br>1                        | Divisor<br>Prescale<br>0                        |

**TABLE 2: Channel B Registers**

|                                             |                  |                                  | DATA BIT NUMBER                  |                                 |                                 |                                   |                                        |                                     |                                 |                               |  |  |

|---------------------------------------------|------------------|----------------------------------|----------------------------------|---------------------------------|---------------------------------|-----------------------------------|----------------------------------------|-------------------------------------|---------------------------------|-------------------------------|--|--|

| REGISTER                                    |                  | ADDRESS<br>WR0 (3:0)             | D7                               | D6                              | D6                              | D4                                | D3                                     | D2                                  | D1                              | Do                            |  |  |

| Comman<br>d<br>Register                     | WRO              | 0                                | CRC<br>Reset<br>1                | CRC<br>Reset                    | Command<br>Code<br>2            | Command<br>Code<br>1              | Command<br>Code<br>0                   | Register<br>Select<br>2             | Register<br>Select<br>1         | Register<br>Select<br>0       |  |  |

| Tx/Rx<br>Interrupt<br>Data<br>Transfer      | WR1              | 1<br>(WR only)                   | 0                                | 0                               | 0                               | Receive<br>Interrupt<br>Mode<br>1 | Receive<br>Interrupt<br>Mode<br>0      | Parity<br>Special                   | Tx Int<br>Enable                | Externa<br>Interrup<br>Enable |  |  |

| Interrupt<br>Vector<br>Register             | WR2              | 2<br>(RD/WR)                     | Bit 7<br>(MSB)                   | Bit 6                           | Bit 5                           | Bit 4                             | Bit 3                                  | Bit 2                               | Bit 1                           | Bit 0<br>(LSB)                |  |  |

| Receive<br>Control                          | WR3              | 3<br>(WR only)                   | Rx Bits<br>/Char 1               | Rx Bits<br>/Char 0              | Auto<br>Enable                  | Enter<br>Hunt<br>Mode             | Rx CRC<br>Enable                       | Address<br>Search<br>Mode<br>(SDLC) | SYNC<br>Char<br>Load<br>Inhibit | Receive<br>Enable             |  |  |

| Tx/Rx<br>Misc.<br>Modes                     | WR4<br>RR4       | 4<br>(RD/WR)                     | Clock<br>Rate<br>1               | Clock<br>Rate<br>0              | SYNC<br>Mode<br>1               | SYNC<br>Mode<br>0                 | Stop<br>Bits<br>1                      | Stop<br>Bits<br>0                   | Even<br>Parity                  | Parity<br>Enable              |  |  |

| Transmit<br>Control                         | WR5<br>RR5       | 5<br>(RD/WR)                     | DTR                              | Tx Bits<br>/Char 1              | Tx Bits<br>/Char 0              | Send<br>Break                     | Transmit<br>Enable                     | SDLC/<br>CRC-16                     | RTS                             | Tx CRK<br>Enable              |  |  |

| SYNC<br>Char or<br>SDLC<br>Address          | WR6<br>RR6       | 6<br>(RD/WR)                     | Bit 7                            | Bit 6                           | Bit 5                           | Bit 4                             | Bit 3                                  | Bit 2                               | Bit 1                           | Bit 0                         |  |  |

| SYNC<br>Char or<br>SDLC<br>Flag             | WR7<br>RR7       | 7<br>(RD/WR)                     | Bit 7                            | Bit 6                           | Bit 5                           | Bit 4                             | Bit 3                                  | Bit 2                               | Brit 1                          | Bit 0                         |  |  |

| Transmit<br>Buffer<br>Register              | WRB              | 8<br>D/C=1<br>A/B=1<br>(WR only) | Bit 7                            | Bit 6                           | Bit 5                           | Bit 4                             | Bit 3                                  | Bit 2                               | 9at 1                           | Bit O                         |  |  |

| Mester<br>Interrupt<br>Control              | WR9<br>RR9       | 9<br>(RD/WR)                     | Reset<br>Command<br>1            | Reset<br>Command<br>0           | 0                               | Status<br>High                    | Master<br>Interrupt<br>Enable<br>(MIE) | 0                                   | 0                               | Vector<br>Include<br>Status   |  |  |

| Tx/Rx<br>Misc.<br>Control                   | WR1<br>0         | 10<br>(WR only)                  | CRC<br>Preset                    | Data<br>Encoding<br>1           | Data<br>Encoding<br>0           | Go<br>Active<br>on Poll           | Mark<br>idle                           | Abort<br>on<br>Underrun             | Loop                            | 6 Bit<br>Sync                 |  |  |

| Clock<br>Mode<br>Control                    | WR1<br>1<br>RR11 | 11<br>(RD/WR)                    | Manchester<br>Encode<br>Transmit | Receive<br>Clock<br>Source<br>1 | Receive<br>Clock<br>Source<br>1 | Transmit<br>Clock<br>Source<br>1  | Transmit<br>Clock<br>Source<br>0       | TRxC<br>Pin<br>Output               | TRxC<br>Output<br>Source<br>1   | TRxC<br>Output<br>Source<br>0 |  |  |

| Lower<br>Byte<br>Baud<br>Generator          | WR1<br>2<br>RR12 | 12<br>(RD/WR)                    | Bit 7                            | B×t6                            | Bit 5                           | Bit 4                             | Bit 3                                  | Bit 2                               | Bit 1                           | Bit 0                         |  |  |

| Upper<br>Byte<br>Baud<br>Generator          | WR1<br>3<br>RR13 | 13<br>(RD/WR)                    | Bit 15                           | Bit 14                          | Bit 13                          | Bit 12                            | Bit 11                                 | Bit 10                              | Bit 9                           | Bit 8                         |  |  |

| Misc.<br>Control                            | WR1<br>4<br>RR14 | 14<br>(RD/WR)                    | PLL<br>Command<br>2              | PLL<br>Command<br>1             | PLL<br>Command<br>0             | Local<br>Loopback                 | Auto<br>Echo                           | TX<br>CRC-32                        | Baud<br>Generator<br>Source     | Baud<br>Generat<br>Enable     |  |  |

| External<br>/Status<br>Interrupt<br>Control | WR1<br>5<br>RR15 | 15<br>(RD/WR)                    | Break/<br>Abort<br>Interrupt     | Tx<br>Underrun<br>/EOM          | CTS<br>Interrupt<br>Enable      | Syno/<br>Hunt<br>Interrupt        | DCD<br>Interrupt<br>Enable             | DSR<br>Interrupt<br>Enable          | Zero<br>Count<br>interrupt      | Ri<br>Interrup<br>Enable      |  |  |

**TABLE 3: SCC Channel A Write Registers**

|                                           |      |                      |                           |                              |                                     | DATA                                          | BIT NUMBER                             |                                |                                |                                |

|-------------------------------------------|------|----------------------|---------------------------|------------------------------|-------------------------------------|-----------------------------------------------|----------------------------------------|--------------------------------|--------------------------------|--------------------------------|

| REGIST                                    | ER   | ADDRESS<br>WR0 (3:0) | D7                        | D6                           | D5                                  | D4                                            | D3                                     | D2                             | D1                             | D0                             |

| Tx/Rx<br>Buffer/<br>External<br>Status    | RR0  | 0                    | Break/<br>Abort<br>Detect | Transmit<br>Underrun<br>/EOM | стѕ                                 | Hunt                                          | DCD                                    | Transmit<br>Buffer<br>Empty    | Zero<br>Count                  | Receive<br>Char.<br>Available  |

| Special<br>Receive<br>Condition<br>Status | RR1  | 1                    | End of<br>Frame<br>(SDLC) | CRC/<br>Framing<br>Error     | Receive<br>Overrun<br>Error         | Parity/<br>CRC-32<br>Error                    | Bit<br>Remainder<br>2                  | Bit<br>Remainder<br>1          | Bit<br>Remainder<br>0          | All<br>Sent                    |

| interrupt<br>Vector<br>Register           | RR2  | 2                    | Bit 7<br>(MSB)            | Bit 6                        | Bit 5                               | Bit 4                                         | Bit 3                                  | Bit 2                          | Bit 1                          | Bit 0<br>(LSB)                 |

| Interrupt<br>Pending<br>Register          | RR3  | 3                    | 0                         | 0                            | Channel A Receive Interrupt Pending | Channel A<br>Transmit<br>Interrupt<br>Pending | Channel A Ext/Status Interrupt Pending | Channel B<br>Interrupt<br>ID 2 | Channel B<br>Interrupt<br>ID 1 | Channel B<br>Interrupt<br>ID 0 |

| Receive<br>Data<br>Register               | RR8  | 8                    | Bit 7                     | Bit 6                        | Bit 5                               | Bit 4                                         | Bit 3                                  | Bit 2                          | Bit 1                          | Bit 0                          |

| Misc.<br>Status                           | RR10 | 10                   | One<br>Clock<br>Missing   | Two<br>Clocks<br>Missing     | DSR                                 | Loop<br>Sending                               | CRC16                                  | CRC32                          | On<br>Loop                     | RI                             |

**TABLE 4: SCC Channel A Read Registers**

# ADDRESS MAPPING: Single Processor Register Maps in Single-Chip-Select Mode

| REGSEL1 | REGSEL0 | A2 | A1     | A0   | A/B | D/C | Addressed Register      |

|---------|---------|----|--------|------|-----|-----|-------------------------|

| 0       | 0       | 0  | 00 - 1 | 11   | Х   | Х   | 550 Registers as normal |

| 0       | 1       | 0  | 00     | - 11 | Х   | Х   | 550 Registers as normal |

| 0       | 1       | 1  | Х      | Х    | 0   | 0   | Channel B Control       |

| 0       | 1       | 1  | X      | Χ    | 0   | 1   | Channel B Data          |

| 0       | 1       | 1  | X      | X    | 1   | 0   | Channel A Control       |

| 0       | 1       | 1  | X      | X    | 1   | 1   | Channel A Data          |

| 1       | 1       | Х  | Х      | Х    | Х   | X   | External Device         |

FIGURE 8: 40 and 44 Pin Versions

| REGSEL1 | REGSEL0 | A2 | <b>A</b> 1 | A0   | A/B | D/C | Addressed Register      |

|---------|---------|----|------------|------|-----|-----|-------------------------|

| 0       | 0       | 0  | 00 - 1     | 11   | -   | -   | 550 Registers as normal |

| 0       | 1       | 0  | 00         | - 11 |     | -   | 550 Registers as normal |

| 00      | 1       | 1  | 0          | 0    | -   | -   | Channel A Data          |

| 0       | 1       | 1  | 0          | 1    | -   | -   | Channel A Control       |

| 0       | 1       | 1  | 1          | 0    | -   | -   | Channel B Data          |

| 0       | 1       | 1  | 1          | 1    | -   | -   | Channel B Control       |

FIGURE 9: 28 Pin Version (73M1650)

**FIGURE 4: Typical Clock Circuits**

### TYPICAL CRYSTAL OSCILLATOR NETWORK

| CRYSTAL | RP   | RX2  | <b>C</b> 1 | C2       |

|---------|------|------|------------|----------|

| 1.8 MHz | 1 ΜΩ | 1.5K | 10-30 pF   | 40-60 pF |

| 20 MHz  | 1 ΜΩ | 0    | 10-30 pF   | 10-30 pF |

### **ELECTRICAL SPECIFICATIONS**

### **ABSOLUTE MAXIMUM RATINGS**

(TA = -40°C to +85°C, VCC = 5V  $\pm$  10%, unless otherwise noted. Operation above absolute maximum ratings may permanently damage the device.)

| PARAMETER           | CONDITIONS         | RATING            |

|---------------------|--------------------|-------------------|

| VCC Supply Voltage  |                    | +7V               |

| Storage Temperature |                    | -65°C to 150°C    |

| Lead Temperature    | Soldering, 10 sec. | 260°C             |

| Applied Voltage     |                    | -0.3 to Vcc + 0.3 |

### **DC CHARACTERISTICS**

(TA = -40°C to +85°C, VCC = 5V  $\pm$ 10%, unless otherwise noted.)

| PARAM | METER                          | CONDITION                                | MIN  | NOM         | MAX    | UNITS |

|-------|--------------------------------|------------------------------------------|------|-------------|--------|-------|

| VILX  | Clock Input Low Voltage        |                                          | -0.3 |             | 0.8    | ٧     |

| VIHX  | Clock Input High Voltage       |                                          | 2.0  |             | vcc    | V     |

| VIL   | Input Low Voltage              |                                          | -0.3 |             | 0.8    | V     |

| VIH   | Input High Voltage             |                                          | 2.0  |             | VCC+.3 | V     |

| VOL   | Output Low Voltage             | IOL = -5 mA<br>(except XOUT,<br>MD0-MD7) |      |             | 0.4    | ٧     |

| VOL   | Output Low Voltage,<br>MD0-MD7 | IOL = -3 mA                              |      |             | 0.4    | ٧     |

| VOH   | Output High Voltage            | IOH = 5 mA<br>(except XOUT & MINT)       | 2.4  |             |        | V     |

| IOH   | Output High Current            | MINT = 2.5V                              | 20   |             | 250    | μА    |

| ICC1  | Supply Current                 | See Note 1                               |      | 2           | 10     | mA    |

| ICC2  | Power Down Current             | See Note 2                               |      |             | 50     | μА    |

| IIL   | Input Leakage                  |                                          |      | <del></del> | ±10    | μА    |

| IOZ   | High-Impedance Leakage         |                                          |      |             | ±20    | μA    |

Note 1: Outputs unloaded, CMOS level inputs, Xtal = Data Rate = 10 MHz.

Note 2: Outputs unloaded, CMOS level input, Oscillator disabled or XIN = VCC.

### **AC CHARACTERISTICS**

(TA = -40°C to +85°C, VCC = 5V  $\pm$ 10%, unless otherwise noted.)

| PARAME | TER                                                     | MIN | NOM | MAX | UNITS  |

|--------|---------------------------------------------------------|-----|-----|-----|--------|

| tCD    | TRXC (Transmit Clock) or RTXC (Receive Clock) to TXdata |     | 75  | 150 | ns     |

| fOSC   | Baud Rate Crystal/External Clock                        | 0   |     | 20  | MHz    |

| fBG    | Baud Rate Generator                                     |     |     | 15  | MHz    |

| fDPLL  | Input Frequency Digital Phase Lock Loop DPLL            | 0   |     | 20  | MHz    |

| fDATA  | Serial Data Rate                                        | 0   |     | 6   | MBit/s |

| fDLOOP | Serial Data Rate SDLC Loop Mode Bit/s                   | 0   |     | 4   | Mbit/s |

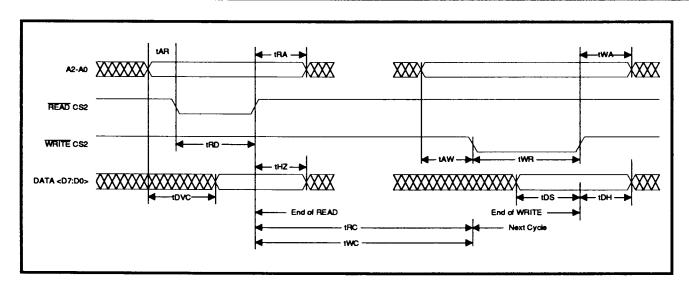

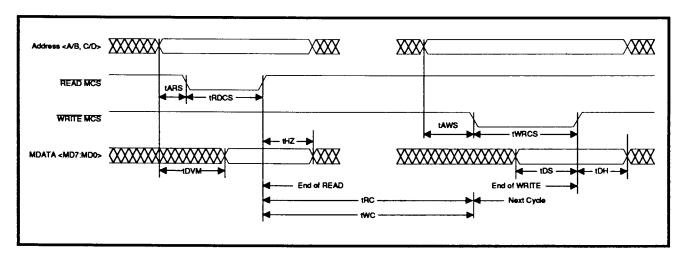

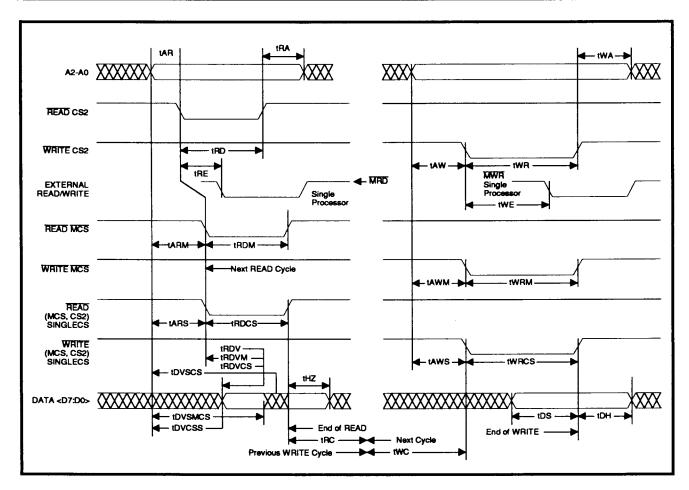

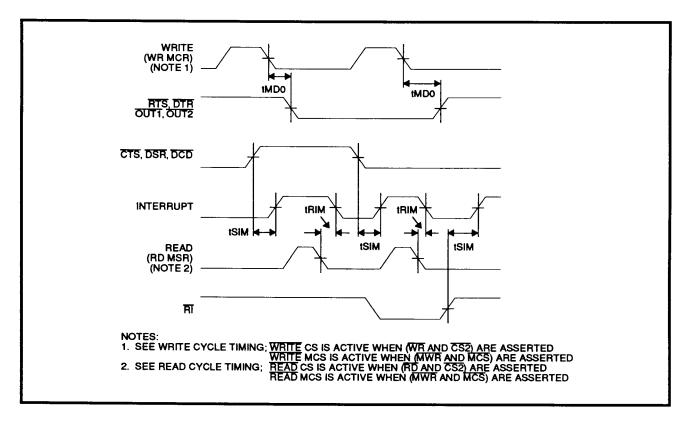

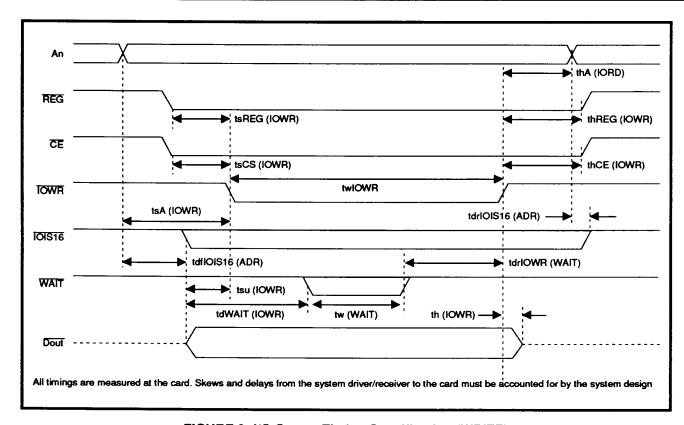

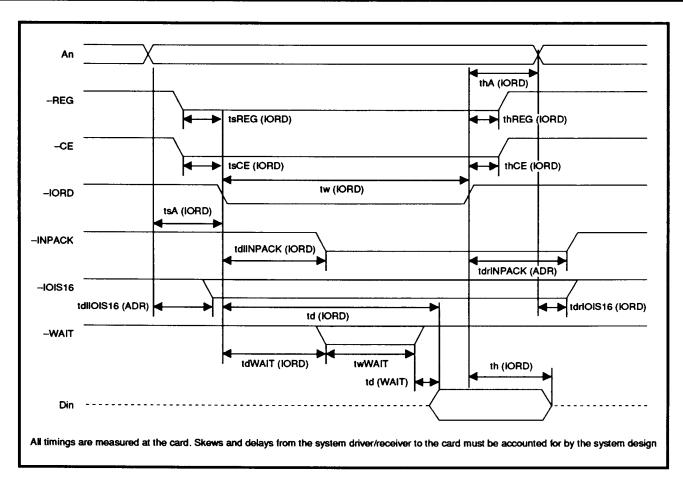

# READ AND WRITE CYCLE - DUAL PROCESSOR (Refer to Figures 5 & 6)

| PARAM | ETER                                                                                       | MIN | NOM | MAX | UNITS |

|-------|--------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| tAR   | Address Setup before READ (CS2)                                                            | 15  | 0   |     | ns    |

| tARM  | Address Setup before READ (MCS)                                                            | 15  | 0   |     | ns    |

| tAW   | Address Setup before WRITE (CS2)                                                           | 15  | 0   |     | ns    |

| tAWM  | Address Setup before WRITE (MCS)                                                           | 15  | 0   |     | ns    |

| tRA   | Address Hold after READ with CS2                                                           | 10  | 0   |     | ns    |

| tWA   | Address Hold after WRITE with CS2                                                          | 10  | 0   |     | ns    |

| tRAS  | Address Hold after READ with MCS                                                           | 20  | 10  |     | ns    |

| tWAS  | Address Hold after WRITE with MCS                                                          | 20  | 10  |     | ns    |

| tRD   | READ Minimum Width Asserted with CS2                                                       | 60  | 25  |     | ns    |

| tWR   | WRITE Minimum Width Asserted with CS2                                                      | 60  | 25  |     | ns    |

| tRDM  | READ Minimum Width Asserted with MCS                                                       | 80  | 25  |     | ns    |

| tWRM  | WRITE Minimum Width Asserted with MCS                                                      | 80  | 25  |     | ns    |

| tRDV  | READ to Data Output Asserted with CS2                                                      |     | 25  | 60  | ns    |

| tRDVM | READ to Data Output Asserted with MCS                                                      |     | 25  | 80  | ns    |

| tDS   | DATA Setup before end of WRITE                                                             | 30  | 5   |     | ns    |

| tDH   | DATA Hold Time after WRITE                                                                 | 30  | 5   |     | ns    |

| tHZ   | DATA to High Impedance after READ                                                          |     | 15  | 30  | ns    |

| tDVC  | Address to Data Available Dual Processor using CS2                                         |     | 60  | 100 | ns    |

| tDVM  | Address to Data Available Dual Processor using MCS                                         |     | 90  | 140 | ns    |

| tRC   | Channels A & B Register Bank, End of READ Cycle to a subsequent to New Command Cycle       | 200 | 100 |     | ns    |

| tWC   | Channels A & B Register Bank, End of WRITE Cycle Command to a subsequent New Command Cycle | 200 | 100 |     | ns    |