NO. 85-03 3

# YM3015

# 2-Channel Serial & Binary input Floating D/A Converter(DAC-GS)

#### **OUTLINE**

The YM 3015: DAC-GS is a floating D/A converter (referred to as DAC hereafter) with the 2-channel serial and 16-bit binary input or 2's complement input. It can produce analog output (16-bit dynamic range) which has 10-bit mantissa and 7-step exponent characteristic for the input digital signal.

#### **■ FEATURES**

- 16-bit input format can select either binary or 2's complement (equipped with a built-in floating converter logic).

- Externally equipped with buffer operational amplifier it allows easy analog output.

- 16-bit wide dynamic range.

- Capable of processing PCM sound source up to 2 channels.

- Equipped with a built-in analog switch for sample hold.

- Lower noise and less harmonic distortion and outstanding temperature characteristics.

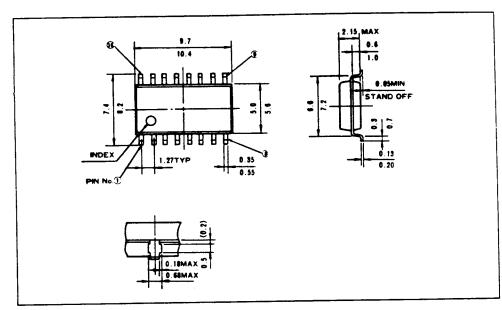

- Made by the monolithic process of highly accurate thin film resistor and CMOS and enclosed in the 16-pin plastic flat package.

NIPPON GAKKI CO., LTD.

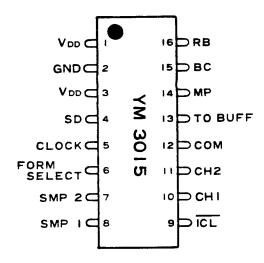

## Pin assignment

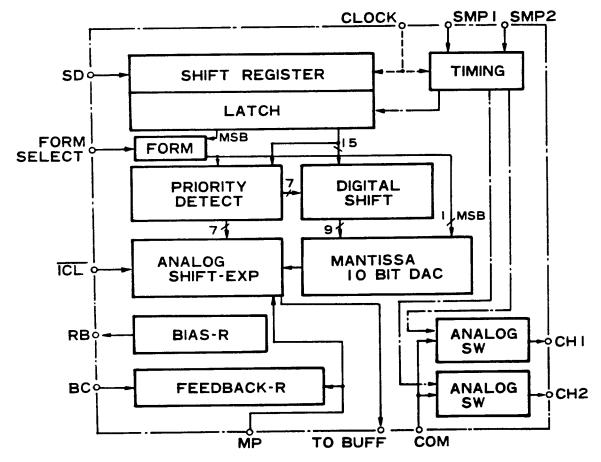

# Block diagram

# Pin function

| Pin No. | Signature      | Description                                                                                                                                                                                                                                                                                                                    |

|---------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VDD            | High electric potential side standard power source                                                                                                                                                                                                                                                                             |

| 2       | Vss            | Low electric potential side power source (GND)                                                                                                                                                                                                                                                                                 |

| 3       | VDD            | High electric potential side standard power source                                                                                                                                                                                                                                                                             |

| 4       | SD             | Serial input of digital signal to be converted                                                                                                                                                                                                                                                                                 |

| 5       | CLOCK          | Clock to operate shift register and timing generator (Ø4)                                                                                                                                                                                                                                                                      |

| 6       | FORM<br>SELECT | Capable of processing binary input format at "1" and 2's complement input format at "0"                                                                                                                                                                                                                                        |

| 7       | SMP2           | Interval "1" becomes sampling time for CH2.                                                                                                                                                                                                                                                                                    |

| 8       | SMP1           | Interval "1" becomes sampling time for CH1.  The internal signal for latching serial data is produced by using SMP 1 and SMP 2 fall.                                                                                                                                                                                           |

| 9       | ĪCL            | "1" - normal operation, "0" - output under - 36dB regardless of the signal SD.                                                                                                                                                                                                                                                 |

| 10      | Vout<br>CH1    | Sample hold analog switch output for CH1.                                                                                                                                                                                                                                                                                      |

| 11      | VOUT<br>CH2    | Sample hold analog switch output for CH2.                                                                                                                                                                                                                                                                                      |

| 12      | COM            | Common input to analog switches for CH1 and CH2.                                                                                                                                                                                                                                                                               |

| 13      | To BUFF        | DAC analog output, input to the buffer operational amplifier.                                                                                                                                                                                                                                                                  |

| 14      | MP             | Exponential analog shift is carried out with the electric potential applied to the MP as a standard.  Normally it is biased to the 1/2 VDD.                                                                                                                                                                                    |

| 15      | ВС             | Included between this terminal and 14 pin is a resistor which cancels an error caused by the input bias current of the buffer operational amplifier. It is recommended to add phase compensation capacity Cc externally. As shown in the standard circuit example, it can be used with or without being connected with 14 pin. |

| 16      | Rв             | Internally generated highly accurate 1/2 VDD voltage comes out through this pin and it is applied to 14 pin by way of the buffer operational amplifier.                                                                                                                                                                        |

# Description of Operation

#### 1. Operation

The serial digital input data is synchronized with the clock fall and taken into the shift register through the SD pin. The latch signal is produced in the timing circuit by making use of the fall of SMP1 and SMP2 and it latches I15~I0 serial data.

After being latched, the 16-bit binary or 2's complement input data or I<sub>15</sub> to I<sub>0</sub> are logic converted into the data for the floating DAC by means of the priority detecting circuit and digital shift circuit. Then they become 10-bit mantissa DAC data and 7-step exponential characteristic DAC (analog shift) data and determine the DA conversion output value.

The data conversion truth table is given below.

|      | Analog shift |      |      |      |      |                |                |  |  |

|------|--------------|------|------|------|------|----------------|----------------|--|--|

| N    | 0            | 1    | 2    | 3    | 4    | 5              | 6              |  |  |

| ر1ء  | So           | Sı   | S₂   | S₃   | S،   | S <sub>5</sub> | S <sub>6</sub> |  |  |

| I 14 | Ī 15         | I 15 | I 15 | I 15 | I 15 | I 15           | I 15           |  |  |

| I 13 | _            | Ī 15 | Ì 15 | Ī 15 | Ī 15 | I 15           | Ī 15           |  |  |

| I 12 | _            | _    | Ī 15 | I 15 | I 15 | I 15           | I 15           |  |  |

| 1 ,, | _            | -    | _    | T 15 | I 15 | I 15           | I 15           |  |  |

| I 10 | -            | -    | _    |      | Ī 15 | I 15           | I 15           |  |  |

| 1 9  | _            | -    | -    | _    | -    | I 1!           | l 15           |  |  |

| 7                    |                |                | A               | nal            | og i            | shif           | t              |                 |

|----------------------|----------------|----------------|-----------------|----------------|-----------------|----------------|----------------|-----------------|

|                      | راياً          | So             | Sı              | S₂             | S <sub>3</sub>  | S٠             | S <sub>5</sub> | S <sub>6</sub>  |

|                      | D <sub>9</sub> | Ī15            | Ī15             | Ī15            | Ī <sub>15</sub> | Ī15            | Ī15            | Ī <sub>15</sub> |

| İ                    | $D_8$          | I 14           | I 13            | I 12           | I11             | I 10           | I,             | I <sub>8</sub>  |

| <b>65</b>            | D <sub>7</sub> | I 13           | I <sub>12</sub> | I11            | I 10            | I,             | Is             | I 7             |

| data                 | $D_6$          | I 12           | I11             | I 10           | l,              | Is             | 17             | I <sub>6</sub>  |

| 3-bit                | D <sub>5</sub> | I11            | I10             | l,             | I <sub>8</sub>  | 17             | I <sub>6</sub> | I <sub>5</sub>  |

| Mantissa 10-bit data | D <sub>4</sub> | I10            | I,              | I <sub>8</sub> | 17              | 16             | I <sub>5</sub> | I.              |

| ntis                 | $D_3$          | I,             | I.              | 1,             | I6              | I <sub>5</sub> | I.             | I <sub>3</sub>  |

| ×                    | $D_2$          | l <sub>e</sub> | 17              | I <sub>6</sub> | Is              | 14             | 13             | I2              |

|                      | D <sub>1</sub> | I,             | I <sub>6</sub>  | Is             | I.              | l <sub>3</sub> | l2             | I <sub>1</sub>  |

|                      | Do             | I <sub>6</sub> | 15              | I.             | I3              | I2             | I,             | Io              |

This is the case of 2's complement input. With binary input, positive and negative of I15 are reversed.

The DA converted analog output voltage is, for example with the standard circuit, as follows.

$$V_{OUT} = \frac{1}{2} V_{DD} + \frac{1}{4} V_{DD} (-1 + D_9 + D_8 2^{-1} + \dots + D_0 2^{-9} + 2^{-10}) 2^{-N}$$

It has  $1/2~\mathrm{VDD}$  maximum amplitude and  $1/2~\mathrm{VDD}$  ·  $2^{-16}$  minimum amplitude with the 1/2 VDD electric potential as the center.

The analog output comes out to the To BUFF pin. When this is input through an appropriate buffer operational amplifier and resistor into the COM pin, it is output to the CH1 and CH2 pins in the interval "1" of the SMP1 and SMP2, and the analog output of each channel is retained to the proper electrostatic capacity in the interval "0".

#### 2. Tips on Operation

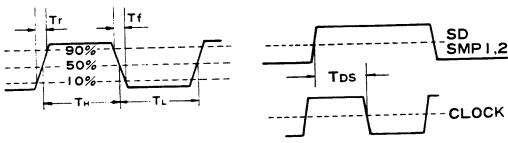

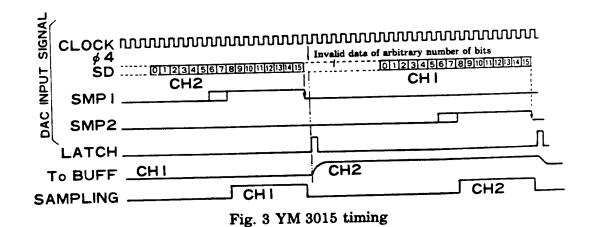

- As shown in the timing diagram Fig. 3, be sure to synchronize the fall of SMP1 and SMP2 with the rear end timing of the MSB (I15) signal.

- The sampling time of the SMP1 and SMP2 can be set to other than 8-bit time which is shown in Fig. 3.

- When using the CH1 only, be sure to synchronize the rear end timing of the MSB (I15) signal and the SMP1 fall timing, for example, by setting the SMP2 to VSS.

- When executing the conversion cycle at a different bit time, an adjustment can be made by increasing or decreasing the number of invalid bits.

#### 3. Initial Clear Function

Setting the  $\overline{ICL}$  to "0", the mantissa of the output coming out to both channels remains the same and its exponent characteristic is decreased to  $2^{-6}$  regardless of digital input data value.

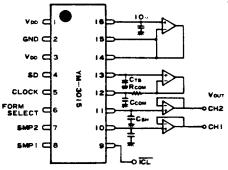

## Standard circuit example

NJM4560 equivalent

OFFSET Within ± 2.0mV

External constant example Example hold capacity

Example hold capacity

Common resistor

Recommended [2700PF]

33Ω

CSH 3300PF ~ 2200PF

RCOM 0~180

The optimum value varies slightly with the usage conditions of  $V_{\rm DD}$  and others.

For the VDD power source, it is desirable to use the one equivalent to the commercially available 3-pin regulator in the output impedance and stability.

\*CTB68PF, added, good noise resistance

# Electrical characteristics

# ① Absolute maximum ratings

| Item                          | Rating         | Unit |

|-------------------------------|----------------|------|

| Supply voltage                | -0.3 - +15.0   | V    |

| High-level input voltage      | $V_{DD} + 0.3$ | v    |

| Low-level input voltage       | Vss - 0.3      | V    |

| Operating ambient temperature | 0~70           | °C   |

| Storing temperature           | -50~+125       | °C   |

# 2 Recommended conditions

| Item                          | Signature              | Min      | Nom  | Max       | Unit   |

|-------------------------------|------------------------|----------|------|-----------|--------|

| Supply voltage                | V <sub>DD</sub><br>Vss | 9.0<br>0 | 12.0 | 12.0<br>0 | v<br>v |

| Input signal voltage          | CLOCK<br>SD<br>SMP1, 2 | 0        | -    | VDD       | v      |

| Operating ambient temperature | ICL<br>Ta              | o        |      | 70        | °C     |

#### 3 DC characteristics

| Item                     | Signature | Measuring<br>Conditions        | Min     | Nom     | Max  | Unit                                |

|--------------------------|-----------|--------------------------------|---------|---------|------|-------------------------------------|

| High-level input voltage | VIH       | V <sub>DD</sub> ≥ 9.0V         | 1/3 VDD | _       | _    | v                                   |

| Low-level input voltage  | VIL       | V <sub>DD</sub> ≥ 9.0V         |         | _       | 1.0  | V                                   |

| Input current            | IIN       | $V_{\rm DD} = 12.0 \mathrm{V}$ | _       | -       | 10-3 | μΑ                                  |

| Analog output voltage    | Vout      |                                |         | 0.50VDD | -    | $\mathbf{V}\mathbf{p} - \mathbf{p}$ |

| Supply current           | IDD       | $V_{\rm DD} = 12.0 \mathrm{V}$ | _       |         | 6    | mA                                  |

#### **4** AC characteristics

| Item                                                                                                                                             | Signature                         | Conditions           | Min               | Nom | Max                         | Unit               |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------|-------------------|-----|-----------------------------|--------------------|

| <ul> <li>Clock     Frequency     High-level time     Rise time     Fall time</li> <li>Data     Setup time     Rise time     Fall time</li> </ul> | fc<br>TH<br>Tr<br>Tf<br>TDS<br>Tr | SD<br>SMP 1<br>SMP 2 | 0.65<br>100<br>50 | 4.3 | 5.0<br>30<br>30<br>30<br>30 | MHz ns ns ns ns ns |

# **5** Capacity

| Item           | Signature | Conditions | Min | Nom | Max | Unit |

|----------------|-----------|------------|-----|-----|-----|------|

| Input capacity | Cin       |            |     |     | 5   | PF   |

#### **© DAC characteristics**

| Item                                                           | Signature   | Conditions                                         | Min | Nom                  | Max                 | Unit                           |

|----------------------------------------------------------------|-------------|----------------------------------------------------|-----|----------------------|---------------------|--------------------------------|

| Maximum output amplitude<br>Resolution                         | <del></del> |                                                    |     | 1/2 VDD<br>16<br>1.5 | 3.5                 | V <sub>pp</sub><br>Bit<br>µsec |

| Setting time Total harmonic distortion normal: noise contained | THD 1       | V <sub>DD</sub> = 9V, 1KHz,<br>Level 0dB           |     | 0.06<br>0.20         | 0.10                | %                              |

| Noise                                                          | THD 6       | -40dB                                              |     | -92<br>-74           | <b>0.3</b> 5<br>-80 | dBm<br>dB                      |

| Crosstalk Temperature characteristics                          |             | 1KHz, 0dB Output voltage Total harmonic distortion |     | 5                    |                     | ppm/°C                         |

Recommended constant and Midpoint buffer operational amplifier NJM 4560 (offset voltage within  $\pm 2mV$ ) used,

Any other condition such as supply voltage is specified separatedly.

## 7. Timing diagram

Fig. 1 Data timing

Fig. 2 Input data clock timing

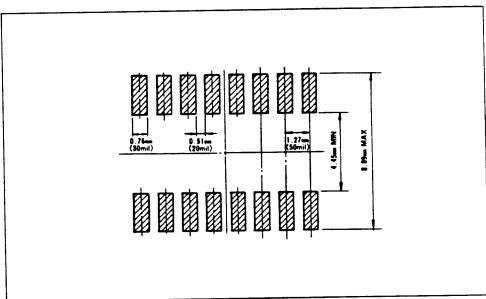

#### Dimensions

\*Specifications subject to change for improvement without notice.

| AGENCY — | Address inquiries to: Electronic System | Division                                                                                                                          |

|----------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|          | Toyooka Factory                         | 203, Matsunokijima, Toyooka-mura,<br>Iwata-gun, Shizuoka-ken, 438-01<br>Electronic Equipment business section<br>Tel. 053962-3125 |

|          | ■Tokyo Office                           | 3-4, Surugadai Kanda, Chiyoda-ku,<br>Tokyo, 104<br>Ryumeikan Bldg. 4F<br>Tel. 03-255-4481                                         |

|          | Osaka Office                            | 1-6 Shin-ashiya shita, Suita-city.<br>Osaka-fu. 565<br>Tel. 06-877-4481                                                           |