# YAMAHA'LSI

# **YTD427**

# **APPLICATION MANUAL**

**IAFE**

ISDN DSU Analog Front End

# YAMAHA

YTD427 APPLICATION MANUAL CATALOG No.: LSI-6TD427A2

1997.12

#### IMPORTANT NOTICE

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. Yamaha assumes no liability for incidental, consequential or special damages or injury that may result from misapplication or improper use or operation of the Products.

- 4. Yamaha makes no warranty or representation that the Products are subject to intellectual property license from Yamaha or any third party, and Yamaha makes no warranty or representation of non-infringement with respect to the Products. Yamaha specifically excludes any liability to the Customer or any third party arising from or related to the Products' infringement of any third party's intellectual property rights, including the patent, copyright, trademark or trade secret rights of any third party.

- 5. Examples of use described herein are merely to indicate the characteristics and performance of Yamaha products. Yamaha assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein. Yamaha makes no warranty with respect to the products, express or implied, including, but not limited to the warranties of merchantability, fitness for a particular use and title.

# Contents

| 1 | INTRODUCTION                         | 3  |

|---|--------------------------------------|----|

|   | 1.1 General Description              | 3  |

|   | 1.2 Features                         | 3  |

| 2 | BLOCK DIAGRAM                        | 5  |

| 3 | PIN DESCRIPTIONS                     | 7  |

|   | 3.1 Pin Assignments                  | 7  |

|   | 3.2 Pin Functions                    |    |

| 4 | FUNCTIONS                            | 11 |

| 5 | ELECTRICAL CHARACTERISTICS           | 13 |

|   | 5.1 Absolute Maximum Ratings         | 13 |

|   | 5.2 Recommended Operating Conditions | 14 |

|   | 5.3 DC Characteristics               | 15 |

|   | 5.4 AC Characteristics               | 17 |

| 6 | PACKAGE OUTLINE                      | 19 |

| A | PPENDIX                              |    |

| A | EXMAPLE OF APPLICATIONS              | 21 |

|   | A.1 Example of Application Circuits  | 21 |

2 CONTENTS

# INTRODUCTION

#### 1.1 General Description

YTD427 is a communication LSI which provides the ISDN subscriber interface (two-wire metallic time compression multiplexing operation). It is capable of providing the electric characteristics conforming to TTC Standard JT-G961.

A DSU (Digital Service Unit) can easily be constructed by combining with YTD426B.

#### 1.2 Features

- 1. Automatic Gain Control (AGC) function

- 2. Filter function

- 3. Peak hold function

- 4. ADC (Analog Digital Converter) function

- 5. Low Power Consumption

Operation mode 72mW(typ.)

- 6. CMOS technology

- 7. 64-pin QFP

- 8. Single +5 volt supply

# **BLOCK DIAGRAM**

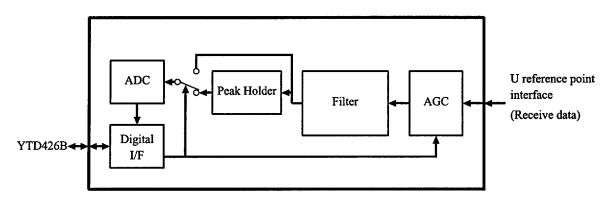

YTD 427 internal block diagram is shown in Figure 2.1.

Figure 2.1: Internal Block Diagram

# PIN DESCRIPTIONS

#### 3.1 Pin Assignments

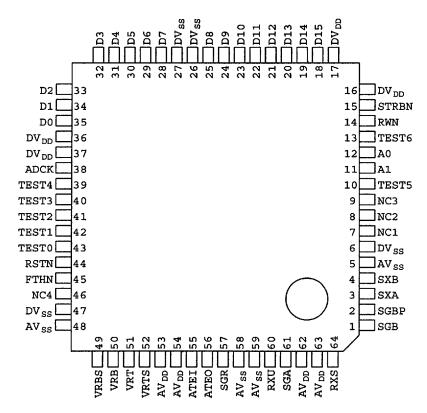

The pin assignments of YTD427 are shown in Figure 3.1.

Figure 3.1: YTD427-F (64-pin QFP) Pin Assignments [Top View]

#### 3.2 Pin Functions

| Pin No.        | Pin Name                    | I/O | Function                                                                 | Remarks                                 |

|----------------|-----------------------------|-----|--------------------------------------------------------------------------|-----------------------------------------|

| 1              | SGB                         |     | Connect a $0.015\mu F$ capacitor across the SGB and SGR pins.            |                                         |

| 2              | SGBP                        | _   | Connect a $0.015\mu F$ capacitor across the SGBP and SGR pins.           |                                         |

| 3              | SXA                         | _   | Connected to SXB.                                                        |                                         |

| 4              | SXB                         | _   | Connected to SXA.                                                        |                                         |

| 5, 48, 58, 59  | AV <sub>SS</sub>            | GND | Analog ground                                                            | All pins must<br>be joined<br>together. |

| 6, 26, 27, 47  | $\mathrm{DV}_{\mathrm{SS}}$ | GND | Digital ground                                                           | All pins must<br>be joined<br>together. |

| 7              | NC1                         | IN  | Unused<br>Connected to DV <sub>SS</sub>                                  |                                         |

| 8              | NC2                         | IN  | Unused<br>Connected to DV <sub>SS</sub>                                  |                                         |

| 9              | NC3                         | IN  | Unused<br>Connected to DV <sub>SS</sub>                                  |                                         |

| 10             | TEST5                       | IN  | Test input 5 Connected to DV <sub>SS</sub>                               |                                         |

| 11             | A1                          | IN  | Address bus bit 1 Connected to ADDRES1 of YTD426B                        |                                         |

| 12             | A0                          | IN  | Address bus bit 0 Connected to ADDRES0 of YTD426B                        |                                         |

| 13             | TEST6                       | IN  | Test input 6 Connected to DV <sub>SS</sub>                               | ·                                       |

| 14             | RWN                         | IN  | Read/write signal  "H": Read  "L": Write  Connected to RWN of YTD426B    |                                         |

| 15             | STRBN                       | IN  | Strobe signal  "H": Inactive  "L": Active  Connected to STRBN of YTD426B |                                         |

| 16, 17, 36, 37 | $\mathrm{DV_{DD}}$          | PWR | Digital power supply                                                     | All pins must<br>be joined<br>together. |

3.2. PIN FUNCTIONS 9

| Pin No. | Pin Name | I/O     | Function                           | Remarks        |                |  |

|---------|----------|---------|------------------------------------|----------------|----------------|--|

| 18      | D15      | OUT     | Data bus bit 15                    |                |                |  |

| 16      | D19      | 001     | Connected to AFEDATA15 of YTD426B. |                |                |  |

| 19      | D14      | OUT     | Data bus bit 14                    |                |                |  |

| 19      | D14      | 001     | Connected to AFEDATA14 of YTD426B. |                |                |  |

| 20      | D13      | OUT     | Data bus bit 13                    |                |                |  |

| 20      | D13      | 001     | Connected to AFEDATA13 of YTD426B. |                |                |  |

| 21      | D12      | OUT     | Data bus bit 12                    |                |                |  |

| 21      | D12      | 001     | Connected to AFEDATA12 of YTD426B. | •              |                |  |

| 22      | D11      | OUT     | Data bus bit 11                    |                |                |  |

| 22      | D11      | 001     | Connected to AFEDATA11 of YTD426B. |                |                |  |

| 0.2     | D10      | OUT     | Data bus bit 10                    |                |                |  |

| 23      | D10      | 001     | Connected to AFEDATA10 of YTD426B. |                |                |  |

| 24      | 24 D9    | Do      | OUT                                | Data bus bit 9 |                |  |

| 24      |          | OUT     | Connected to AFEDATA9 of YTD426B.  |                |                |  |

| 25      | 25 D8    | Do OITT | OUT                                | Data bus bit 8 |                |  |

| 25      | D0       | 001     | Connected to AFEDATA8 of YTD426B.  |                |                |  |

| 28      | D7       | D7      | D7                                 | IN             | Data bus bit 7 |  |

| 28      | ן טיי    | IIN     | Connected to AFEDATA7 of YTD426B.  |                |                |  |

| 29      | D6       | 06 IN   | Data bus bit 6                     |                |                |  |

| 29      | 1 100    | 111     | Connected to AFEDATA6 of YTD426B.  |                |                |  |

| 30      | D5       | IN      | Data bus bit 5                     |                |                |  |

| 30      | Do       | 111/    | Connected to AFEDATA5 of YTD426B.  |                |                |  |

| 31      | D4       | IN      | Data bus bit 4                     |                |                |  |

| 31      | D4       | 111     | Connected to AFEDATA4 of YTD426B.  |                |                |  |

| 32      | D3       | IN      | Data bus bit 3                     |                |                |  |

| 32      | D3       | 114     | Connected to AFEDATA3 of YTD426B.  |                |                |  |

| 33      | D2       | IN      | Data bus bit 2                     |                |                |  |

| 33      | 102      | 111     | Connected to AFEDATA2 of YTD426B.  |                |                |  |

| 34      | D1       | IN      | Data bus bit 1                     |                |                |  |

| ±       | 1/1      | 77.4    | Connected to AFEDATA1 of YTD426B.  |                |                |  |

| 35      | D0       | IN      | Data bus bit 0                     |                |                |  |

| J.      | 1 100    | 11.4    | Connected to AFEDATA0 of YTD426B.  |                |                |  |

| Pin No.        | Pin Name  | I/O | Function                                                            | Remarks                                 |

|----------------|-----------|-----|---------------------------------------------------------------------|-----------------------------------------|

| 38             | ADCK      | IN  | ADC operation clock signal<br>Connected to CLK640K of YTD426B.      |                                         |

| 39             | TEST4     | IN  | Test input 4 Connected to DV <sub>SS</sub> .                        |                                         |

| 40             | TEST3N    | I/O | Test input 3 Usually fixed to "H".                                  |                                         |

| 41             | TEST2     | IN  | Test input 2 Connected to DV <sub>SS</sub> .                        |                                         |

| 42             | TEST1     | IN  | Test input 1 Connected to DV <sub>SS</sub> .                        |                                         |

| 43             | TEST0     | IN  | Test input 0 Connected to DV <sub>SS</sub> .                        |                                         |

| 44             | RSTN      | IN  | Reset input pin  "L": Reset  Reset time is $2\mu s(\text{minimum})$ |                                         |

| 45             | FTHN      | IN  | Test input Usually fixed to "H".                                    |                                         |

| 46             | NC4       | IN  | Unused Connected to DV <sub>SS</sub> .                              |                                         |

| 49             | VRBS      | OUT | ADC reference power supply output (low voltage)                     |                                         |

| 50             | VRB       | IN  | ADC reference power supply input (low voltage)                      |                                         |

| 51             | VRT       | IN  | ADC reference power supply input (high voltage)                     |                                         |

| 52             | VRTS      | OUT | ADC reference power supply output (high voltage)                    |                                         |

| 53, 54, 62, 63 | $AV_{DD}$ | PWR | Analog power supply                                                 | All pins must<br>be joined<br>together. |

| 55             | ATEI      | IN  | Test signal input Connected to AV <sub>SS</sub> .                   |                                         |

| 56             | ATEO      | I/O | Test signal input, output<br>Connected to AV <sub>SS</sub> .        |                                         |

| 57             | SGR       | OUT | Analog signal reference output                                      |                                         |

| 60             | RXU       | IN  | Receive signal input                                                |                                         |

| 61             | SGA       | _   | Connect a $0.0047\mu F$ capacitor across SGA and SGR.               |                                         |

| 64             | RXS       |     | Connect a $0.0022\mu\mathrm{F}$ capacitor across RXS and SGR.       |                                         |

# **FUNCTIONS**

Receive Interface

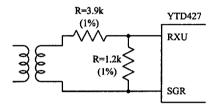

Receive pin RXU has a high input impedance. An example of a reference circuit of the receive interface is shown in Figure 4.1.

Figure 4.1: Receive Interface Connection

AGC

The AGC section adjusts the gain in 0.22 dB step in the range from 0.0 to 56.1 dB at the receive signal center frequency (f=160 kHz) and amplifies the receive signal amplitude to the maximum dynamic range.

Filter

The filter section is to prevent the ADC and the peak hold section from erroneous operation caused by high-frequency noise.

Peak Hold section

Peak hold is performed during the initial training so that the gain of the AGC section is set to make best communication condition.

ADC

The ADC section makes an A/D conversion of the received signal and transfers it to YTD426B. The A/D conversion timing is synchronized to the clock (ADCK) provided by YTD426B.

Digital Interface

The digital section provides the interface to YTD426B.

## ELECTRICAL CHARACTERISTICS

#### 5.1 Absolute Maximum Ratings

$(DV_{SS}=AV_{SS}=0.0V T_a=25 C)$

| Parameters               | Symbol            | Min.                   | Max.                     | Units         |

|--------------------------|-------------------|------------------------|--------------------------|---------------|

| Supply Voltage (Digital) | $DV_{DD}$         | -0.3                   | +7.0                     | V             |

| Supply Voltage (Analog)  | AV <sub>DD</sub>  | -0.3                   | +7.0                     | v             |

| Input Voltage (Digital)  | $DV_{IN}$         | $DV_{SS} - 0.3$        | $DV_{DD} + 0.3$          | v             |

| Input Voltage (Analog)   | $AV_{IN}$         | $AV_{SS} - 0.3$        | $AV_{DD}+0.3$            | v             |

| Output Voltage (Digital) | DVOUT             | $\mathrm{DV_{SS}}-0.3$ | $\mathrm{DV_{DD}}{+0.3}$ | v             |

| Output Voltage (Analog)  | AVOUT             | $AV_{SS}-0.3$          | $AV_{DD}+0.3$            | v             |

| Power Dissipation        | $P_{D}$           |                        | 400                      | mW            |

| Operating Temperature    | $T_{OP}$          | -20                    | +70                      | $\mathcal{C}$ |

| Storage Temperature      | $\mathbf{T_{ST}}$ | -55                    | +125                     | $\mathcal{C}$ |

- Note 1 The values represent the minimum and maximum voltages that can be applied to the pins without causing damage. It does not guarantee the operation. Applying a voltage exceeding the absolute maximum ratings may cause permanent damage to YTD427.

- Note 2 Use digital power supply  $DV_{DD}$  and analog power supply  $AV_{DD}$  under the condition:  $DV_{DD} = AV_{DD}$ . Also, insert a  $C \geq 0.1 \mu F$  across  $DV_{DD}$  and  $DV_{SS}$  and across  $AV_{DD}$  and  $AV_{SS}$  to prevent latch up.

- Note 3 Use digital ground  $DV_{SS}$  and analog ground  $AV_{SS}$  under the condition:  $DV_{SS} = AV_{SS}$ .

- Note 4 Even though digital power supply  $DV_{DD}$  and analog power supply  $AV_{DD}$  have the same pin name, they are not connected inside YTD427. Make sure to connect the pins that have the same name.

- Note 5 Even though digital ground DV<sub>SS</sub> and analog ground AV<sub>SS</sub> have the same pin name, they are not connected inside YTD427. Make sure to connect the pins that have the same name.

#### 5.2 Recommended Operating Conditions

(DV<sub>SS</sub>=AV<sub>SS</sub>=0.0V.  $T_a$ =25 °C)

| Parameters                          | Symbol              | Condition | Min.             | Тур. | Max.      | Units |

|-------------------------------------|---------------------|-----------|------------------|------|-----------|-------|

| Digital Power Supply Voltage        | $DV_{DD}$           |           | 4.75             | 5.0  | 5.25      | V     |

| Analog Power Supply Voltage         | $AV_{DD}$           |           | 4.75             | 5.0  | 5.25      | v     |

| Digital Input Voltage               | $DV_{IN}$           |           | $DV_{SS}$        |      | $DV_{DD}$ | v     |

| Analog Input Voltage                | $AV_{IN}$           |           | $AV_{SS}$        |      | $AV_{DD}$ | v     |

| Digital Output Voltage              | $DV_{IN}$           |           | DV <sub>SS</sub> |      | $DV_{DD}$ | v     |

| Analog Output Voltage               | AV <sub>IN</sub>    |           | AVSS             |      | $AV_{DD}$ | v     |

| Operating Temperature Range         | $T_{OP}$            |           | -20              | 25   | 70        | ဗ     |

| External Clock Input                |                     |           |                  |      |           |       |

| Clock Frequency                     | $f_{\mathrm{CP}}$   | (Note1)   |                  | 0.64 |           | MHz   |

| Clock Frequency Allowable Deviation | $\Delta f_{CP}$     | (Note1)   | -50              |      | 50        | ppm   |

| Clock Duty                          | $t_{DUTY}$          | (Note1)   | 45               | 50   | 55        | %     |

| High Level Time                     | $t_{WCH}$           | (Note1)   | 400              |      |           | ns    |

| Low Level Time                      | twcl                | (Note1)   | 400              |      |           | ns    |

| Rise Time                           | tTLHC               | (Note1)   |                  |      | 20        | ns    |

| Fall Time                           | t <sub>THLC</sub>   | (Note1)   |                  |      | 20        | ns    |

| YTD426 Supply Input Signal          |                     |           |                  |      |           |       |

| High-Level Pulse Width              | $t_{\mathrm{WDH}}$  | (Note2)   | 90               |      |           | ns    |

| Low-Level Pulse Width               | $t_{\mathrm{WDL}}$  | (Note2)   | 90               |      |           | ns    |

| Rise Time                           | $t_{\mathrm{TLHD}}$ | (Note2)   |                  |      | 10        | ns    |

| Fall Time                           | $t_{ m THLD}$       | (Note2)   |                  |      | 10        | ns    |

Note 1 With respect to ADCK pin.

Note 2 With respect to A1, A0, RWN, STRBN, D15 to D0 pins.

#### 5.3 DC Characteristics

$({\rm DV_{DD}}{=}{\rm AV_{DD}}{=}4.75{\sim}5.25{\rm V},\,{\rm DV_{SS}}{=}{\rm AV_{SS}}{=}0.0{\rm V},\,{\rm T_a}{=}25~{\rm ^{\circ}\!\!C})$

| Parameters          | Symbol             | Condition | Min.                  | Тур. | Max.                  | Units                  |

|---------------------|--------------------|-----------|-----------------------|------|-----------------------|------------------------|

| High-Level Input    | $V_{\mathrm{IHC}}$ | (Note1)   | $0.7\mathrm{DV_{DD}}$ |      | $DV_{DD}$             | V                      |

| Voltage (CMOS)      |                    |           |                       |      |                       |                        |

| Low-Level Input     | $V_{ILC}$          | (Note1)   | 0.0                   |      | $0.3\mathrm{DV_{DD}}$ | V                      |

| Voltage (CMOS)      |                    |           |                       |      |                       |                        |

| Input Leak          | $I_{LIC}$          | (Note1)   |                       |      | ±10                   | $\mu$ A                |

| Current (CMOS)      |                    | (Note2)   |                       |      |                       |                        |

| High-Level          | $V_{IHT}$          | (Note3)   | 2.0                   |      | $DV_{DD}$             | V                      |

| Input Voltage (TTL) |                    |           |                       |      |                       |                        |

| Low-Level Input     | V <sub>ILT</sub>   | (Note3)   | 0.0                   |      | 0.8                   | v                      |

| Voltage (TTL)       |                    |           |                       |      |                       |                        |

| Input Leak          | I <sub>LIT</sub>   | (Note3)   |                       |      | ±10                   | $\mu$ A                |

| Current (TTL)       |                    | (Note4)   |                       |      |                       |                        |

| High-Level Output   | $V_{OHT}$          | (Note3)   | 4.4                   |      |                       | V                      |

| Voltage (TTL)       |                    | (Note5)   |                       |      |                       |                        |

| Low-Level Output    | $V_{OLT}$          | (Note3)   |                       |      | 0.4                   | V                      |

| Voltage (TTL)       |                    | (Note6)   |                       |      |                       |                        |

| Supply Current      | $I_{\mathrm{DD1}}$ | (Note7)   |                       | 14.4 | 24.9                  | mA                     |

| (Normal)            |                    |           |                       |      |                       |                        |

| Supply Current      | $I_{\mathrm{DD4}}$ | (Note7)   |                       | 4.4  | 7.6                   | mA                     |

| (at reset)          |                    | (Note8)   |                       |      |                       |                        |

| Power Consumption   | P <sub>tot1</sub>  | (Note7)   |                       | 72   | 131                   | $\mathbf{m}\mathbf{W}$ |

| (Normal)            |                    |           |                       |      |                       |                        |

| Power Consumption   | P <sub>tot4</sub>  | (Note7)   |                       | 22   | 40                    | mW                     |

| (at reset)          |                    | (Note8)   |                       |      |                       |                        |

Note1 With respect to ADCK, TEST4, TEST2 to TEST0, RSTN, FTHN, NC4 to NC1 pins.

Note2  $V_{IC}=DV_{SS}$  -  $DV_{DD}$

Note3 With respect to A1, A0, RWN, STRBN, D15 to D0, TEST3, TEST5, TEST6 pins.

Note4  $V_{IT}=DV_{SS}$  -  $DV_{DD}$

Note5 I<sub>OH</sub>=-4mA

Note6  $I_{OL}=12mA$

Note7 Neither external circuit nor parts

Note8 ADCK pin fixed to  $DV_{SS}$

$(DV_{DD}=AV_{DD}=4.75\sim5.25V, DV_{SS}=AV_{SS}=0.0V, T_a=25 \ ^{\circ}C)$

| Parameters              | Symbol    | Condition | Min.                           | Тур.                   | Max.                               | Units              |

|-------------------------|-----------|-----------|--------------------------------|------------------------|------------------------------------|--------------------|

| Analog Output Allowable | Zo        | (Note1)   | 30                             |                        |                                    | kΩ                 |

| Load Impedance          |           |           |                                |                        |                                    |                    |

| Analog Receive Buffer   | $Z_{i1}$  | (Note2)   | 10                             |                        |                                    | MΩ                 |

| Input Impedance         |           |           |                                |                        |                                    |                    |

| Analog Receive Buffer   | $Z_{i2}$  | (Note3)   |                                | 100                    |                                    | kΩ                 |

| Input Impedance         |           | :         |                                |                        |                                    |                    |

| Reference Resistance    | $R_{REF}$ | (Note4)   | 1.92                           | 2.40                   | 3.84                               | $\mathbf{k}\Omega$ |

| Voltage Divider         | $R_{DIV}$ | (Note5)   | 1.44                           | 1.80                   | 2.88                               | ${f k}\Omega$      |

| Resistance              |           |           |                                |                        |                                    |                    |

| Analog Signal Reference | $V_{SG}$  | (Note6)   | $0.5\mathrm{AV_{DD}}$ - $0.05$ | $0.5 \mathrm{AV_{DD}}$ | $0.5 \text{AV}_{\text{DD}} + 0.05$ | V                  |

| Voltage                 |           |           |                                |                        |                                    |                    |

| ADC                     |           |           |                                |                        |                                    |                    |

| High-Level Reference    | $V_{RT}$  | (Note7)   | $0.7 \mathrm{AV_{DD}}$         |                        | AV <sub>DD</sub>                   | V                  |

| Voltage Level           |           |           |                                |                        |                                    |                    |

| Low-Level Reference     | $V_{RB}$  | (Note8)   | 0.0                            |                        | $0.3 \mathrm{AV_{DD}}$             | V                  |

| Voltage Level           |           |           |                                |                        |                                    |                    |

| Self-Bias VRT           | $V_{RTS}$ | (Note9)   | $0.7\mathrm{AV_{DD}}$ - $0.1$  | $0.7 \mathrm{AV_{DD}}$ | $0.7 \text{AV}_{\text{DD}} + 0.1$  | v                  |

| Self-Bias VRB           | $V_{RBS}$ | (Note10)  | $0.3 \mathrm{AV_{DD}}$ - $0.1$ | $0.3 \mathrm{AV_{DD}}$ | $0.3 \text{AV}_{\text{DD}} + 0.1$  | v                  |

Note1 With respect to SGR, SXA pins.

Note2 With respect to RXU pin.

Note3 With respect to SXB pin.

Note4 Across VRT and VRB pins. VRB=1.5 V

$\bf Note5~{\rm Across~VRT~and~AV_{\rm DD}}$  pins and across VRB and  $\rm AV_{SS}$  pins.

Note6 SGR pin is open.

Note7 With respect to VRT pin.

Note8 With respect to VRB pin.

Note9 Short VRT pin and VRTS pin

Note10 Short VRB pin and VRBS pin

#### 5.4 AC Characteristics

$(DV_{DD} = AV_{DD} = 4.75 \sim 5.25V, DV_{SS} = AV_{SS} = 0.0V, T_a = 25 \text{ }^{\circ}\text{C})$

|         | Parameters           |                            | Condition | Min.  | Тур.  | Max.  | Units      |

|---------|----------------------|----------------------------|-----------|-------|-------|-------|------------|

| Total I | Harmonic Distortion  | THD                        |           |       |       | 1.0   | %          |

|         | Gain                 | $G_{\mathbf{A}}$           |           | 43.76 | 45.76 | 47.76 | dB         |

| AGC     | Noise                | $N_{oag}$                  |           |       |       | 6     | $mV_{rms}$ |

|         | DC Offset Voltage    | $V_{agoff}$                |           |       |       | ±50   | mV         |

| Filter  | Cut Off Frequency    | $\mathbf{f_c}$             |           | 213   | 320   | 427   | kHz        |

|         | Flatness             | $\mathbf{A}_{\mathbf{p}}$  |           | -1.0  | 0.0   | 1.0   | dB         |

|         | Max. Conversion Time | $F_{PH}$                   |           |       | 160   | 200   | kHz        |

| PH      | Refresh Time         | $t_{ m phr}$               |           |       | 60    | 100   | ns         |

|         | Peak Hold Error      | $V_{ m phe}$               |           |       |       | ±50   | mV         |

|         | Resolution           | $ m R_{es}$                |           |       |       | 8     | Bit        |

|         | Linearity Error      | EL                         |           |       | ±1.0  | ±2.0  | LSB        |

| ADC     | Quantization Error   | $\mathbf{E}_{e}$           |           | -1.0  |       | 1.0   | LSB        |

|         | Max. Conversion Time | $\mathbf{F}_{\mathtt{AD}}$ |           |       |       | 1.28  | MSPS       |

| [       | Clock Frequency      | $F_{ADCK}$                 |           |       | 640   |       | kHz        |

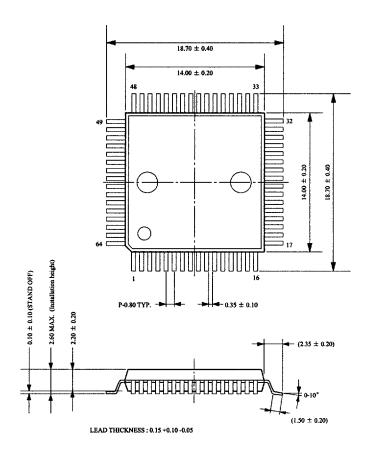

# PACKAGE OUTLINE

(UNIT): mm (millimeters)

The shape of the molded corner may be slightly different from the shape in this diagram

The figure in the parenthesis ( ) should be used as a reference. Plastic body dimensions do not include burr of resin.

Note: The LSIs for surface mount need special consideration on storage and soldering conditions. For detailed information, please contact your nearest Yamaha agent.

# Appendix A

# EXMAPLE OF APPLICATIONS

#### A.1 Example of Application Circuits

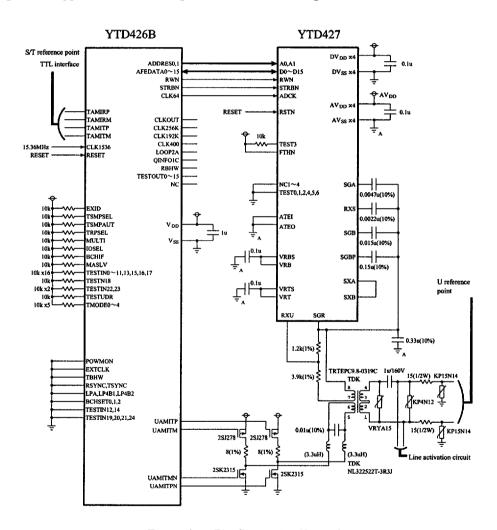

An example of an application circuit using YTD427 is shown in Figure A.1.

Figure A.1: Pin Connection Example