## ST5421

## SID-GCI: S/T INTERFACE DEVICE WITH GCI

PRELIMINARY DATA

- SINGLE CHIP 4 WIRES 192kb/s TRANS-CEIVER FULLY COMPLYING WITH CCITT I.430

- ISDN BASIC ACCESS HANDLING 144kb/s 2B + D TRANSMISSION

- GCI COMPATIBLE INTERCHIP INTERFACE

- ADAPTIVE AND FIXED TIMING OPTIONS FOR NT

- CLOCK RESYNCHRONIZER AND DATA BUFFERS FOR NT2

- PROGRAMMABLE S1 AND Q CHANNELS HANDLING ACCORDING TO US ANSI STANDARD FOR LAYER 1 MAINTENANCE

- EASILY INTERFACEABLE WITH ST5451 HDLC & GCI CONTROLLER AND ANY OTHER GCI COMPATIBLE DEVICE

#### DESCRIPTION

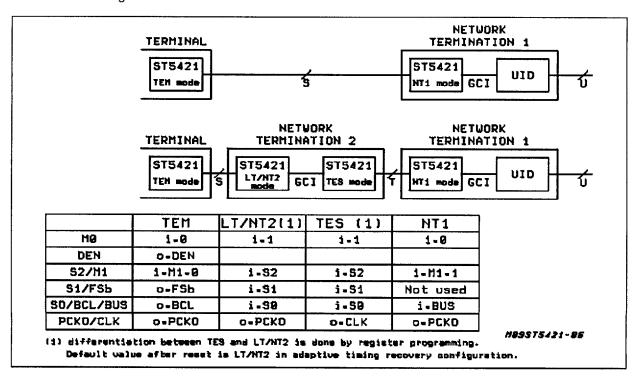

The ST5421 (SID-GCI) is a complete monolithic transceiver for data transmission on twisted pair subscriber loops. It is bullt on SGS-THOMSON HCMOS 3A double metal advanced process, and requires only a single + 5V supply. All functions specified in CCITT recommendation I.430 for ISDN basic access at the 'S' and 'T' interfaces are provided, and the device can be configured to operate either in TE (Terminal Equipment), in NT1 or NT2 (Network Termination) or in PABX line-card device.

GCI interchip interface highly enhances device connection efficiency by multiplexing controls and data on the same bus and requiring only 4 pins. ST5421 implements all the GCI standard functions for Monitor and Control/Indicate channels, supporting up to 8 GCI peripherals in multiplexed mode.

As specified in I.430, full-duplex transmission at 192kb/s is provided on separate transmit and receive twisted wire pairs using inverted Alternate Mark Inversion (AMI) line coding. Various channels are combined to form the 192kb/s aggregate rate, including 2 'B' channels, each of 64kb/s, and 1 'D' channel at 16kb/s. In addition, multiframe transmission is provided in a switchable processing mode based on United State ANSI standard for Layer 1 maintenance. 800 bit/s message oriented data transmission is supported by S1 and Q channels.

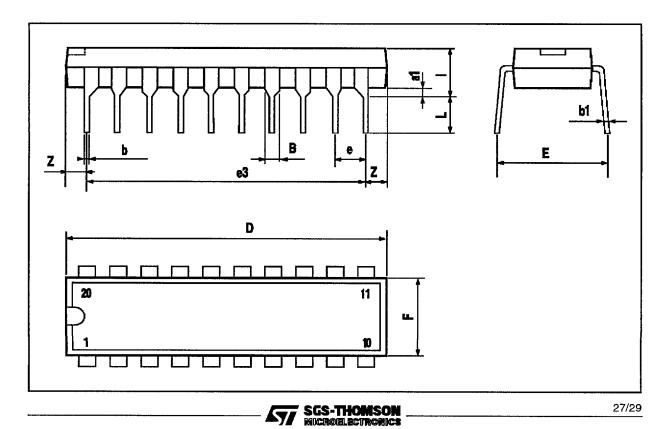

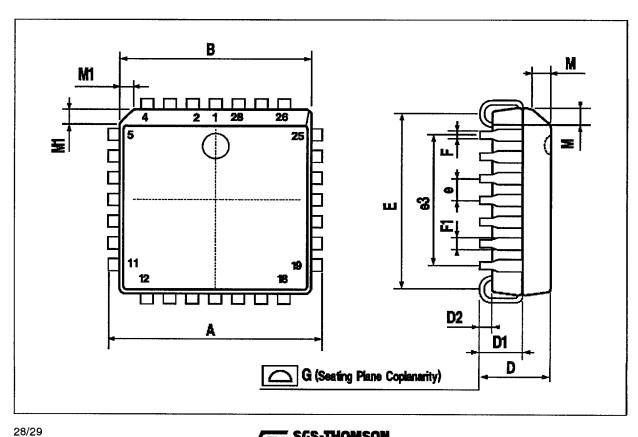

## PIN CONNECTIONS (Top views)

September 1995

1/29

■ 7929237 0071582 4T1 ■

## **DESCRIPTION** (Continued)

All I.430 wiring configurations are supported by ST5421 including passive bus for TE's distributed point-to-point and point-to-multipoint extended. Adaptive receive signal processing enables the device to operate with low bit error rate on any of

the standard types of cable pairs commonly found in premise wiring installations when tested with the noise sources specified in I.430.

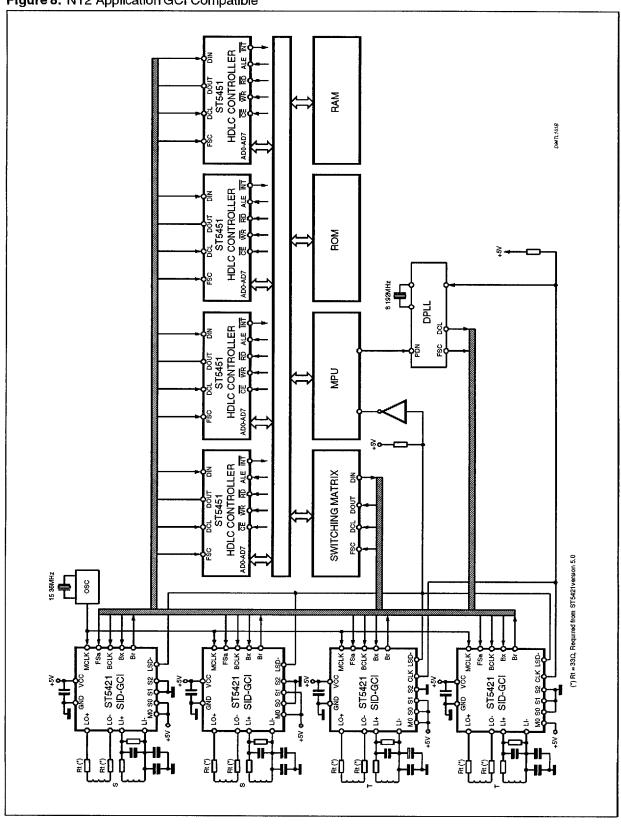

Far-end Clock Resynchronizer automatically selected, data buffer and slave-slave mode allow design of NT2 trunk-card connected to several T interfaces.

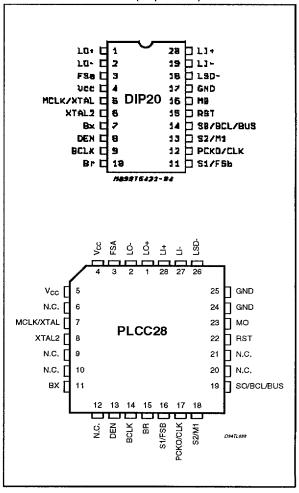

#### **BLOCK DIAGRAM**

2/29

SGS-THOMSON MICROELECTRONICS

**7929237 0071583 338 🞟**

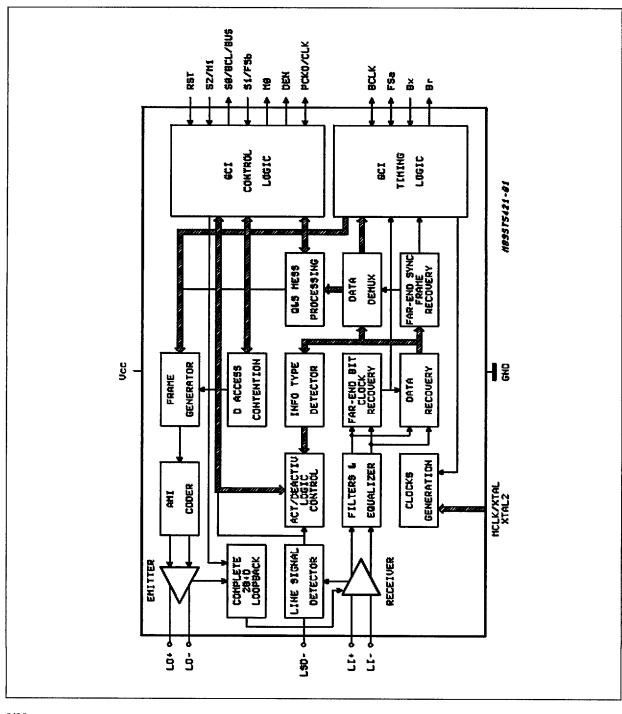

## **PIN DESCRIPTION**

| Name          | DIP | PLCC                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND           | 17  | 24,25               | Ground Reference Voltage: all analog and digital signals are referenced to this pin.                                                                                                                                                                                                                                                                                                                                                                |

| Vcc           | 4   | 4,5                 | Positive Power Supply Input 5V ( ± 5%) relative to GND                                                                                                                                                                                                                                                                                                                                                                                              |

| MCLK/XTAL     | 5   | 7                   | Master Clock or Crystal Oscillator Input: this pin requires either a 15.36MHz crystal (parallel resonant with $R_{\rm S}<$ 100 $\Omega$ ) to be tied between this pin and XTAL2 or a logic CMOS level 15.36MHz clock from a stable source. When using a 20pF crystal, a total of 33pF load capacitance to GND must also be connected. In NT configurations. MCLK clock input doesn't need to be synchronous with the Network Reference Clock (FSa). |

| XTAL2         | 6   | 8                   | Crystal Oscillator Output. This pin should be connected to one end of the 15.36MHz crystal, otherwise is not connected. (see MCLK/XTAL).                                                                                                                                                                                                                                                                                                            |

| BCLK          | 9   | 14                  | Bit Clock: this signal determines the data shift rate at GCI. Data is shifted-in on Bx and shifted-out on Br at half the BCLK frequency. When NT/TES mode is selected, BCLK is an input which does not need to be synchronous with the Master Clock input (MCLK).  When TEM is selected, BCLK is an output at frequency of 1536kHz. This clock is phase locked to the receive line signal and synchronous with FSa output.                          |

| FSa           | 3   | 3                   | Frame Synchronization Clock: 8kHz clock which defines the start of the frame. In GCI slave (NT/TES) FSa is an input used as a network reference clock for S/T line. In GCI master (TEM) is an output applicable as a validation strobe for the first B channel.                                                                                                                                                                                     |

| S1/FSb        | 11  | 16                  | S1 if M0 = 1; is GCI channel number selection (input). FSb if M0 = 0 and M1 = 0 (TEM): is a data strobe indicating the active slot for the second B channel on the GCI (output). In NT1 mode, M0 = 0; M1 = 1, this pin is not used and must be left floating.                                                                                                                                                                                       |

| Вх            | 7   | 11                  | Digital Input for GCI Channels: data to be transmitted to S line is shifted-in at half the BCLK frequency on the 2nd falling edge.                                                                                                                                                                                                                                                                                                                  |

| Br            | 10  | 15                  | Digital Output for GCI Channel (OPENDRAIN): data is shifted-out at half the BCLK frequency on the transmit rising edges of BCLK. An external pull-up resistor is needed.                                                                                                                                                                                                                                                                            |

| DEN           | 8   | 13                  | In TEM mode DEN is an output, normally low, that pulses high to indicate the active time slot for D channel data at the Bx input. It is intended to be gated with BCLK to control the D channel shifting from a layer 2 device (i.e. ST5451) to ST5421 transmit buffer. Using ST5451 HDCL/GCI controller, no external circuitry is needed. In NT/TES mode this pin is not used and must be kept floating.                                           |

| Not Connected | -   | 6,9,10,<br>12,20,21 | Leave open on the board.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PCK0/CLK      | 12  | 17                  | PCK0 IN TEM, LT/NT2, NT1 mode: 32 kHz clock output synchronized to GCl clocks. It is intended to synchronize DC/DC converter in TEM mode. CLK in TES mode: is a clock signal open drain output phased-locked to the receive S line signal and applicable as far-end clock reference. Its frequency is 1536kHz compatible with 768kbit/s GCl data rate. An external pull-up resistor is needed.                                                      |

| Мо            | 16  | 23                  | M0 = 0; GCl mode selection; Time slot Assigner is selected on GCl channel 0. $M0$ = 1; GCl in a multiplex mode; S0, S1, S2 pins define the GCl channel number allocated to ST5421. TES/NT2 selection is done with the configuration registers (input).                                                                                                                                                                                              |

## **PIN DESCRIPTION** (continued)

| Name       | DIP   | PLCC  | Description                                                                                                                                                                                                                                                                                        |

|------------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S2/M1      | 13    | 18    | S2 if M0 = 1: GCI channel number selection (input). When M0 = 0 M1 select TEM or NT1 mode: M1 = 0 selects TEM, M1 = 1 selects NT1.                                                                                                                                                                 |

| S0/BCL/BUS | 14    | 19    | S0 if M0 = 1; GCl channel number selection (input). BCL in TEM; bit clock output at 768kHz compatible with COMBO families ETC5054/57. BUS in NT1; S Bus Configuration Selection: low for fixed timing recovery and high for adaptive timing recovery (input).                                      |

| RST        | 15    | 22    | Reset Pin: must be low at Power On Reset; after, a high pulse on this pin reset ST5421 in a state depending on the other configuration pins (input).                                                                                                                                               |

| LSD-       | 18    | 26    | Line Signal Detect: open drain output, normally high impedance, pulling low when SID-GCI is powered down and an S line signal is detected. It is applicable to wake up a microprocessor from a low power idle mode. LSD <sup>-</sup> output goes back to high impedance when ST5421 is powered up. |

| LO+, LO-   | 1,2   | 1,2   | Transmit AMI signal differential outputs to the S/T line transformer; when used with an appropriate 2:1 step down transformer, the line signal conforms to the output pulse masks in CCITT 1.430.                                                                                                  |

| LIT,LI*    | 19,20 | 27,28 | Receive AMI signal inputs from the S/T line transformer. They should be connected to an appropriate 1:2 or 1:1 transformer through a line coupling circuit to conform I.430 recommendation. LI pin is also the internal voltage reference pin.                                                     |

Table 1: Pin configurations

#### **FUNCTIONAL DESCRIPTION**

#### POWER ON INITIALIZATION

Following initial application of power, SID-GCI enters the power down de-activated state.

RST input must be tied low during power-on.

After Power on reset, all the internal I.430 circuits including the master oscillator are inactive and in a low power state except for the line signal detection circuit.

After any period of activity a high pulse on RST reset completely SID-GCI.

Configuration mode programming of SID-GCI is done by means of pins polarization and register programming.

NT1 and TEM modes are defined only by means of 2 configuration pins M0, M1 at Power On Reset.

For NT2 and TES modes (M0=1), configuration has to be completed by means of a Control Instruction on Monitor channel prior a Power Up instruction.

#### POWER UP/DOWN CONTROL

When TEM configuration is selected, ST5421 provides GCI Clocks needed for control channel transfer. Power Up instruction is directly provided by pulling low the Bx data input. SID-GCI then reacts sending GCI clocks. LSD- output pin can be directly connected to Bx data input for providing an automatic Power up when far-end attempts to activate.

After a period of activity, Power down state is normally re-entered by C/I control code DC (1111) while ST5421 is sending C/I indication code DP (0000); then ST5421 send twice C/I indication code DI(1111) before to power down.

It is possible to force immediately power down state by using PDN (0001) C/I control code.

When NT1 configuration is selected, ST5421 is powered up directly by receiving GCI clocks on BCLK and FSa input from the "U" device. The only way to power down ST5421 is to stop BCLK or FSa clock signal inputs.

For example PDN (0001) C/I control code has no effect.

When NT2 or TES configuration is selected, SID-GCI is powered up by the PUP code (0000) on C/I Control Channel. After a period of activity, Power down state is normally reentred by C/I control code DC (1111) while ST5421 is sending C/I indication DI(1111).

It is possible to force immediately Power down state by using PDN (0001) C/I control code. In

NT1, NT2 or TES mode, loss of GCI clocks automatically forces the power down state.

#### POWER UP/DOWN STATE

Following a period of activity in the power up state, power down state may be re-entered as described above. Configuration Registers remain in their current state. They can be changed by the GCI Monitor channel.

The power down transition disables analog and 1.430 circuitry, stops the Crystal Oscillator and all the clocks internally generated. Line Signal Detector Circuit remains active allowing LSD-pin to pull low if a receive signal is detected.

Power up transition enables all analog and I.430 circuitry, starts the Crystal oscillator and reset the state machine to the de-activated state. It also inhibits LSD-output.

#### LINE CODING AND FRAME FORMAT

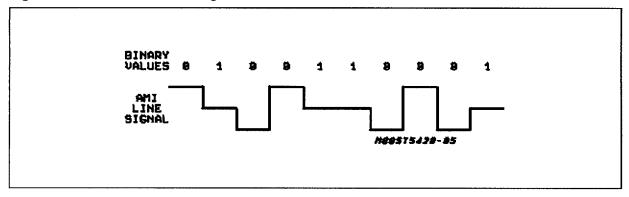

For both directions of transmission, Alternate Mark Inversion (AMI) coding with inverted binary is used, as illustrated in figure 1.

This coding rule requires that a binary ONE is represented by a 0 current high impedance output, whereas a binary ZERO is represented by a positive or negative-going 100% duty cycle pulse. Normally, binary ZEROs alternate in polarity to maintain a d.c. balanced line signal.

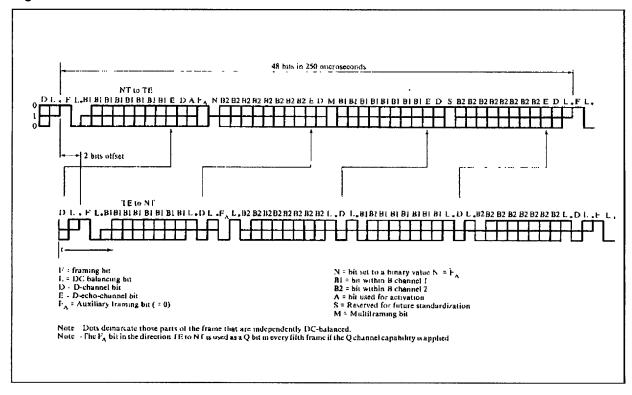

The frame format used in SID-GCI follows CCITT reccommendation in I.430 and illustrated in figure 2. Each complete frame consists of 48 bits, with a line bit rate of 192kbit/s, giving a frame repetition rate of 4kHz. A violation of the AMI coding rule is used to indicate a frame boundary, by using a 0+bit followed by a 0-balance bit to indicate the start of a frame, and by forcing the first binary zero following the balance bit to be of the same polarity as the balance bit.

In the Network Termination (NT) to Terminal Equipment (TE) transmission direction, the frame contains in addition to the 2B+D basic access data, an echo channel, the E bit, which is used to retransmit the D bits that are received from the TE (s), and three extra channels: FA, M and S bit.

In the TE to NT direction, the frame contains in addition to the 2B + D data, an extra channel, the FA bit.

FA, M and S bits are used to set up a Q multiframe channel in the TE or NT direction, and a S1 multiframe channel from NT to TE. These 800bit/s message oriented channels are structured on the base of the United States ANSI standard specification for layer 1 maintenance.

Figure 1: Inverted AMI Line-coding Rule.

Figure 2: Frame Format

#### LINE TRANSMIT SECTION

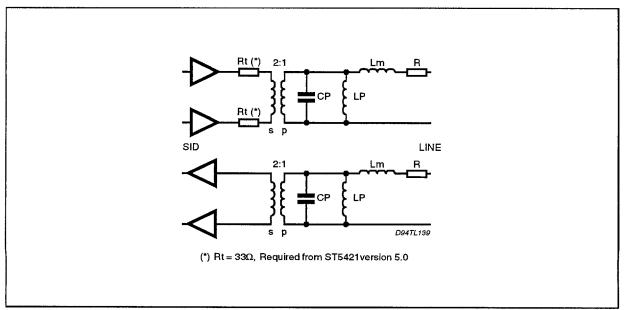

The differential line driver outputs LO+ and LOare designed to drive a suitable transformer with an external termination resistor. A 2:1 transformer, results in a signal amplitude of 750mV on the line which meets the I.430 pulse shape for all the loads specified.

When driving a binary 1 symbol, the output presents a high impedance in accordance with I.430. When driving a 0+ or 0- symbol, the voltage limited current source is turned on.

Short protection is included in the output stage.

Overvoltage protection is required externally.

Depending on TE or NT selected configuration, 192kbit/s data is transmitted on LO+,LO- by means of clocks respectively locked on the farend received bit and frame clocks recovered from the line with two bit delay between transmit and receive frame, or locked with a fixed delay on the Frame Sync signal received from FSa input.

#### LINE RECEIVE SECTION

The receive input signal should be derived via a 1:1 a or 1:2 transformer of the same type used for

6/29

**■ 7929237 0071587 T83 ■**

the transmit direction. At the front end of the receive section is a continuous filter which limits the noise bandwith. To improve the protection of the line interface and to comply with the receive input impedance specification even if power is lost, it is necessary to add 3 external resistors between the receive transformer and the LI+/LI- pins.

To correct pulse attenuation and distorsion caused by the transmission line in point-to-point and extended passive bus applications, an adaptive equalizer enhances the received pulse shape, thereby restoring a "flat" channel response with maximum eye opening over a wide spread of cable attenuation characteristics.

This equalizer is always enabled when either TE or NT mode adaptive sampling is selected, but is disabled for NT short passive bus applications, when NT mode fixed sampling is selected.

An adaptive threshold circuit maximizes Signal to Noise ratio in the eye at the detector for all loop conditions.

A DPLL (Digital Phase-Locked Loop) recovers a low-jitter clock for optimum sampling of the received symbols.

The MCLK input provides the reference clock for the DPLL at 15.36MHz.

When the device is powered down, a Line Signal Detect circuit, able to discriminate a valid line signal from noise, is enabled to detect the presence of incoming data. LSD-output pulls low to wake up the equipment.

#### **GCI INTERFACE**

#### **General Description**

GCI interface is an European standardized interface to connect ISDN dedicated components in the different configurations of equipment as Terminals, Network Terminations, PBX, etc...

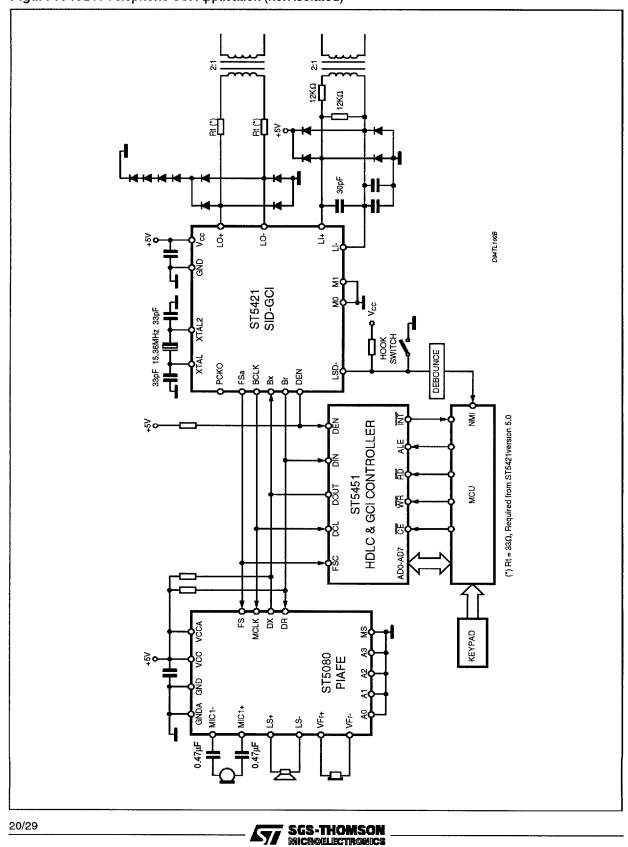

In Terminal Equipments, this interface allows connection between SID-GCI and an associated ST5451 HDLC&GCI Controller used for 16kbit/s D channel processing and SID-GCI control. 64kbit/s B1 and B2 channels are transferred on GCI interface providing direct connection for B channel processing peripherals like Programmable ISDN COMBO ST5080 or extra ST5451 controllers.

In NT2 or PBX line card, GCI interface permits connection of up to 8 SID-GCI onto a common serial multiplexed bus. Each SID-GCI is assigned to one GCI channel selected by hardware configuration.

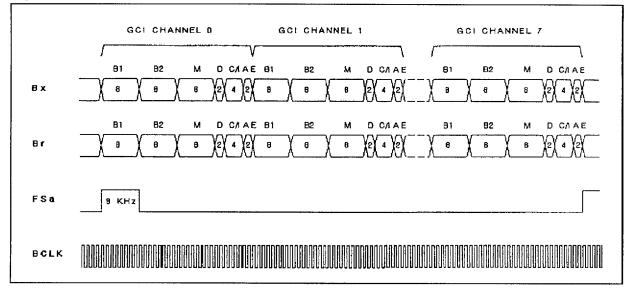

Figure 3 shows the Frame structure of a GCI channel. One GCI channel is structured in four subchannels:

- B1 channel 8 bits

- B2 channel 8 bits

- Monitor (M) channel 8 bits

- SC channel which is structured as follows:

- D channel 2 bits

- C/I channel 4 bits

- A bit associated with M channel

- E bit associated with M channel

B1,B2 and D channels are used to transfer 2B + D basic access data.

M channel is used to read and write multiframe S1 and Q channel messages and to configurate SID-GCI. Protocol for byte exchange on the M channel uses the E and A bits.

C/I (Control/Indicate) channel is used to exchange "real time" primitives between the SID-GCI and the Controller as Activation/Deactivation codes.

#### **Physical Description**

The interface consists of 4 wires:

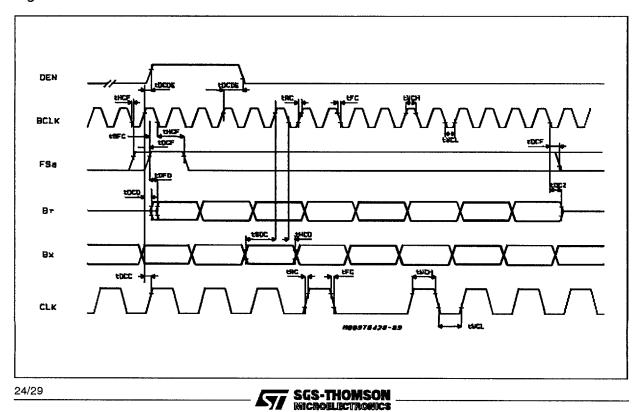

Input Data: Bx Output Data: Br Bit Clock: BCLK

Frame Synchronization: FSa

Data is synchronized by BCLK and FSa signals. The latter insures reinitialization of a time slot counter at each frame beginning. Its rising edge is the reference for the first bit of the first GCI channel. Data is transmitted in both directions at half the BCLK frequency, on the rising edge of BCLK and is sampled 1.5 period after the transmit rising edge. Unused channels are high impedance.

In NT2 or PABX equipments, up to 8 GCI channels (32 bits each) may be multiplexed on Bx and Br links used as a serial bus for several devices. The channel number selection is made by programming pins S0,S1 and S2 according to the following rules:

| S2 | S1 | S0 | Channel Number | Timeslots |

|----|----|----|----------------|-----------|

| 0  | 0  | 0  | 0              | 0 -3      |

| 0  | 0  | 1  | 1              | 4 - 7     |

| 0  | 1  | 0  | 2              | 8 - 11    |

| 0  | 1  | 1  | 3              | 12 - 15   |

| 1  | 0  | 0  | 4              | 16 - 19   |

| 1  | 0  | 1  | 5              | 20 - 23   |

| 1  | 1  | 0  | 6              | 24 - 27   |

| 1  | 1  | 1  | . 7            | 28 - 31   |

SGS-THOMSON MICROELECTRONICS

Figure 3: GCI Interface Structure

BCLK frequency may be any value between 512 and 6176kHz.

In TEM and NT1 configurations, the first GCl channels is automatically selected.

In TEM configuration, due to SID-GCI recovery circuitry, a low jitter should be provided on FSa and BCLK clocks. FSa and BCLK are always in phase. The maximum value of jitter amplitude is a step of 65ns at each GCI frame (125µs). The maximum high frequency jitter amplitude is 130ns pk-pk.

For applications such as the network side of an NT2, eg, a PABX trunk card, TES mode allows the transmission side of SID-GCI to be a slave to the received frame timing while GCI is also in slave mode Elastic buffers which allow any phase relationship between FSa and I.430 frames and a clock resynchroniser circuit absorb jitter and low frequency wander up to at least 18µs pk-pk at frequencies below 10Hz.

## Exchange Protocol on the C/I channel

Exchange of information in the C/I channel runs as follows:

Two devices connected on a GCI channel send each other a permanent four bit command code in the C/I field. The same code is sent at a 8kHz frequency as long as the content of the internal C/I register remains unchanged.

Note: as for GCl definition, in case that a command code has to be executed twice, it is necessary that the device, that is sending the commands, sends, after the first code, a NOP before repeting the command for the second time.

When a change of C/I the command is initiated

that is recognized by SID-GCI if detected in two consecutive frames.

ST5421 will interpret the new code and send the corresponding control instructions on the S line or switch a local function as long as the corresponding action is required.

An information change received from the S line or a local status change of SID-GCI set a new indication code on the C/I channel. The code is sent at least in 2 consecutive frames.

Table 2 gives the C/I codes meaning. C1 bit is first transmitted. Here after for each mode a list of recognized Control and Indicate codes is given.

#### **TEM mode: Control**

**0000 (DR):** Deactivation Request In the Power Up state, DR instruction can be used as a Deactivation Request instruction to force transmission of INFO0 on the S line.

**0001 (PDN):** Power Down Request. PDN instruction forces the device to the Power Down state after that DI (1111) has been sent in two consecutive frames.

0110 (NOP): No operations.

1000 (AR8): Activate Request Class 8.

AR8 instruction combines an Activation Request, which initiates the Activation Sequence on the line, and a request to attempt to access the transmit D channel in the high priority class at the S interface after its complete activation.

After activation of the S interface, Al8 indication is sent by ST5421. D channel access attempt is

8/29

SGS-THOMSON MICROELECTROPICS

Table 2: C/I Channel Coding

| Code        | T    | EM   | LT/  | NT2    | Т    | ES     | N'   | T1   |

|-------------|------|------|------|--------|------|--------|------|------|

| C1 C2 C3 C4 | Ind. | Com. | Ind. | Com.   | Ind. | Com.   | Ind. | Com. |

| 0000        | DP   | DR   | TIM  | PUP/DR | DP   | PUP/DR | TIM  | DR   |

| 0001        | X    | PDN  | X    | PDN    | х    | PDN    | Х    | x    |

| 0010        | X    | Х    | X    | X      | х    | Х      | х    | x    |

| 0011        | ЕОМ  | Х    | X    | х      | х    | х      | Х    | х    |

| 0100        | El   | х    | El   | Х      | EI   | х      | Ei   | Fl2  |

| 0101        | х    | х    | Х    | Х      | х    | x      | х    | X    |

| 0110        | Х    | NOP  | Х    | NOP    | Х    | NOP    | Х    | NOP  |

| 0111        | X    | Х    | х    | X      | Х    | Х      | Х    | х    |

| 1000        | AP   | AR8  | AP   | AR     | AP   | AR     | AP   | AR   |

| 1001        | CON  | AR10 | X    | X      | х    | Х      | Х    | х    |

| 1010        | Х    | ARL  | Х    | ARL    | X    | ARL    | Х    | ARL  |

| 1011        | Х    | Х    | х    | X      | х    | Х      | х    | Х    |

| 1100        | Al8  | Х    | Al   | FI4    | Al   | Х      | Al   | FI4  |

| 1101        | Al10 | Х    | x    | x      | x    | х      | х    | Х    |

| 1110        | AIL  | Х    | AIL  | X      | AIL  | Х      | AIL  | Х    |

| 1111        | DI   | DC   | DI   | DC     | DI   | DC     | DI   | DC   |

(x) codes reserved

automatically processed for each HDLC frame to be transmitted without need for new Control Instruction.

Except for code EOM, any further indication change on C/I as CON or EI deactivates D channel access attempt at the S interface. A new AR8 instruction is needed to restart the procedure.

Note: A new AR8 instruction means that if the controller was already sending AR8, it has to change first the code sent to ie DC (1111) and after change again to AR8.

1001 (AR10): Activate Request Class 10. Same meaning as AR8 command but requesting access to transmit D channel with low priority class.

After activation of the S interface has been completed, Al10 indication is sent by SID-GCI.

1010 (ARL): Activate Request Loopback.

ARL instruction operates a loopback of 2B + D channels from Bx input to Br output. It may be set when the device is either activated, in which case it is transparent (the composite signal is also transmitted to the line), or when it is deactivated in which case it is non transparent.

Any change from ARL to another C/I command clears the loopback.

When the complete loopback is activated, (AIL) code is sent by SID-GCI.

1111 (DC): Deactivation Control.

DC instruction allows ST5421 to enter automat-

ically the Power Down state if the S line is deactivated (DP sent by SID-GCI). When S line is not deactivated, DC has no effect.

#### **TEM mode: Indication**

**0000 (DP):** Deactivation Pending Indication. DP code indicates ST5421 is powered up and that no identified signal has been detected on the S line. DP indication is sent when one of the following events occur:

- Power Up has been completed and no signal is identified on the line,

- after a period of activity, INFO0 is detected on the S line,

- the device being in status F4, F5, F6, F7 or, F8, a DR instruction is issued.

0011 (EOM): End of Message.

EOM indicates that the closing flag of a D channel message has been transmitted on S line indicating successfull completion of a packet sending. EOM is sent continuously until receiving of a new AR8 or AR10 command or line status change.

EOM code sending can be disabled via a Monitor channel instruction EID: (see table 3).

0100 (EI): Error Indication.

El indicates that a frame loss of has been detected on S line; is sent when one of the following events occur:

- being in the F6 or F7 states, detection of a loss of frame, (jump to F8).

SGS-THOMSON MICROELECTRONICS

being in the F7 state, receiving of INFO2, (jump to F6).

1000 (AP): Activation Pending.

AP indicates that INFO2 (or INFO4) frames have been identified on the line.

AP indication is sent when one of the following events occur:

- being in F2 deactivated state, detection of INFO2 or INFO4.

- being in the loss framing state F8, detection of INFO2

1001 (CON): Contention Indication

CON is sent when, during transmission of a packet in the D channel, a received E bit does not match the last transmitted D bit, indicating a lost collision.

D channel access attempt is deactivated at the S interface. A new AR8 or AR10 instruction is needed to restart the procedure.

1100 (Al8): Activation Indication Class 8.

Al8 is sent when, following an AR8 instruction, the S line is completely activated (state F7). The D channel access procedure is set in the high priority class 8 (or 9).

1101 (Al10): Activation Indication Class 10. Al10 is sent when, following an AR10 instruction, the S line is completely activated. The D channel access procedure is set in the low priority class 10 (or 11).

**1110 (AIL):** Activation Indication Loopback. AIL indicates that the complete loopback requested by the instruction ARL is completed.

1111 (DI): Deactivation Indication.

DI is sent at least in two consecutive frames when, being in the S line deactivated state (DP indication sent by SID-GCI) DC control instruction is received on C/I control channel.

After that, SID-GCI is automatically powered down.

#### TES mode: Control.

**0000 (PUP/DR):** Power Up Request/Deactivation Request.

When in Power Down, Power Up instruction powers up the device in the configuration previously set. When in Power Up, PUP/DR can be used as a Deactivation Request instruction to force the transmission of INFO0 on the line.

**0001 (PDN):** Power Down Request. PDN instruction forces the device to the Power Down state.

0110 (NOP): Some as TEM

1000 (AR): Activate Request.

AR instruction initiates the Activation Sequence

on the line. It is recommended that an AR be delayed at least 2ms after the PUP instruction.

**1010 (ARL):** Activate Request Loopback. Identical to TEM mode.

1111 (DC): Deactivation Control.

DC instruction allows ST5421 to enter automatically the Power Down state if the S line is deactivated (DI sent by SID-GCI). When S line is not deactivated, DC has no effect.

#### TES mode: Indication.

**0000 (DP):** Deactivation Pending. DP code indicates ST5421 has been just powered up and no signal has been identified on the line.

**0100 (EI):** Error Indication. Identical to TEM mode.

**1000 (AP) :** Activation Pending. Identical to TEM mode.

1100 (AI): Activation Indication.

All is sent when, following an AR instruction, the S line is completely activated in state F7.

**1110 (AIL) :** Activation Indication Loopback. Identical to TEM mode.

1111 (DI): Deactivation indication.

DI indication is sent when one of the following events occur:

- After a period of activity, INFO0 is detected on the S line,

- the device beeing in status F4, F5, F6, F7 or F8, DR instructions is issued.

#### NT1 mode: Control.

0000 (DR): Deactivation Request.

DR command forces ST5421 through the appropriate deactivation sequence where INFO0 is sent on the line. The device remains in the Power Up state. DI indication is sent.

0100 (FI2): Force Info 2

Being in the activated state G3, FI2 instruction forces the appropriate sequence to send INFO2 on the line. If the S line is not completely activated, FI2 instruction has no effect.

0110 (NOP): Some as TEM

1000 (AR): Activation Request.

Being in the inactive Power Up state, sending INFO0, AR instruction forces SID-GCI through the appropriate sequence to send INFO2 on the line. It is recommended that an AR instruction be delayed at least 2ms after setting the GCI clocks.

**1010 (ARL):** Activate Request Loopback. Identical to TEM mode.

1100 (FI4): Force Info 4.

An activation Request being in progress, FI4 instruction allows SID-GCI through the appropriate sequence to send INFO4 on the line.

**1111 (DC):** Deactivation Control. DC instruction has no effect on SID-GCI.

#### NT1 mode: Indication.

0000 (TIM): Timing Requested.

Being in Power down state, the LSD- output is pulled low to indicate that the far-end is attempting to activate the S interface. The device requests GCI clock signals. Receiving of GCI clocks powers up the SID-GCI, LSD- is freed, and TIM code is sent on the C/I channel.

0100 (EI): Error Indication.

El code índicates that a loss of frame has been detected on the S line, ST5421 being previously activated.

1000 (AP): Activation Pending.

AP code indicates that INFO1 frames have been identified of the line. The device is waiting for an activate request to send INFO2.

1100 (AI): Activation Indication.

Al code indicates that the S line is activated. That means it is receiving INFO3.

1111 (DI): Deactivation Indication.

DI code indicates S line is completely deactivated: the device can be powered down switching off GCI clocks.

**1110 (AIL) :** Activation Indication Loopback. Identical to TEM mode.

#### NT2 mode: Control.

0000 (PUP/DR) Power Up Request/Deactiva-

tion Request.

When in Power Down state, PUP code powers up the device in the NT2 configuration previously selected. When in Power Up state DR code forces the appropriate deactivation sequence where INFO0 is sent on the line. SID-GCI remains in Power Up state.

**0001 (PDN):** Power Down Request. Identical to TES mode.

0110 (NOP): Some as TEM

1000 (AR): Activation Request.

After à PÚP instruction, AR forces the appropriate sequence to send INFO2 on the line. It is

recommended that AR instruction is sent after receiving TIM indication..

**1010 (ARL):** Activation Request Loopback. Identical to TEM mode.

1100 (FI4): Force Info 4.

An Activation Request being in progress, FI4 instruction puts ST5421 through the appropriate sequence to send INFO4 on the line.

1111 (DC): Deactivation Control.

The DC instruction allows to enter the power down state if the S line is deactivated.

DC control has no effect if SID-GCI not sending DI indication.

#### NT2 mode: Indication.

0000 (TIM): Timing Requested.

Being in Power down state, LSD- output is pulled low to indicate that far-end is attempting to activate the interface. SID-GCI requests GCI clocks followed by a PUP instruction. After receiving, LSD- is freed and TIM is sent on C/I channel.

**0100 (EI):** Error Indication. Identical to NT1 mode.

**1000 (AP):** Activation Pending. Identical to NT1 mode.

**1101 (AI):** Activation Indication. Identical to NT1 mode.

**1110 (AIL):** Activation Indication Loopback. Identical to TEM mode.

1111 (DI): Deactivation Indication.

The DI code indicates that the S line is completely deactivated.

#### EXCHANGE PROTOCOL ON M CHANNEL

Protocol allows a bidirectional transfer of bytes between SID-GCl and a Controller (for example ST5451) with an acknowledgement at each received byte.

### Write cycle.

The Controller sends to ST5421 control instruction(s) coded on a single byte. It is possible but optional to write several control instructions in a single message. Control instruction bytes are structured as defined in Table 3.

#### Read cycle.

When a new validated S1 or Q message is received from the line, the device send a single byte message as defined in table 4. If a new message is received from the S line before the previous is acknowledged by the controller end, this new message is lost.

SGS-THOMSON

### Exchange protocol.

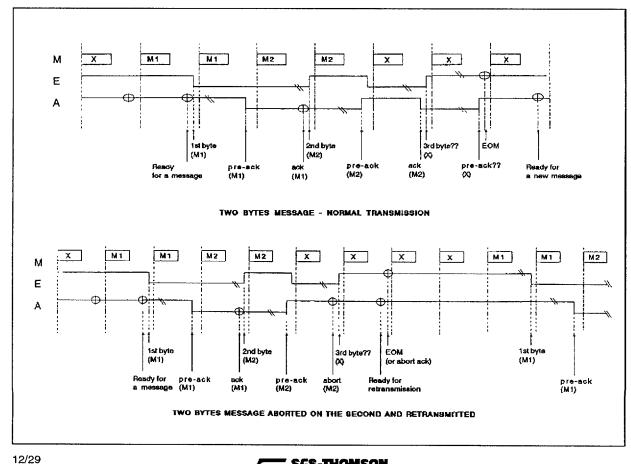

The exchange protocol is identical for both directions.

The sender uses E bit to indicate that it is sending a M byte while the receiver uses A bit to acknowledge the received byte.

When no message is transferred, E bit and A bit are forced to inactive state (i.e. high impedance).

A transmission is initialized by the sender setting E bit in active state and sending the first byte on M channel in the same frame. Transmission of a message is allowed only if A bit received has been detected inactive in the last two frames.

When the receiver is ready, it validates the received byte internally when it has been detected identical in two consecutive frames. Then, the receiver set first A bit from inactive to active state; it is the pre-acknowledgement, and maintain A bit active at least in the following frame, it is the acknowledgement.

If validation is not possible, the two last bytes received not identical, the receiver abort the message by setting A bit active for one frame only.

A second M byte may be transmitted by the

sender turning E bit from active to inactive state and sending the byte in the same frame. The E bit is set inactive for one frame only. If it remains inactive more than one frame, it is an end of message. The second byte may be transmitted only after receiving the pre-acknowledgement of the previous byte (see timing diagram).

The receiver validates the current received byte as for the first one and then set A bit in the next two frames first from active to inactive state (preacknowledgement) and from inactive to active (acknowledgement). If the receiver cannot validate (the two bytes received are not identical) it pre-acknowledges normally but let A bit in the inactive state in the next frame which indicates an abort request.

If a message is aborted, ST5421 sends again the complete message until receiving acknowledgement.

A received message is acknowledged or aborted without flow Control.

Figure 4 gives the timing of a write cycle. The most significant bit of a Monitor byte is sent first of the M channel. E & A bits are active low and inactive state on Br is high impedance.

Figure 4: Monitor messaging

12/29

SGS-THOMSON MICROELECTRONICS

**--** 7929237 0071593 287 **--**

Table 3: Monitor Channel Instruction

| NTM Ode Adaptive Sampling (*)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Functions       | Mnemonic |     |          |   | Bit N | umber |    |    |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|-----|----------|---|-------|-------|----|----|-----|

| NT Mode Adaptive Sampling (*)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |          | 7   | 6        | 5 | 4     | 3     | 2  | 1  | 0   |

| NTF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Device Mode:    |          |     |          |   |       |       |    |    |     |

| TE Slave Mode (slave-slave)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |          | 0   | 0        | 0 | 0     | 0     | 1  | 0  | 0   |

| Monitoring Mode Activation   MMA   0   0   0   1   1   1   1   1   1   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |          | 0   | 0        | 0 | 0     | 0     | 1  | 0  | 1   |

| TEM   Section   TEM   Section   TEM   TE |                 |          |     | -        | - | -     | _     | 1  | 1  | _   |

| B Channel Configuration: B Channel Mapped Direct (*) B Channel Exchanged BEX 0 0 0 0 1 1 0 0 B Channel Exchanged BEX 0 0 0 0 1 0 1 1 0 1 B1 Channel Enabled (*) B1E 0 0 0 1 0 1 0 1 0 1 B2 Channel Disabled B1D 0 0 0 1 0 1 0 1 1 0 1 B2 Channel Disabled B2D 0 0 0 1 0 1 1 1 0 1 B2 Channel Disabled B2D 0 0 0 1 0 1 1 1 1 0 B2 Channel Disabled B2D 0 0 0 1 0 1 1 1 1 1  End of Messages Indication: EOM Indication Enabled (*) EIE 0 0 0 0 1 0 0 0 1 1 1 1 1 END Multiframe Processing: Multiframe Disabled MID 0 0 0 1 0 0 0 1 1 0 0 0 0 Multiframe Enabled MIE 0 0 0 1 0 0 1 1 0 0 1 1 1 Enable Three Time Checking DIS3X 0 0 1 0 1 0 0 0 1 Enable Three Time Checking (*) EN3X 0 0 1 0 1 0 0 0 0 Write Multiframe Message MFT 0 0 1 1 M1 M2 M3 M4  Loopback Test Mode: Clear All loopbacks (*) CAL 0 0 0 1 1 0 0 0 1 Loopback B2 on Line Enabled LB1E 0 0 0 1 1 0 0 0 1 LOOpback 2B+D Enabled (1) LBS 0 0 0 1 1 0 0 1 1 0 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |          |     |          | _ | -     |       | 1  | 1  | •   |

| B Channel Mapped Direct (*)   BDIR   0 0 0 0 0 1 1 0 0 0     B Channel Exchanged   BEX   0 0 0 0 0 1 1 1 0 0 1     B1 Channel Enabled (*)   B1E   0 0 0 0 1 0 1 0 1 0 0     B1 Channel Disabled   B1D   0 0 0 0 1 0 1 0 1 0 1 0 1     B2 Channel Enabled (*)   B2E   0 0 0 0 1 0 1 0 1 1 0 1 0     B2 Channel Disabled   B2D   0 0 0 0 1 0 1 1 1 1 1     End of Messages Indication:   EOM Indication Enabled (*)   EIE   0 0 0 0 1 0 0 0 0 1     EOM Indication Disabled   EID   0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I E Master Mode | IEM      | 0   | 0        | 0 | 0     | 0     | 1  | 1  | 11  |

| B Channel Exchanged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |          |     |          |   |       |       |    |    |     |

| B1 Channel Enabled (*)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |          | _   |          |   |       | 1     | 1  | 0  | 0   |

| B1 Channel Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |          |     | _        | _ | 0     | 1     | 1  | _  |     |

| B2 Channel Enabled (*)   B2E   0 0 0 0 1 0 1 1 0 1 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 | 1        | 1 - | -        | - | 1     | -     | 1  | •  | -   |

| B2 Channel Disabled   B2D   0   0   0   1   0   1   1   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |          |     | -        | - | 1     | -     | 1  | 0  |     |

| End of Messages Indication:         EIE         0         0         0         1         0         0         0         1           EOM Indication Enabled (*)         EID         0         0         0         1         0         0         0         0           Multiframe Processing:         Multiframe Processing:           Multiframe Disabled (*)         MID         0         0         0         1         0         0         1         1           Multiframe Disabled (*)         MIE         0         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         0         0         1         0         0         0         0         0         0         0         0         0         0 <td></td> <td></td> <td>, -</td> <td>-</td> <td>-</td> <td>]</td> <td>-</td> <td>1</td> <td>1</td> <td>-</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |          | , - | -        | - | ]     | -     | 1  | 1  | -   |

| EOM Indication Enabled (*)         EIE         0         0         0         1         0         0         0         1           EOM Indication Disabled         EID         0         0         0         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         1         0         0         1         1         0         0         1         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         0         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 | B2D      | 0   | <u> </u> | U | 1     |       | ı  | 1  | 1   |

| EOM Indication Disabled         EID         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         1         1         0         0         1         1         0         0         1         1         0         0         1         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         0         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <td></td> <td></td> <td></td> <td>_</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |          |     | _        |   |       |       |    |    |     |

| Multiframe Processing:         MID         0         0         0         1         0         0         1         1           Multiframe Disabled (*)         MID         0         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         1         0         0         0         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |          |     |          |   | 1     |       |    |    |     |

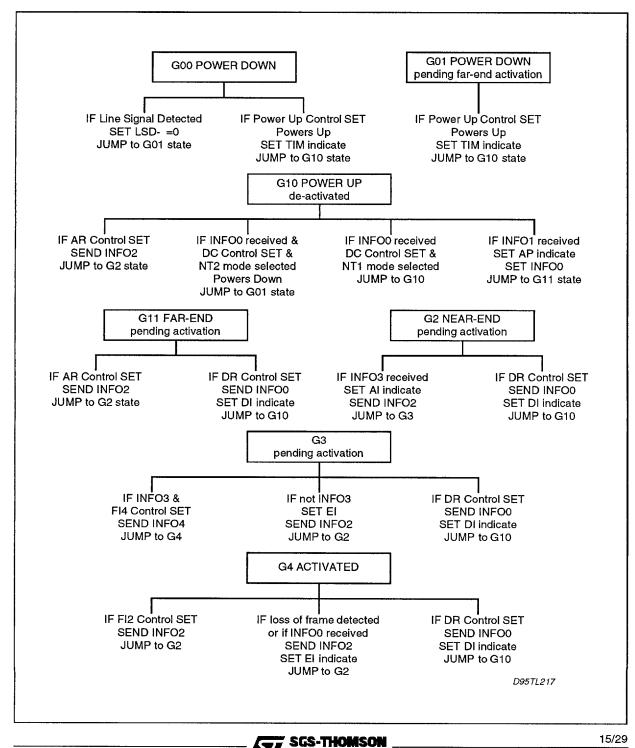

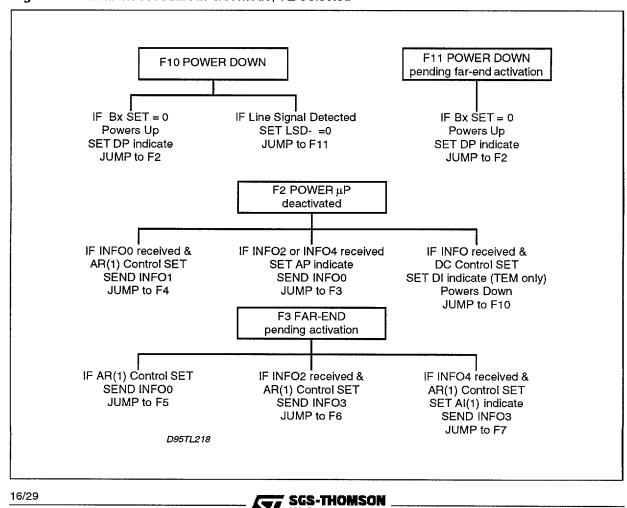

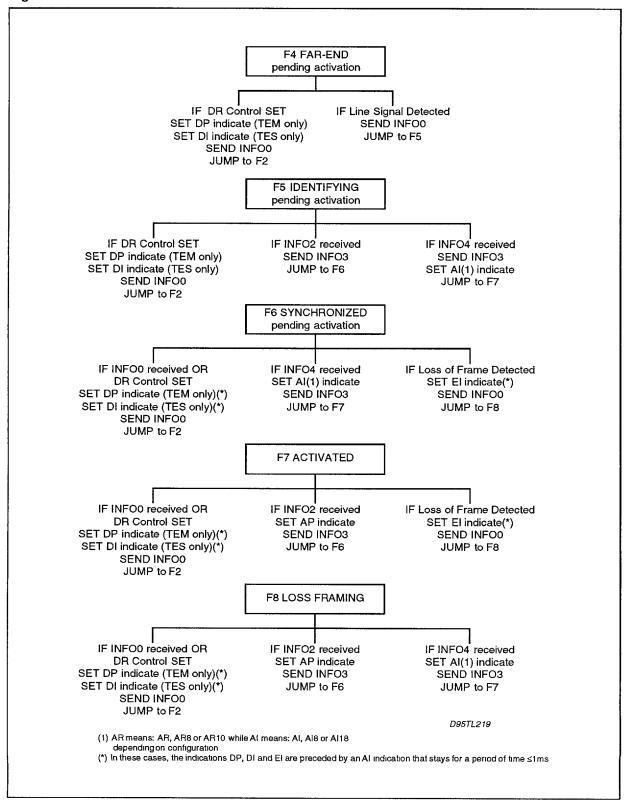

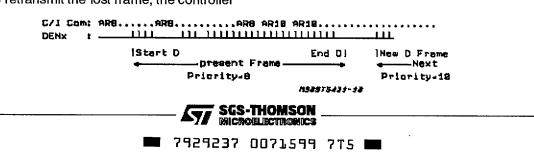

| Multiframe Disabled (*)         MID         0         0         1         0         0         1         1           Multiframe Enabled         MIE         0         0         0         1         0         0         1         0           Disable Three Time Checking         DIS3X         0         0         1         0         0         1           Enable Three Time Checking (*)         EN3X         0         0         1         0         0         0           Write Multiframe Message         MFT         0         0         1         1         MID         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 | FID      | 0   | 0        | U | 1     | 0     | 0  | 0  | 0   |