9984043 ZILOG INC

03E 08155

**Z8030 Military** Z8000<sup>®</sup> Z-SCC Serial **Communications Controller**

## **Z110**0

**Military Electrical** Specification

July 1985

#### **FEATURES**

- Two independent, 0 to 1.5M bit/second, full-duplex channels, each with a separate crystal oscillator, baud rate generator, and Digital Phase-Locked Loop for clock recovery.

- Multi-protocol operation under program control; programmable for NRZ, NRZI, or FM data encoding.

- Asynchronous mode with five to eight bits and one, one and one-half, or two stop bits per character; programmable clock factor; break detection and generation; parity, overrun, and framing error detection.

- Synchronous mode with internal or external character

- synchronization on one or two synchronous characters and CRC generation and checking with CRC-16 or CRC-CCITT preset to either 1s or 0s.

- SDLC/HDLC mode with comprehensive frame-level control, automatic zero insertion and deletion, I-field residue handling, abort generation and detection, CRC generation and checking, and SDLC Loop mode operation.

- Local Loopback and Auto Echo modes.

- 1.544M bit/second T1 digital trunk compatible version available.

#### **GENERAL DESCRIPTION**

The Z8030 Z-SCC Serial Communications Controller is a dual-channel, multi-protocol data communications peripheral designed for use with the Zilog Z-BUS. The Z-SCC functions as a serial-to-parallel, parallel-to-serial converter/controller. The Z-SCC can be software-configured to satisfy a wide variety of serial communications applications. The device contains a variety of new, sophisticated internal functions including on-chip baud rate generators, Digital Phase-Locked Loops, and crystal oscillators that dramatically reduce the need for external

The Z-SCC handles asynchronous formats, synchronous byte-oriented protocols such as IBM Bisync, and Synchronous bit-oriented protocols such as HDLC and IBM

SDLC. This versatile device supports virtually any serial data transfer application (cassette, diskette, tape drives, etc.).

The device can generate and check CRC codes in any Synchronous mode and can be programmed to check data integrity in various modes. The Z-SCC also has facilities for modern controls in both channels. In applications where these controls are not needed, the modem controls can be used for general-purpose I/O.

The Z-BUS daisy-chain interrupt hierarchy is also supported—as is standard for Zilog peripheral components.

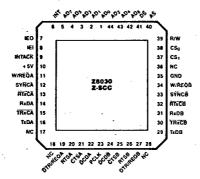

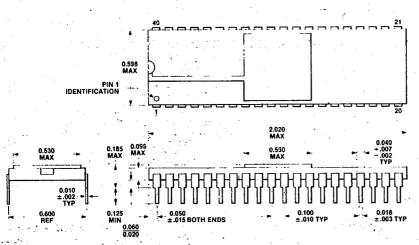

The Z8030 Z-SCC is packaged in a 40-pin ceramic DIP and 44-pin chip carrier and uses a single + 5V power supply.

03E 08156

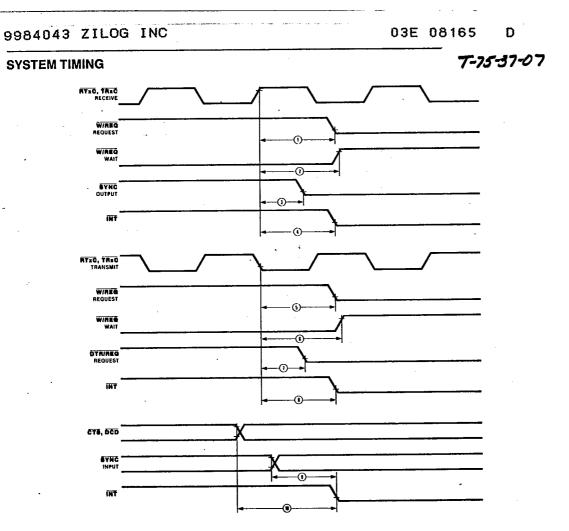

#### **TIMING**

T-75-37-07

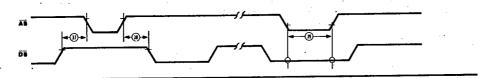

The Z-SCC generates internal control signals from  $\overline{AS}$  and  $\overline{DS}$  that are related to PCLK. Since PCLK has no phase relationship with  $\overline{AS}$  and  $\overline{DS}$ , the circuitry generating these internal control signals must provide time for metastable conditions to disappear. This gives rise to a recovery time related to PCLK. The recovery time applies only between bus transactions involving the Z-SCC. The recovery time required for proper operation is specified from the rising edge of  $\overline{DS}$  in the first transaction involving the Z-SCC to the falling edge of  $\overline{DS}$  in the second transaction

involving the Z-SCC. This time must be at least 6 PCLK cycles plus 200 ns.

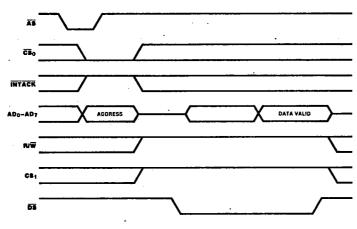

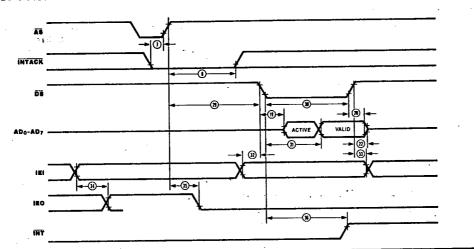

**Read Cycle Timing.** Figure 1 illustrates read cycle timing. The address on AD<sub>0</sub>-AD<sub>7</sub> and the state of  $\overline{CS}_0$  and  $\overline{INTACK}$  are latched by the rising edge of  $\overline{AS}$ .  $R/\overline{W}$  must be High to indicate a Read cycle. CS<sub>1</sub> must also be High for the Read cycle to occur. The data bus drivers in the Z-SCC are then enabled while  $\overline{DS}$  is Low.

Figure 1. Read Cycle Timing

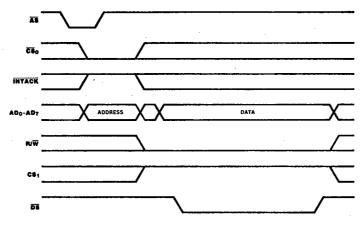

Write Cycle Timing. Figure 2 illustrates Write cycle timing. The address on AD<sub>0</sub>-AD<sub>7</sub> and the state of  $\overline{CS}_0$  and  $\overline{INTACK}$  are latched by the rising edge of  $\overline{AS}$ .  $R/\overline{W}$  must be Low to

indicate a Write cycle. CS<sub>1</sub> must be High for the Write cycle to occur. DS Low strobes the data into the Z-SCC.

Figure 2. Write Cycle Timing

03E 08157 D

T-75-37-07

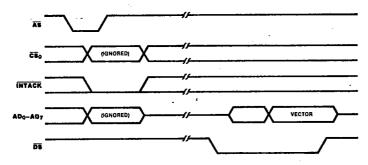

Interrupt Acknowledge Cycle Timing. Figure 3 illustrates Interrupt Acknowledge cycle timing. The address on AD<sub>0</sub>-AD<sub>7</sub> and the state of  $\overline{\text{CS}}_0$  and  $\overline{\text{INTACK}}$  are latched by the rising edge of  $\overline{\text{AS}}$ . However, if  $\overline{\text{INTACK}}$  is Low, the address and  $\overline{\text{CS}}_0$  are ignored. The state of the  $\overline{\text{RW}}$  and  $\overline{\text{CS}}_1$  are also ignored for the duration of the Interrupt Acknowledge cycle. Between the rising edge of  $\overline{\text{AS}}$  and the

falling edge of  $\overline{DS}$ , the internal and external IEI/IEO daisy chains settle. If there is an interrupt pending in the Z-SCC and IEI is High when  $\overline{DS}$  falls, the Acknowledge cycle was intended for the Z-SCC. In this case, the Z-SCC may be programmed to respond to  $\overline{DS}$  Low by placing its interrupt vector on AD<sub>0</sub>-AD<sub>7</sub>. It then sets the appropriate Interrupt Under-Service latch internally.

Figure 3. Interrupt Acknowledge Cycle Timing

03E 08158 [

#### T-75-37-07

#### **ABSOLUTE MAXIMUM RATINGS**

Guaranteed by characterization/design.

Voltages on all inputs and outputs

with respect to ground. ..... - 0.3V to +7.0V

Operating Case Temperature .... - 55°C to + 125°C

Storage Temperature Range .... - 65°C to + 150°C

Absolute Maximum Power Dissipation ..... 2.0W

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### STANDARD TEST CONDITIONS

The DC Characteristics and Capacitance sections listed below apply for the following standard test conditions, unless otherwise noted.

Military Operating Temperature Range (T<sub>C</sub>) -55°C to +125°C

Standard Military Test Condition +  $4.5V \le V_{CC} \le + 5.5V$

All voltages are referenced to GND (0V). Positive current flows into the referenced pin.

All ac parameters assume a load capacitance of 50 pf max.

Standard Test Load

Open-Drain Test Load

#### **DC CHARACTERISTICS**

| Symbol          | Parameter                      | Min    | Max                                | Unit | Condition                       |

|-----------------|--------------------------------|--------|------------------------------------|------|---------------------------------|

| VIH             | Input High Voltage             | + 2.2a | V <sub>CC</sub> + 0.3 <sup>c</sup> | V    |                                 |

| V <sub>IL</sub> | Input Low Voltage              | -0.3c  | +0.8a                              | ٧    |                                 |

| VoH             | Output High Voltage            | +2.4c  | ~ .                                | V    | $I_{OH} = -250 \mu A$           |

| V <sub>OL</sub> | Output Low Voltage             |        | +0.4c                              | V    | $I_{OL} = 2.0  \text{mA}$       |

| l <sub>IL</sub> | Input Leakage Current          |        | ± 10a                              | μΑ   | $+0.4 \le V_{ N} \le +2.4V$     |

| OL              | Output Leakage                 |        | ± 10a                              | μΑ   | +0.4 € V <sub>OUT</sub> € +2.4V |

| lcc             | V <sub>CC</sub> Supply Current |        | +350a                              | - mA |                                 |

$V_{CC}$  = 5V ± 5% unless otherwise specified, over specified temperature range.

#### **CAPACITANCE**

| Symbol           | Parameter                 | Max             | Unit |

|------------------|---------------------------|-----------------|------|

| C <sub>IN</sub>  | Input Capacitance         | 10°             | pf   |

| C <sub>OUT</sub> | Output Capacitance        | 15 <sup>c</sup> | pf   |

| CI/O             | Bidirectional Capacitance | 20 <sup>c</sup> | pf   |

T<sub>A</sub> = 25°C, f = 1 MHz

Unmeasured pins returned to ground.

Parameter Test Status:

- a Tested

- b Guaranteed

- <sup>C</sup> Guaranteed by characterization/design

8085-006, 001

03E 08159

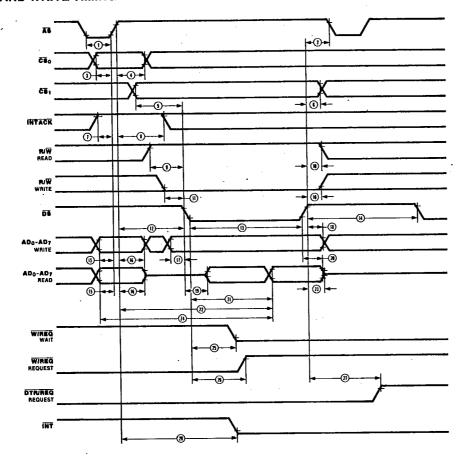

#### **READ AND WRITE TIMING**

T-75-37-07

2016-010

03E 08160

**AC CHARACTERISTICS**

Read and Write Timing

| nation of the second of the se |           | 4 M                                | Hz              | 6 M              | Hz                 |      |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------|-----------------|------------------|--------------------|------|-------|

| Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Symbol    | Parameter                          | Min -           | Max              | Min                | Max  | Notes |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TwAS      | AS Low Width                       | 70ª             |                  | 50a                |      |       |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TdDS(AS)  | DS f to AS ↓ Delay                 | 50b             |                  | 25b                |      |       |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TsCS0(AS) | CS <sub>0</sub> to AS ↑ Setup Time | 0р .            |                  | <b>0</b> p         |      | 1     |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ThCS0(AS) | CS <sub>0</sub> to AS † Hold Time  | 60a             |                  | 40a                |      | 1     |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TsCS1(DS) | CS <sub>1</sub> to DS I Setup Time | 100b            |                  | 80a                |      | 1     |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ThCS1(DS) | CS <sub>1</sub> to DS f Hold Time  | 55a             |                  | 40b                | •    | 1     |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TsIA(AS)  | INTACK to AS † Setup Time          | <b>0</b> p      |                  | 0р                 |      |       |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ThIA(AS)  | INTACK to AS † Hold Time           | 250b            |                  | 250b               |      |       |

| 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TsRWR(DS) | R/W (Read) to DS ↓ Setup Time      | 100a            |                  | 80a                |      |       |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ThRW(DS)  | R/W to DS ↑ Hold Time              | 55b             | •                | 40b                |      |       |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TsRWW(DS) | R/W (Write) to DS ↓ Setup Time     | 0р              |                  | 0р                 |      |       |

| 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TdAS(DS)  | AS to DS ↓ Delay                   | 85 <sup>b</sup> |                  | 50b                |      |       |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TwDSI     | DS Low Width .                     | 390b            |                  | 250b               |      |       |

| 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TrC .     | Valid Access Recovery Time         | 6TcPC           |                  | 6TcPC              |      | 2     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                    | +200b           |                  | + 130 <sup>b</sup> |      |       |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TsA(AS)   | Address to AS † Setup Time         | 30a             |                  | 10 <sup>a</sup>    |      | 1     |

| 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ThA(AS)   | Address to AS + Hold Time          | 50a             |                  | 30a                |      | 1     |

| 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TsDW(DS)  | Write Data to DSI Setup Time       | 30a             |                  | 20a                |      |       |

| 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ThDW(DS)  | Write Data to DS † Hold Time       | 30p             |                  | 20 <sup>b</sup>    |      |       |

| . 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TdDS(DA)  | DS I to Data Active Delay          | <b>0</b> p      |                  | 0р                 |      |       |

| 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TdDSr(DR) | DS to Read Data Not Valid Delay    | <b>0</b> p      |                  | 0a                 |      |       |

| 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TdDSf(DR) | DS I to Read Data Valid Delay      |                 | 250 <sup>b</sup> |                    | 180b |       |

| 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TdAS(DR)  | AS to Read Data Valid Delay        |                 | 520 <sup>b</sup> |                    | 335b |       |

#### NOTES:

#### Parameter Test Status:

<sup>1.</sup> Parameter does not apply to Interrupt Acknowledge transactions.

2. Parameter applies only between transactions involving the SCC.

†Units in nanoseconds (ns).

a Tested

b Guaranteed

c Guaranteed by characterization/design.

03E 08161

## INTERRUPT ACKNOWLEDGE TIMING

#### **RESET TIMING**

#### **CYCLE TIMING**

03E 08162

7-75-37-07

#### **AC CHARACTERISTICS**

Read and Write Timing (Continued)

|        | •          |                                 |                  | 4 MHz            |                  | 6 MHz            |        |

|--------|------------|---------------------------------|------------------|------------------|------------------|------------------|--------|

| Number | Symbol     | Parameter                       | Min              | Max              | Min              | Max              | Notes* |

| 23     | TdDS(DRz)  | DS † to Read Data Float Delay   |                  | 70b              |                  | 45b              | 3      |

| 24     | TdA(DR)    | Address Required Valid to Read  | ٠                |                  |                  |                  |        |

|        | •          | Data Valid Delay                |                  | 570b             |                  | 420a             |        |

| 25     | TdDS(W)    | DS I to Wait Valid Delay        |                  | 240 <sup>b</sup> |                  | 200b             | 4      |

| 26     | TdDSf(REQ) | DS ↓ to W/REQ Not Valid Delay   |                  | 240b             |                  | 200b             |        |

| 27     | TdDSr(REQ) | DS t to DTR/REQ Not Valid Delay |                  | 5TcPC            |                  | 5TcPC            |        |

|        |            |                                 |                  | +300b            |                  | +500b            |        |

| 28     | TdAS(INT)  | AS t to INT Valid Delay         | 1.               | 500b             |                  | 500b             | 4      |

| 29     | TdAS(DSA)  | AS to DS ↓ (Acknowledge) Delay  | 250b             |                  | 250b             |                  | 5      |

| 30     | Twdsa      | DS (Acknowledge) Low Width      | 390b             |                  | 250b             |                  |        |

| 31     | TdDSA(DR)  | DS I (Acknowledge) to Read Data |                  |                  |                  |                  |        |

|        |            | Valid Delay                     |                  | 250 <sup>b</sup> |                  | 180 <sup>b</sup> |        |

| 32     | TsIEI(DSA) | IEI to DS ↓ (Acknowledge) Setup |                  |                  | •                |                  |        |

|        |            | Time                            | 120 <sup>b</sup> |                  | 100b             | •                |        |

| 33     | ThiEi(DSA) | IEI to DS † (Acknowledge) Hold  |                  |                  |                  |                  |        |

|        |            | Time                            | Оp               |                  | 0р               |                  |        |

| 34     | TdIEI(IEO) | IEI to IEO Delay                |                  | 120 <sup>b</sup> |                  | 100b             |        |

| 35     | TdAS(IEO)  | AS to IEO Delay                 |                  | 250b             |                  | 250b             | 6      |

| 36     | TdDSA(INT) | DS ↓ (Acknowledge) to INT       |                  |                  |                  | •                |        |

|        |            | Inactive Delay                  |                  | 500b             |                  | 500b             | 4      |

| 37     | TdDS(ASQ)  | DS † to AS ↓ Delay for No Reset | 30p              | _                | 15 <sup>b</sup>  |                  |        |

| 38     | TdASQ(DS)  | AS to DS ↓ Delay for No Reset   | 30p              |                  | 30p              |                  | 1      |

| 39     | TWRES      | AS and DS Coincident Low for    |                  | •                |                  |                  |        |

|        |            | Reset                           | 250b             |                  | 250 <sup>b</sup> |                  | 7      |

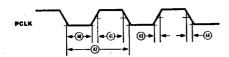

| 40     | TwPCI      | PCLK Low Width                  | 105 <sup>b</sup> | 2000b            | 70a              | 1000b            |        |

| 41     | TwPCh      | PCLK High Width                 | 105 <sup>b</sup> | 2000b            | 70a              | 1000b            |        |

| 42     | TcPC       | PCLK Cycle Time                 | 250a             | 4000b            | 165a             | 2000b            |        |

| 43     | TiPC       | PCLK Rise Time                  |                  | 20 <sup>b</sup>  |                  | 15 <sup>b</sup>  |        |

| 44     | TfPC       | PCLK Fall Time                  |                  | 20 <sup>b</sup>  |                  | 10a              |        |

- 3. Float delay is defined as the time required for a ±0.5V change in the output with a maximum DC toad and minimum AC load.

- 4. Open-drain output, measured with open-drain test load.

- Parameter is system dependent. For any Z-SCC in the daisy chain, TdAS(DSA) must be greater than the sum of TdAS(IEO) for the highest priority device in the daisy chain, TsIEI(DSA) for the Z-SCC, and TdIEIf(IEO) for each device separating them in the daisy chain.

Parameter applies only to a Z-SCC pulling INT Low at the beginning of the Interrupt Acknowledge transaction.

- 7. Internal circuitry allows for the reset provided by the Z8 to be recognized as a reset by the Z-SCC. \*All timing references assume 2.0V for a logic "1" and 0.8V for a logic "0." †Units in nanoseconds (ns).

#### Parameter Test Status:

- a Tested b Guaranteed

- C Guaranteed by characterization/design.

2016-014

03E 08164

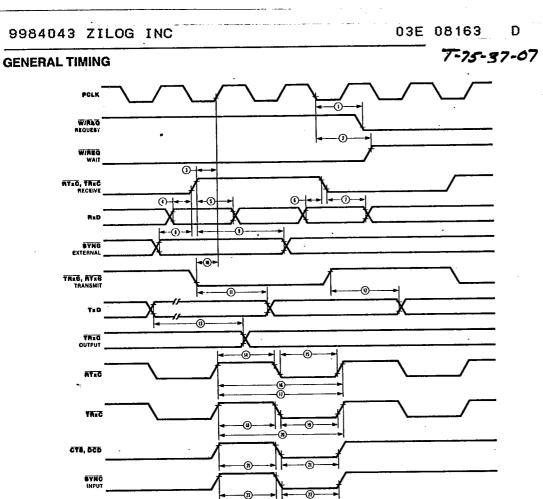

#### **AC CHARACTERISTICS**

**General Timing**

|        | ••          |                                     |                  | MHz    | 6 !              | MHz    |        |

|--------|-------------|-------------------------------------|------------------|--------|------------------|--------|--------|

| Number | Symbol      | Parameter                           | Min              | Max    | Min              | Max    | Notes† |

| 1      | TdPC(REQ)   | PCLK I to W/REQ Valid               |                  | 250b   |                  | 250b   |        |

| 2      | TdPC(W)     | PCLK    to Wait Inactive Delay      |                  | 350b   |                  | 350b   |        |

| 3      | TsRXC(PC)   | RxC t to PCLK t Setup Time          |                  |        |                  |        |        |

|        | 5           | (PCLK ÷ 4 case only)                | 80a              | TwPCLb | 70a              | TwPCLb | 1,4    |

| 4      | TsRXD(RXCr) | RxD to RxC t Setup Time (X1 Mode)   | 0р               |        | <b>0</b> p       |        | 1      |

| 5      | ThRXD(RXCr) | RxD to RxC † Hold Time (X1 Mode)    | 150 <sup>b</sup> |        | 150a             |        | 1      |

| 6      | TsRXD(RXCf) | RxD to RxC ↓ Setup Time (X1 Mode)   | 0р               |        | 0р               |        | 1,5    |

| 7      | ThRXD(RXCf) | RxD to RxC I Hold Time (X1 Mode)    | 150 <sup>b</sup> |        | 150a             |        | 1,5    |

| 8      | TsSY(RXC)   | SYNC to RxC t Setup Time            | -200b            |        | -200b            |        | 1      |

| 9      | ThSY(RXC)   | SYNC to RxC f Hold Time             | 3TcPC            |        | 3TcPC            | -      |        |

|        |             | e i green in                        | +200b            |        | +200b            |        | 1      |

| 10     | TsTXC(PC)   | TxC I to PCLK t Setup Time          | . 0a             |        | 0a               | •      | 2,4    |

| 11     | TdTXCf(TXD) | TxC I to TxD Delay (X1 Mode)        |                  | 300a   |                  | 230a   | 2      |

| 12     | TdTXCr(TXD) | TxC t to TxD Delay (X1 Mode)        |                  | 300a   |                  | 230a   | 2,5    |

| 13     | TdTXD(TRX)  | TxD to TRxC Delay (Send Clock Echo) |                  | 200b   |                  | 200b   |        |

| 14     | TwRTXh      | RTxC High Width                     | 180 <sup>b</sup> |        | 180 <sup>b</sup> |        | 6      |

| 15     | TwRTXI      | RTxC Low Width                      | 180 <sup>b</sup> |        | 180b             |        | 6      |

| 16     | TcRTX       | RTxC Cycle Time                     | 400b             |        | 400b             |        | 6      |

| 17     | TcRTXX      | Crystal Oscillator Period           | 250b             | 1000b  | 250b             | 1000b  | 3      |

| 18     | TwTRXh      | TRxC High Width                     | 180 <sup>b</sup> |        | 180b             |        | 6      |

| 19     | TWTRXI      | TRxC Low Width                      | 180 <sup>b</sup> |        | 180 <sup>b</sup> |        | 6      |

| 20     | TcTRX       | TRXC Cycle Time                     | 400b             |        | 400b             | •      | 6      |

| 21     | TWEXT       | DCD or CTS Pulse Width              | 200b             |        | 200b             |        |        |

| 22     | TwSY        | SYNC Pulse Width                    | 200b             |        | 200b             |        |        |

#### NOTES:

- NOTES:

1. RxC is RtxC or TRxC, whichever is supplying the receive clock.

2. TxC is TRxC or RtxC, whichever is supplying the transmit clock.

3. Both RtxC and SYNC have 30 pf capacitors to the ground connected to them.

4. Parameter applies only if the data rate is one-fourth the PCLK rate. In all other cases, no phase relationship between RxC and PCLK or TxC and PCLK is required.

5. Parameter applies only to FM encoding/decoding.

6. Parameter applies only for transmitter and receiver; DPLL and baud rate generator timing requirements are identical to chip PCLK requirements. †Units in nanoseconds (ns).

#### Parameter Test Status:

- a Tested

- b Guaranteed

- c Guaranteed by characterization/design.

2016-015

03E 08166

#### **AC CHARACTERISTICS**

System Timing

|           |            |                                          |            | fHz             | 6 N        | 1Hz             |       |

|-----------|------------|------------------------------------------|------------|-----------------|------------|-----------------|-------|

| Number Sy | Symbol     | Parameter                                | Min        | Max             | Min        | Max             | Notes |

| 1         | TdRXC(REQ) | RxC t to W/REQ Valid Delay               | 8p         | 12b             | gb         | 12b             | 2,4   |

| 2         | TdRXC(W)   | RXC to Wait Inactive Delay               | Вp         | 12 <sup>b</sup> | Вp         | 12 <sup>b</sup> | 1,2,4 |

| 3         | TdRXC(SY)  | RXC f to SYNC Valid Delay                | 4b         | 7b              | 4b         | <b>7</b> b      | 2,4   |

| 4         | TdRXC(INT) | RxC † INT Valid Delay                    | gb         | 12 <sup>b</sup> | gb         | 12 <sup>b</sup> | 1,2,4 |

|           |            |                                          | +2         | +3              | +2         | +3              | 5     |

| 5         | TdTXC(REQ) | TxC                                      | 5b         | Вp              | 5b         | вр              | 3,4   |

| 6         | TdTXC(W)   | TxC I to Wait Inactive Delay             | 5b         | Вp              | 5b         | gb              | 1,3,4 |

| 7         | TdTXC(DRQ) | TxC ↓ to DTR/REQ Valid Delay '           | 4b         | 7b              | <b>4</b> b | 7b              | 3,4   |

| 8         | TdTXC(INT) | TxC I to INT Valid Delay                 | <b>4</b> b | 6b              | <b>4</b> b | <b>6</b> b      | 1,3,4 |

|           |            |                                          | +2         | +3              | +2         | +3              | 5     |

| 9         | TdSY(INT)  | SYNC Transition to INT Valid Delay       | <b>2</b> b | 3b              | <b>2</b> b | зb              | 1,5   |

| 10        | TdEXT(INT) | DCD or CTS Transition to INT Valid Delay | 2b         | зb              | <b>2</b> b | Зb              | 1,5   |

#### NOTES:

#### Parameter Test Status:

a Tested b Guaranteed

C Guaranteed by characterization/design.

<sup>1.</sup> Open-drain output, measured with open-drain test load.

2. RxC is RtxC or TRxC, whichever is supplying the receive clock.

3. TxC is TRxC or RtxC, whichever is supplying the transmit clock.

4. Units equal to TcPC.

5. Units equal to AS.

#### **PIN DESCRIPTION**

T-75-37-07

The following section describes the pin functions of the Z-SCC. Figures 1 and 2 detail the respective pin functions and pin assignments.

AD<sub>0</sub>-AD<sub>7</sub>. Address/Data Bus (bidirectional, active High, 3-state). These multiplexed lines carry register addresses to the Z-SCC as well as data or control information to and from the Z-SCC.

**AS.** Address Strobe (input, active Low). Addresses on AD<sub>0</sub>-AD<sub>7</sub> are latched by the rising edge of this signal.

**CS<sub>0</sub>.** Chip Select 0 (input, active Low). This signal is latched concurrently with the addresses on AD<sub>0</sub>-AD<sub>7</sub> and must be active for the intended bus transaction to occur.

**CS<sub>1</sub>.** Chip Select 1 (input, active High). This second select signal must also be active before the intended bus transaction can occur. CS<sub>1</sub> must remain active throughout the transaction.

CTSA, CTSB. Clear to Send (inputs, active Low). If these pins are programmed as Auto Enables, a Low on the inputs enables their respective transmitters. If not programmed as Auto Enables, they may be used as general-purpose inputs. Both inputs are Schmitt-trigger buffered to accommodate slow rise-time inputs. The Z-SCC detects pulses on these inputs and can interrupt the CPU on both logic level transitions.

DCDA, DCDB. Data Carrier Detect (inputs active Low). These pins function as receiver enables if they are programmed for Auto Enables; otherwise they may be used as general-purpose input pins. Both pins are Schmitt-trigger buffered to accommodate slow rise-time signals. The Z-SCC detects pulses on these pins and can interrupt the CPU on both logic level transitions.

**DS.** Data Strobe (input, active Low). This signal provides timing for the transfer of data into and out of the Z-SCC. If  $\overline{AS}$  and  $\overline{DS}$  coincide, this is interpreted as a reset.

**DTR/REQA, DTR/REQB.** Data Terminal Ready/Request (outputs, active Low). These outputs follow the state programmed into the DTR bit. They can also be used as general-purpose outputs or as Request lines for a DMA controller.

**IEI.** Interrupt Enable In (input, active High). IEI is used with IEO to form an interrupt daisy chain when there is more than one interrupt driven device. A High IEI indicates that no other higher priority device has an interrupt under service or is requesting an interrupt.

**IEO.** Interrupt Enable Out (output, active High). IEO is High only if IEI is High and the CPU is not servicing a Z-SCC interrupt or the Z-SCC is not requesting an interrupt (Interrupt Acknowledge cycle only). IEO is connected to the next lower priority devices IEI input and thus inhibits interrupts from lower priority devices.

**INT.** Interrupt Request (output, open-drain, active Low) This signal is activated when the Z-SCC requests an interrupt.