# **Z8060 FIFO**

Buffer Unit and FIFO Expander

# **DISTINCTIVE CHARACTERISTICS**

- Bidirectional, asynchronous data transfer capability

- Large 128-bit-by-8-bit buffer memory

- Two-wire, interlocked handshake protocol

- 3-state data outputs

- Wire-ORing of empty and full outputs for sensing of multiple-unit buffers

- Connects any number of FIFOs in series to form buffer of any desired length

- Connects any number of FIFOs in parallel to form buffer of any desired width

# GENERAL DESCRIPTION

The Z8060\* First-In, First-Out (FIFO) buffer unit consists of a 128-bit-by-8-bit memory, bidirectional data transfer and handshake logic. The structure of the FIFO unit is similar to that of other available buffer units. FIFO is a general-purpose unit; its handshake logic is compatible with that of other members of the Z8000 family.

FIFOs can be cascaded end-to-end without limit to form a parallel 8-bit buffer of any desired length (in 128-byte increments). Any number of single- or multiple-unit FIFO serial buffers can be connected in parallel to form buffers of any desired width (in 8-bit increments).

# FIFO BLOCK DIAGRAM DATA DATA DATA BUFFER CONTROL CONTROL CONTROL ND STATUS BD003311

\*Z8000 is a trademark of Zilog, inc

02128B

Refer to page 7-1 for Essential Information on Military Devices

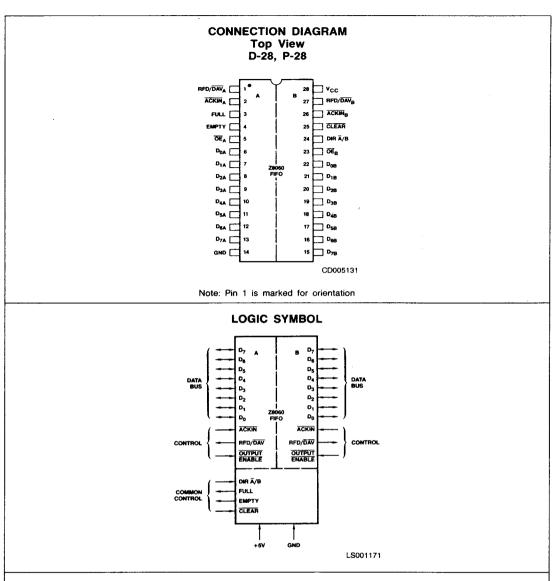

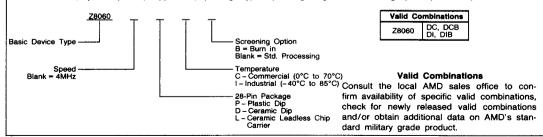

## ORDERING INFORMATION

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

021200

2-309

#### PIN DESCRIPTION Description Pin No. Name 1/0 +5V Power Supply 28 Vcc GND Ground Acknowledge input. This line signals the FIFO that output data has been received by ACKIN 2 26 peripherals or that input data is valid. active LOW Clear Buffer. When set to LOW, this line causes all data to be cleared from the FIFO buffer. CLEAR 25 active LOW Data Bus (bidirectional). These bidirectional lines are used by the FIFO to receive and to 6 - 13 1/0 Do-D7 transmit data Direction input A/B (two control states), A HIGH on this line signals that input data is to be 24 DIR A/B received at port B. A LOW on this line signals that input data is to be received at port A. Buffer Status (open-drain). A HIGH on this line indicates that the FIFO buffer is empty. **EMPTY** O active HIGH Buffer Status (open-drain). A HIGH on this line indicates that the FIFO buffer is full. 3 FULL active HIGH Output Enable A, Output Enable B. When LOW, $\overline{OE}_A$ enables the bus drivers for port A; when HIGH, $\overline{OE}_A$ causes the bus drivers to float to a high-impedance level. Input $\overline{OE}_B$ controls the bus drivers for port B in the same manner as $\overline{OE}_A$ controls those for port A. OEA, OEB 5, 23 active LOW

## **DETAILED DESCRIPTION**

RFD/DAV

1, 27

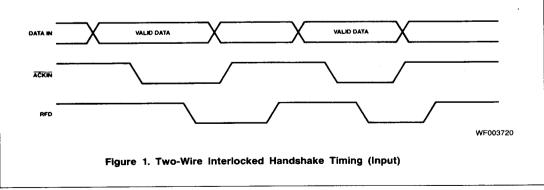

#### Interlocked 2-Wire Handshake

In interlocked 2-wire handshake operation, the action of FIFO must be acknowledged by the other half of the handshake before the next action can occur. In an Output Handshake mode, the FIFO indicates that new data is available only after the external device has indicated that it is ready for the data. In an Input Handshake mode, the FIFO does not indicate that it is ready for new data until the data source indicates that the previous byte of the data is no longer available, thereby acknowledging the acceptance of the last byte. This control feature allows the FIFO, with no external logic, to directly interface with the port of any CPU in the Z8 Family — a CIO, a UPC, an FIO, or another FIFO. The timing for the input and output handshake operations is shown in Figures 1 and 2, respectively.

o

#### Resetting or Clearing the FIFO

The CLEAR is used to initialize and clear the FIFO. A Low level on this input clears all data from the FIFO, allows the EMPTY output to go HIGH and forces both outputs RFD/  $\overline{DAV}_A$  and RFD/ $\overline{DAV}_B$  HIGH. A HIGH level on  $\overline{CLEAR}$  allows the data to transfer through the FIFO.

# LOW, signals to the peripherals involved that FIFO has data available to send. Bidirectional Transfer Control

Ready-for-Data/Data Available (outputs RFD, active HIGH, DAV active LOW). RFD, when HIGH, signals to the peripherals involved that the FIFO is ready to receive data. DAV, when

The FIFO has bidirectional data transfer capability under control of the DIR  $\overline{A}/B$  input. When DIR  $\overline{A}/B$  is set LOW, port A becomes input handshake and port B becomes output handshake; data transfers are then made from port A to port B. Setting DIR  $\overline{A}/B$  HIGH reverses the handshake assignments and the direction of transfer. This bidirectional control is illustrated in Table 1.

TABLE 1. BIDIRECTIONAL CONTROL FUNCTION TABLE

| DIR A/B |   | Port A<br>Handshake | Port B<br>Handshake | Transfer |  |  |

|---------|---|---------------------|---------------------|----------|--|--|

|         | 0 | Input               | Output              | A to B   |  |  |

|         | 1 | Output              | Input               | B to A   |  |  |

The FIFO buffer must be empty before the direction of transfer is changed; otherwise, the results of the change will be unpredictable. If FIFO status is unknown when a transfer direction change is to be made, the recommended procedure

- (1) Force and hold CLEAR LOW,

- (2) Set DIR A/B to the level required for the desired direction, and then

- (3) Force CLEAR HIGH.

02128B

2-310

Refer to page 7-1 for Essential Information on Military Devices

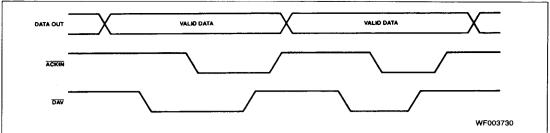

Figure 2. Two-Wire Interlocked Handshake Timing (Output)

#### **EMPTY** and **FULL** Operation

The EMPTY and FULL output lines can be wire-ORed with the EMPTY and FULL lines of other FIFOs and FIOs. This capability enables the user to determine the EMPTY/FULL status of a buffer consisting of multiple FIFOs, FIOs, or a combination of both. Table 2 shows the various states of EMPTY and FULL.

TABLE 2. SIGNALS EMPTY AND FULL OPERATION TABLE

|   | Number of<br>Bytes in FIFO | Empty  | Full |

|---|----------------------------|--------|------|

| Г | 0                          | HIGH . | LOW  |

|   | 1-127                      | LOW    | LOW  |

|   | 128                        | LOW    | HIGH |

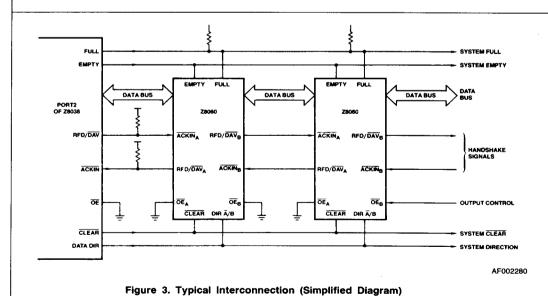

## Interconnection Example

A simplified block diagram showing the manner in which FIFOs can be interconnected to extend a FIO buffer is shown in Figure 3.

#### **Output Enable Operation**

The FIFO provides a separate Output Enable  $(\overline{OE})$  signal for each port of the buffer. An  $\overline{OE}$  output is valid only when its port is in the Output Handshake mode. The control of this output function is shown in Table 3. Signal  $\overline{OE}$  operates with lines DIR  $\overline{A}/B$ . A HIGH on a valid  $\overline{OE}$  line 3-states its port's data bus but does not affect the handshake operation. A LOW level on a valid  $\overline{OE}$  enables the data bus outputs if its port is in the Output Handshake mode. Note that the handshake operation is unaffected by the Output Enable pin.

TABLE 3. OUTPUT CONTROL FUNCTION TABLE

| DIR A/B | ŌĒĄ | ŌĒB | Function                                       |  |

|---------|-----|-----|------------------------------------------------|--|

| 0       | х   | 0   | Disable Port A Output<br>Enable Port B Output  |  |

| 0       | x   | 1   | Disable Port A Output<br>Disable Port B Output |  |

| 1       | 0   | ×   | Enable Port A Output<br>Disable Port B Output  |  |

| 1       | 1   | x   | Disable Port A Output<br>Disable Port B Output |  |

Note: X = Don't Care.

02128B

2-311

Refer to page 7-1 for Essential Information on Military Devices

# **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature      |           | 65 | to +150°C  |

|--------------------------|-----------|----|------------|

| Voltage to any Pin Relat | ve to Vss | 0. | 5 to +7.0V |

| Power Dissination        |           |    | 1.8W       |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

# **OPERATING RANGES**

|                                                                                                         | Z8060   |

|---------------------------------------------------------------------------------------------------------|---------|

| Commercial Operating Range T <sub>A</sub> = 0 to +70°C V <sub>CC</sub> = 5V ±5% V <sub>SS</sub> = 0V    | Z8060DC |

| Industrial Operating Range T <sub>A</sub> = -40 to +85°C V <sub>CC</sub> = 5V ±10% V <sub>SS</sub> = 0V | Z8060DI |

Operating ranges define those limits over which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over operating range unless otherwise specified (Note 1)

| Parameters | Description            | Test Conditions                                       | Min  | Тур | Max                   | Units |

|------------|------------------------|-------------------------------------------------------|------|-----|-----------------------|-------|

| VIL        | Input LOW Voltage      |                                                       | -0.3 |     | + 0.8                 | Volts |

| ViH        | Input HIGH Voltage     | Standard Temp                                         | 2.0  |     | V <sub>CC</sub> + 0.3 | Volts |

| *ID        |                        | IOL = 3.2mA                                           |      |     | 0.5                   | Volts |

| VOL        | Output LOW Voltage     | I <sub>OL</sub> = 2.0mA                               |      |     | 0.4                   | 10.13 |

| VoH        | Output HIGH Voltage    | I <sub>OH</sub> = -250μA                              | 2.4  |     |                       | Volts |

| lozi       | Output Leakage Current | V <sub>OUT</sub> = 0.4V                               |      |     | 10                    | μΑ    |

| lozh       | Output Leakage Current | V <sub>OUT</sub> = V <sub>CC</sub>                    |      |     | 10                    | μА    |

| lı lı      | Input Leakage Current  |                                                       |      |     | ±10                   | μΑ    |

| Cin        | Input Capacitance      | Unmeasured pins returned                              |      |     | 10                    | pF    |

| CI/O       | I/O Capacitance        | to ground. f = 1MHz over specified temperature range. |      |     | 20                    | ρF    |

| COUT       | Output Capacitance     |                                                       |      |     | 15                    | pF    |

| Icc        | Power Supply Current   | V <sub>CC</sub> = MAX                                 |      |     | 250                   | mA    |

# **Standard Test Conditions**

The characteristics below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the referenced pin. Standard conditions are as follows:

$$+4.75V \le V_{CC} \le +5.25V$$

$GND = 0V$

$0^{\circ}C \le T_{A} \le +70^{\circ}C$

#### **Test Load Conditions**

02128B

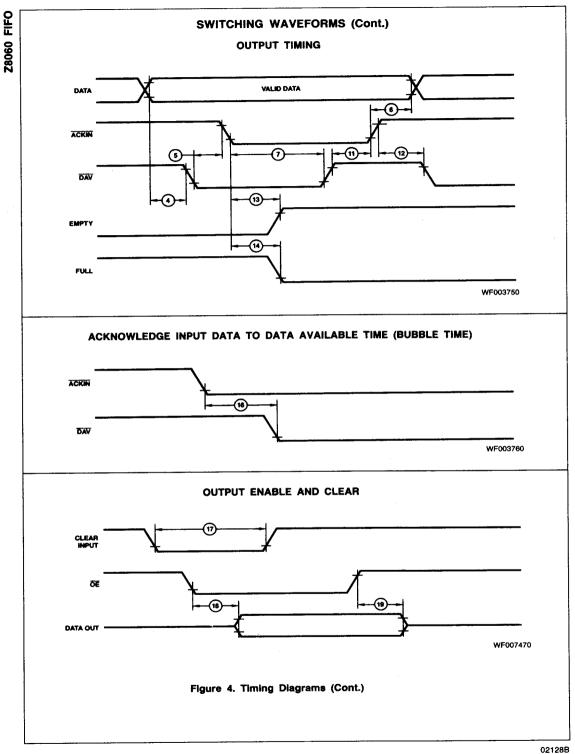

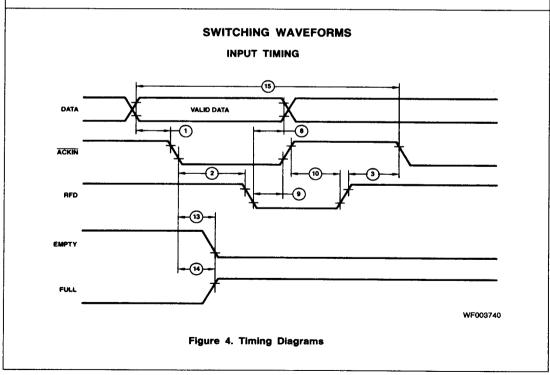

#### FIFO 2-WIRE HANDSHAKE TIMING

Timing for 2-wire interlock handshake operation is shown in Figure 1. The symbol, description and values for the numbered parameters (Figure 1) are given in Switching Characteristics.

# SWITCHING CHARACTERISTICS over operating range unless otherwise specified

| Number | Parameters       | Description                                                        | Min | Max | Units |

|--------|------------------|--------------------------------------------------------------------|-----|-----|-------|

| 1      | TsDI(ACK)        | Data Input to ACKIN: to Setup Time                                 | 50  |     | ns    |

| 2      | TdACKf(RFD)      | ACKIN; to RFD; Delay                                               | 0   | 500 | ns    |

| 3      | TdRFDr(ACK)      | RFD† to ACKIN; Delay                                               | 0   |     | ns    |

| 4      | TsDO(DAV)        | Data Out to DAV Setup Time                                         | 25  |     | ns    |

| 5      | TdDAVf(ACK)      | DAV; to ACKIN; Delay                                               | 0   |     | ns    |

| 6      | ThDO(ACK)        | Data Out to ACKIN: Hold Time                                       | 50  |     | ns    |

| . 7    | TdACK(DAV)       | ACKIN₁ to DAV↑ Delay                                               | 0   | 500 | ns    |

| 8      | ThDI(RFD)        | Data input to RFD   Hold Time                                      | 0   |     | ns    |

| 9      | TdRFDf(ACK)      | RFD↓ to ACKIN↑ Delay                                               | 0   |     | ns    |

| 10     | TdACKr(RFD)      | ACKIN 1 to RFD 1 Delay                                             | 0   | 400 | ns    |

| 11     | TdDAVr(ACK)      | DAV † to ACKIN †                                                   | 0   |     | ns    |

| 12     | TdACKr(DAV)      | ACKIN 1 to DAV 1                                                   | 0   | 800 | ns    |

| 13     | TdACKINf(EMPTY)  | (Input) ACKIN i to EMPTY i Delay (Output) ACKIN i to EMPTY i Delay |     | 600 | ns    |

| 14     | TdACKINf(FULL)   | (Input) ACKIN ⊥ to FULL ↑ Delay (Output) ACKIN ⊥ to FULL ⊥ Delay   |     | 600 | ns    |

| 15     | ACKIN Clock Rate | (Input)                                                            |     | 1.0 | MHz   |

| 16     | TdACKINf(DAVf)   | (Bubble Time)                                                      |     | 800 | ns    |

| 17     | TWCLR            | Width of Clear to Reset FIFO                                       | 700 |     | ns    |

| 18     | TdOE(DO)         | OE ⊥ to Data Bus Driven                                            | 0   | 150 | ns    |

| 19     | TdOE(DRZ)        | OE † to Data Bus Float                                             |     | 100 | ns    |

Note: All timing references assume 2.0V for a logic 1 and 0.8V for a logic 0.

02128B