# Z8152A/53A

PRELIMINARY PRODUCT SPECIFICATION

#### DISTINCTIVE CHARACTERISTICS

- 100 MHz Video Dot Rate

- $\bullet$  Four-level current driven (75 $\Omega$ ) differential video output

- Digital Video output ECL option (Z8152A provides TTL option)

- On-board crystal driven oscillator

- Proportional Spacing Support (2—17 dots)

- 9-bit dot data parallel input, with expansion capability to seventeen bits

- Trailing blanks (0—3 dots)

- Double Width Characters

- Attribute Support:

Character Blink

Underline

Overstrike

Reverse Highlight

- Buffered and Synchronized Character Clock Outputs

- Background color selection

- Buffered and Synchronized Vertical and Horizontal Sync

#### **GENERAL DESCRIPTION**

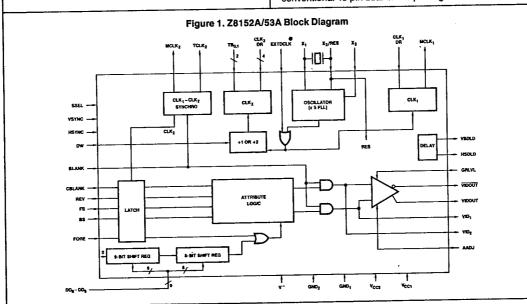

The Z8152A/53A Video System Controller (VSC) provides interface between a CRT controller and a CRT monitor. The basic chip functions are:

- Support proportional and non-proportional character display

- Correctly synchronize and mix character attributes with video signals

- Output the video information in a four-level analog or digital format

The VSC consists of a parallel-to-serial converter which provides a video bit stream to on-chip attribute logic. This logic, under control of the attribute inputs, operates on the bit stream to generate grey scale video. Video outputs from the VSC are of two forms-analog and digital. The digitally encoded outputs implement four video levels: Blank, Black, Grey and White. Identical information is available in analog form via differential outputs (current driven) into a nominal 75Ω impedance.

The Z8152A/53A also supports proportional spacing using a bit width programmable character clock. Character ROM pixel information is selectable from two to seventeen pixels per character. Up to three blank pixels can be appended to the character ROM input thereby facilitating right justification of text.

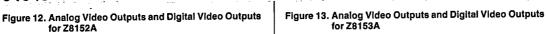

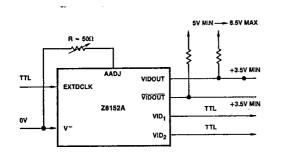

The difference between the Z8152A and the Z8153A is in the output scheme. The Z8152A has standard TTL outputs and operates in the 25-60 MHz range, while the Z8153A has 10K ECL outputs and operates in the 40-100 MHz

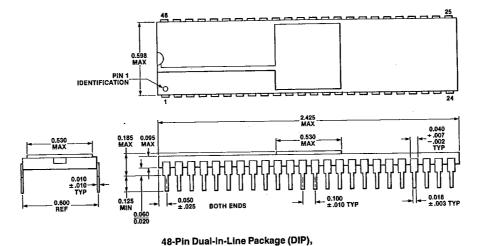

The Z8152A/53A is fabricated using an advanced bipolar process with internal ECL logic. The device is available in conventional 48-pin dual-in-line packages.

#### PIN DESCRIPTION

MCLK<sub>1</sub>

CLOCK<sub>1</sub> (output, non-TTL compatible)

MCLK<sub>1</sub> is a system clock. It is intended to drive the Z8052 horizontal and vertical timing circuitry as well as the DMA operations. MCLK1 output is nominally a square wave divided down from the internal dot clock frequency according to the CLK<sub>1</sub> DR (CLK<sub>1</sub> Divide Ratio) input.

CLK<sub>1</sub> DR

CLK<sub>1</sub> DIVIDE RATIO (inputs (3))

CLK<sub>1</sub> DR are three inputs which control the MCLK<sub>1</sub> divide ratio. The three inputs may be programmed to divide the MCLK1 signal by two, four, six, . . . , sixteen.

| 2 | CLK <sub>1</sub> D | A <sup>(1)</sup> | B <sup>(1)</sup>      |        |

|---|--------------------|------------------|-----------------------|--------|

| L | L                  | L                | 1                     | 1      |

| L | L                  | Н                | 2                     | 2      |

|   | Н                  | L                | 2<br>3<br>4<br>5<br>6 | 2<br>3 |

| L | н                  | н                | 4                     | 4      |

| Н | L                  | L                | 5                     | 5      |

| Н | L                  | н                | 6                     | 6      |

| Н | L                  | L                | 7                     | 7      |

| Н | н                  | н                | 8                     | 8      |

MCLK<sub>2</sub>

CLOCK<sub>2</sub> (output, non-TTL compatible)

MCLK2 is a character display clock. Its function is to control the character code and attribute data output rate from the appropriate Z8052 CRTC's ports.

CLK<sub>2</sub>DR

CLOCK<sub>2</sub> DIVIDE RATIO (inputs (4))

CLK2 DR are four inputs which control an internal divider to divide the dot clock frequency by a value from two to seventeen.

| Γ     | CLK |   |             |                                 |                                      |

|-------|-----|---|-------------|---------------------------------|--------------------------------------|

| 3     | 2   | 1 | 0           | C <sup>(1)</sup>                | D(1)                                 |

| L     | L   | L | L           | 1                               | 1                                    |

| L     | L   | L | н           | 1                               | 2                                    |

| l L l | L   | н | L           | 2                               | 2                                    |

| lll   | L   | н | н           | 2                               | 3                                    |

| L     | н   | L | L           | 3                               | 3                                    |

| L     | н   | L |             | 1<br>2<br>3<br>3<br>4<br>4<br>5 | 1<br>2<br>2<br>3<br>4<br>4<br>5<br>5 |

| L     | н   | н | L           | 4                               | 4                                    |

| L     | н   | н | Н           | 4                               | 5                                    |

| H     | L   | L | L           | 5                               | 5                                    |

| l H   | L   | L | Н           | 5                               | 6                                    |

| l н   | L   | н | L           | 6                               | 6                                    |

| н     |     |   | L<br>H<br>L | 6                               | 6<br>7<br>7<br>8                     |

| Н     | н   | L | L           | 7                               | 7                                    |

| Н     | Н   | L | Н           | 7<br>7<br>8                     | 8                                    |

| Н     | Н   | Н | L           | 8                               | 8                                    |

|       | н   | н | L<br>H      | 8                               | 9                                    |

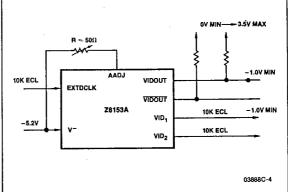

Note 1. A, B, C, and D are measured in **EXTDCLK** periods

(See Reset Timing on page 15).

TTL CLOCK<sub>2</sub> (output) TCLK<sub>2</sub>

TCLK2 is a TTL compatible version of MCLK2.

X<sub>1</sub>,X<sub>2</sub>/RES X<sub>1</sub>, X<sub>2</sub>/RESET (inputs, X<sub>2</sub>, is non-TTL compatible, reset is TTL compatible)

X<sub>1</sub>, X<sub>2</sub>/RES are the external crystal inputs when the on-chip oscillator of the VSC is being used. The external crystal frequency is multiplied by five to produce the on-chip dot clock. If the external dot clock option is used, the X<sub>1</sub> should be tied LOW and X2/RES may be used as a reset input, to synchronize multiple VSC's. Note that the reset signal should be synchronous to the external dot clock.

X<sub>3</sub> (input, non-TTL compatible)  $X_3$

X3 is used as an input to the on-chip voltagecontrolled oscillator. When the on-chip oscillator of the VSR is being used, X3 should be connected to ground by an appropriate capacitor. If the external dot clock option is used, X<sub>3</sub> and X<sub>1</sub> should be tied LOW.

**VERTICAL SYNC (input)** VSYNC

VSYNC is an input that must be synchronous to either MCLK1 or MCLK2, dependent on the SSEL input. If SSEL is HIGH, VSYNC must be synchronous to MCLK1.

**VERTICAL SYNC DELAYED (output) VSDLD**

VSDLD is the delayed output of VSYNC, synchronous to MCLK<sub>1</sub> or MCLK<sub>2</sub>, depending on the setting of SSEL.

**HORIZONTAL SYNC DELAYED (input)**

HSYNC is an Input that must be synchronous to either  $\mathsf{MCLK}_1$  or  $\mathsf{MCLK}_2$ , dependent upon the SSEL input. If SSEL is LOW, HSYNC must be synchronous to MCLK2; if SSEL is HIGH, HSYNC must be synchronous to MCLK<sub>1</sub>.

**HORIZONTAL SYNC (output) HSDLD**

HSDLD is the delayed output of HSYNC, synchronous to MCLK<sub>1</sub> or MCLK<sub>2</sub>, depending upon the setting of SSEL.

SYNC SELECT (input) SSEL

**HSYNC**

The SSEL line determines if the VSYNC, HSYNC and BLANK are going to be synchronized to the MCLK1 or MCLK2 signals. A HIGH on SSEL also will resynchronize CLK2 and CLK<sub>1</sub> during blanking.

**BLANK (input) BLANK**

BLANK is an input normally synchronous to MCLK<sub>1</sub>, although it may be synchronous to MCLK<sub>2</sub> in non-proportional spacing applications. The active pulse width of BLANK will usually overlap the inactive-to-active waveforms of HSYNC and VSYNC, as well as the active-toinactive portion of VSYNC. While BLANK is active TCLK2/MCLK2 may be forced to synchronize to the MCLK1 clock. When BLANK goes inactive, the rising edges of MCLK1 and TCLK<sub>2</sub>/MCLK<sub>2</sub> must be synchronized in order to prevent "dot walk" in proportional spacing applications. BLANK active also forces the video output level to "blank" regardless of DD, FORE or

other inputs.

**CHARACTER BLANK (Input) CBLANK**

CBLANK forces video output levels (VID1, VID2, VIDOUT and VIDOUT) to switch to the

background color level.

FOREGROUND VIDEO (input)

The FORE video input is "OR'ed" with the dot data output by the parallel-to-serial shift register to switch to the foreground color level (e.g., to implement underlines).

**FORE**

#### **REVERSE** (input) **REV**

The REV input causes the foreground color levels to be transposed with the background color level for the total character period (including any tracking blanks).

#### FS

#### FOREGROUND SHIFT (input)

The FS input causes the shift in the video output levels to produce a highlight effect. See Table 1.

#### TB<sub>0</sub>, TB<sub>1</sub>

#### TRAILING BLANKS (inputs(2))

The TB inputs concatenate "blank" video dots to the tail end of the dot data contained in the parallel-to-serial shift register. TB can be specified to concatenate 0, 1, 2 or 3 dots. The TB value is also added to the CLK2 DR value to obtain the total. The combination of all CLK2DR inputs being High (17 dots) and both TB inputs being High (3 trailing blanks) is not allowed. The maximum CLK2 period is 19 dot periods.

#### $DD_0 - DD_8$

#### **DOT DATA (inputs (9))**

The DD inputs accept parallel character dot matrix information for serial conversion for video output. DD data is accepted at the TCLK2/MCLK2 clock rate. DDo is shifted out first.

#### BS

#### **BACKGROUND SELECT (input)**

The BS input specifies the color level of the background video. This input can be overridden by BLANK active.

#### VIDOUT, VIDOUT

#### **VIDEO OUTPUT**

(analog outputs (2), non-TTL compatible)

VIDOUT and VIDOUT outputs in a differential mode the composite blank, and video dot levels to a nominal 75 $\Omega$  load impedance from switched current sources.

#### VID1, VID2

#### **VIDEO DIGITAL**

#### (outputs (2), (8152A-TTL; 8153A-ECL)

VID<sub>1</sub> and VID<sub>2</sub> are digitally encoded outputs of the video out. VID<sub>1</sub> is the least significant bit. Encoding is as follows:

|             | VID <sub>2</sub><br>(VIDEO) | VID <sub>1</sub><br>(HIGHLIGHT) |

|-------------|-----------------------------|---------------------------------|

| Blank Level | 0                           | 0                               |

| Black       | 0                           | 1                               |

| Grev        | 1                           | 0                               |

| White       | 1                           | 1                               |

#### **GRLVL**

#### **GREY LEVEL (input)**

The GRLVL input adjusts the current level output, via the VIDOUT and VIDOUT outputs, of the grey video level. There are two pre-selected grey levels; for GRLVL HIGH grey is brighter, for LOW grey is darker.

#### DW

## DOUBLE WIDTH (inputs)

The DW input, when active HIGH, causes the dot clock supplied to the TCLK2/MCLK2 clock divide to be divided by two. This function is used to

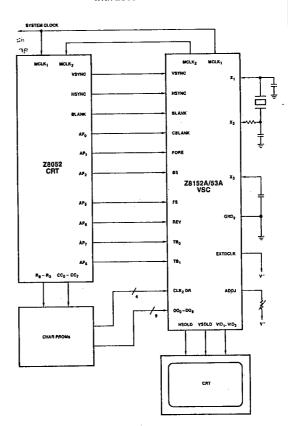

#### Figure 4. Z8152A/53A Application with Z8052 CRT Controller

facilitate doubling the width of a character cell matrix in the horizontal direction. The trailing blank information is also widened during a double width character.

#### **EXTDCLK**

#### **EXTERNAL DOT CLOCK**

#### (input, 8152A-TTL; 8153A-ECL)

EXTDCLK is an external, TTL or ECL compatible dot clock input for use in multiple Z8152A/53A configurations. This signal replaces the internal oscillator function. To enable EXTDCLK both  $\mathbf{X}_{\mathbf{1}}$ and X3 must be grounded.

#### AADJ

#### **ANALOG OUTPUTS CURRENT ADJUST** (input, non - TTL compatible)

#### Analog output current adjust is used for setting the analog video output current to 13.3mA. This is done by connecting AADJ to V- via an appli-

cable 1% resistor.

#### **FUNCTIONAL DESCRIPTION**

The Z8152A Video System Controller (VSC) supports both black and white and color video applications for CPUs, CRT controllers, and terminals. The essential functions of the VSC are to support proportional and non-proportional character display, to synchronize and mix character attributes with video, and to output the video in a four level analog or digital format.

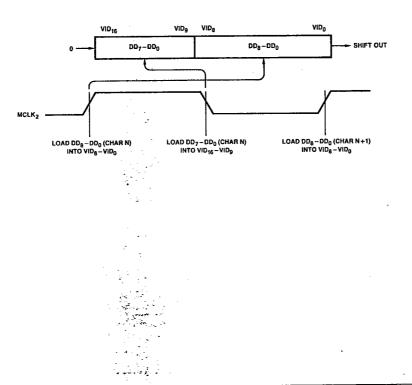

#### PARALLEL PIXEL LOADING

Pixel information that must be serialized for video transmission is loaded into the serial shift register via inputs DD0-DD8. Information is loaded on both edges of the MCLK2 character clock, as shown in Figure 3. The information set up on DD (0:7) prior to the falling edge of MCLK2 is loaded into positions VID9-VID16. Note that DD8 information is ignored. Information set up on DD(0:8) prior to the rising edge of MCLK2 is loaded into positions VID0-VID8. Thus, up to 17 bits of pixel information can be loaded into the shift register. Note that if the character width is nine pixels or less the information captured on the falling edge of the MCLK2 is not used. Any trailing blank insertion only occurs after the total number of pixels for the character

CLK<sub>2</sub>DR (0:3) and TB (0:1) determine the divide ratio for the character clock. The sum of both values specifies the character clock period in dot clocks. During the trailing blank, the VSC shifts out what was loaded into the shift register. Therefore, it is the responsibility of the user to insure that the pixels output during the trailing blank dot period are set to the blank level.

#### **VIDEO OPERATION**

Parallel video data is obtained from the character ROM inputs; bits are shifted out serially and mixed with attribute information such as underline, shifted underline, and any other video sources. Video is internally encoded into one of four levels: White, Grey, Black and Blank. White is the highest analog current level, and Blank is the lowest. This information is then output through two ports (see Figure 5/6). One port provides a single current source output into a  $75\Omega$  impedance and the second port outputs either encoded TTL or ECL video on

There are two distinct blank inputs to the Z8152A/53A. BLANK is the CRTC's horizontal and vertical retrace period input which causes a blank output level to the display. CBLANK is an attribute input to selectively blank a character cell by forcing the video information for the particular character cell period to switch to the selected background color level.

Figure 5. Shift Register Loading

#### VIDEO INPUTS/OUTPUTS

Video information may be input in a number of different ways. Table 1 depicts all the combinations of video outputs achievable with each of the various inputs. The background color is determined by a separate pin input allowing either a black or white background. Using the REVERSE VIDEO (REV) input, a grey background can also be selected. The foreground then becomes black or white according to the signal on the foreground SHIFT line. Foreground and video sums can be modified depending on the combination of background, foreground shift, and reverse inputs. The user may apply any of his video inputs to the foreground to obtain a desired effect.

**TABLE 1. Z8152A/53A VIDEO ATTRIBUTES**

|    |    |     | INPUTS                   | Z8152A/53A VIDEO |

|----|----|-----|--------------------------|------------------|

| BS | FS | REV | CBLANK (DD (0:8) + FORE) | ATTRIBUTES       |

| 0  | 0  | 0   | 0                        | 32               |

| 0  | 0  | 0   | 1 .                      | #                |

| 0  | 0  | 1   | 0                        | <b>1</b> ////    |

| 0  | 0  | 1   | 1 '                      |                  |

| 0  | 1  | 0   | 0 .                      |                  |

| 0  | 1  | 0   | 1 .                      |                  |

| 0  | 1  | 1   | 0                        |                  |

| 0  | 1  | 1   | 1                        |                  |

| 1  | 0  | 0   | 0                        |                  |

| 1  | 0  | 0   | 1                        | Ø                |

| 1  | 0  | 1   | 0                        | <b>1</b> ////    |

| 1  | 0  | 1   | 1                        | <del>1/6/1</del> |

| 1  | 1  | 0   | 0                        | 100              |

| 1  | 1  | 0   | 1                        | •                |

| 1  | 1  | 1   | 0                        |                  |

| 1  | 1  | 1   | 1                        |                  |

|    |    |     |                          |                  |

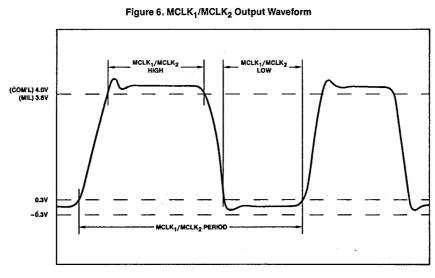

#### SYSTEM TIMING

The CPU clock (MCLK<sub>1</sub>) output is derived from an on-board oscillator by an externally programmable divide by two or three prescaler and a one to eight decoder. The internal oscillator is capable of operating a frequency of up to 100MHz and in a fundamental or third harmonic mode. Figure 4 shows the output waveform of MCLK<sub>1</sub> and MCLK<sub>2</sub>.

The character clock (MCLK2) output to the CRTC is frequency modulated according to the chosen number of dots per character cell. The duty cycle of MCLK2 is 50% ( $\pm 1$  dot clock period) and is derived from an internal crystal driven oscillator whose divide ratio is set by the width of the character ROM plus the number of trailing blanks. A double width input further modifies MCLK2 doubling the character width. During an active BLANK input MCLK2 is internally re-synchronized to MCLK1. This action aligns character cells at the left-end side of the display thereby eliminating "Dot Walk." The Vertical and Horizontal Sync (VSYNC, HSYNC) inputs from the CRT controller are buffered and delayed by a MCLK1 or MCLK2 clock period in order to phase correctly with the character video output.

#### PROPORTIONAL/VARIABLE SPACING

Proportional spacing is achieved by programming on a character-by-character basis, a number of two to twenty dot clock periods per character. The character ROM pixel information is selectable from two to seventeen per character. Up to three trailing blank pixels can be concatenated to the character ROM input, making it easier to provide a straight right margin for right justification of text.

#### **COLOR APPLICATION**

The Z8152A/53A may be used for many high-end color display applications. The foreground video and background information is mixed by the Z8152A/53A, and the encoded TTL video output can be used externally to select a color mix for the particular pixel being displayed. The horizontal and vertical synchronization, and video blank is output by the Z8152A/53A.

E

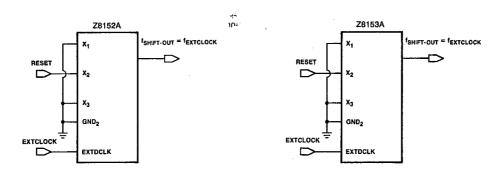

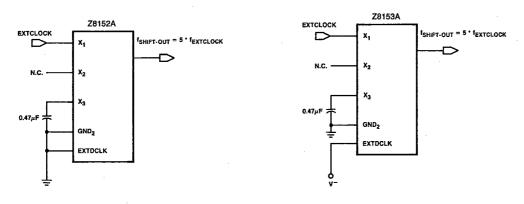

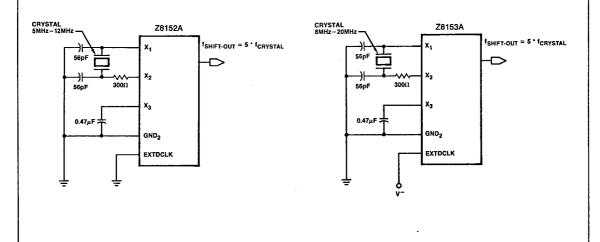

Figure 7. Dotclock Generation Mode

#### EXTERNAL CLOCK FLOW THROUGH MODE

#### EXTERNAL CLOCK MULTIPLIER MODE

#### CRYSTAL OSCILLATOR MULTIPLIER MODE

#### Z8152A

#### MAXIMUM RATINGS (Above which the useful life may be impaired)

| Storage Temperature                                 |        | −65 to +150°C             |

|-----------------------------------------------------|--------|---------------------------|

| Supply Voltage to Ground Potential Continuous       | 14. A. | -0.5 to +7.0V             |

| DC Voltage Applied to Outputs for High Output State |        | -0.5V to +V <sub>CC</sub> |

| DC Input Voltage                                    | 49.5   | -0.5 to +5.5V             |

| DC Output Current into Outputs                      |        | 30mA                      |

| DC Input Current                                    |        | -30 to +5.0mA             |

#### Z8152A DC CHARACTERISTICS (See Note 4)

The following conditions apply unless otherwise specified:

COM'L  $T_A = 0$  to +70°C

| Parameters      | Description                                |                                                  | Test Con                              | ditions (Note 1)             |                  | Min | Typ<br>(Note 2) | Max  | Units |

|-----------------|--------------------------------------------|--------------------------------------------------|---------------------------------------|------------------------------|------------------|-----|-----------------|------|-------|

|                 |                                            |                                                  | MCLK <sub>1</sub>                     |                              | MIL              | 3.6 |                 |      | Volts |

|                 |                                            |                                                  | MCLK <sub>2</sub>                     | $I_{OH} = -0.1 \text{mA}$    | COM'L            | 4.0 | -               |      | Volts |

| V <sub>OH</sub> | Output HIGH Voltage                        | V <sub>CC</sub> = Min                            | TTL                                   | I <sub>OH</sub> = -1mA       | · MIL            | 2.4 | 3.4             |      | Volts |

|                 |                                            |                                                  | Outputs                               | I <sub>OH</sub> = -2.6mA     | COM'L            | 2.4 | 3.4             |      | Volts |

|                 |                                            |                                                  |                                       | I <sub>OL</sub> = 0.1mA MCL  | K <sub>1/2</sub> |     |                 | 0.3  | Volts |

| V <sub>OL</sub> | Output LOW Voltage                         | V <sub>CC</sub> = Min                            |                                       | I <sub>OL</sub> = 16mA TTL 0 | Outputs          |     |                 | 0.5  | Volts |

| V <sub>IH</sub> | Input HIGH Level                           | Guaranteed In                                    | put HIGH Vo                           | oltage                       |                  | 2.0 |                 |      | Volts |

| V <sub>IL</sub> | Input LOW Level                            | Guaranteed In                                    | put LOW Vo                            | Itage                        |                  |     |                 | 0.8  | Volts |

| VI              | Input Clamp Voltage                        | V <sub>CC</sub> = Min, I <sub>II</sub>           | <sub>1</sub> = -18mA                  |                              |                  |     |                 | -1.2 | Volts |

|                 |                                            | V <sub>CC</sub> = Max                            |                                       | All inputs (Except RE        | S, EXTDCLK)      |     |                 | -0.4 | mA    |

| I               | Input LOW Current                          | V <sub>IN</sub> = 0.4V                           |                                       | RES, EXTDCLK                 |                  |     |                 | -1.0 | mA    |

|                 |                                            | V <sub>CC</sub> = Max                            |                                       | All Inputs (Except           | RES)             |     |                 | +50  | μΑ    |

| lн              | Input HIGH Current                         | V <sub>IN</sub> = 2.7V                           |                                       | RES                          |                  |     |                 | +600 | μΑ    |

| l <sub>i</sub>  | Input HIGH Current at<br>Max Input Voltage | V <sub>CC</sub> = Max<br>V <sub>IN</sub> = 5.5V  |                                       |                              |                  |     |                 | +1.0 | mA    |

|                 | Output Short Current                       | V 14                                             | MCLK <sub>1</sub> , MCLK <sub>2</sub> |                              | -50              |     | -250            | mA   |       |

| Isc             | Current (Note 3)                           | V <sub>CC</sub> = Max                            |                                       | Others                       |                  | -40 |                 | -130 | mA    |

|                 |                                            |                                                  | Over Ope                              | rating Range                 |                  |     |                 | 415  | mA    |

| lcc             | Power Supply Current                       | V <sub>CC1</sub> = Max<br>V <sub>CC2</sub> = Max | @ T <sub>A</sub> = 70°C               |                              |                  |     | 375             | mA   |       |

| = =             |                                            | ACCS - MIGY                                      | @ T <sub>C</sub> =                    | @ T <sub>C</sub> = 125°C     |                  |     |                 | 350  | mA    |

Notes: 1. For conditions shown as Min or Max use the appropriate value specified under DC Characteristics for the applicable device type.

Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

Except: X<sub>1</sub>, X<sub>2</sub>, X<sub>3</sub>, AADJ, VIDOUT, VIDOUT.

#### Z8153A

#### MAXIMUM RATINGS (Above which the useful life may be impaired)

| Storage Temperature                                 | −65 to +150°C             |

|-----------------------------------------------------|---------------------------|

| Supply Voltage to Ground Potential Continuous       | -0.5 to +7.0V             |

| DC Voltage Applied to Outputs for High Output State | -0.5V to +V <sub>CC</sub> |

| DC Input Voltage                                    | -0.5 to +5.5V             |

| DC Output Current into Outputs                      | 30mA                      |

| DC Input Current                                    | -30 to +5.0mA             |

#### Z8153A DC CHARACTERISTICS (See Note 4)

The following conditions apply unless otherwise specified:

| Parameters                  | Description                                |                                        | Test Cond               | ditions (Note 1)                      |                   | Min | (Note 2) | Max   | Units |

|-----------------------------|--------------------------------------------|----------------------------------------|-------------------------|---------------------------------------|-------------------|-----|----------|-------|-------|

|                             |                                            |                                        | MCLK <sub>1</sub>       |                                       | MIL               | 3.6 | 1        |       | Volts |

| .,                          |                                            | ,, ,,                                  | MCLK <sub>2</sub>       | I <sub>OH</sub> = −0.1mA              | COM'L             | 4.0 |          |       | Volts |

| V <sub>OH</sub>             | Output HIGH Voltage                        | V <sub>CC</sub> = Min                  | TTL                     | I <sub>OH</sub> = -1mA                | MIL               | 2.4 | 3.4      |       | Volts |

|                             |                                            | •                                      | Outputs                 | I <sub>OH</sub> = -2.6mA              | COM'L             | 2.4 | 3.4      |       | Volts |

| V                           | Output I OW Voltage                        | V <sub>CC</sub> = Min                  |                         | I <sub>OL</sub> = 0.1mA MC            | LK <sub>1/2</sub> |     |          | 0.3   | Volts |

| V <sub>OŁ</sub>             | Output LOW Voltage                         | ACC = MIII                             |                         | I <sub>OL</sub> = 16mA TTL            | Outputs           |     |          | 0.5   | Volts |

| V <sub>IH</sub>             | Input HIGH Level                           | Guaranteed In                          | put HIGH Vo             | Itage                                 |                   | 2.0 |          |       | Volts |

| V <sub>IL</sub>             | Input LOW Level                            | Guaranteed In                          | put LOW Vol             | tage                                  |                   |     |          | 0.8   | Volts |

| VI                          | Input Clamp Voltage                        | V <sub>CC</sub> = Min, I <sub>II</sub> | $_{N} = -18 \text{mA}$  | = -18mA                               |                   |     |          | -1.2  | Volts |

| l                           | Input LOW Current                          | V <sub>CC</sub> = Max All              |                         | All Inputs (Except                    | RES)              |     |          | -0.4  | mA    |

| İ                           | input LOW Current                          | $V_{IN} = 0.4V$                        |                         | RES                                   |                   |     |          | -1.0  | mA    |

| l                           | Input HIGH Current                         | V <sub>CC</sub> = Max                  |                         | All Inputs (Except                    | RES)              |     |          | +50   | μΑ    |

| lн                          | · · · · · · · · · · · · · · · · · · ·      | $V_{IN} = 2.7V$                        |                         | RES                                   |                   |     |          | +600  | μΑ    |

| Įį                          | Input HIGH Current at<br>Max Input Voltage | $V_{CC} = Max$<br>$V_{IN} = 5.5V$      |                         | •                                     |                   |     |          | +1.0  | mA    |

| 1                           | Output Short Current                       | V <sub>CC</sub> = Max                  |                         | MCLK <sub>1</sub> , MCLK <sub>2</sub> |                   | -50 |          | -250  | mA    |

| Isc                         | Current (Note 3)                           | ACC - Max                              |                         | Others                                |                   | -40 |          | - 130 | mA    |

|                             |                                            |                                        | Over Oper               | ating Range                           |                   |     |          | 410   | mA    |

| I <sub>CC</sub> Power Suppl | Power Supply Current                       | $V_{CC1} = Max$<br>$V_{CC2} = Max$     | @ T <sub>A</sub> = 70   | 70°C                                  |                   |     |          | 370   | mA    |

|                             |                                            | 1002 /                                 | @ T <sub>C</sub> = 1    | 25°C                                  |                   |     |          | 345   | mA    |

|                             |                                            |                                        | Over Oper               | ating Range                           |                   |     |          | 40    | mA    |

| <b>!</b> -                  | Power Supply Current                       | V <sup>-</sup> = Max                   | @ T <sub>A</sub> = 70°C |                                       |                   |     | 37       | mA    |       |

|                             |                                            |                                        | @ T <sub>C</sub> = 12   | 25°C                                  |                   |     |          | 35    | mA    |

Notes: 1. For conditions shown as Min or Max use the appropriate value specified under DC Characteristics for the applicable device type.

2. Typical limits are at  $V_{CC} = 5.0V$ , 25°C ambient and maximum loading.

Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

Except: X<sub>1</sub>, X<sub>2</sub>, X<sub>3</sub>, AADJ, VIDOUT, VIDOUT.

## **Z8152A SWITCHING CHARACTERISTICS** OVER OPERATING RANGE ( $T_A = 0$ to 70 °C, $V_{CC} = 5.0V \pm 5\%$ , $V^- = 0V$ )

| umber | Description                                                                | Min      | Max   | Units              |    |

|-------|----------------------------------------------------------------------------|----------|-------|--------------------|----|

| 1     | MCLK <sub>1</sub> Period                                                   |          | 100   |                    | ns |

| 2     | CLK <sub>2</sub> Period                                                    |          | 70    |                    | ns |

| 3     | MCLK <sub>1</sub> HIGH (See Note 5)                                        | 4.0V     | 38    |                    | ns |

| 4     | MCLK <sub>1</sub> LOW (See Notes 3 and 5)                                  | 0.3V     | 38    |                    | ns |

| 5     | MCLK <sub>2</sub> HIGH (See Note 6)                                        | 4.0V     | 23    |                    | ns |

| 6     | MCLK <sub>2</sub> LOW (See Notes 3 and 6)                                  | 0.3V     | 23    |                    | ns |

| 7     | Data to MCLK <sub>2</sub> /TCLK <sub>2</sub> RE (See Note 1)               |          | 20    |                    | ns |

| 8     | MCLK <sub>2</sub> /TCLK <sub>2</sub> to Data Not Valid                     |          | 0     |                    | ns |

| 9     | VSYNC/HSYNC to MCLK <sub>1</sub> RE Setup (SSEL = HIGH)                    |          | 20    |                    | ns |

| 10    | VSYNC/HSYNC to MCLK <sub>2</sub> RE Setup (SSEL = LOW)                     |          | 20    |                    | ns |

| 11    | TCLK <sub>2</sub> RE to MCLK <sub>2</sub> RE Delay                         |          |       | 8                  | ns |

| 12    | TCLK <sub>2</sub> FE to MCLK <sub>2</sub> FE Delay                         |          | et De | 12                 | ns |

| 13    | MCLK <sub>1</sub> to VSLD, HSLD (SSEL = HIGH)                              | <b>6</b> | VAY   | 6 4 T <sub>D</sub> | ns |

| 14    | TCLK <sub>2</sub> to VSLD, HSLD (SSEL = LOW)                               | . 6      | 140 V | 6 + T <sub>D</sub> | ns |

| 15    | DD(0:7) to TCLK <sub>2</sub> FE                                            | MARCON   | 20    |                    | ns |

| 16    | TCLK <sub>2</sub> RE to VID <sub>1</sub> VID <sub>2</sub> VAL (See Note 2) | MAN      | 3.0   | 6 + T <sub>D</sub> | ns |

| 17    | BLANK FE to MCLK <sub>2</sub> RE Setup (SSEL = LOW)                        | M M to   | 20    |                    | ns |

| 18    | BLANK FE to MCLK, FE Setup (SSEL = HIGH)                                   | (A)      | 20    | i i                | ns |

| 19    | BLANK RE to MCLK, RE Setup (SSEL = HIGH)                                   |          | 20    |                    | ns |

| 20    | BLANK RE to MCLK RE Setup (SSEL LOW)                                       |          | 20    |                    | ns |

| 22    | VID <sub>1</sub> to VID <sub>2</sub> SkeW                                  |          | -5    | +5                 | ns |

| 24    | EXTOCLK IO MOLKE                                                           |          |       | 20                 | ns |

| 25    | EXTOCIK 10 TCLK2                                                           |          |       | 13                 | ns |

| 26    | EXTOCLK to MCLK <sub>2</sub>                                               |          |       | 23                 | ns |

| 27    | EXTOCLK to VID <sub>1</sub> /VID <sub>2</sub>                              |          |       | 13                 | ns |

| 28    | EXTDCLK to HSDLD/VSDLD (SSEL HI)                                           |          | -     | 13                 | ns |

| 29    | EXTDCLK to HSDLD/VSDLD (SSEL LO)                                           |          |       | 13                 | ns |

| 30    | EXTDCLK to Data in Setup                                                   |          | 9     |                    | ns |

| 31    | EXTDCLK to Data Not Valid Hold                                             |          | 11    |                    | ns |

| 32    | EXTDCLK to H/V SYNC Setup                                                  |          | 10    |                    | ns |

| 33    | EXTDCLK Period                                                             | 1        | 16.6  |                    | ns |

| 34    | EXTDCLK LOW Cycle                                                          |          | 5     |                    | ns |

| 35    | EXTDCLK HIGH Cycle                                                         |          | 5.0   |                    | ns |

| 36    | Reset Pulse Width (High)                                                   |          | 10.0  |                    | ns |

| 37    | Reset Low to EXTDCLK Setup                                                 |          | 8.0   |                    | ns |

Notes: 1. Data includes CBLANK, FORE, REV, FS, DD<sub>0</sub>-DD<sub>8</sub>, TB0, TB1, BS, CLK<sub>1</sub>DR, CLK<sub>2</sub>DR, DW.

2. First Pixel of character. T<sub>D</sub> is pixel period as defined by oscillator frequency.

3. Max undershoot on these outputs is guaranteed to be -0.3V.

T<sub>D</sub> is the dot clock period.

Guaranteed to 100ns MCLK<sub>1</sub> cycle time.

Guaranteed to 70ns MCLK<sub>2</sub> cycle time (even divide ratio only).

# ZILOG INC 72 **Z8153A SWITCHING CHARACTERISTICS**

OVER OPERATING RANGE ( $T_A = 0$  to 70 °C,  $V_{CC} = 5.0 V \pm 5\%$ ,  $V^- = -5.25 V \pm 5\%$ )

| lumber | Description                                                                |       | Min                                | Max    | Units |

|--------|----------------------------------------------------------------------------|-------|------------------------------------|--------|-------|

| 1      | MCLK <sub>1</sub> Period                                                   |       | 100                                |        | ns    |

| 2      | CLK <sub>2</sub> Period                                                    | -     | 70                                 |        | ns    |

| 3      | MCLK <sub>1</sub> HIGH (See Note 5)                                        | 4.0V  | 38                                 |        | ns    |

| 4      | MCLK <sub>1</sub> LOW (See Notes 3 and 5)                                  | 0.3V  | 38                                 |        | ns    |

| 5      | MCLK <sub>2</sub> HIGH (See Note 6)                                        | 4.0V  | 23                                 |        | ns    |

| 6      | MCLK <sub>2</sub> LOW (See Notes 3 and 6)                                  | 0.3V  | 23                                 |        | ns    |

| 7      | Data to MCLK <sub>2</sub> /TCLK <sub>2</sub> RE (See Note 1)               |       | 20 +T <sub>D</sub><br>(See Note 4) |        | ns    |

| 8      | MCLK <sub>2</sub> /TCLK <sub>2</sub> to Data Not Valid                     |       | 0                                  |        | ns    |

| 9      | VSYNC/HSYNC to MCLK <sub>1</sub> RE Setup (SSEL = HIGH)                    |       | 20 +T <sub>D</sub>                 | . 4    | ns    |

| 10     | VSYNC/HSYNC to MCLK <sub>2</sub> RE Setup (SSEL = LOW)                     |       | 20 +T <sub>D</sub>                 |        | ns    |

| 11     | TCLK <sub>2</sub> RE to MCLK <sub>2</sub> RE Delay                         |       |                                    | 12 8 W | ns    |

| 12     | TCLK <sub>2</sub> FE to MCLK <sub>2</sub> FE Delay                         |       | A. Ve                              | 12     | ns    |

| 13     | MCLK <sub>1</sub> to VSLD, HSLD (SSEL = HIGH)                              | €     | VAV                                | 6      | ns    |

| 14     | TCLK <sub>2</sub> to VSLD, HSLD (SSEL = LOW)                               |       | W.                                 | ° 6    | ns    |

| 15     | DD(0:7) to TCLK <sub>2</sub> FE                                            | A LON | 20 +T <sub>D</sub>                 |        | пѕ    |

| 16     | TCLK <sub>2</sub> RE to VID <sub>1</sub> VID <sub>2</sub> VAL (See Note 2) | WW W  |                                    | 6      | ns    |

| 17     | BLANK FE to MCLK <sub>2</sub> RE Setup (SSEL = LOW)                        |       | 20 +T <sub>D</sub>                 |        | ns    |

| 18     | BLANK FE to MCLK <sub>1</sub> FE Setup (SSEL = HIGH)                       | W.    | 20 +T <sub>D</sub>                 |        | ns    |

| 19     | BLANK RE to MCLK, RE Setup (SSEL = HIGH)                                   |       | 20 +T <sub>D</sub>                 |        | ns    |

| 20     | BLANK RE to MCLK RE Setup (SSEL & LOW)                                     |       | 20 +T <sub>D</sub>                 |        | ns    |

| 21     | VID <sub>1</sub> to VID <sub>2</sub> Skew                                  |       | -2                                 | +2     | ns    |

| 24     | EXTOCLK to MCLK                                                            |       |                                    | 20     | ns    |

| 25     | EXTOCLK 10 TCLK2                                                           |       |                                    | 10     | ns    |

| 26     | EXTOCLK to MCLK2                                                           |       |                                    | 23     | ns    |

| 27     | EXTDCLK to VID <sub>1</sub> /VID <sub>2</sub>                              |       |                                    | 8      | ns    |

| 28     | EXTDCLK to HSDLD/VSDLD (SSEL HI)                                           |       |                                    | 10     | ns    |

| 29     | EXTDCLK to HSDLD/VSDLD (SSEL LO)                                           |       |                                    | 10     | ns    |

| 30     | EXTDCLK to Data in Setup                                                   |       | 9                                  |        | ns    |

| 31     | EXTDCLK to Data Not Valid Hold                                             |       | 11                                 |        | ns    |

| 32     | EXTDCLK to H/V SYNC Setup                                                  |       | 10                                 |        | ns    |

| 33     | EXTDCLK Period                                                             |       | 10                                 |        | ns    |

| 34     | EXTDCLK LOW Cycle                                                          |       | 5                                  |        | ns    |

| 35     | EXTDCLK HIGH Cycle                                                         |       | 3.5                                |        | ns    |

| 36     | Reset Pulse Width (High)                                                   |       | 10.0                               |        | ns    |

| 37     | Reset Low to EXTDCLK Setup                                                 |       | 8.0                                |        | ns    |

Notes: 1. Data includes CBLANK, FORE, REV, FS, DD<sub>0</sub> – DD<sub>8</sub>, TB0, TB1, BS, CLK<sub>1</sub>DR, CLK<sub>2</sub>DR, DW.

2. First Pixel of character. T<sub>D</sub> is pixel period as defined by oscillator frequency.

3. Max undershoot on these outputs is guaranteed to be – 0.3V.

4. T<sub>D</sub> is the dot clock period.

5. Guaranteed to 100ns MCLK<sub>1</sub> cycle time.

6. Guaranteed to 70ns MCLK<sub>2</sub> cycle time (even divide ratio only).

13

# 9984043 ZILOG INC

# ANALOG ELECTRICAL CHARACTERISTICS (see notes)

The following conditions apply unless otherwise specified:

COM'L

$$T_A = 0$$

to  $+70^{\circ}$ C  $V_{CC} = 5.0V \pm 5\%$  (Min = 4.75V Max = 5.25V) Am8152A:  $V^- = 0V \cdot Z8153A$ :  $V^- = -5.2V \pm 5\%$  MIL  $T_C = -55$  to  $+125^{\circ}$ C  $V_{CC} = 5.0V \pm 10\%$  (Min = 4.50V Max = 5.50V)  $V^- = 0V$   $V^- = -5.2V \pm 10\%$

| Grey  |                  |                  |                    | VID     | VIDOUT  |         | OUT     |

|-------|------------------|------------------|--------------------|---------|---------|---------|---------|

| Level | VID <sub>2</sub> | VID <sub>1</sub> |                    | Min (%) | Max (%) | Min (%) | Max (%) |

| X     | 1                | ı                | l <sub>White</sub> | 0       | 0       | 100     | 100     |

| ı     | ı                | 0                | I <sub>Grey1</sub> | 37      | 44      | 56      | 63      |

| 0     | 1                | 0                | I <sub>Grey2</sub> | 45      | 53      | 47      | 55      |

| x     | 0                | 1                | I <sub>Black</sub> | 90.5    | 92.5    | 7.5     | 9.5     |

| х     | 0                | 0                | IBlank             | 100     | 100     | 0       | 0       |

03888C-3

#### **DRIFT OVER OPERATING CONDITIONS** (For particular part)

| Grey<br>Level | VID <sub>2</sub> | VID <sub>1</sub> |                    | VIDOUT | VIDOUT |

|---------------|------------------|------------------|--------------------|--------|--------|

| ×             | ı                | i                | lWhite             | 0      | 0      |

| ı             | 1                | 0                | I <sub>Grey1</sub> | 2% Max | 2% Max |

| 0             | 1                | 0                | I <sub>Grey2</sub> | 2% Max | 2% Max |

| X             | 0                | 1                | IBlack             | 1% Max | 1% Max |

| x             | 0                | 0                | IBlank             | 0      | 0      |

#### Notes:

- Test Condition: Normal l<sub>White</sub> for VIDOUT + 13.3mA.

Positive current flowing into VIDOUT/VIDOUT.

- 3. tg, tr = 5ns Max.

4. VIDOUT output currents normalized to l<sub>White</sub>. VIDOUT output cur-

- rents normalized to I<sub>Blank</sub>.

5. Min/Max values for VIDOUT and VIDOUT account for variation of different devices.

- 6. Z8152A

- V Pull-Up:  $8.5V \ge V$  Pull-Up  $\Rightarrow$   $^{\bullet}V_{CC}$  VIDOUT/VIDOUT: (V Pull-Up)  $\Rightarrow$  VIDOUT/VIDOUT  $\Rightarrow$  (V<sub>CC</sub> 1V)

- 7. Z8153A

- V Pull-Up:  $3.5V \ge V$  Pull-Up  $\ge 0V$  VIDOUT/VIDOUT:  $(V \text{ Pull-Up}) \ge V\text{IDOUT/VIDOUT} \ge -1.0V$

03888C-20

Note 1. See pin description on page 3.

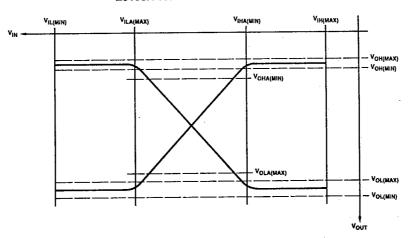

# **Z8153A 10K ECL SPECIFICATIONS**

#### DC CHARACTERISTICS

| ·                                        | Parameters                                                               | Test<br>Conditions                                  | −55°C                | o°C                     | 25°C                 | 70°C                  | 125°C                | Unit           |

|------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------|----------------------|-------------------------|----------------------|-----------------------|----------------------|----------------|

| 10K ECL<br>Outputs                       | VOH (Max)<br>VOH (Min)<br>VOHA (Min)                                     | 50Ω<br>to -2V                                       | 880<br>1080<br>1100  | 840<br>1000<br>1020     | 780<br>930<br>950    | -720<br>-900<br>-920  | -630<br>-825<br>-845 | mV<br>mV<br>mV |

| VID <sub>1</sub> and<br>VID <sub>2</sub> | V <sub>OLA</sub> (Max)<br>V <sub>OL</sub> (Max)<br>V <sub>OL</sub> (Min) | 50Ω<br>to -2V                                       | 1635<br>1655<br>1920 | -1645<br>-1665<br>-1870 | 1600<br>1620<br>1850 | -1605<br>1625<br>1830 | 1525<br>1545<br>1820 | mV<br>mV<br>mV |

| 10K ECL<br>Input                         | V <sub>IH (Max)</sub><br>V <sub>IHA (Min)</sub>                          |                                                     | -880<br>1255         | 840<br>1145             | -780<br>1105         | -720<br>-1045         | -630<br>-1000        | mV<br>mV       |

| EXTDCLK                                  | V <sub>ILA</sub> (Max)<br>V <sub>IL</sub> (Min)                          |                                                     | -1510<br>-1920       | -1490<br>-1870          | -1475<br>-1850       | 1450<br>1830          | -1400<br>-1820       | mV<br>mV       |

|                                          | liн                                                                      | V- = Max<br>V <sub>IN</sub> = V <sub>IH</sub> (Max) | 200                  | 200                     | 200                  | 200                   | 200                  | μА             |

|                                          | l <sub>IL</sub>                                                          | $V^- = Max$<br>$V_{IN} = V_{IL (Min)}$              | 150                  | 150                     | 150                  | 150                   | 150                  | μΑ             |

# **ORDERING INFORMATION**

Z8152A/53A VSC 48-pin DIP Z8152A CS Z8153A CS

#### Codes

First letter is for package; second letter is for temperature.

C = Ceramic DIP

P = Plastic DIP

L = Ceramic LCC

V = Plastic PCC

= Protopack

= Low Profile Protopack

DIP = Dual-In-Line Package LCC = Leadless Chip Carrier

PCC = Plastic Chip Carrier (Leaded)

FLOW

B = 883 Class B

TEMPERATURE

S = 0°C to +70°C

E = -40 °C to +85 °C

M\*= -55°C to +125°C

Example: PS is a plastic DIP, 0°C to +70°C.

\*For Military Orders, contact your local Zilog Sales Office for Military Electrical Specifications.

#### **PACKAGE INFORMATION**

NOTE: Package dimensions are given in inches. To convert to millimeters, multiply by 25.4.