03E 08303

Z8440/1/2/4 Military Z80<sup>®</sup> SIO Serial Input/Output Controller

Zilog

Military Electrical Specification

July 1985

## **FEATURES**

- Two independent full-duplex channels, with separate control and status lines for modems or other devices.

- Data rates of 0 to 500K bits/second in the x1 clock mode with a 2.5 MHz clock (Z80 SIO), or 0 to 800K bits/second with a 4.0 MHz clock (Z80A SIO).

- Asynchronous protocols: everything necessary for complete messages in 5, 6, 7, or 8 bits/character. Includes variable stop bits and several clock-rate multipliers; break generation and detection; parity; overrun and framing error detection.

- Synchronous protocols: everything necessary for complete bit- or byte-oriented messages in 5, 6, 7, or 8 bits/character, including IBM Bisync, SDLC, HDLC, CCITT-X.25 and others. Automatic CRC generation/ checking, sync character and zero insertion/deletion, abort generation/detection, and flag insertion.

- Receiver data registers quadruply buffered, transmitter registers doubly buffered.

- Highly sophisticated and flexible daisy-chain interrupt vectoring for interrupts without external logic.

# **GENERAL DESCRIPTION**

The Z80 SIO Serial Input/Output Controller is a dual-channel data communication interface with extraordinary versatility and capability. Its basic functions as a serial-to-parallel, parallel-to-serial converter/controller can be programmed by a CPU for a broad range of serial communication applications.

The device supports all common asynchronous and synchronous protocols, byte or bit-oriented, and performs all of the functions traditionally done by UARTs, USARTs, and synchronous communication controllers combined, plus additional functions traditionally performed by the CPU. Moreover, it does this on two fully-independent channels, with an exceptionally sophisticated interrupt structure that

allows very fast transfers.

Full interfacing is provided for CPU or DMA control. In addition to data communication, the circuit can handle virtually all types of serial I/O with fast, or slow, peripheral devices. While designed primarily as a member of the Z80 family, its versatility makes it well suited to many other CPUs.

The Z80 SIO is an n-channel silicon-gate depletion-load device packaged in a 40-pin ceramic DIP. It uses a single +5V power supply and the standard Z80 family single-phase clock. The Z8444 is packaged in a 44-pin ceramic LCC.

03E 08304 I

T-75-37-07

# TIMING

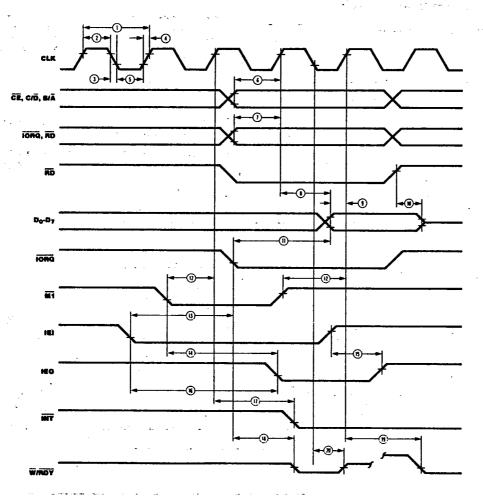

The SIO must have the same clock as the CPU (same phase and frequency relationship, not necessarily the same driver).

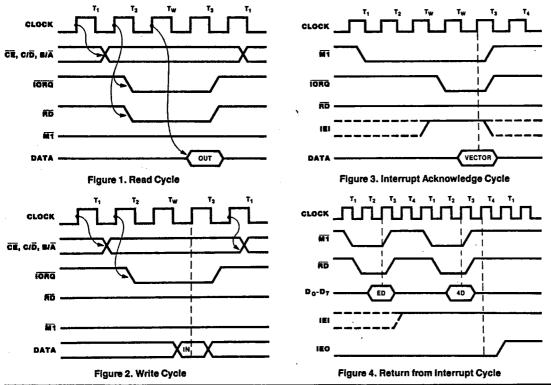

**Read Cycle.** The timing signals generated by a Z80 CPU input instruction to read a data or status byte from the SIO are illustrated in Figure 1.

**Write Cycle.** Figure 2 illustrates the timing and data signals generated by a Z80 CPU output instruction to write a data or control byte into the SIO.

interrupt-Acknowledge Cycle. After receiving an interrupt-request signal from an SIO (INT pulled Low), the Z80 CPU sends an interrupt-acknowledge sequence, M1 cow and IORQ Low, a few cycles later (Figure 3).

The SIO contains an internal daisy-chained interrupt structure for prioritizing nested interrupts for the various functions of its two channels, and this structure can be used within an external user-defined daisy chain that prioritizes several peripheral circuits.

The IEI of the highest-priority device is terminated High. A device that has an interrupt pending or under service forces its IEO Low. For devices with no interrupt pending or under service, IEO = IEI.

To insure stable conditions in the daisy chain, all interrupt status signals are prevented from changing while  $\overline{\text{M1}}$  is Low. When  $\overline{\text{IOAQ}}$  is Low, the highest priority interrupt requestor

(the one with IEI High) places its interrupt vector on the data bus and sets its internal interrupt-under-service latch.

Return From Interrupt Cycle. Figure 4 illustrates the return from interrupt cycle. Normally, the Z80 CPU issues a Return From Interrupt (RETI) instruction at the end of an interrupt service routine. RETI is a 2-byte opcode (ED-4D) that resets the interrupt-under-service latch in the SIO to terminate the interrupt that has just been processed. This is accomplished by manipulating the daisy chain in the following way.

The normal daisy-chain operation can be used to detect a pending interrupt; however, it cannot distinguish between an interrupt under service and a pending unacknowledged interrupt of a higher priority. Whenever ED is decoded, the daisy chain is modified by forcing High the IEO of any interrupt that has not yet been acknowledged. Thus the daisy chain identifies the device presently under service as the only one with an IEI High and an IEO Low. If the next opcode byte is 4D, the interrupt-under-service latch is reset.

The ripple time of the interrupt daisy chain (both the High-to-Low and the Low-to-High transitions) limits the number of devices that can be placed in the daisy chain. Ripple time can be improved with carry-look-ahead, or by extending the interrupt-acknowledge cycle. For further information about techniques for increasing the number of daisy-chained devices, refer to the Z80 CPU Product Specification in this document.

# 3

# 9984043 ZILOG INC

03E 08305 D

T-75-37-07

# **ABSOLUTE MAXIMUM RATINGS**

Guaranteed by characterization/design.

| Voltages on all pins with respect | ·              |

|-----------------------------------|----------------|

| to GND                            | 0.3V to +7\    |

| Operating Case Temperature        | 55°C to +125°C |

| Storage Temperature Range         | 65°C to +150°C |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# STANDARD TEST CONDITIONS

The DC Characteristics and Capacitance sections listed below apply for the following standard test conditions, unless otherwise noted.

Military Operating Temperature Range (T<sub>C</sub>) -55°C to +125°C

Standard Military Test Condition +4.5V ≤ V<sub>CC</sub> ≤ +5.5V All voltages are referenced to GND (0V). Positive current flows into the referenced pin.

All AC parameters assume a load capacitance of 100 pf. AC output timing measurements are referenced to 1.5 volts.

# DC CHARACTERISTICS

| Symbol | Parameter                         | Min                    | Max                   | Unit     | Test Condition               |

|--------|-----------------------------------|------------------------|-----------------------|----------|------------------------------|

| VILC   | Clock Input Low Voltage           | -0.3c                  | +0.45a                | ٧        |                              |

| VIHC   | Clock Input High Voltage          | V <sub>CC</sub> - 0.6a | V <sub>CC</sub> +0.3b | ٧        |                              |

| VIL    | Input Low Voltage                 | -0.3°                  | +0.8a                 | ٧        | * *                          |

| VIH    | Input High Voltage                | +2.2a                  | Vccb                  | ٧        |                              |

| VOL    | Output Low Voltage                |                        | + 0.4b                | ٧        | $l_{OL} = 2.0  mA$           |

| VOH    | Output High Voltage               | +2.4b                  | est si e de e         | <b>V</b> | $I_{OH} = -250 \mu A$        |

| ILI    | Input Leakage Current             |                        | ± 10ª                 | μA       | $V_{IN} = 0$ to $V_{CC}$     |

| loL    | 3-State Output Leakage Current in | Float                  | ± 10a                 | μΑ       | $V_{OUT} = 0.4V$ to $V_{CC}$ |

|        | SYNC Pin Leakage Current          |                        | +10/-40a              | μA       | 0 < VIN < VCC                |

| IL(SY) | Power Supply Current              |                        | 150a                  | mA       |                              |

Over specified temperature and voltage range.

## CAPACITANCE

| Symbol | Parameter          | Min | Max             | Unit   |

|--------|--------------------|-----|-----------------|--------|

|        |                    |     | 40°             | pf     |

| C .    | Clock Capacitance  |     | 5C              | ٠.     |

| CIN    | Input Capacitance  |     | -               | pt<br> |

| COUT   | Output Capacitance |     | 15 <sup>C</sup> | pf     |

Over specified temperature range; f = 1 MHz. Unmeasured pins returned to ground.

Parameter Test Status:

- a Tested

- b Guaranteed

- C Guaranteed by Characterization/Design

03E 08306 D

**AC CHARACTERISTICS TIMING**

T-75-37-07

03E 08307

# **AC CHARACTERISTICS\***

T- 75- 37- 07

| •      |             | and the supplied a section of the pro-       |                  | 0 SIO            | Z80              | A SIO            |

|--------|-------------|----------------------------------------------|------------------|------------------|------------------|------------------|

| Number | Symbol      | Parameter                                    | Min              | Max              | Min              | Max              |

| 1      | TcC         | Clock Cycle Time                             | 400a             | 4000b            | 250a             | 4000             |

| 2      | TwCh        | Clock Width (High)                           | 170b             | 2000b            | 105b             | 2000             |

| 3      | TfC         | Clock Fall Time                              |                  | 30p              |                  | 301              |

| 4      | TiC         | Clock Rise Time                              | •                | 30b              |                  | 30               |

| 5      | TwCi        | Clock Width (Low)                            | 170 <sup>b</sup> | 2000b            | 105 <sup>b</sup> | 2000t            |

| 6.     | TsAD(C)     | CE, C/D, B/A to Clock † Setup Time           | 160a             | 4 · 4200.        | 145a             |                  |

| 7      | TsCS(C)     | IORQ, RD to Clock † Setup Time               | 240a             | <b>*</b>         | 115a             |                  |

| Ė      | TdC(DO)     | Clock † to Data Out Delay                    |                  | 240a             |                  | 220              |

| ·9     | TsDI(C)     | Data In to Clock † Setup (Write or MT Cycle) | 50a              |                  | 50a              |                  |

| 10     | TdRD(DOz)   | RD to Data Out Float Delay                   |                  | 230b             |                  | 110 <sup>t</sup> |

| 11     | TdlO(DOI)   | IORQ ↓ to Data Out Delay (INTACK Cycle)      |                  | 340b             | <del></del>      | 160              |

| 12     | TsM1(C)     | M1 to Clock † Setup Time                     | 210a             |                  | 90a              |                  |

| 13     | TsiEl(IO)   | IEI to IORQ ↓ Setup Time (INTACK Cycle)      | 200b             |                  | 140b             |                  |

| 14     | TdM1(IEO)   | M1 ↓ to IEO ↓ Delay (interrupt before M1)    |                  | 300p             |                  | 190 <sup>t</sup> |

| 15     | TdlEl(lEOr) | IEI † to IEO † Delay (after ED decode)       | -                | 150b             |                  | 100 <sup>t</sup> |

| 16     | TdlEl(IEOf) | IEI ∔ to IEO ∔ Delay                         |                  | 150a             |                  | 100              |

| - 17   | TdC(INT)    | Clock f to INT I Delay                       |                  | 200a             | •                | 200              |

| 18     | TdIO(W/RWf) | IORQ ↓ or CE ↓ to W/RDY ↓ Delay (Wait Mode)  |                  | 300b             |                  | 210 <sup>t</sup> |

| 19     | TdC(W/RRf)  | Clock † to W/RDY ↓ Delay (Ready Mode)        |                  | 120 <sup>b</sup> |                  | 120              |

| 20     | TdC(W/RWz)  | Clock                                        |                  | 150b             |                  | 130 <sup>t</sup> |

| 21     | Th          | Any unspecified Hold when Setup is specified | ΟÞ               |                  | 0p.              | .50              |

<sup>\*</sup>Units in nanoseconds (ns).

Parameter Test Status:

a Tested b Guaranteed

<sup>©</sup> Guaranteed by Characterization/Design

03E 08308 D

AC CHARACTERISTICS TIMING (Continued)

T-75-37-07

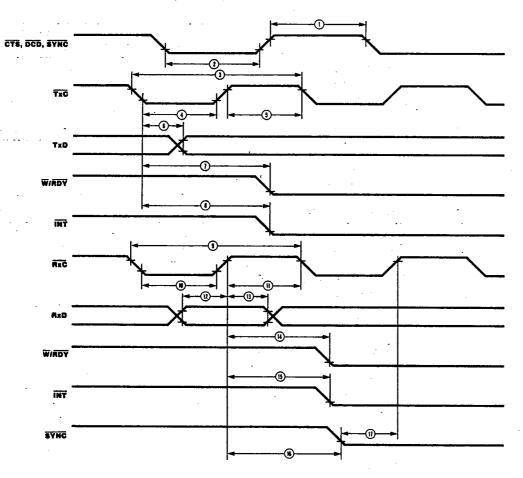

# AC CHARACTERISTICS (Continued)

9984043 ZILOG INC

T-75-37-07

|        |              |                                             |                   | SIO             | Z80A             | SIO             |       |

|--------|--------------|---------------------------------------------|-------------------|-----------------|------------------|-----------------|-------|

| Number | Symbol       | Parameter                                   | Min               | Max             | Min              | Max             | Notes |

| 1      | TwPh         | Pulse Width (High)                          | 200b              |                 | 200b             |                 | 2     |

| 2      | TwPI         | Pulse Width (Low)                           | 200b              |                 | 200b             |                 | 2     |

| 3      | TcTxC        | TxC Cycle Time                              | 400b              | ∞b              | 400b             | ∞p              | 2     |

| 4      | TwTxCl       | TxC Width (Low)                             | 180 <sup>b</sup>  | ∞b              | 180b             | ∞b              | 2     |

| 5      | TwTxCh       | TxC Width (High)                            | 180 <sup>b</sup>  | ∞b              | 180 <sup>b</sup> | ∞b              | 2     |

| 6      | TdTxC(TxD)   | TxC ↓ to TxD Delay (x1 Mode)                |                   | 400a            |                  | 300a            | 2     |

| 7      | TdTxC(W/RRf) | TxC + to W/RDY + Delay (Ready Mode)         | 5b                | 9b              | 5b               | gb              | 1     |

| 8      | TdTxC(INT)   | TxC + to INT + Delay                        | 5b                | 9ь              | 5b               | 9ь              | 1     |

| 9      | TcRxC        | RxC Cycle Time                              | 400 <sup>b</sup>  | ∞b              | 400b             | ∞b              | 2     |

| 10     | TwRxCl       | RxC Width (Low)                             | 180 <sup>b</sup>  | doo             | 180 <sup>b</sup> | ∞b              | 2     |

| 11     | TwRxCh       | RxC Width (High)                            | 180 <sup>b</sup>  | ∞b              | 180b             | ∞b              | 2     |

| 12     | TsRxD(RxC)   | RxD to RxC t Setup Time (x1 Mode)           | Ор                |                 | Ор               | _               | 2     |

| 13     | ThRxD(RxC)   | RxC t to RxD Hold Time (x1 Mode)            | 140ª              |                 | 140a             |                 | . 2   |

| 14     | TdRxC(W/RRf) | RxC to W/RDY + Delay (Ready Mode)           | 10 <sup>b</sup>   | 13 <sup>b</sup> | 10 <sup>b</sup>  | 13 <sup>b</sup> | 1     |

| 15     | TdRxC(INT)   | RxC t to INT ↓ Delay                        | 10 <sup>b</sup>   | 13b             | 10 <sup>b</sup>  | 13 <sup>b</sup> | 1     |

| 16     | TdRxC(SYNC)  | RxC to SYNC + Delay (Output Modes)          | 4a                | 7a              | 4a               | 7a              | 1     |

| 17     | TsSYNC(RxC)  | SYNC I to RxC t Setup (External Sync Modes) | -100 <sup>b</sup> |                 | -100b            |                 | 2     |

In all modes, the System Clock rate must be at least five times the maximum data rate. RESET must be active a minimum of one complete clock cycle.

1. Units equal to System Clock Periods.

2. Units in nanoseconds (ns).

Parameter Test Status:

a Tested

b Guaranteed

C Guaranteed by Characterization/Design

03E 08310

# T-75-37-07

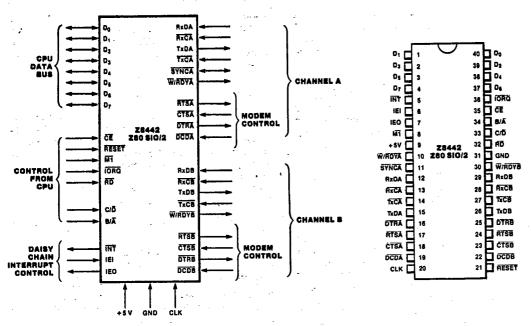

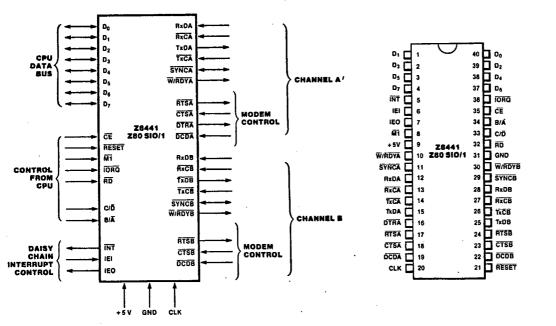

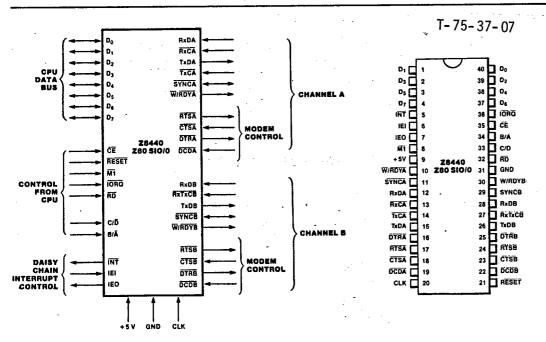

#### PIN DESCRIPTION

Figures 5 through 10 illustrate the three 40-pin configurations (bonding options) available in the SIO. The constraints of a 40-pin package make it impossible to bring out the Receive Clock (RxC), Transmit Clock (TxC), Data Terminal Ready (DTR) and Sync (SYNC) signals for both channels. Therefore, either Channel B lacks a signal or two signals are bonded together:

- Z80 SIO/2 lacks SYNCB

- Z80 SIO/1 lacks DTRB

- Z80 SIO/0 has all four signals, but TxCB and RxCB are bonded together

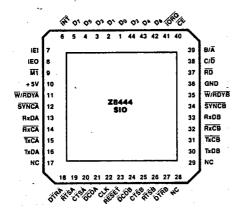

The 44-pin package, the Z80 SIO/4, has all options (Figure

The first bonding option above (SIO/2) is the preferred version for most applications. The pin descriptions are as

B/A. Channel A or B Select (input, High selects Channel B). This input defines which channel is accessed during a data transfer between the CPU and the SiO. Address bit  $\overline{\mathsf{A}_0}$  from the CPU is often used for the selection function.

C/D. Control or Data Select (input, High selects Control). This input defines the type of information transfer performed between the CPU and the SIO. A High at this input during a CPU write to the SIO causes the information on the data bus to be interpreted as a command for the channel selected by B/A. A Low at C/D means that the information on the data bus is data. Address bit A<sub>1</sub> is often used for this function.

CE. Chip Enable (Input, active Low). A Low level at this input enables the SIO to accept command or data input from the CPU during a write cycle, or to transmit data to the CPU during a read cycle.

CLK. System Clock (input). The SIO uses the standard Z80 System Clock to synchronize internal signals. This is a single-phase clock.

CTSA, CTSB. Clear To Send (inputs, active Low). When programmed as Auto Enables, a Low on these inputs enables the respective transmitter. If not programmed as Auto Enables, these inputs may be programmed as general-purpose inputs. Both inputs are Schmitt-trigger buffered to accommodate slow-risetime signals. The SIO detects pulses on these inputs and interrupts the CPU on both logic level transitions. The Schmitt-trigger buffering does not guarantee a specified noise-level margin.

Do-D7. System Data Bus (bidirectional, 3-state). The system data bus transfers data and commands between the CPU and the Z80 SIO. Do is the least significant bit.

DCDA, DCDB. Data Carrier Detect (inputs, active Low). These pins function as receiver enables if the SIO is programmed for Auto Enables; otherwise they may be used as general-purpose input pins. Both pins are Schmitt-trigger buffered to accommodate slow-risetime signals. The SIO

detects pulses on these pins and interrupts the CPU on both logic level transitions. Schmitt-trigger buffering does not guarantee a specific noise-level margin.

DTRA, DTRB. Data Terminal Ready (outputs, active Low). These outputs follow the state programmed into the Z80 SIO. They can also be programmed as general-purpose

In the Z80 SIO/1 bonding option, DTRB is omitted.

IEI. Interrupt Enable In (input, active High). This signal is used with IEO to form a priority daisy chain when there is more than one interrupt-driven device. A High on this line indicates that no other device of higher priority is being serviced by a CPU interrupt service routine.

IEO. Interrupt Enable Out (output, active High). IEO is High only if IEI is High and the CPU is not servicing an interrupt from this SIO. Thus, this signal blocks lower priority devices from interrupting while a higher priority device is being serviced by its CPU interrupt service routine.

INT. Interrupt Request (output, open drain, active Low). When the SIO is requesting an interrupt, it pulls INT Low.

IORQ. Input/Output Request (input from CPU, active Low). IORQ is used in conjunction with B/A, C/D, CE, and RD to transfer commands and data between the CPU and the SIO. When CE, RD, and IORQ are all active, the channel selected by B/A transfers data to the CPU (a read operation). When CE and IORQ are active, but RD is inactive, the channel selected by B/A is written to by the CPU with either data or control information as specified by C/D. As mentioned previously, if IORQ and M1 are active simultaneously, the CPU is acknowledging an interrupt and the SIO automatically places its interrupt vector on the CPU data bus if it is the highest priority device requesting an interrupt.

M1. Machine Cycle One (input from Z80 CPU, active Low). When  $\overline{\text{M1}}$  is active and  $\overline{\text{RD}}$  is also active, the Z80 CPU is fetching an instruction from memory; when M1 is active while IORQ is active, the SIO accepts M1 and IORQ as an interrupt acknowledge if the SIO is the highest priority device that has interrupted the Z80 CPU.

RxCA, RxCB. Receiver Clocks (inputs). Receive data is sampled on the rising edge of RxC. The Receive Clocks may be 1, 16, 32, or 64 times the data rate in asynchronous modes. These clocks may be driven by the Z80 CTC Counter Timer Circuit for programmable baud rate generation. Both inputs are Schmitt-trigger buffered; no noise level margin is specified.

In the Z80 SIO/0 bonding option, RxCB is bonded together with TxCB.

RD. Read Cycle Status (input from CPU, active Low). If RD is active, a memory or I/O read operation is in progress. RD is used with B/A, CE, and IORQ to transfer data from the SIO to the CPU.

T-75-37-07

03E 08311

D

RxDA, RxDB. Receive Data (inputs, active High). Serial data at TTL levels.

**RESET.** Reset (input, active Low). A Low RESET disables both receivers and transmitters, forces TxDA and TxDB marking, forces the modem controls High, and disables all interrupts. The control registers must be rewritten after the SIO is reset and before data is transmitted or received.

RTSA, RTSB. Request To Send (outputs, active Low). When the RTS bit in Write Register 5 is set, the RTS output goes Low. When the RTS bit is reset in the Asynchronous mode, the output goes High after the transmitter is empty. In Synchronous modes, the RTS pin strictly follows the state of the RTS bit. Both pins can be used as general-purpose outputs.

SYNCA, SYNCB. Synchronization (bidirectional, active Low). These pins can act either as inputs or outputs. In the asynchronous receive mode, they are inputs similar to CTS and DCD. In this mode, the transitions on these lines affect the state of the Sync/Hunt status bits in Read Register 0, but have no other function. In the External Sync mode, these lines also act as inputs. When external synchronization is achieved, SYNC must be driven Low on the second rising edge of RxC after that rising edge of RxC on which the last bit of the sync character was received. In other words, after the sync pattern is detected, the external logic must wait for two full Receive Clock cycles to activate the SYNC input. Once SYNC is forced Low, it should be kept Low until the CPU informs the external synchronization detect logic that synchronization has been lost or a new message is about to start. Character assembly begins on the rising edge of RxC

that immediately precedes the falling edge of SYNC in the External Sync mode.

In the internal synchronization mode (Monosync and Bisync), these pins act as outputs that are active during the part of the receive clock ( $\overline{\text{RxC}}$ ) cycle in which sync characters are recognized. The sync condition is not latched, so these outputs are active each time a sync pattern is recognized, regardless of character boundaries.

In the Z80 SIO/2 bonding option, SYNCB is omitted.

TxCA, TxCB. Transmitter Clocks (inputs). In asynchronous modes, the Transmitter Clocks may be 1, 16, 32, or 64 times the data rate; however, the clock multiplier must be the same for the transmitter and the receiver. The Transmit Clock inputs are Schmitt-trigger buffered for relaxed rise- and fall-time requirements; no noise level margin is specified. Transmitter Clocks may be driven by the Z80 CTC Counter Timer Circuit for programmable baud rate generation.

In the Z80 SiO/0 bonding option,  $\overline{\text{TxCB}}$  is bonded together with  $\overline{\text{RxCB}}$ .

**TxDB.** *Transmit Data* (outputs, active High). Serial data at TTL levels. TxD changes from the falling edge of TxC.

W/RDYA, W/RDYB. Wait/Ready (outputs, open drain when programmed for Wait function; driven High and Low when programmed for Ready function). These dual-purpose outputs may be programmed as Ready lines for a DMA controller or as Wait lines that synchronize the CPU to the SIO data rate. The reset state is open drain.

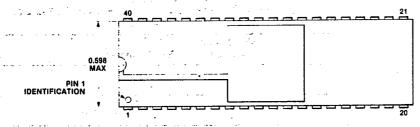

# **PACKAGE PINOUTS**

Figure 5. Pin Functions

Figure 6. 40-pin Dual-In-Line Package (DIP), Pin Assignments

Figure 7. Pin Functions

Figure 8. 40-pin Dual-In-Line Package (DIP), Pin Assignments

Figure 9. Pin Functions

Figure 10. 40-pin Dual-In-Line Package (DIP), Pin Assignments

Figure 11. 44-pin Chip Carrier, **Pin Assignments**

03E 08314

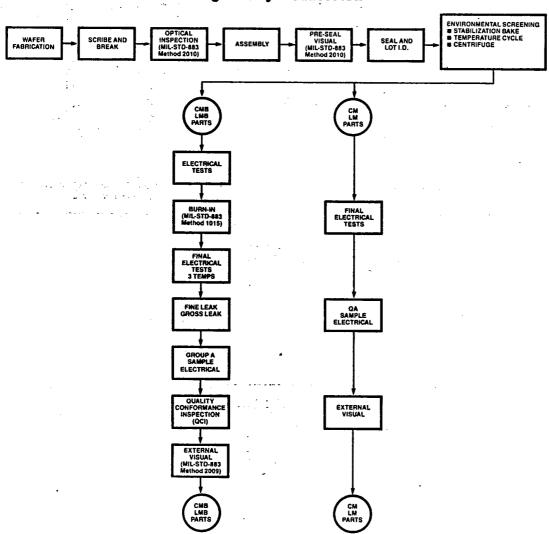

# MIL-STD-883 MILITARY PROCESSED PRODUCT

T-75-37-07

- Mil-Std-883 establishes uniform methods and procedures for testing microelectronic devices to insure the electrical, mechanical, and environmental integrity and reliability that is required for military applications.

- Mil-Std-883 Class B is the industry standard product assurance level for military ground and aircraft application.

- The total reliability of a system depends upon tests that are designed to stress specific quality and reliability concerns that affect microelectronic products.

- The following tables detail the 100% screening and electrical tests, sample electrical tests, and Qualification/Quality Conformance testing required.

# **Zilog Military Product Flow**

T-75-37-07

# Table I MIL-STD-883 Class B Screening Requirements Method 5004

| Test               | . 11<br>               | Mil-Std-883<br>Method | Test Condition                                                                                                                         | Requirement |

|--------------------|------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Internal Visual    |                        | 2010                  | Condition B                                                                                                                            | 100%        |

| Stabilization Ba   | ake                    | 1008                  | Condition C                                                                                                                            | 100%        |

| Temperature C      | ycle                   | 1010                  | Condition C                                                                                                                            | 100%        |

| Constant Acce      | leration (Centrifuge)  | 2001                  | Condition E or D <sup>(Note 1)</sup> , Y <sub>1</sub> Axis Only                                                                        | 100%        |

| Initial Electrical | Tests                  |                       | Zilog Military Electrical Specification<br>Static/DC T <sub>C</sub> = +25 °C                                                           | 100%        |

| Burn-In            | <del></del>            | 1015                  | Condition $D^{(Note 2)}$ , 160 hours,<br>$T_A = +125$ °C                                                                               | 100%        |

| Interim Electric   | eal Tests              |                       | Zilog Military Electrical Specification<br>Static/DC T <sub>C</sub> = +25 °C                                                           | . 100%      |

| PDA Calculation    | on                     | ·.                    | PDA = 5%                                                                                                                               | 100%        |

| Final Electrical   | Tests                  |                       | Zilog Military Electrical Specification<br>Static/DC T <sub>C</sub> = +125°C, -55°C<br>Functional, Switching/AC T <sub>C</sub> = +25°C | 100%        |

| Fine Leak          | ,                      | 1014                  | Condition A <sub>2</sub>                                                                                                               | 100%        |

| Gross Leak         |                        | 1014                  | Condition C                                                                                                                            | 100%        |

| Quality Confor     | mance Inspection (QCI) |                       |                                                                                                                                        |             |

| Group A            | Each Inspection Lot    | 5005                  | (See Table II)                                                                                                                         | Sample      |

| Group B            | Every Week             | 5005                  | (See Table III)                                                                                                                        | Sample      |

| Group C            | Periodically (Note 3)  | 5005                  | (See Table IV)                                                                                                                         | Sample      |

| Group D            | Periodically (Note 3)  | 5005                  | (See Table V)                                                                                                                          | Sample      |

| External Visual    |                        | 2009                  |                                                                                                                                        | 100%        |

| QAShip             |                        |                       |                                                                                                                                        | 100%        |

<sup>1.</sup> Applies to larger packages which have an inner seal or cavity perimeter of two inches or more in total length or have a package mass of >5 grams.

2. In process of fully implementing of Condition D Burn-In Circuits. Contact factory for copy of specific burn-in circuit available.

3. Performed periodically as required by Mil-Std-883, paragraph 1.2.1 b(17).

DE 9984043 0008316 8

9984043 ZILOG INC

03E 08316

T-75-37-07

# Table II Group A Sample Electrical Tests MIL-STD-883 Method 5005

| Subgroup    | Tests        | Temperature (T <sub>C</sub> ) | LTPD<br>Max Accept = 2 |

|-------------|--------------|-------------------------------|------------------------|

| Subgroup 1  | Static/DC    | +25°C                         | 2                      |

| Subgroup 2  | Static/DC    | +125°C                        | 3                      |

| Subgroup 3  | Static/DC    | -55°C                         | 5                      |

| Subgroup 7  | Functional   | +25°C                         | 2                      |

| Subgroup 8  | Functional   | -55°C and +125°C              | 5                      |

| Subgroup 9  | Switching/AC | +25°C                         | 2                      |

| Subgroup 10 | Switching/AC | +125°C                        | 3                      |

| Subgroup 11 | Switching/AC | -55°C                         | 5                      |

<sup>The specific parameters to be included for tests in each subgroup shall be as specified in the applicable detail electrical specification. Where no parameters have been identified in a particular subgroup or test within a subgroup, no Group A testing is required for that subgroup or test.

A single sample may be used for all subgroup testing. Where required size exceeds the lot size, 100% inspection shall be allowed.

Group A testing by subgroup or within subgroups may be performed in any sequence unless otherwise specified.</sup>

T-75-37-07

# Table III Group B Sample Test Performed Every Week to Test Construction and Insure Integrity of Assembly Process. MIL-STD-883 Method 5005

| Subgroup                                                                  | Mil-Std-883<br>Method | Test Condition                                                                                                                                                              | Quantity or<br>LTPD/Max Accept |

|---------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Subgroup 1 Physical Dimensions                                            | 2016                  | ·                                                                                                                                                                           | 2/0                            |

| Subgroup 2 Resistance to Solvents                                         | 2015                  |                                                                                                                                                                             | 4/0                            |

| Subgroup 3 . Solderability                                                | 2003                  | Solder Temperature<br>+245°C ± 5°C                                                                                                                                          | 15(Note 1)                     |

| Subgroup 4 Internal Visual and Mechanical                                 | 2014                  |                                                                                                                                                                             | 1/0                            |

| Subgroup 5<br>Bond Strength                                               | 2011                  | C                                                                                                                                                                           | 15(Note 2)                     |

| Subgroup 6(Note 3) Internal Water Vapor Content                           | 1018                  | 1000 ppm.<br>maximum at +100°C                                                                                                                                              | 3/0 or 5/1                     |

| Subgroup 7 <sup>(Note 4)</sup><br>Seal<br>7a) Fine Leak<br>7b) Gross Leak | 1014                  | 7a) A <sub>2</sub><br>7b) C                                                                                                                                                 | 5                              |

| Subgroup 8 <sup>(Note 5)</sup> Electrostatic Discharge Sensitivity        | 3015                  | Zilog Military Electrical Specification Static/DC T <sub>C</sub> = +25 °C A = 20-2000V B = >2000V Zilog Military Electrical Specification Static/DC T <sub>C</sub> = +25 °C | 15/0                           |

- Number of leads inspected selected from a minimum of 3 devices.

Number of bond pulls selected from a minimum of 4 devices.

Test applicable only if the package contains a dessicant.

Test not required if either 100% or sample seal test is performed between final electrical tests and external visual during Class B screening.

Test required for initial qualification and product redesign.

T-75-37-07

# Table IV Group C Sample Test Performed Periodically to Verify Integrity of the Die. MIL-STD-883 Method 5005

| Subgroup                                | Mil-Std-883<br>Method                 | Test Condition                                                                   | Quantity or<br>LTPD/Max Accept        |

|-----------------------------------------|---------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|

| Subgroup 1                              | -                                     |                                                                                  |                                       |

| Steady State Operating Life             | 1005                                  | Condition D <sup>(Note 1)</sup> , 1000 hours at<br>+ 125°C                       | 5                                     |

| End Point Electrical Tests              | · · · · · · · · · · · · · · · · · · · | Zilog Military Electrical Specification T <sub>C</sub> = +25°C, +125°C, -55°C    | e e e e e e e e e e e e e e e e e e e |

| Subgroup 2 Temperature Cycle            | - 1010                                | Condition C                                                                      |                                       |

| Constant Acceleration (Centrifuge)      | 2001                                  | Condition E or D(Note 2), Y1 Axis Only                                           |                                       |

| Seal<br>2a) Fine Leak<br>2b) Gross Leak | 1014                                  | 2a) Condition A <sub>2</sub> 2b) Condition C                                     | 15                                    |

| Visual Examination                      | 1010 or 1011                          | 11                                                                               |                                       |

| End Point Electrical Tests              |                                       | Zilog Military Electrical Specification<br>T <sub>C</sub> = +25°C, +125°C, -55°C |                                       |

In process of fully implementing Condition D Burn-In Circuits. Contact factory for copy of specific burn-in circuit available.

Applies to larger packages which have an inner seal or cavity perimeter of two inches or more in total length or have a package mass of ≥5 grams.

T-75-37-07

# Table V Group D Sample Test Performed Periodically to Insure Integrity of the Package. MIL-STD-883 Method 5005

| Subgroup                                                      | Mil-Std-883<br>Method                 | Test Condition                                                                   | Quantity or<br>LTPD/Max Accep |

|---------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------|-------------------------------|

| Subgroup 1                                                    | · · · · · · · · · · · · · · · · · · · |                                                                                  | <u>-</u>                      |

| Physical Dimensions                                           | 2016                                  |                                                                                  | 15                            |

| Subgroup 2<br>Lead Integrity                                  | 2004                                  | Condition B <sub>2</sub> or D <sup>(Note 1)</sup>                                | 15                            |

| Subgroup 3<br>Thermal Shock                                   | 1011                                  | Condition B minimum,<br>15 cycles minimum                                        |                               |

| Temperature Cycling                                           | 1010                                  | Condition C, 100 cycles minimum                                                  | 15                            |

| Moisture Resistance                                           | 1004                                  | •                                                                                |                               |

| Seal<br>3a) Fine Leak<br>3b) Gross Leak<br>Visual Examination | 1014<br>1004 or 1010                  | 3a) Condition A <sub>2</sub> 3b) Condition C                                     |                               |

| End Point Electrical Tests                                    |                                       | Zilog Military Electrical Specification<br>T <sub>C</sub> = +25°C, +125°C, -55°C |                               |

| Subgroup 4<br>Mechanical Shock                                | 2002                                  | Condition B minimum                                                              |                               |

| Vibration Variable Frequency                                  | 2007                                  | Condition A minimum                                                              | 15                            |

| Constant Acceleration (Centrifuge) Seal                       | 2001<br>1014                          | Condition E or D <sup>(Note 2)</sup> , Y <sub>1</sub> Axis Only                  | 15                            |

| 4a) Fine Leak<br>4b) Gross Leak                               | 1014                                  | <ul><li>4a) Condition A<sub>2</sub></li><li>4b) Condition C</li></ul>            |                               |

| Visual Examination                                            | 1010 or 1011                          |                                                                                  |                               |

| End Point Electrical Tests                                    |                                       | Zilog Military Electrical Specification<br>T <sub>C</sub> = +25°C, +125°C, -55°C |                               |

| Subgroup 5 Salt Atmosphere Seal                               | 1009<br>1014                          | Condition A minimum                                                              | . 15                          |

| 5a) Fine Leak<br>5b) Gross Leak                               | 1014                                  | 5a) Condition A <sub>2</sub> . 5b) Condition C                                   | 15                            |

| Visual Examination                                            | 1009                                  |                                                                                  |                               |

| Subgroup 6 Internal Water Vapor Content                       | 1018                                  | 5,000 ppm. maximum water content at +100°C                                       | 3/0 or 5/1                    |

| Subgroup 7(Note 3) Adhesion of Lead Finish                    | 2025                                  |                                                                                  | 15(Note 4)                    |

| Subgroup 8 <sup>(Note 5)</sup><br>Lid Torque                  | 2024                                  |                                                                                  | 5/0                           |

- Lead Integrity Condition D for leadless chip carriers.

Applies to larger packages which have an inner seal or cavity perimeter of two inches or more in total length or have a package mass of ≥5 grams.

- Not applicable to leadless chip carriers.

LTPD based on number of leads.

- 5. Not applicable for solder seal packages.

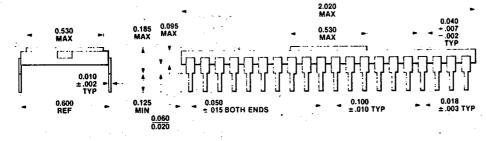

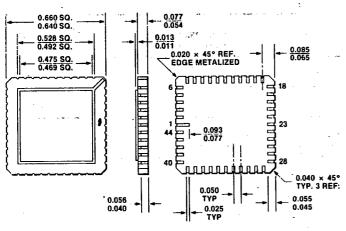

# **PACKAGE INFORMATION**

# 40-Pin Ceramic Dual In-line Package (DIP)

44-Pin Ceramic Leadless Chip Carrier (LCC)

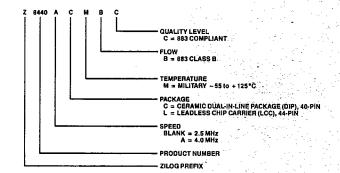

# ZILOG ORDERING INFORMATION

T-75-37-07

# **AVAILABLE MILITARY PRODUCTS**

|            | Z80 SIO/0, 2.5 | MHz       |

|------------|----------------|-----------|

| 40-pin DIP |                | 44-pin LC |

Z8440 CM Z8440 CMBC

# Z80 SIO/1, 2.5 MHz

Z8444 LM

Z8444 LMBC

40-pin DIP

44-pin LCC

Z8441 CM

Z8444 LM

Z8441 CMBC

Z8444 LMBC

# Z80 SIO/2, 2.5 MHz

40-pin DIP

44-pin LCC

Z8442 CM

Z8444 LM

Z8442 CMBC

Z8444 LMBC

# Z80A SIO/0, 4.0 MHz

40-pin DIP

44-pin LCC

Z8440A CM

Z8444A LM

Z8440A CMBC

Z8444A LMBC

## Z80A SIO/1, 4.0 MHz

40-pin DIP

44-pin LCC

Z8441A CM

Z8444A LM

Z8441A CMBC

Z8444A LMBC

# Z80A SIO/2, 4.0 MHz

40-pin DIP

44-pin LCC

Z8442A CM

Z8444A LM

Z8442A CMBC

Z8444A LMBC