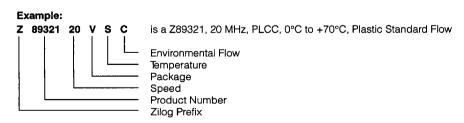

# Z89321/371/391

16-BIT DIGITAL SIGNAL PROCESSORS

### **FEATURES**

| Part   | DSP ROM<br>(K Words) | OTP<br>(K Words) | DSP RAM<br>(Words) | MIPS<br>(Max) |

|--------|----------------------|------------------|--------------------|---------------|

| Z89321 | 4                    |                  | 512                | 20            |

| Z89371 |                      | 4                | 512                | 16            |

| Z89391 | 64*                  |                  | 512                | 20            |

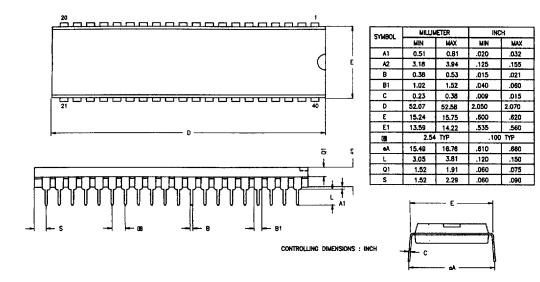

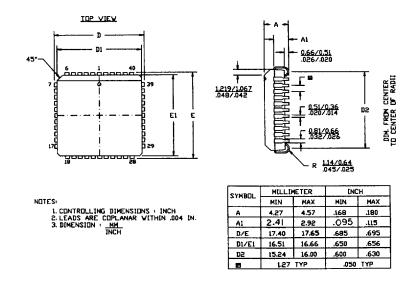

| Package<br>Part | 40-Pin<br>DIP | 44-Pin<br>PLCC | 44-Pin<br>QFP | 84-Pin<br>PLCC |

|-----------------|---------------|----------------|---------------|----------------|

| Z89321          | Х             | Х              | Х             |                |

| Z89371          | X             | X              | X             |                |

| Z89391          |               |                |               | Х              |

- 0°C to +70°C Operating Temperature Range

- 4.5- to 5.5-Volt Operating Range

#### **DSP Core**

- 20 MIPS @ 20 MHz, 16-Bit Fixed Point DSP

- 50 ns Instruction Cycle Time

- Six-Level Hardware Stack

- Six Register Address Pointers

- Optimized Instruction Set (30 Instructions)

## **On-Board Peripherals**

- Dual 8/16-Bit CODEC Interface Capable of up to 10 Mbps

- µ-Law Compression Option (Decompression is performed in software)

- 16-Bit I/O Bus (Tri-Stated)

- Three I/O Address Pins (Latched Outputs)

- Wait-State Generator

- Three Vectored Interrupts

- 13-Bit General-Purpose Timer

#### **GENERAL DESCRIPTION**

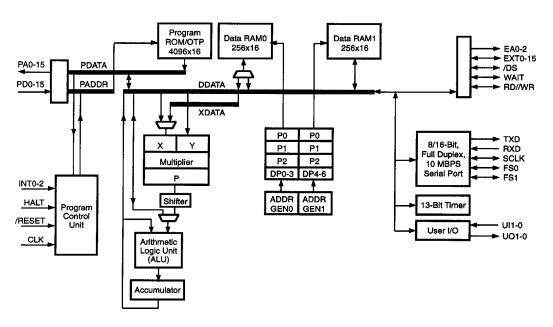

The Z893XX family of products are high-performance Digital Signal Processors (DSPs) with a modified Harvard-type architecture featuring separate program and data memory. The design has been optimized for processing power and minimizing silicon space.

The single-cycle instruction execution and bus structure promotes efficient algorithm execution, while the six register pointers provide circular buffering capabilities and dual operand fetching.

Three vectored interrupts are complemented by a six level stack, and the CODEC interface allows high-speed transfer rates to accommodate digital audio and voice data.

A dedicated Counter/Timer provides the necessary timing signals for the CODEC interface, and an additional 13-bit timer is available for general-purpose use.

The Z893XX DSPs are optimized to accommodate advanced signal processing algorithms. The 20 MIPS (maximum) operating performance and efficient architecture provides real-time instruction execution. Compression, filtering, frequency detection, audio, voice detection/synthesis and other vital algorithms can all be accommodated.

<sup>\*</sup> External

## GENERAL DESCRIPTION (Continued)

The Z89321/371/391 devices feature an on-board CODEC interface, compatible with 8-bit PCM and 16-bit CODECs for digital audio applications. Additionally, an on-board wait-state generator is provided to accommodate slow external peripherals.

For prototypes, as well as production purposes, the Z89371 member of the DSP product family is a one-time programmable (OTP) device with a 16 MHz maximum operating frequency.

Throughout this specification, references to the Z89321 device applies equally to the Z89371 and Z89391, unless otherwise specified.

### Notes:

All Signals with a preceding front slash, "/", are active Low, e.g., B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>cc</sub> | V <sub>DD</sub> |

| Ground     | GNĎ             | V <sub>ss</sub> |

Figure 1. Z89321/371/391 Functional Block Diagram

### PIN DESCRIPTION

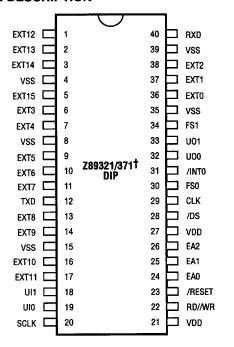

Figure 2. Z89321/371 40-Pin DIP Pin Assignments

Table 1. Z89321/371 40-Pin DIP Pin Identification

| No.         | Symbol                         | Function                        | Direction             |

|-------------|--------------------------------|---------------------------------|-----------------------|

| 1-3<br>4    | EXT12-EXT14<br>V <sub>ss</sub> | External data bus<br>Ground     | Input/Output          |

| 5           | EXT15                          | External data bus               | Input/Output          |

| 6-7         | EXT3-EXT4                      | External data bus               | Input/Output          |

| 8<br>9-11   | V <sub>ss</sub><br>EXT5-EXT7   | Ground<br>External data bus     | Input/Output          |

| 12          | TXD                            | Serial output to CODECs         | Output                |

| 13-14       | EXT8-EXT9                      | External data bus               | Input/Output          |

| 15          | $V_{ss}$                       | Ground                          |                       |

| 16-17<br>18 | EXT10-EXT11<br>UI1             | External data bus<br>User input | Input/Output<br>Input |

| 19          | UI0                            | User input                      | Input                 |

| 20          | SCLK                           | CODEC serial clock              | Input/Output*         |

| 21          | V <sub>DD</sub>                | Power supply                    | Input                 |

| 22          | RD//WR                         | Strobes for external bus        | Output                |

| 23          | /RESET                         | Reset                           | Input                 |

| 24-26       | EA0-EA2                        | External address bus            | Output                |

| 27          | V_00_                          | Power supply                    | Input                 |

| 28          | /DS                            | Data strobe for external bus    | Output                |

| 29          | CLK                            | Clock                           | Input                 |

| 30          | FS0                            | CODEC 0 frame sync              | Input/Output*         |

| 31          | /INTO                          | Interrupt                       | Input                 |

| 32-33       | U00-U01                        | User output                     | Output                |

| 34          | FS1                            | CODEC 1 frame sync              | Input/Output*         |

| 35          | V <sub>ss</sub><br>EXT0-EXT2   | Ground                          |                       |

| 36-38       | EXTO-EXT2                      | External data bus               | Input/Output          |

| 39          | V <sub>SS</sub>                | Ground                          | l                     |

| 40          | RXD                            | Serial input from CODECs        | Input                 |

#### Notes

<sup>\*</sup> Input or output is defined by interface mode selection.

<sup>†</sup> HALT and WAIT pins are not available on the 40-pin DIP package.

### PIN DESCRIPTION (Continued)

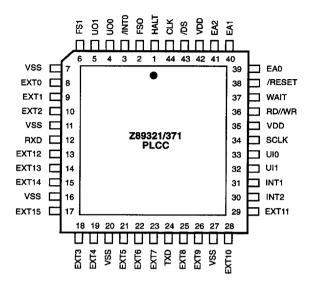

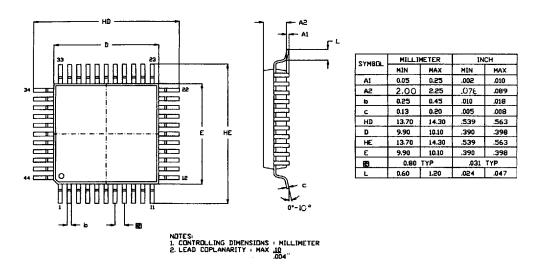

Figure 3. Z89321/371 44-Pin PLCC Pin Assignments

Table 2. Z89321/371 44-Pin PLCC Pin Identification

| No.   | Symbol                       | Symbol Function Direction |               |

|-------|------------------------------|---------------------------|---------------|

| 1     | HALT                         | Stop execution            | Input         |

| 2     | FS0                          | CODEC 0 frame sync        | Input/Output* |

| 3     | /INTO                        | Interrupt                 | Input         |

| 4-5   | U00-U01                      | User output               | Output        |

| 6     | FS1                          | CODEC 1 frame sync        | Input/Output* |

| 7     | V <sub>ss</sub><br>EXT0-EXT2 | Ground                    |               |

| 8-10  | EXTO-EXT2                    | External data bus         | Input/Output  |

| 11    | $V_{ss}$                     | Ground                    |               |

| 12    | RXD                          | Serial input from CODECs  | Input         |

| 13-15 | EXT12-EXT14                  | External data bus         | Input/Output  |

| 16    | $V_{ss}$                     | Ground                    |               |

| 17    | EXT15                        | External data bus         | Input/Output  |

| 18-19 | EXT3-EXT4                    | External data bus         | Input/Output  |

| 20    | V <sub>SS</sub>              | Ground                    |               |

| 21-23 | EXT5-EXT7                    | External data bus         | Input/Output  |

| 24    | TXD                          | Serial output to CODECs   | Output        |

| No.         | Symbol                       | Symbol Function              |               |

|-------------|------------------------------|------------------------------|---------------|

| 25-26<br>27 | EXT8-EXT9<br>V <sub>ss</sub> | External data bus<br>Ground  | Input/Output  |

| 28-29       | EXT10-EXT11                  | External data bus            | Input/Output  |

| 30          | /INT2                        | Interrupt                    | Input         |

| 31          | /INT1                        | Interrupt                    | Input         |

| 32          | Ul1                          | User input                   | Input         |

| 33          | UIO                          | User input                   | Input         |

| 34          | SCLK                         | CODEC serial clock           | Input/Output* |

| 35          | V <sub>DD</sub>              | Power supply                 | Input         |

| 36          | RĎ//WR                       | RD//WR strobe for EXT bus    | Output        |

| 37          | WAIT                         | WAIT state                   | Input         |

| 38          | /RESET                       | Reset                        | input         |

| 39-41       | EA0-EA2                      | External address bus         | Output        |

| 42          | V <sub>DD</sub>              | Power supply                 | Input         |

| 43          | /ĎŠ                          | Data strobe for external bus | Output        |

| 44          | CLK                          | Clock                        | Input         |

Note:

1-4

**- 9984043 0027453 801 -**

<sup>\*</sup> Input or output is defined by interface mode selection.

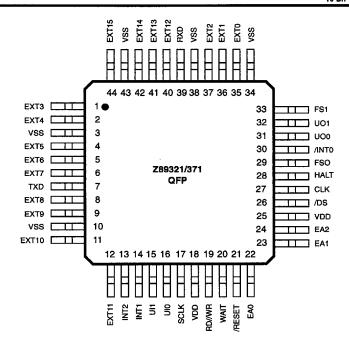

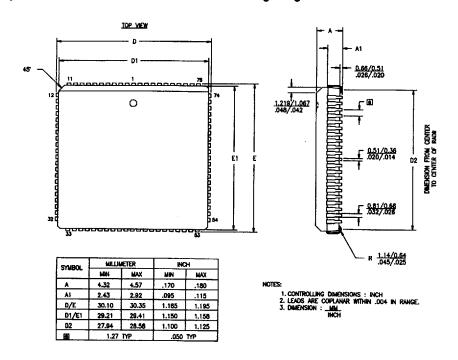

Figure 4. Z89321/371 44-Pin QFP Pin Assignments

Table 3. Z89321/371 44-Pin QFP Pin Identification

| No.      | No. Symbol Function          |                             | Direction     |  |

|----------|------------------------------|-----------------------------|---------------|--|

| 1-2<br>3 | EXT3-EXT4<br>V <sub>ss</sub> | External data bus<br>Ground | Input/Output  |  |

| 4-6      | EXT5-EXT7                    | External data bus           | Input/Output  |  |

| 7        | TXD                          | Serial output to CODECs     | Output        |  |

| 8-9      | EXT8-EXT9                    | External data bus           | Input/Output  |  |

| 10       | $V_{ss}$                     | Ground                      |               |  |

| 11-12    | EXT10-EXT1                   | External data bus           | input/Output  |  |

| 13       | /INT2                        | Interrupt                   | Input         |  |

| 14       | /INT1                        | Interrupt                   | Input         |  |

| 15       | UI1                          | User input                  | Input         |  |

| 16       | UI0                          | User input                  | Input         |  |

| 17       | SCLK                         | CODEC serial clock          | Input/Output* |  |

| 18       | V <sub>DD</sub>              | Power supply                | Input         |  |

| 19       | RĎ//WR                       | RD//WR strobe EXT bus       | Output        |  |

| 20       | WAIT                         | WAIT state                  | Input         |  |

| 21       | /RESET                       | Reset                       | Input         |  |

| No.                     | Symbol                                         | Function                                                                   | Direction                             |

|-------------------------|------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------|

| 22-24                   | EAO-EA2                                        | External address bus                                                       | Output                                |

| 25                      | V <sub>DD</sub>                                | Power supply                                                               | Input                                 |

| 26                      | /DS                                            | Data strobe for external bus                                               | Output                                |

| 27                      | CLK                                            | Clock                                                                      | Input                                 |

| 28                      | HALT                                           | Stop execution                                                             | Input                                 |

| 29                      | FS0                                            | CODEC 0 frame sync                                                         | Input/Output*                         |

| 30                      | /INT0                                          | Interrupt                                                                  | Input                                 |

| 31-32                   | U00-U01                                        | User output                                                                | Output                                |

| 33                      | FS1                                            | CODEC 1 frame sync                                                         | Input/Output* Input/Output            |

| 34                      | V <sub>ss</sub>                                | Ground                                                                     |                                       |

| 35-37                   | EXT0-EXT2                                      | External data bus                                                          |                                       |

| 38                      | V <sub>ss</sub>                                | Ground                                                                     |                                       |

| 39<br>40-42<br>43<br>44 | RXD<br>EXT12-EXT14<br>V <sub>ss</sub><br>EXT15 | Serial input to CODECs<br>External data bus<br>Ground<br>External data bus | Input<br>Input/Output<br>Input/Output |

Note:

<sup>\*</sup>Input or output is defined by interface mode selection.

### PIN DESCRIPTION (Continued)

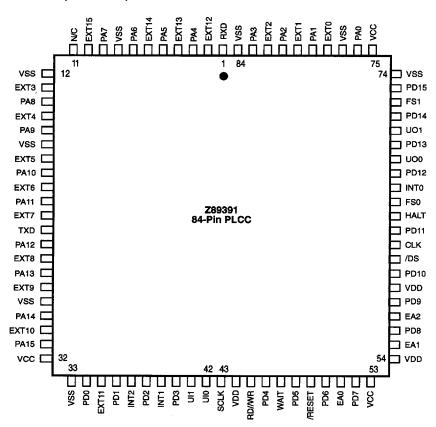

Figure 5. Z89391 84-Pin PLCC Pin Assignments

Table 4. Z89391 84-Pin PLCC Pin Identification

| Symbol          | Function             | Direction                       | Symbol    | Function                                                                                                | Direction     |

|-----------------|----------------------|---------------------------------|-----------|---------------------------------------------------------------------------------------------------------|---------------|

| EXT15-EXT0      | External data bus    | Input/Output Input Output Input | CLK       | Clock                                                                                                   | Input         |

| V <sub>ss</sub> | Ground               |                                 | HALT      | Stop execution                                                                                          | Input         |

| PD15-PD0        | Program data bus     |                                 | UI1-UI0   | User inputs                                                                                             | Input         |

| PA15-PA0        | Program address bus  |                                 | INT2-INT0 | Interrupts                                                                                              | Input         |

| V <sub>DD</sub> | Power supply         |                                 | UO1-UO0   | User outputs                                                                                            | Output        |

| EA2-EA0         | External address bus | Output                          | SCLK      | CODEC serial clock CODEC 0 frame sync CODEC 1 frame sync Serial input to CODECs Serial output to CODECs | Input/Output* |

| /DS             | Data strobe          | Output                          | FS0       |                                                                                                         | Input/Output* |

| RD//WR          | READ//WRITE strobe   | Output                          | FS1       |                                                                                                         | Input/Output* |

| WAIT            | WAIT state           | Input                           | RXD       |                                                                                                         | Input         |

| /RESET          | Reset                | Input                           | TXD       |                                                                                                         | Output        |

Note:

1-6

**■ 9984043 0027455 684** ■

<sup>\*</sup> Input or output is defined by interface mode selection.

### **PIN FUNCTIONS**

**CK** Clock (input). This pin controls the external clock.

**EXT15-EXT0** External Data Bus (input/output). These pins control the data bus for user-defined outside registers, such as an ADC or DAC. The pins are normally tri-stated, except when the outside registers are specified as destination registers in the instructions. All the control signals exist to allow a read or a write through this bus.

**RD//WR** Read/Write Strobe (output). This pin controls the data direction signal for EXT-Bus. Data is available from the CPU on EXT15-EXT0 when this signal is Low. EXT-Bus is in input mode (high-impedance) when this signal is High.

**EA2-EA0** External Address (output). These pins control the user-defined register address output (latched). One of eight user-defined external registers is selected by the processor with these address pins for read or write operations. Since the addresses are part of the processor memory map, the processor is simply executing internal reads and writes. External Addresses EXT4-EXT7 are used internally by the processor if the CODEC interface and 13-bit timer are enabled.

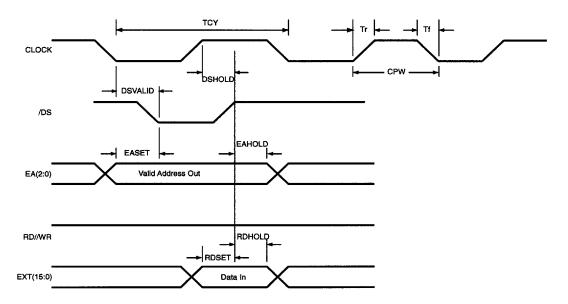

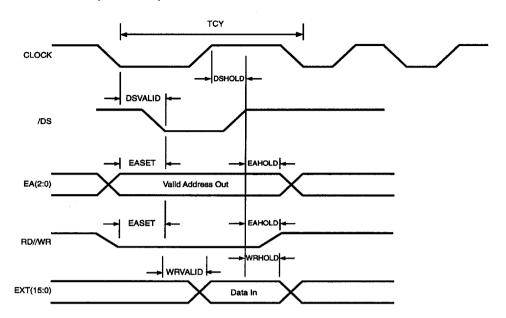

/DS Data Strobe (output). This pin control the data strobe signal for EXT-Bus. Data is read by the external peripheral on the rising edge of /DS. Data is also read by the processor on the rising edge of CK /DS.

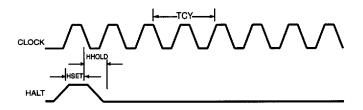

HALT Halt State (input). This pin controls Stop Execution. The CPU continuously executes NOPs and the program counter remains at the same value when this pin is held High. An interrupt request must be executed (enabled) to exit HALT mode. After the interrupt service routine, the program continues from the instruction after the HALT. (HALT is not available on the 40-pin DIP package.)

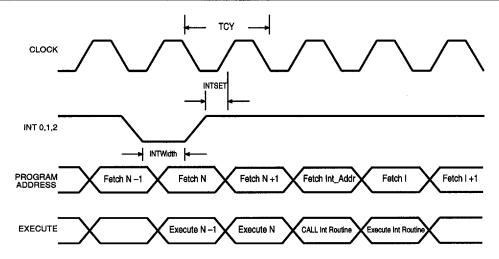

/INT2-/INT0 Three Interrupts (input, active Low). These pins control interrupt requests 2-0. Interrupts are generated on the rising edge of the input signal. Interrupt vectors for

the interrupt service starting address are stored in the following program memory locations:

|   | Device     | /INTO | /INT1 | /INT2 |

|---|------------|-------|-------|-------|

| • | Z89321/371 | OFFFH | OFFEH | 0FFDH |

|   | Z89391     | FFFFH | FFFEH | FFFDH |

Priority is: INT2 = lowest, INT0 = highest. INT1 is dedicated to the CODEC interface and INT2 is dedicated to the 13-bit timer if both peripherals are enabled. (**Note:** INT1 and INT2 pins are not bonded-out on the 40-pin DIP package.)

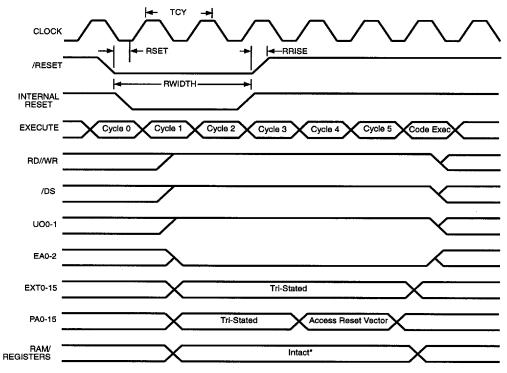

**RESET** Reset (input, active Low). This pin controls the asynchronous reset signal. The /RESET signal must be kept Low for at least one clock cycle. The CPU pushes the contents of the Program Counter (PC) onto the stack and then fetches a new PC value from program memory address OFFCH (or FFFCH for the Z89391) after the reset signal is released.

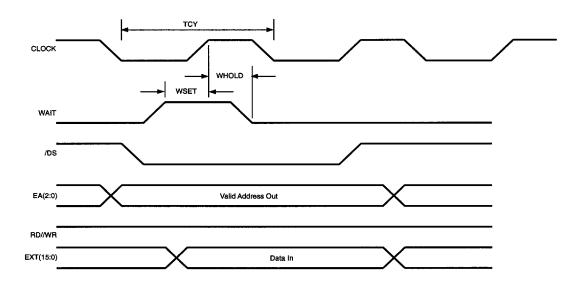

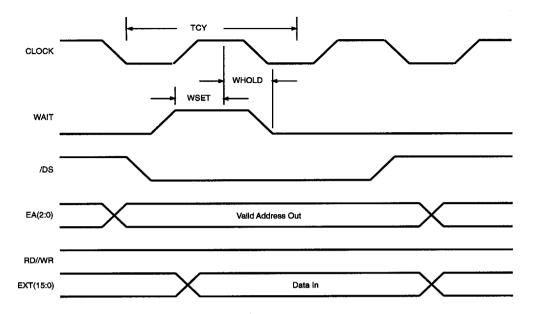

**WAIT** WAIT State (input). The wait signal is sampled at the rising edge of the clock with appropriate setup and hold times. The normal write cycle will continue when wait is inactive on a rising clock. A single wait-state can be generated internally by setting the appropriate bits in the EXT7-2 register. (WAIT is not available on the 40-pin DIP package.)

**UI1-UI0** Two Input Pins (input). These general-purpose input pins are directly tested by the conditional branch instructions. These are asynchronous input signals that have no special clock synchronization requirements.

**UO1-UO0** Two Output Pins (output). These generalpurpose output pins reflect the value of two bits in the status register S5 and S6. These bits have no special significance and may be used to output data by writing to the status register. A mask option is available for opendrain or push-pull outputs. **Note:** The user output value is the opposite of the status register content.

### ADDRESS SPACE

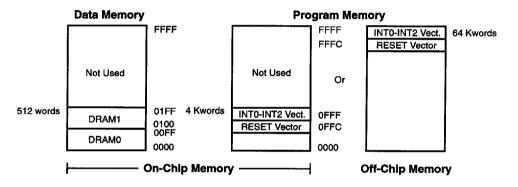

**Program Memory.** Programs of up to 4 Kwords can be masked into internal ROM (OTP for Z89371). Four locations are dedicated to the vector address for the three interrupts (OFFDH-0FFFH) and the starting address following a Reset (OFFCH). Internal ROM is mapped from 0000H to 0FFFH, and the highest location for program is 0FFBH. A 64 Kword External Program Memory Space is available on the Z89391. The vector addresses for the Z89391 reside at FFFCH-FFFFH (Figure 6).

**Internal Data RAM.** The Z89321, 371 and 391 all have internal 512 x 16-bit word data RAM organized as two banks of 256 x 16-bit words each: RAM0 and RAM1. Each data RAM bank is addressed by three pointers: Pn:0 (n = 0-2) for RAM0 and Pn:1 (n = 0-2) for RAM1. The RAM addresses for RAM0 and RAM1 are arranged from 0-255 and 256-511, respectively. The address pointers, which

may be written to, or read from, are 8-bit registers connected to the lower byte of the internal 16-bit D-Bus and are used to perform modulo addressing. Three addressing modes are available to access the Data RAM: register indirect, direct addressing, and short form direct. The contents of the RAM can be read to, or written from, in one machine cycle per word, without disturbing any internal registers or status other than the RAM address pointer used for each RAM. The contents of each RAM can be loaded simultaneously into the X and Y inputs of the multiplier.

**Registers.** The Z89321 has 19 internal registers and up to an additional eight external registers. The external registers are user-definable for peripherals, such as A/D or D/A, or to DMA, or other addressing peripherals. Both external and internal registers are accessed in one machine cycle.

Figure 6. Memory Map

#### **FUNCTIONAL DESCRIPTION**

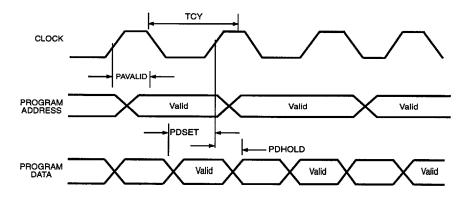

**Instruction Timing.** Most instructions are executed in one machine cycle. Long immediate instructions and Jump or Call instructions are executed in two machine cycles. A multiplication or multiplication/accumulate instruction requires a single cycle. Specific instruction cycle times are described in the Condition Code section.

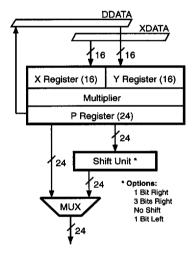

**Multiply/Accumulate.** The multiplier can perform a 16-bit x 16-bit multiply, or multiply accumulate, in one machine cycle using the Accumulator and/or both the X and Y inputs. The multiplier produces a 32-bit result, however, only the 24 most significant bits are saved for the next instruction or accumulation. For operations on very small numbers where the least significant bits are important, the data should first be scaled by eight bits (or the multiplier and multiplicand by four bits each) to avoid truncation errors. Note that all inputs to the multiplier should be

fractional two's-complement, 16-bit binary numbers (Figure 7). This puts them in the range [-1 to 0.9999695], and the result is in 24 bits so that the range is [-1 to 0.9999999]. In addition, if 8000H is loaded into both X and Y registers, the resulting multiplication is considered an illegal operation as an overflow would result. Positive one cannot be represented in fractional notation, and the multiplier will actually yield the result 8000H x 8000H = 8000H (-1 x -1 = -1)

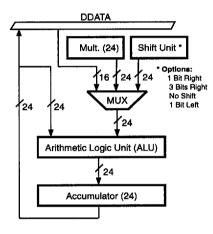

**ALU.** The ALU has two input ports, one of which is connected to the output of the 24-bit Accumulator. The other input is connected to the 24-bit P-Bus, the upper 16 bits of which are connected to the 16-bit D-Bus. A shifter between the P-Bus and the ALU input port can shift the data by three bits right, one bit right, one bit left or no shift (Figure 8).

Figure 7. Multiplier Block Diagram

Figure 8. ALU Block Diagram

## **FUNCTIONAL DESCRIPTION** (Continued)

Hardware Stack. A six-level hardware stack is connected to the D-Bus to hold subroutine return addresses or data. The Call instruction pushes PC+2 onto the stack, and the RET instruction pops the contents of the stack to the PC.

**User Inputs.** The Z89321 has two inputs, UIO and UI1, which may be used by Jump and Call instructions. The Jump or Call tests one of these pins and if appropriate, jumps to a new location. Otherwise, the instruction behaves like a NOP. These inputs are also connected to the status register bits S10 and S11, which may be read by the appropriate instruction (Figure 8).

**User Outputs.** The status register bits S5 and S6 connect directly to UO0 and UO1 pins and may be written to by the appropriate instruction. **Note:** The user output value is the opposite of the status register content.

Interrupts. The Z89321 has three positive edge-triggered interrupt inputs. An interrupt is acknowledged at the end of an instruction execution. It takes two machine cycles to enter an interrupt instruction sequence. The PC is pushed onto the stack. A RET instruction transfers the contents of the stack to the PC and decrements the stack pointer by one word. The priority of the interrupts is INTO = highest, INT2 = lowest. INT1 is dedicated to the CODEC interface and INT2 is dedicated to the 13-bit timer if both peripherals are enabled. **Note:** The SIEF instruction enables the interrupts. The SIEF instruction must be used before exiting an interrupt routine since the interrupts are automatically disabled when entering the routine.

**Registers.** The Z89321 has 19 physical internal registers and up to eight user-defined external registers. The EA2-EA0 determines the address of the external registers. The signals are used to read from or write to the external registers /DS, WAIT, RD/WR.

I/O Bus. The processor provides a 16-bit, CMOS-compatible bus. I/O Control pins provide convenient communication capabilities with external peripherals, and single-cycle access is possible. For slower communications, an on-board hardware wait-state generator can be used to accommodate timing conflicts. Three latched I/O address pins are used to access external registers. The EXT 4, 5, 6, 7 pins are used by the internal peripherals. Disabling a peripheral allows access to these addresses for general-purpose use.

**CODEC Interface.** The multi-compatible, dual CODEC interface provides the necessary control signals for transmission of CODEC information to the DSP processor. The interface accommodates 8-bit PCM or 16-bit Linear CODECs. Special compatibility with Crystal Semiconductor's 4215/4216 CODECs provides the necessary interface for audio applications. Many general-purpose 8-, 16-bit A/Ds, D/As are adaptable. The interface can also be used as a high-speed serial port.

$\mu$ -Law Compression. The 8-bit CODEC interface mode provides  $\mu$ -law compression from 13-bit format to 8-bit format. Decompression is performed in software by use of a 128-word lookup table.

**Timer.** Two programmable timers are available. One is dedicated to the CODEC interface, the other for general-purpose use. When a time-out event occurs, an interrupt request is generated. Single pass and/or continuous modes are available. If the CODEC interface is not used, both timers can be used for general-purpose.

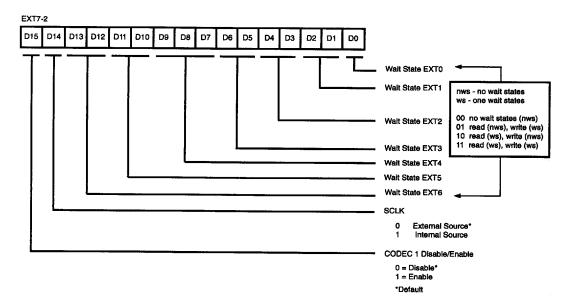

**Wait-State Generator.** An internal wait-state generator is provided to accommodate slow external peripherals. A single wait-state can be implemented through control registers EXT7-2. For additional states, a dedicated pin (WAIT) can be held High. The WAIT pin is monitored only during execution of a read or write instruction to external peripherals (EXT bus). **Note:** A WAIT pin is not available on the 40-pin DIP package.

1-10

**398**4043 0027459 22T |

#### REGISTERS

There are 19 internal registers which are defined below:

| Register                                                         | Register Definition                                                                                                                                                                                                                                                |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P                                                                | Output of Multiplier, 24-bit                                                                                                                                                                                                                                       |

| X                                                                | X Multiplier Input, 16-bit                                                                                                                                                                                                                                         |

| Y                                                                | Y Multiplier Input, 16-bit                                                                                                                                                                                                                                         |

| A                                                                | Accumulator, 24-bit                                                                                                                                                                                                                                                |

| SR                                                               | Status Register, 16-bit                                                                                                                                                                                                                                            |

| Pn:b                                                             | Six Ram Address Pointers, 8-bit each                                                                                                                                                                                                                               |

| PC                                                               | Program Counter, 16-bit                                                                                                                                                                                                                                            |

| EXT4<br>EXT5-1<br>EXT5-2<br>EXT6-1<br>EXT6-2<br>EXT7-1<br>EXT7-2 | 13-Bit Timer Configuration Register CODEC Interface Channel 0 Data CODEC Interface Channel 0 Data CODEC Interface Channel 1 Data CODEC Interface Channel 1 Data CODEC Interface Configuration Register Wait-State Generator/CODEC Interface Configuration Register |

The following are virtual registers as physical RAM does not exist on the chip.

| Register | Register Definition        |  |

|----------|----------------------------|--|

| EXTn     | External Registers, 16-bit |  |

| BUS      | D-Bus                      |  |

| Dn:b     | Eight Data Pointers*       |  |

### Note:

P holds the result of multiplications and is read-only.

**X** and **Y** are two 16-bit input registers for the multiplier. These registers can be utilized as temporary registers when the multiplier is not being used.

A is a 24-bit Accumulator. The output of the ALU is sent to this register. When 16-bit data is transferred into this register, it is placed into the 16 MSBs and the least significant eight bits are set to zero. Only the upper 16 bits are transferred to the destination register when the Accumulator is selected as a source register in transfer instructions.

**Pn:b** are the pointer registers for accessing data RAM, (n = 0,1,2 refer to the pointer number) (b = 0,1 refers to RAM

Bank 0 or 1). They can be directly read from or written to, and can point to locations in data RAM or Program Memory.

**EXTn** are external registers (n = 0 to 7). There are eight 16-bit registers provided here for mapping external devices into the address space of the processor. Note that the actual register RAM does not exist on the chip, but would exist as part of the external device, such as an ADC result latch. Use of the CODEC interface and 13-bit timer reduces the number of external registers to four.

**BUS** is a read-only register which, when accessed, returns the contents of the D-Bus. Bus is used for emulation only.

**Dn:b** refers to locations in RAM that can be used as a pointer to locations in program memory which is efficient for coefficient addressing. The programmer decides which location to choose from two bits in the status register and two bits in the operand. Thus, only the lower 16 possible locations in RAM can be specified. At any one time, there are eight usable pointers, four per bank, and the four pointers are in consecutive locations in RAM. For example, if S3/S4 = 01 in the status register, then D0:0/D1:0/D2:0/D3:0 refer to register locations 4/5/6/7 in RAM Bank 0. Note that when the data pointers are being written to, a number is actually being loaded to Data RAM, so they can be used as a limited method for writing to RAM.

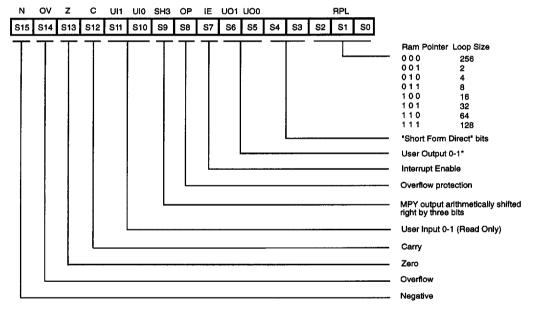

**SR** is the status register (Figure 8) which contains the ALU status and certain control bits (Table 5).

Table 5. Status Register Bit Functions

| Status Register Bit | Function                                                 |

|---------------------|----------------------------------------------------------|

| S15 (N)             | ALU Negative                                             |

| S14 (OV)            | ALU Overflow                                             |

| S13 (Z)             | ALU Zero                                                 |

| S12 (L)             | Carry                                                    |

| S11 (UI1)           | User Input 1                                             |

| S10 (U10)           | User Input 0                                             |

| S9 (SH3)            | MPY Output Arithmetically<br>Shifted Right by three bits |

| S8 (OP)             | Overflow Protection                                      |

| S7 (IE)             | Interrupt Enable                                         |

| S6 (UO1)            | User Output 1                                            |

| S5 (UO0)            | User Output 0                                            |

| S4-S3               | "Short Form Direct" bits                                 |

| S2-S0 (RPL)         | RAM Pointer Loop Size                                    |

<sup>\*</sup> These occupy the first four locations in RAM bank.

## **REGISTERS** (Continued)

The status register can always be read in its entirety. S15-S10 are set/reset by hardware and can only be read by software. S9-S0 control hardware looping and can be written by software (Table 6).

Table 6. RPL Description

| Tubic of the Dubbon party |    |    |                       |   |  |  |  |  |

|---------------------------|----|----|-----------------------|---|--|--|--|--|

| S2                        | S1 | S0 | Loop Size             |   |  |  |  |  |

| 0                         | 0  | 0  | 256                   | _ |  |  |  |  |

| 0                         | 0  | 1  | 2                     |   |  |  |  |  |

| 0                         | 1  | 0  | 4                     |   |  |  |  |  |

| 0                         | 1  | 1  | 8                     |   |  |  |  |  |

| <br>1                     | 0  | 0  | 16<br>32<br>64<br>128 | _ |  |  |  |  |

| 1                         | 0  | 1  | 32                    |   |  |  |  |  |

| 1                         | 1  | 0  | 64                    |   |  |  |  |  |

| 1                         | 1  | 1  | 128                   |   |  |  |  |  |

S15-S12 are set/reset by the ALU after an operation. S11-S10 are set/reset by the user inputs. S6-S0 are control bits described in Table 5. S7 enables interrupts. If S8 is set, the hardware clamps at maximum positive or negative values instead of overflowing. If S9 is set and a multiple/shift option is used, then the shifter shifts the result three bits right. This feature allows the data to be scaled and prevents overflows.

**PC** is the Program Counter. When this register is assigned as a destination register, one NOP machine cycle is added automatically to adjust the pipeline timing.

**External Register, EXT4-EXT7**, are used by the CODEC interface and 13-bit timer, the registers are reviewed in the CODEC interface section.

<sup>\*</sup> The output value is the opposite of the status register content.

Figure 8. Status Register

1-12

**3984043 002746% 988**

### PERIPHERAL OPERATION

## **Disabling Peripherals**

Disabling a peripheral (CODEC Interface, Counter) allows general-purpose use of the EXT address for the disabled peripheral. If the peripheral is not disabled, the EXT control signals and EXT data are still provided, but transfer of data on the EXT pins is not available (because internal transfers are being processed on the internal bus). Care must be taken to ensure that control of the EXT bus does not cause bus conflicts.

## Reading Data from CODEC Interface\*

External data is serially transferred into the CODEC interface registers from an external CODEC. This serial data is loaded into EXT5-2 (8- or 16-bit modes). Because the

interface is double-buffered, data must be transferred to EXT5-1 before being transferred along the internal data bus of the processor. This is accomplished by writing data to EXT5-2.

## Writing Data to CODEC Interface\*

Internal data is transferred from the internal data bus of the processor to the EXT5-2 register. The CODEC interface constantly transfers and receives data during normal operation. Data to be transferred is loaded to EXT5-2 and is automatically serially transferred.

**Note:** \*EXT5-1 and EXT5-2 are used in the example, but this information applies equally to EXT6-1 and EXT6-2. (Refer to Figure 10, CODEC Block Diagram.)

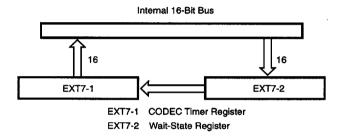

Figure 9. EXT7 Register Configuration

## Loading EXT7

Because EXT7 is double-buffered, a pair of writes are performed when loading the EXT7 registers (Figure 9).

LD EXT7, #%54F4 LD EXT7, #%6CDA LD @P0:0. EXT7 Loads CODEC Timer Register Loads Wait-State Register Reads EXT7-1 and places

data in RAM

#### Interrupts

The Z89321 features three interrupts:

INTO General-Purpose

INT1 CODEC Interface

INT2 13-Bit Timer

If all peripherals are enabled, INTO (general-purpose) can be used.

## **PERIPHERALS** (Continued)

#### **CODEC Interface**

The CODEC Interface provides direct-connect capabilities for standard 8-, 16-bit CODECs. The interface also supports 8-bit PCM, 8-bit PCM with hardware  $\mu$ -law conversion ( $\mu$ -law expansion is done in software), 16-bit Linear and Crystal's Sigma-Delta Stereo CODEC modes. Registers are used to accommodate the CODEC Interface (EXT5, EXT6 and EXT7). The CODEC interface provides two Frame Sync signals, which allows two channels of data for transmission/receiving.

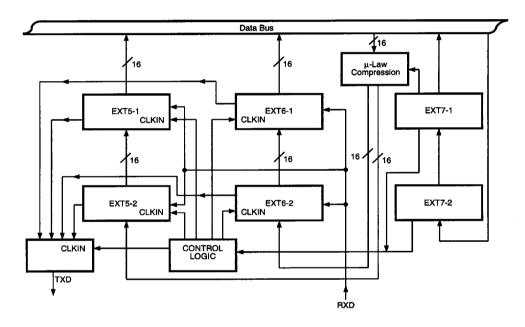

### **CODEC Interface Hardware**

The CODEC Interface hardware uses six 16-bit registers,  $\mu$ -law compression logic and general-purpose logic to control transfers to the appropriate register (Figure 10).

## **CODEC Interface Control Signals**

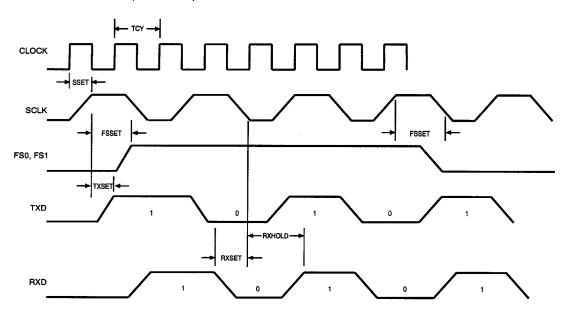

### **SCLK (Serial Clock)**

The Serial Clock provides a clock signal for operating the external CODEC. A 4-bit prescaler is used to determine the frequency of the output signal.

SCLK = (0.5\* CLK)/PS where: CLK = System Clock PS = 4-bit Prescaler\*

**Note:** An internal divide-by-two is performed before the clock signal is passed to the Serial Clock prescaler.

Figure 10. CODEC Interface Block Diagram

1-14

**9984043** 0027463 750 🖿

<sup>\*</sup> The Prescaler is an up-counter.

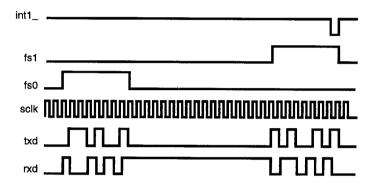

## TXD (Serial Output to CODEC)

The TXD line provides 8-, 16-, and 64-bit data transfers. Each bit is clocked out of the processor by the rising edge of the SCLK, with the MSB transmitted first.

#### RXD (Serial Input from CODEC)

The RXD line provides 8-, 16-, and 64-bit data transfers. Each bit is clocked into the processor by the falling edge of the SCLK, with the MSB received first.

### FS0, FS1 (Frame Sync)

The Frame Sync is used for enabling data transfer/receive. The rising and falling edge of the Frame Sync encloses the serial data transmission.

#### Interrupt

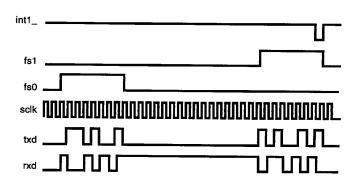

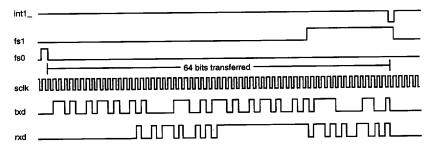

Once the transmission of serial data is completed an internal interrupt signal is initiated. A single-cycle Low pulse allows an interrupt on INT1. When this occurs, the processor will jump to the defined Interrupt 1 vector location (Figure 11).

Figure 11. CODEC Interface Timing (8-Bit Mode)

## **CODEC Interface Timing**

Figure 11 depicts a typical 8-bit serial data transfer using both of the CODEC Interface Channels. The transmitting data is clocked out on the rising edge of the SCLK signal. An external CODEC clocks data in on the falling edge of the SCLK signal. Once the serial data is transmitted, an interrupt is given. The CODEC interface signals are not initiated if the CODEC interface is not enabled.

The following modes are available for FSYNC and SCLK signals:

| SCLK     | FSYNC    |  |

|----------|----------|--|

| Internal | Internal |  |

| External | External |  |

| External | Internal |  |

| Internal | External |  |

The CODEC interface timing is independent of the processor clock when external mode is chosen. This feature provides the capability for an external device to control the transfer of data to the Z89321. The Frame Sync signal envelopes the transmitted data, therefore care must be taken to ensure proper sync signal timing (Figure 11).

### **Full Duplex Operation**

The Transmit and Receive lines are used for transfer of serial data to or from the CODEC interface. The CODEC interface performs both data transmit and receive simultaneously.

### **PERIPHERALS** (Continued)

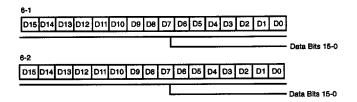

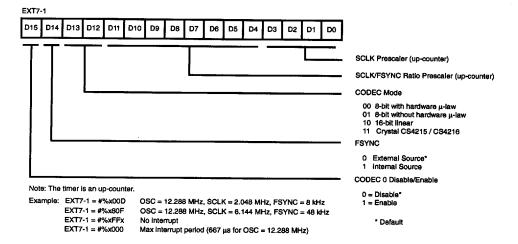

## **Control Registers**

The CODEC interface is double-buffered, therefore, four registers are provided for CODEC interface data storage. EXT5-1 and EXT5-2 operate with the Frame Sync 0 while EXT6-1 and EXT6-2 operate with Frame Sync 1. In 8- or 16-bit mode, the CODEC interface uses EXT5-1 and EXT6-1. For Stereo mode, all four registers are used (Figures 12 and 13).

The CODEC Interface Control Register (EXT7-1) is shown in Figure 14. Setting of the CODEC mode, FSYNC, and Enable/Disable of CODEC 0 is done through this register. The Wait-State Generator, SCLK, and CODEC 1 are controlled from EXT7-2 (Figure 14).

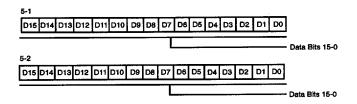

Figure 12. CODEC Interface Data Registers (Channel 0)

Figure 13. CODEC Interface Data Registers (Channel 1)

## Registers

Figure 14. CODEC Interface Control Register

Figure 15. WSG, SCLK and CODEC Interface Control Register

## **PERIPHERALS** (Continued)

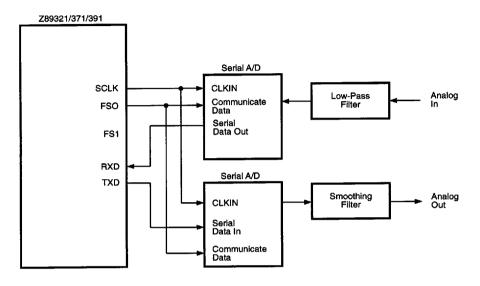

### A/D Accommodation

The CODEC interface can be used for serial A/D or serial D/A transmission. The interface provides the necessary control signals to adapt to many standard serial converters.

The low-pass and smoothing filters are necessary for systems with converters.

Figure 16. A/D, D/A Implementation Block Diagram

## **High-Speed Serial Port**

The Z89321 CODEC interface can be used as a highspeed serial port. The necessary control signals are provided for adaptation to standard processors or external peripherals. Byte, word, or 64-bit data can be transmitted at speeds up to 10 Mbps. (Condition includes a 20 MHz oscillator. Data can be transferred with single-cycle instructions to an internal register file.)

Table 7. Tabulated Transmission Rates\*

| Transmission       | Rate      |

|--------------------|-----------|

| Maximum SCLK       | 10 Mbps   |

| Maximum Frame Sync |           |

| 8-bit              | 769.2 kHz |

| 16-bit             | 476.2 kHz |

| Stereo (64-bit)    | 263.2 kHz |

#### Notes:

Calculations consider the interrupt access time (typically four cycles), transfer of data, loading of new data, and latency periods between CODEC transfers. During the interrupt cycle, developers often execute additional software, affecting the maximum transfer rate. Calculations are for single-channel transfers only.

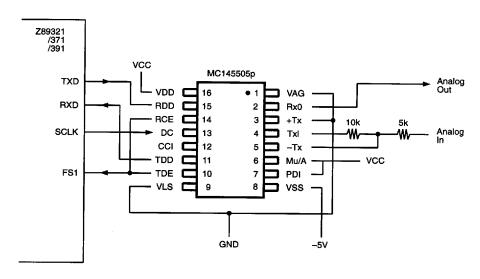

### 8-Bit CODEC Interface

The Z89321 provides an option for a standard 8-bit CODEC interface. Hardware  $\mu$ -law compression is available (expansion performed by software lookup table). The CODEC interface transmits data consisting of 8-bit or compounded 8-bit information. Figure 17 shows a typical schematic arrangement.

The timing for this type of arrangement is presented in Figure 18. The flexible design provides adaptation for 16-bit linear CODEC.

Figure 17. 8-Bit CODEC Schematic

Figure 18. 8-Bit Mode Timing Diagram

## **PERIPHERALS** (Continued)

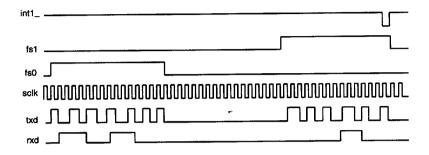

### 16-Bit Linear CODEC Interface

For higher precision transmissions, a 16-bit linear CODEC is used, however, data is not compressed in this mode of transmission. The Z89321 provides accommodation for two channels of 16-bit transmission (Figure 19). For data

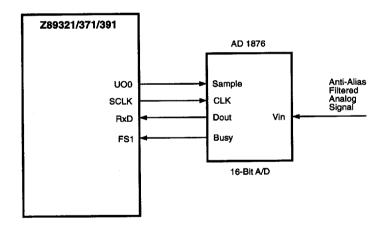

acquisition systems, designers may opt for a 16-bit serial A/D. A block diagram of the Z89321 with the AD1876 16-bit 100 Kbps sampling ADC is shown in Figure 20.

Figure 19. 16-Bit Mode Timing Diagram

Figure 20. 16-Bit Serial A/D

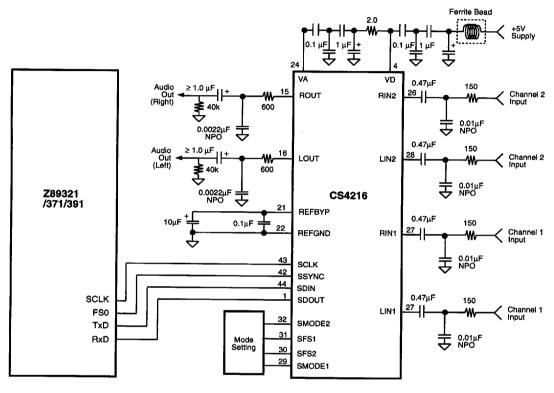

### Stereo CODEC Interface

The Z893XX DSP product family CODEC interface provides direct connection to other CODECs for master or slave modes, supporting 64 bits of transmission data (16 bits right channel, 16 bits left channel, and 32 bits of configuration information). This configuration information

consists of input gain, input MUX, output attenuation, ADC clipping, and mute and error functions of the CODECs. A key feature of the Z893XX DSP product family is that it adapts easily to other stereo CODECs, including Crystal Semiconductor's CS4215 and CS4216 devices (Figure 21).

Figure 21. Z893XX and CS4216 CODEC Interface

## **PERIPHERALS** (Continued)

The 64 bits of data transferred from the CODEC are placed in four registers, EXT5-1, 5-2, 6-1, and 6-2 (Figure 22).

Figure 22. CODEC Stereo Mode Timing Diagram

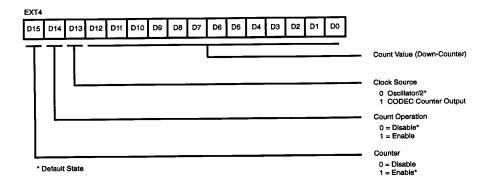

## 13-Bit General-Purpose Timer

The 13-bit counter/timer is available for general-purpose use. When the counter counts down to the zero state, an interrupt is received on INT2. If the counter is disabled, EXT4 can be used as a general-purpose address. The counting operation of the counter can be disabled by resetting bit 14. Selection of the clock source allows the ability to extend the counter value past the 13 bits available in the control register. Use of the CODEC counter output can extend the counter to 26 bits (see Figure 23).

#### Notes:

Placing zeroes into the count value register does not generate an interrupt. Therefore, it is possible to have a single-pass option by loading the counter with zeroes after the start of count.

The counter is defaulted to the enable state, but if it is not needed, it can be disabled. However, once disabled, the counter cannot be enabled unless a reset of the processor is performed.

## Example:

LD EXT, #%C008 ;1100 0000 0000 1000

; Enable Counter ; Enable Counting

; Clock Source = OSC/2 ; Count Value = 1000 = 8

; Interrupt will occur every

16 clock cycles

Figure 23. CODEC Timer Register

1-22

**■ 9984043 0027471 827 ■**

## ADDRESSING MODES

This section discusses the syntax of the addressing modes supported by the DSP assembler.

Table 8. Addressing Modes

| Symbolic Name                                                                            | Syntax                                                   | Description                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                          |                                                          |                                                                                                                                                                                                                          |

| <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre> | Pn:b                                                     | Pointer Register                                                                                                                                                                                                         |

| <dregs><br/>(Points to RAM)</dregs>                                                      | Dn:b                                                     | Data Register                                                                                                                                                                                                            |

| <hwregs></hwregs>                                                                        | X,Y,PC,SR,P<br>EXTn,A,BUS                                | Hardware Registers                                                                                                                                                                                                       |

| <accind><br/>(Points to Program Memory)</accind>                                         | @A                                                       | Accumulator Memory Indirect                                                                                                                                                                                              |

| <direct></direct>                                                                        | <expression></expression>                                | Direct Address Expression                                                                                                                                                                                                |

| <li><li><li><li></li></li></li></li>                                                     | # <const exp=""></const>                                 | Long (16-bit) Immediate Value                                                                                                                                                                                            |

| <simm></simm>                                                                            | # <const exp=""></const>                                 | Short (8-bit) Immediate Value                                                                                                                                                                                            |

| <regind><br/>(Points to RAM)</regind>                                                    | @Pn:b<br>@Pn:b+<br>@Pn:b-LOOP<br>@Pn:b+LOOP              | Pointer Register Indirect Pointer Register Indirect with Increment Pointer Register Indirect with Loop Decrement Pointer register Indirect with Loop Increment                                                           |

| <memind><br/>(Points to Program Memory)</memind>                                         | @@Pn:b<br>@Dn:b<br>@@Pn:b-LOOP<br>@@Pn:b+LOOP<br>@@Pn:b+ | Pointer Register Memory Indirect Data Register Memory Indirect Pointer Register Memory Indirect with Loop Decrement Pointer Register Memory Indirect with Loop Increment Pointer Register Memory Indirect with Increment |

## **ADDRESSING MODES** (Continued)

There are eight distinct addressing modes for data transfer.

<pregs>, <hwregs> These two modes are used for simple

loads to and from registers within the chip, such as loading

to the Accumulator, or loading from a pointer register. The

names of the registers need only be specified in the

operand field (destination first, then source).

<regind> This mode is used for indirect accesses to the data RAM. The address of the RAM location is stored in the pointer. The "@" symbol indicates "indirect" and precedes the pointer, therefore @P1:1 instructs the processor to read or write to a location in RAM1, which is specified by the value in the pointer.

<dregs> This mode is also used for accesses to the data RAM, but only the lower 16 addresses in either bank. The 4-bit address comes from the status register and the operand field of the data pointer. Note that data registers are typically used not for addressing RAM, but loading data from program memory space.

<memind> This mode is used for indirect accesses to the program memory. The address of the memory is located in a RAM location, which is specified by the value in a pointer. Therefore, @@P1:1 instructs the processor to read (write is not possible) from a location in memory, which is specified by a value in RAM, and the location of

the RAM is in turn specified by the value in the pointer. Note that the data pointer can also be used for a memory access in this manner, but only one "@" precedes the pointer. In both cases, the memory address stored in RAM is incremented by one, each time the addressing mode is used, to allow easy transfer of sequential data from program memory.

<accind> Similar to the previous mode, the address for the program memory read is stored in the Accumulator. @A in the second operand field loads the number in memory specified by the address in A.

<direct> The direct mode allows read or write to data RAM from the Accumulator by specifying the absolute address of the RAM in the operand of the instruction. A number between 0 and 255 indicates a location in RAMO, and a number between 256 and 511 indicates a location in RAM1.

This address mode indicates a long immediate load. A 16-bit word can be copied directly from the operand into the specified register or memory.

<simm> This address mode can only be used for immediate transfer of 8-bit data in the operand to the specified RAM pointer.

### **CONDITION CODES**

The following Instruction Description defines the condition codes supported by the DSP assembler. If the instruction description refers to the <cc> (condition code) symbol in

one of its addressing modes, the instruction will only execute if the condition is true.

| Code | Description            |

|------|------------------------|

| С    | Carry                  |

| EQ   | Equal (same as Z)      |

| F    | False                  |

| ΙE   | Interrupts Enabled     |

| MI   | Minus                  |

| NC   | No Carry               |

| NE   | Not Equal (same as NZ) |

| NIE  | Not Interrupts Enabled |

| NOV  | Not Overflow           |

| NUO  | Not User Zero          |

| Code | Description                    |

|------|--------------------------------|

| NU1  | Not User One                   |

| NZ   | Not zero                       |

| OV   | Overflow                       |

| PL   | Plus (Positive)                |

| UO   | User Zero                      |

| U1   | User One                       |

| UGE  | Unsigned Greater Than or       |

|      | Equal (Same as NC)             |

| ULT  | Unsigned Less Than (Same as C) |

| Z    | Zero                           |

1-24

9984043 0027473 677 1

## **INSTRUCTION DESCRIPTIONS**

| Inst. | Description      | Synopsis                              | Operands                                                            | Words | Cycles | Examples         |

|-------|------------------|---------------------------------------|---------------------------------------------------------------------|-------|--------|------------------|

| ABS   | Absolute Value   | ABS[ <cc>,]<src></src></cc>           | <cc>,A</cc>                                                         | 1     | 1      | ABS NC,A         |

|       |                  |                                       | Α                                                                   | 1     | 1      | ABS A            |

| \DD   | Addition         | ADD <dest>,<src></src></dest>         | A, <pregs></pregs>                                                  | 1     | 1      | ADD A,P0:0       |

|       |                  |                                       | A, <dregs></dregs>                                                  | 1     | 1      | ADD A,D0:0       |

|       |                  |                                       | A, <limm></limm>                                                    | 2     | 2      | ADD A,#%1234     |

|       |                  |                                       | A, <memind></memind>                                                | 1     | 3      | ADD A,@@P0:0     |

|       |                  |                                       | A, <direct></direct>                                                | 1     | 1      | ADD A,%F2        |

|       |                  |                                       | A, <regind></regind>                                                | 1     | 1      | ADD A,@P1:1      |

|       |                  |                                       | A, <hwregs></hwregs>                                                | 1     | 1      | ADD A,X          |

|       |                  |                                       | A, <simm></simm>                                                    |       |        | ADD A, #%12      |

| ND    | Bitwise AND      | AND <dest>,<src></src></dest>         | A, <pregs></pregs>                                                  | 1     | 1      | AND A,P2:0       |

|       |                  |                                       | A, <dregs></dregs>                                                  | 1     | 1      | AND A,D0:1       |

|       |                  |                                       | A, <limm⊳< td=""><td>2</td><td>2</td><td>AND A,#%1234</td></limm⊳<> | 2     | 2      | AND A,#%1234     |

|       |                  |                                       | A, <memind></memind>                                                | 1     | 3      | AND A,@@P1:0     |

|       |                  |                                       | A, <direct></direct>                                                | 1     | 1      | AND A,%2C        |

|       |                  |                                       | A, <regind></regind>                                                | 1     | 1      | AND A,@P1:2+L00P |

|       |                  |                                       | A, <hwregs></hwregs>                                                | 1     | 1      | AND A,EXT3       |

|       |                  |                                       | A, <simm></simm>                                                    |       |        | AND A, #%12      |

| ALL   | Subroutine call  | CALL [ <cc>,]<address></address></cc> | <cc>,<direct></direct></cc>                                         | 2     | 2      | CALL Z,sub2      |

|       |                  |                                       | <direct></direct>                                                   | 2     | 2      | CALL sub1        |

| CF    | Clear carry flag | CCF                                   | None                                                                | 1     | 1      | CCF              |

| CIEF  | Clear Carry Flag | CIEF                                  | None                                                                | 1     | 1      | CIEF             |

| OPF   | Clear OP flag    | COPF                                  | None                                                                | 1     | 1      | COPF             |

| P     | Comparison       | CP <src1>,<src2></src2></src1>        | A, <pregs></pregs>                                                  | 1     | 1      | CP A,P0:0        |

|       |                  |                                       | A, <dregs></dregs>                                                  | 1     | 1      | CP A,D3:1        |

|       |                  |                                       | A, <memind></memind>                                                | 1     | 3      | CP A,@@P0:1      |

|       |                  |                                       | A, <direct></direct>                                                | 1     | 1      | CP A,%FF         |

|       |                  |                                       | A, <regind></regind>                                                | 1     | 1      | CP A,@P2:1+      |

|       |                  |                                       | A, <hwregs></hwregs>                                                | 1     | 1      | CP A,STACK       |

|       |                  |                                       | A <limm></limm>                                                     | 2     | 2      | CP A,#%FFCF      |

|       |                  |                                       | A, <simm></simm>                                                    |       |        | CP A, #%12       |

| EC    | Decrement        | DEC [ <cc>,]<dest></dest></cc>        | <cc>A,</cc>                                                         | 1     | 1      | DEC NZ,A         |

|       |                  |                                       | Α                                                                   | 1     | 1      | DEC A            |

| VC    | Increment        | INC ( <cc>,) <dest></dest></cc>       | <cc>,A</cc>                                                         | 1     | 1      | INC PL,A         |

|       |                  |                                       | Α                                                                   | 1     | 1      | INC A            |

| Р     | Jump             | JP [ <cc>,]<address></address></cc>   | <cc>,<direct></direct></cc>                                         | 2     | 2      | JP NIE,Label     |

|       |                  |                                       | <direct></direct>                                                   | 2     | 2      | JP Label         |

## **INSTRUCTION DESCRIPTIONS** (Continued)

| Inst. | Description      | Synopsis                                                   | Operands                                                                                                                                             | Words                                                                   | Cycles                                                          | Examples                                           |

|-------|------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------|

| LD    | Load destination | LD <dest>,<src></src></dest>                               | A, <hwregs></hwregs>                                                                                                                                 | 1                                                                       | 1                                                               | LD A,X                                             |

|       | with source      |                                                            | A, <dregs></dregs>                                                                                                                                   | 1                                                                       | 1                                                               | LD A,D0:0                                          |

|       |                  |                                                            | A, <pregs></pregs>                                                                                                                                   | 1                                                                       | 1                                                               | LD A,P0:1                                          |

|       |                  |                                                            | A, <regind></regind>                                                                                                                                 | 1                                                                       | 1                                                               | LD A,@P1:1                                         |

|       |                  |                                                            | A, <memind></memind>                                                                                                                                 | 1                                                                       | 3                                                               | LD A,@D0:0                                         |

|       |                  |                                                            | A, <direct></direct>                                                                                                                                 | 1                                                                       | 1                                                               | LD A,124                                           |

|       |                  |                                                            | <direct>,A</direct>                                                                                                                                  | 1                                                                       | 1                                                               | LD 124,A                                           |

|       |                  |                                                            | <dregs>,<hwregs></hwregs></dregs>                                                                                                                    | 1                                                                       | 1                                                               | LD D0:0,EXT7                                       |

|       |                  |                                                            | <pre><pregs>,<simm></simm></pregs></pre>                                                                                                             | 1                                                                       | 1                                                               | LD P1:1,#%FA                                       |

|       |                  |                                                            | <pre><pregs>,<hwregs></hwregs></pregs></pre>                                                                                                         | 1                                                                       | 1                                                               | LD P1:1,EXT1                                       |

|       |                  |                                                            | <regind>,<limm></limm></regind>                                                                                                                      | 1                                                                       | 1                                                               | LD@P1:1,#1234                                      |

|       |                  |                                                            | <regind>,<hwregs></hwregs></regind>                                                                                                                  | 1                                                                       | 1                                                               | LD @P1:1+,X                                        |

|       |                  |                                                            | <hwregs>,<pregs></pregs></hwregs>                                                                                                                    | 1                                                                       | 1                                                               | LD Y,P0:0                                          |

|       |                  |                                                            | <hwregs>,<dregs></dregs></hwregs>                                                                                                                    | 1                                                                       | 1                                                               | LD SR,D0:0                                         |

|       |                  |                                                            | <hwregs>,<limm></limm></hwregs>                                                                                                                      | 2                                                                       | 2                                                               | LD PC,#%1234                                       |

|       |                  |                                                            | <hwregs>,<accind></accind></hwregs>                                                                                                                  | 1                                                                       | 3                                                               | LD X.@A                                            |

|       |                  |                                                            | <hwregs>,<memind></memind></hwregs>                                                                                                                  | i                                                                       | 3                                                               | LD Y,@D0:0                                         |

|       |                  |                                                            | <hwregs>,<regind></regind></hwregs>                                                                                                                  | i                                                                       | 1                                                               | LD A,@P0:0-L00P                                    |

|       |                  |                                                            | <hwregs>,<hwregs></hwregs></hwregs>                                                                                                                  | i                                                                       | i                                                               | LD X,EXT6                                          |

|       |                  |                                                            | if <src> is EXTn, <dest> if <src> is SR.  Note: When <src> is <accind></accind></src></src></dest></src>                                             |                                                                         |                                                                 | is X, <dest> cannot be SF</dest>                   |

| MLD   | Multiply         | MLD <srcl>,<srcl>[,<bank switch="">]</bank></srcl></srcl>  | <hwregs>,<regind></regind></hwregs>                                                                                                                  | 1                                                                       | 1                                                               | MLD A,@P0:0+L00P                                   |

|       | • •              |                                                            | <hwregs>,<regind>,<bank switch<="" td=""><td>1&gt; 1</td><td>1</td><td>MLD A,@P1:0,0FF</td></bank></regind></hwregs>                                 | 1> 1                                                                    | 1                                                               | MLD A,@P1:0,0FF                                    |

|       |                  |                                                            | <regind>,<regind></regind></regind>                                                                                                                  | 1                                                                       | 1                                                               | MLD @P1:1,@P2:0                                    |

|       |                  |                                                            | <regind>,<regind>,<bank switch<="" td=""><td>&gt; 1</td><td>1</td><td>MLD @P0:1,@P1:0,0N</td></bank></regind></regind>                               | > 1                                                                     | 1                                                               | MLD @P0:1,@P1:0,0N                                 |

|       |                  |                                                            | Note: If src1 is <regind> it mus a bank 0 register.</regind>                                                                                         | t be a ba                                                               | nk 1 regis                                                      | ter. Src2's <regind be<="" must="" td=""></regind> |

|       |                  |                                                            | Note: <hwregs> for src1 canno</hwregs>                                                                                                               | t be X.                                                                 |                                                                 |                                                    |

|       |                  |                                                            | Note: For the operands < hwrege                                                                                                                      |                                                                         | nd>the <ba< td=""><td>and switch&gt; defaults to OFF</td></ba<> | and switch> defaults to OFF                        |

|       |                  |                                                            | For the operands < regine                                                                                                                            | d>, the <i< td=""><td>ank switc</td><td>h&gt; defaults to ON.</td></i<> | ank switc                                                       | h> defaults to ON.                                 |