### PRELIMINARY CUSTOMERPROCUREMENTSPECIFICATION

Z89323/373/393

16-BIT DIGITAL SIGNAL PROCESSORS

### FEATURES

| Device | DSP ROM<br>(K Words) | OTP<br>(K Words) | DSP RAM<br>(Words) | Max Core<br>MIPS |

|--------|----------------------|------------------|--------------------|------------------|

| Z89323 | 8                    |                  | 512                | 20               |

| Z89373 |                      | 8                | 512                | 16               |

| Z89393 | 64*                  |                  | 512                | 20               |

\* External

- Operating Temperature Ranges: 0°C to +70°C (Standard) -40°C to +85°C (Extended)

- 4.5- to 5.5-Volt Operating Range

### **DSP** Core

- 20 MIPS @ 20 MHz, 16-Bit Fixed Point DSP

- 50 ns Instruction Cycle Time

- Single-Cycle Multiply and ALU Operations

- Two Internal Data Buses and Address Generators

- Six Register Address Pointers

- Optimized Instruction Set (30 Instructions)

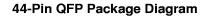

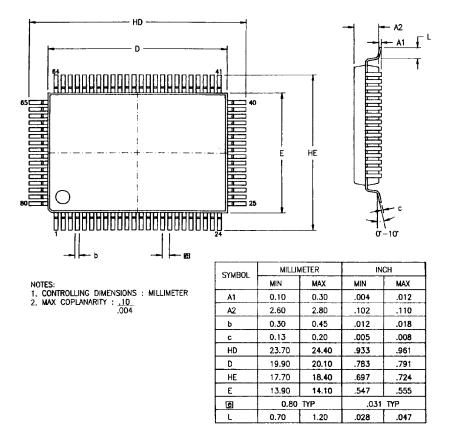

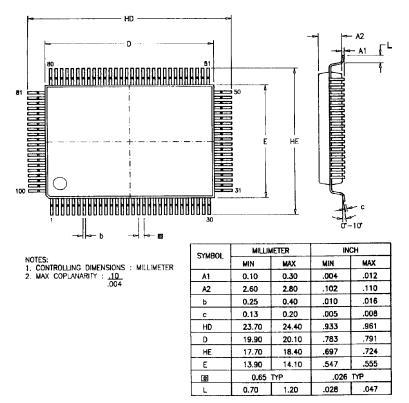

| Package<br>Device | 44-Pin<br>PLCC | 68-Pin<br>PLCC | 44-Pin<br>QFP | 80-Pin<br>QFP | 100-Pin<br>QFP |

|-------------------|----------------|----------------|---------------|---------------|----------------|

| Z89323            | ~              | ~              | ~             | ~             |                |

| Z89373            | ✓              | ~              | ~             | ~             |                |

| Z89393            |                |                |               |               | ~              |

### **On-Board Peripherals**

- 4-Channel, 8-Bit Analog to Digital Converter (A/D)

- On-Board Serial Peripheral Interface (SPI)

- Up to 40 Bits of Programmable I/O

- Two Channels of Programmable Pulse Width Modulators (PWM)

- Three General-Purpose Timer/Counters

- Two Watch-Dog Timers (WDT)

- Programmable PLL

- Three Vectored Interrupts Servicing Eight Interrupt Sources

- Power-Down and Power-On Reset

### **GENERAL DESCRIPTION**

The Z89323/373/393 DSP family of products builds on Zilog's first generation Z893XX DSP core, integrating several peripherals especially well suited for cost-effective voice, telephony, and control applications.

These DSP devices feature a modified Harvard architecture supported by one program bus and two on-chip data buses. This bus structure is supported by two address generators and six register pointers to ensure that the 20 MIPS DSP CPU is continually active.

The Z893X3 DSP family is designed to provide a complete DSP and control system on a single chip. By integrating

various peripherals, such as a high-speed 4-channel, 8-bit A/D, an SPI, three timers with PWM and WDT support, the Z893X3 family provides a compact system solution and reduces overall system cost.

To support a wide variety of development needs, the Z893X3 DSP product family features the cost-effective Z89323 with 8 Kwords of on-chip ROM, and the Z89373, a 16-MIPS OTP version of the Z89323, ideal for prototypes and early production builds. For systems requiring more than 8 Kwords of program memory, the Z89393 device can address up to 64 Kwords of external program memory.

### DS95DSP0101 Q4/95

## **GENERAL DESCRIPTION** (Continued)

The Z893X3 DSP family is 100 percent source and objectcode compatible with the existing Z89321/371/391 devices, providing users, who can benefit from increased integration and reduced system cost, an easy migration path from one DSP product to the next.

Throughout this specification, references to the Z89323 device applies equally to the Z89373 and Z89393, unless otherwise specified.

#### Notes:

All Signals with a preceding front slash, "/", are active Low, e.g., B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>cc</sub> | V <sub>DD</sub> |

| Ground     | GND             | $V_{ss}$        |

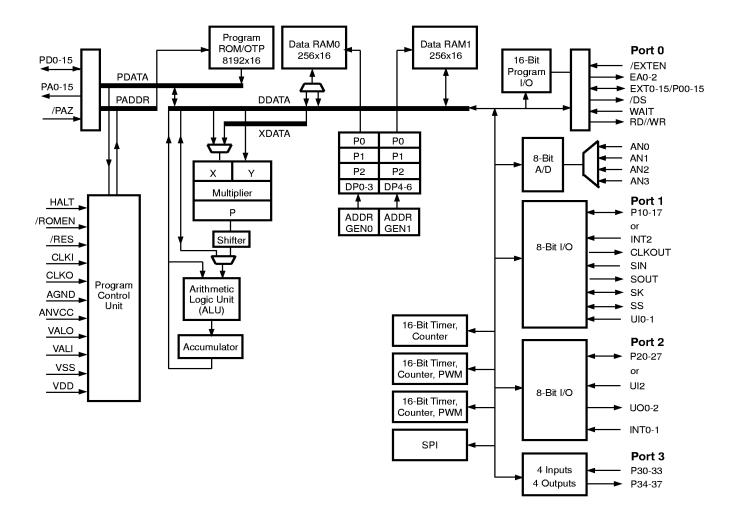

Figure 1. Z893X3 Functional Block Diagram

## **PIN DESCRIPTION**

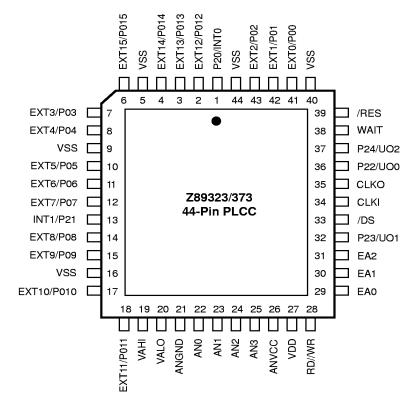

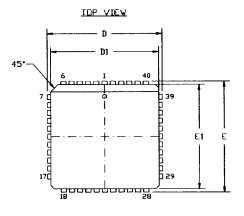

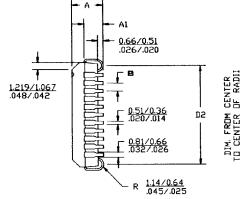

Figure 2. 44-Pin PLCC Z89323/373 Pin Configuration

| No. | Symbol          | Function          | Direction | No. | Symbol          | Function           | Direction |

|-----|-----------------|-------------------|-----------|-----|-----------------|--------------------|-----------|

| 1   | P20/INT0        | Port20/Interrupt0 | In/Output | 23  | ANI             | A/DInput1          | Input     |

| 2   | EXT12/P012      | ExtData12/Port012 | In/Output | 24  | AN2             | A/DInput2          | Input     |

| 3   | EXT13/P013      | ExtData13/Port013 | In/Output | ත   | ANB             | A/DInput3          | Input     |

| 4   | EXT14/P014      | ExtData14/Port014 | In/Output | 26  | ANACC           | AnalogPower        | Input     |

| 5   | Vss             | Ground            |           | 27  | V <sub>DD</sub> | Power              | •         |

| 6   | EXT15/P015      | ExtData15/Port015 | In/Output | 28  | RD/WR           | RWExternalBus      | Culput    |

| 7   | EXT3/P03        | ExtData3/Port03   | In/Output | 29  | EAO             | ExtAddress0        | Cutput    |

| 8   | EXT4/P04        | ExtData4/Port04   | In/Output | 30  | EA1             | ExtAddress1        | Cutput    |

| 9   | V <sub>ss</sub> | Ground            |           | 31  | EA2             | ExtAddress2        | Cutput    |

| 10  | EXT5/P05        | ExtData5/Port05   | In/Output | 32  | P23/UO1         | Port23/UserOutput1 | In/Output |

| 11  | EXT6P06         | ExtData6/Port06   | In/Output | 33  | /DS             | ExtDataStrobe      | Cutput    |

| 12  | EXT7/P07        | ExtData7/Port07   | In/Output | 34  | ак              | Clock/Crystalln    | Input     |

| 13  | P21/INT1        | Port21/Interrupt1 | In/Output | 35  | aко             | Clock/CrystalOut   | Input     |

| 14  | EXT8/P08        | ExtData8/Port08   | In/Output | 36  | P22/UO0         | Port22/UserOutput0 | In/Output |

| 15  | EXT9/P09        | ExtData9/Port09   | In/Output | 37  | P24/UO2         | Port24/UserOutput2 | In/Output |

| 16  | V <sub>ss</sub> | Ground            |           | 38  | WAIT            | WaitforExt         | Input     |

| 17  | EXT10/P010      | ExtData10/Port010 | In/Output | 39  | RES             | Reset              | Input     |

| 18  | EXT11/P011      | ExtData11/Port011 | In/Output | 40  | V <sub>ss</sub> | Ground             |           |

| 19  | VAH             | AnalogHighRef.    | Input     | 41  | EXT0/P00        | ExtData0/Port00    | In/Output |

| 20  | VALO            | AnalogLowRef.     | Input     | 42  | EXT1/P01        | ExtData1/Port01    | In/Output |

| 21  | ANGND           | AnalogGround      | Input     | 43  | EXT2/P02        | ExtData2/Port02    | In/Output |

| 22  | AND             | A/DInput0         | Input     | 44  | Vss             | Ground             | -         |

#### Table 1. 44-Pin PLCC Z89323/373 Pin Description

DS95DSP0101 Q4/95

كالك

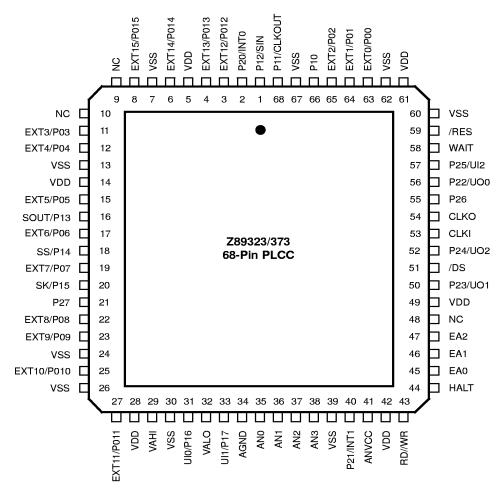

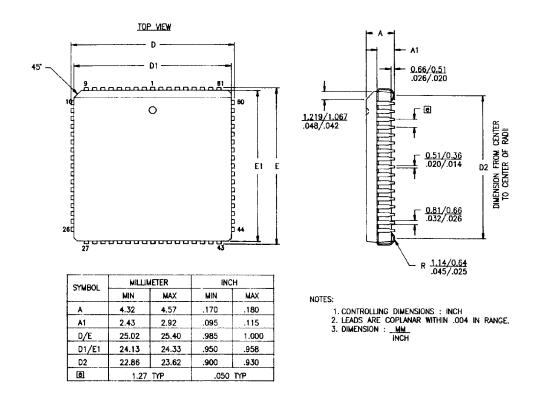

Figure 3. 68-Pin PLCC Z89323/373 Pin Configuration

4

### Table 2. 68-Pin PLCC Z89323/373 Pin Description

| No. | Symbol                | Function            | Direction | No. | Symbol          | Function           | Direction |

|-----|-----------------------|---------------------|-----------|-----|-----------------|--------------------|-----------|

| 1   | P12/SIN               | Port12/SerialInput  | In/Output | 35  | AND             | A/DInput0          | Input     |

| 2   | P20/INT0              | Port20/Interrupt0   | In/Output | 36  | ANI             | A/DInput1          | Input     |

| 3   | EXT12/P012            | ExtData12/Port012   | In/Output | 37  | AN2             | A/DInput2          | Input     |

| 4   | EXT13/P013            | ExtData13/Port013   | In/Output | 38  | ANB             | A/DInput3          | Input     |

| 5   | VDD                   | Power               |           | 39  | V <sub>ss</sub> | Giound             |           |

| 6   | EXT14/P014            | ExtData14/Port014   | In/Output | 40  | P21/INT1        | Port21/Interrupt1  | In/Output |

| 7   | V <sub>ss</sub>       | Ground              |           | 41  | ANACC           | AnalogPower        | Input     |

| 8   | EXT15/P015            | ExtData15/Port015   | In/Output | 42  | V <sub>DD</sub> | Power              | Input     |

| 9   | NC                    | NoConnection        |           | 43  | RĎ/WR           | RWExternalBus      | Cutput    |

| 10  | NC                    | NoConnection        |           | 44  | HALT            | HaltExecution      | Input     |

| 11  | EXT3/P03              | ExtData3/Port03     | In/Output | 45  | EA0             | ExtAddress0        | Cutput    |

| 12  | EXT4/P04              | ExtData4/Port04     | In/Output | 46  | EA1             | ExtAddress1        | Cutput    |

| 13  | V <sub>ss</sub>       | Ground              |           | 47  | EA2             | ExtAddress2        | Cutput    |

| 14  | $V_{DD}^{m}$          | Power               |           | 48  | NC              | NoConnection       |           |

| 15  | EXT5/P05              | ExtData5/Port05     | In/Output | 49  | $V_{DD}$        | Power              |           |

| 16  | P13SOUT               | Port13/SerialOutput | In/Output | 50  | P23/U01         | Port23/UserOutput1 | In/Output |

| 17  | EXT6/P06              | ExtData6/Port06     | In/Output | 51  | /DS             | ExtDataStrobe      | Cutput    |

| 18  | P14/SS                | Port14/SerialSelect | In/Output | 52  | P24U02          | Port24/UserOutput2 | In/Output |

| 19  | EXT7/P07              | ExtData7/Port07     | In/Output | 53  | ам              | Clock/CrystalIn    | Input     |

| 20  | P155K                 | Port15/SerialClock  | In/Output | 54  | ако             | Clock/CrystalOut   | Input     |

| 21  | P27                   | Port27              | In/Output | 55  | P26             | Port26             | In/Output |

| 22  | EXT8/P08              | ExtData8/Port08     | In/Output | 56  | P22/UC0         | Port22/UserOutput0 | In/Output |

| 23  | EXT9/P09              | ExtData9/Port09     | In/Output | 57  | P25/U12         | Port25/UserInput2  | In/Output |

| 24  | V <sub>ss</sub>       | Ground              | -         | 58  | WAT             | WaitforExt         | Input     |

| ත   | EXT10/P010            | ExtData10/Port010   | In/Output | 59  | RES             | Reset              | Input     |

| 26  | V<br>SS<br>EXT11/P011 | Ground              |           | 60  | V<br>Ss<br>V    | Giound             |           |

| 27  | EXT11/P011            | ExtData11/Port011   | In/Output | 61  | ٧ <sub>m</sub>  | Power              |           |

| 28  | $V_{DD}$              | Power               |           | 62  | V <sub>cc</sub> | Giound             |           |

| 29  | VÄH                   | AnalogHighRef.      | Input     | 63  | EXT0/P00        | ExtData0/Port00    | In/Output |

| 30  | V <sub>ss</sub>       | Ground              |           | 64  | EXT1/P01        | ExtData1/Port01    | In/Output |

| 31  | P16/U10               | Port16/UserInput0   | In/Output | 65  | EXT2/P02        | ExtData2/Port02    | In/Output |

| 32  | VALO                  | AnalogLowRef.       | Input     | 66  | P10/INT2        | Port10/Interrupt2  | In/Output |

| 33  | P17/Ul1               | Port17/UserInput1   | In/Output | 67  | Vss             | Giound             | •         |

| 34  | ANGND                 | AnalogGround        | Input     | 68  | PII ALKOUT      | Port11/ClockOutput | In/Output |

| No. | Symbol          | Function          | Direction | No. | Symbol          | Function           | Direction |

|-----|-----------------|-------------------|-----------|-----|-----------------|--------------------|-----------|

| 1   | EXT3/P03        | ExtData3/Port03   | In/Output | 23  | E#0             | ExtAddress0        | Cutput    |

| 2   | EXT4/P04        | ExtData4/Port04   | In/Output | 24  | EA1             | ExtAddress1        | Output    |

| 3   | V <sub>ss</sub> | Ground            |           | න   | EA2             | ExtAddress2        | Cutput    |

| 4   | EXT5/P05        | ExtData5/Port05   | In/Output | 26  | P23U01          | Port23/UserOutput1 | In/Output |

| 5   | EXT6/P06        | ExtData6/Port06   | In/Output | 27  | /DS             | ExtDataStrobe      | Cutput    |

| 6   | EXT7/P07        | ExtData7/Port07   | In/Output | 28  | ам              | Clock/Crystalln    | Input     |

| 7   | P21/INT1        | Port21/Interrupt1 | In/Output | 29  | aко             | Clock/CrystalOut   | Input     |

| 8   | EXT8/P08        | ExtData8/Port08   | In/Output | 30  | P22/UC0         | Port22/UserOutput0 | In/Output |

| 9   | EXT9/P09        | ExtData9/Port09   | In/Output | 31  | P24/UO2         | Port24/UserOutput2 | In/Output |

| 10  | Vss             | Ground            |           | 32  | WAIT            | WaitforExt         | Input     |

| 11  | EXT10/P010      | ExtData10/Port010 | In/Output | 33  | /RES            | Reset              | Input     |

| 12  | EXT11/P011      | ExtData11/Port011 | In/Output | 34  | V <sub>ss</sub> | Ground             |           |

| 13  | VAH             | AnalogHighRef.    | Input     | 35  | EXT0/P00        | ExtData0/Port00    | In/Output |

| 14  | VALO            | AnalogLowRef.     | Input     | 36  | EXT1/P01        | ExtData1/Port01    | In/Output |

| 15  | ANGND           | AnalogGround      | Input     | 37  | EXT2/P02        | ExtData2/Port02    | In/Output |

| 16  | AND             | A/DInput0         | Input     | 38  | Vss             | Ground             |           |

| 17  | ANI             | A/DInput1         | Input     | 39  | P20/INT0        | Port20/Interrupt0  | In/Output |

| 18  | AN2             | A/DInput2         | Input     | 40  | EXT12/P012      | ExtData12/Port012  | In/Output |

| 19  | ANB             | A/DInput3         | Input     | 41  | EXT13/P013      | ExtData13/Port013  | In/Output |

| 20  | ANACC           | AnalogPower       | Input     | 42  | EXT14/P014      | ExtData14/Port014  | In/Output |

| 21  | $V_{DD}$        | Power             |           | 43  | V <sub>ss</sub> | Ground             |           |

| 22  | RD/WR           | RWExternalBus     | Output    | 44  | EXT15/P015      | ExtData15/Port015  | In/Output |

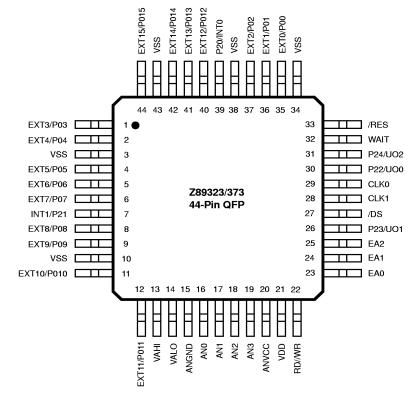

| Table 3. 44-Pin QFP Z89323/373 Pin Descriptio |

|-----------------------------------------------|

|-----------------------------------------------|

DS95DSP0101 Q4/95

6

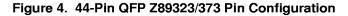

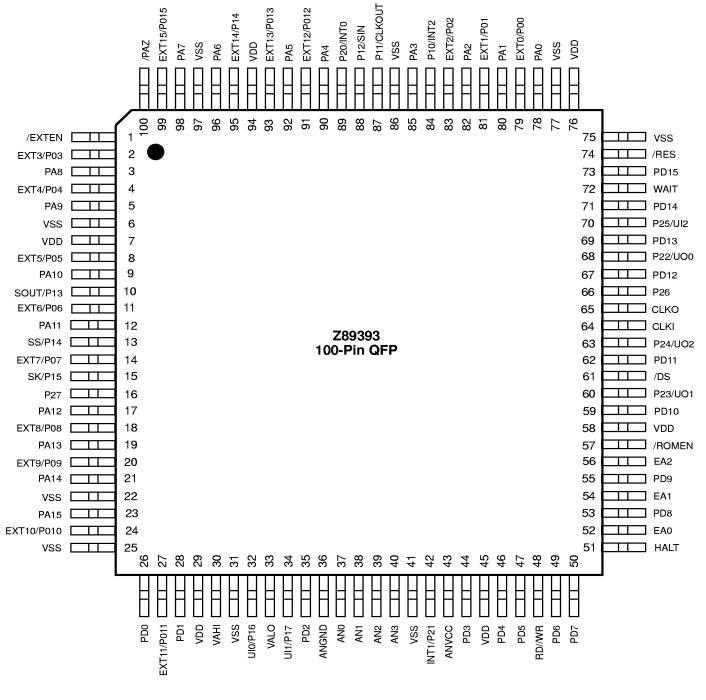

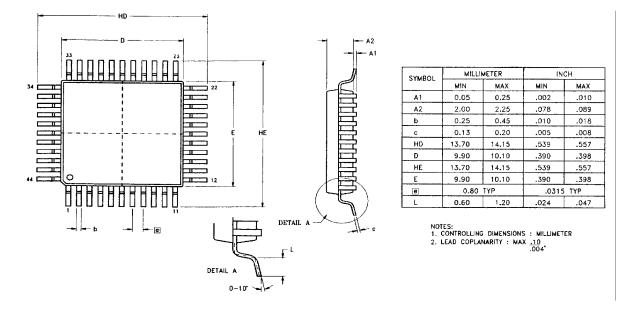

Figure 4a. 80-Pin QFP Z89323/373 Pin Configuration

### Table 4a. 80-Pin QFP Z89323/373 Pin Description

| No. | Symbol                     | Function            | Direction | No. | Symbol                                  | Function           | Direction |

|-----|----------------------------|---------------------|-----------|-----|-----------------------------------------|--------------------|-----------|

| 1   | NC                         | NoConnection        |           | 41  | RD/WR                                   | RWExternalBus      | Cutput    |

| 2   | EXT15/P015                 | ExtData15/Port015   | In/Output | 42  | P35                                     | Port35             | Output    |

| 3   | /EXTEN                     | ExtEnable           | Input     | 43  | NC                                      | NoConnection       | •         |

| 4   | NC                         | NoConnection        |           | 44  | HALT                                    | HaltExecution      | Input     |

| 5   | EXT3/P03                   | ExtData3/Port03     | In/Output | 45  | <b>E</b> 40                             | ExtAddress0        | Output    |

| 6   | P32                        | Port32              | Input     | 46  | P36                                     | Port36             | Output    |

| 7   | EXT4/P04                   | ExtData4/Port04     | In/Output | 47  | EA1                                     | ExtAddress1        | Cutput    |

| 8   | V <sub>ss</sub>            | Ground              | •         | 48  | <b>EA2</b>                              | ExtAddress2        | Output    |

| 9   | V <sub>m</sub>             | Power               |           | 49  | NC                                      | NoConnection       | •         |

| 10  | EXT5/P05                   | ExtData5/Port05     | In/Output | 50  | $V_{DD}$                                | Power              |           |

| 11  | P13SOUT                    | Port13/SerialOutput | In/Output | 51  | P23/U01                                 | Port23/UserOutput1 | In/Output |

| 12  | EXT6/P06                   | ExtData6/Port06     | In/Output | 52  | /DS                                     | ExtDataStrobe      | Cutput    |

| 13  | P14/SS                     | Port14/SerialSelect | In/Output | 53  | P24U02                                  | Port24/UserOutput2 | In/Output |

| 14  | EXT7/P07                   | ExtData7/Port07     | In/Output | 54  | aк                                      | Clock/Crystalln    | Input     |

| 15  | P155K                      | Port15/SerialClock  | In/Output | 55  | аю                                      | Clock/CrystalOut   | Input     |

| 16  | P27                        | Port27              | In/Output | 56  | P26                                     | Port26             | In/Output |

| 17  | EXT8/P08                   | ExtData8/Port08     | In/Output | 57  | P22/UC0                                 | Port22/UserOutput0 | In/Output |

| 18  | EXT9/P09                   | ExtData9/Port09     | In/Output | 58  | P25/U12                                 | Port25/UserInput2  | In/Output |

| 19  | V <sub>m</sub>             | Ground              |           | 59  | WAT                                     | WaitforExt         | Input     |

| 20  | V<br>SS<br>P33             | Port33              | Input     | 60  | P37                                     | Port37             | Cutput    |

| 21  | EXT10/P010                 | ExtData10/Port010   | In/Output | 61  | RES                                     | Reset              | Input     |

| 22  | V <sub>ss</sub><br>NC      | Ground              |           | 62  | V <sub>ss</sub>                         | Ground             |           |

| 23  | NČ                         | NoConnection        |           | 63  | ۷ <sub>m</sub>                          | Power              |           |

| 24  | P34                        | Port34              | Cutput    | 64  | V <sub>ss</sub><br>V <sub>⊡</sub><br>NC | NoConnection       |           |

| 25  | EXT11/P011                 | ExtData11/Port011   | In/Output | 65  | V<br>ss<br>P30                          | Ground             |           |

| 26  | V <sub>ID</sub><br>VAH     | Power               |           | 66  | P30                                     | Port30             | Input     |

| 27  | VÄH                        | AnalogHighRef.      | Input     | 67  | EXT0/P00                                | ExtData0/Port00    | In/Output |

| 28  | V <sub>cc</sub>            | Ground              |           | 68  | EXT1/P01                                | ExtData1/Port01    | In/Output |

| 29  | V <sub>ss</sub><br>P16/U10 | Port16/UserInput0   | In/Output | 69  | EXT2/P02                                | ExtData2/Port02    | In/Output |

| 30  | VALO                       | AnalogLowRef.       | Input     | 70  | P10/INT2                                | Port10/Interrupt2  | In/Output |

| 31  | P17/Ul1                    | Port17/UserInput1   | In/Output | 71  | V <sub>ss</sub>                         | Ground             |           |

| 32  | ANGND                      | AnalogGround        | Input     | 72  | P11/CLKOUT                              | Port11/ClockOutput | In/Output |

| 33  | AND                        | A/DInput0           | Input     | 73  | P12/SIN                                 | Port12/SerialInput | In/Output |

| 34  | ANI                        | A/DInput1           | Input     | 74  | P20/INT0                                | Port20/Interrupt0  | In/Output |

| 35  | AN2                        | A/DInput2           | Input     | 75  | EXT12/P012                              | ExtData12/Port012  | In/Output |

| 36  | ANB                        | A/DInput3           | Input     | 76  | EXT13/P013                              | ExtData13/Port013  | In/Output |

| 37  | V <sub>ss</sub>            | Ground              | -         | 77  | $V_{DD}$                                | Power              | -         |

| 38  | P21/INT1                   | Port21/Interrupt1   | In/Output | 78  | EXT14/P014                              | ExtData14/Port014  | In/Output |

| 39  | ANACC                      | AnalogPower         | Input     | 79  | V <sub>ss</sub><br>P31                  | Ground             | -         |

| 40  | $V_{DD}$                   | Power               | Input     | 80  | P31                                     | Port31             | Input     |

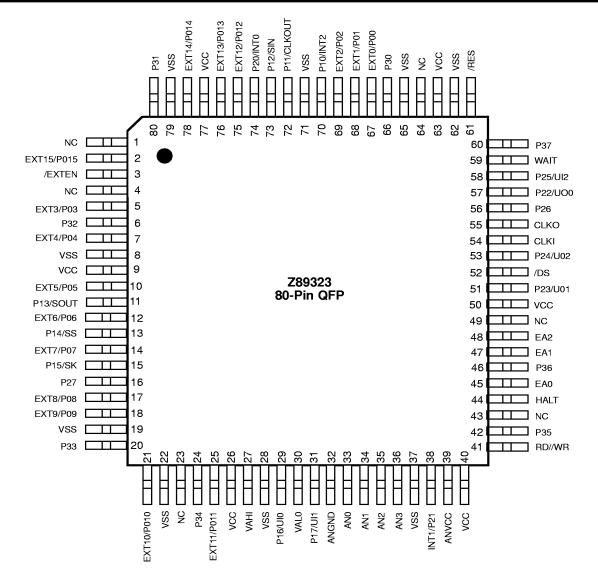

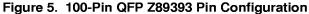

| No.      | Symbol          | Function                        | Direction      | No.      | Symbol          | Function            | Direction |

|----------|-----------------|---------------------------------|----------------|----------|-----------------|---------------------|-----------|

| 1        | /EXTEN          | EXTEnable                       | Input          | 51       | HALT            | HaltExecution       | Input     |

| 2        | EXT3/P03        | ExtData3/Port03                 | In/Output      | 52       | EAO             | ExtAddress0         | Cutput    |

| 3        | P#8             | ProgramAddress8                 | Output         | 53       | PD8             | ProgramData8        | Input     |

| 4        | EXT4/P04        | ExtData4/Port04                 | In/Output      | 54       | EA1             | ExtAddress1         | Ċitput    |

| 5        | PA9             | ProgramAddress9                 | Output         | 55       | PD9             | ProgramData9        | Input     |

| 6        | V <sub>ss</sub> | Ground                          |                | 56       | EA2             | ExtAddress2         | Cutput    |

| 7        | V <sub>DD</sub> | Power                           |                | 57       | ROMEN           | ROMEnable           | Input     |

| 8        | EXT5/P05        | ExtData5/Port05                 | In/Output      | 58       | $V_{DD}$        | Power               | " poc     |

| 9        | PA10            | ProgramAddress10                | Output         | 59       | PD10            | ProgramData10       | Input     |

| 9<br>10  | P13SOUT         | 0                               |                | 60       | P23U01          | Port23/UserOutput1  |           |

|          |                 | Port13/SerialOutput             | In/Output      |          |                 | •                   | In/Output |

| 11       | EXT6/P06        | ExtData6/Port06                 | In/Output      | ଗ        | /DS             | ExtDataStrobe       | Cutput    |

| 12       | PA11            | ProgramAddress11                | Output         | 62       | PD11            | ProgramData11       | Input     |

| 13       | P14/SS          | Port14/SerialSelect             | In/Output      | 63       | P24UO2          | Port24/UserOutput2  | In/Output |

| 14       | EXT7/P07        | ExtData7/Port07                 | In/Output      | 64       | aк              | Clock/CrystalIn     | Input     |

| 15       | P15SK           | Port15/SerialClock              | In/Output      | 65       | ako             | Clock/CrystalOut    | Input     |

| 16       | P27             | Port27                          | In/Output      | 66       | P26             | Port26              | In/Output |

| 17       | PA12            | ProgramAddress12                | Output         | 67       | PD12            | ProgramData12       | Input     |

| 18       | EXT8/P08        | ExtData8/Port08                 | In/Output      | 68       | P22UC0          | Port22/UserOutput0  | In/Output |

| 19       | PA13            | ProgramAddress13                | Output         | 69       | PD13            | ProgramData13       | Input     |

| 20       | EXT9/P09        | ExtData9/Port09                 | In/Output      | 70       | P25/U12         | Port25/UserInput2   | In/Output |

| 21       | PA14            | ProgramAddress14                | Output         | 71       | PD14            | ProgramData14       | Input     |

| 22       | V <sub>ss</sub> | Ground                          | Capor          | 72       | WAIT            | WaitforExt          | Input     |

| 23       | PA15            | ProgramAddress15                | Output         | 73       | PD15            | ProgramData 15      | Input     |

| 24       | EXT10/P010      | ExtData10/Port010               | In/Output      | 74       | RES             | Reset               | Input     |

| 25       |                 |                                 | ii VOuput      | 75       |                 | Ground              | npor      |

|          | V<br>SS<br>FD0  | Ground<br>Dimension             | luno. t        |          | V <sub>SS</sub> |                     |           |

| 26<br>77 |                 | ProgramData0                    | Input          | 76<br>77 | V <sub>D</sub>  | Power               |           |

| 27       | EXT11/P011      | ExtData11/Port011               | In/Output      | 77       | V <sub>ss</sub> | Ground              | <u> </u>  |

| 28       | PD1             | ProgramData1                    | Input          | 78       | PÃO             | ProgramAddress0     | Cutput    |

| 29       | $V_{DD}$        | Power                           |                | 79       | EXT0/P00        | ExtData0/Port00     | In/Output |

| 30       | VAH             | AnalogHighRef.                  | Input          | 80       | PA1             | ProgramAddress1     | Cutput    |

| 31       | V <sub>ss</sub> | Ground                          |                | 81       | EXT1/P01        | ExtData1/Port01     | In/Output |

| 32       | P16/U10         | Port16/UserInput0               | In/Output      | 82       | PA2             | ProgramAddress2     | Cutput    |

| 33       | VALO            | AnalogLowRef.                   | Input          | 88       | EXT2/P02        | ExtData2/Port02     | In/Output |

| 34       | P17/Ul1         | Port17/UserInput1               | In/Output      | 84       | P10/INT2        | Port10/Interrupt2   | In/Output |

| 35       | FD2             | ProgramData2                    | Input          | 85       | PA3             | ProgramAddress3     | Cutput    |

| 36       | ANGND           | AnalogGround                    | Input          | 86       | Vss             | Ground              |           |

| 37       | AND             | A/DInput0                       | Input          | 87       |                 | Port11/ClockOutput  | In/Output |

| 38       | ANI             | A/DInput1                       | Input          | 88       | P12/SIN         | Port12/SerialInput  | In/Output |

| 39<br>39 | AN2             | A/DInput2                       |                | 89       | P20/INTO        | Port20/Interrupt0   | In/Output |

| 40       | ANB             | A/DInput3                       | Input<br>Input | 90       | PA4             | ProgramAddress4     | Output    |

|          |                 | -                               |                |          |                 |                     |           |

| 41       |                 | Ground<br>Dout 0.1 /Intormunt 1 | lo/O to t      | 91       | EXT12/P012      | ExtData12/Port012   | In/Output |

| 42       | P21/INT1        | Port21/Interrupt1               | In/Output      | 92<br>00 | PA5             | ProgramAddress5     | Output    |

| 43       | ANACC           | AnalogPower                     | Input          | 98<br>01 | EXT13/P013      | ExtData13/Port013   | In/Output |

| 44       | FD3             | ProgramData3                    | Input          | 94       | $V_{DD}$        | Power               | = .       |

| 45       | $V_{DD}$        | Power                           |                | 95       | EXT14/P014      | ExtData14/Port014   | In/Output |

| 46       | FD4             | ProgramData4                    | Input          | 96       | P46             | ProgramAddress6     | Cutput    |

| 47       | FD5             | ProgramData5                    | Input          | 97       | V <sub>ss</sub> | Ground              |           |

| 48       | RD/WR           | RWExternalBus                   | Output         | 98       | PĀZ             | ProgramAddress7     | Cutput    |

| 49       | PD6             | ProgramData6                    | Input          |          | EXT15/P015      | ExtData15/Port015   | In/Output |

| 50       | FD7             | ProgramData7                    | Input          | 100      | /PAZ            | Tri-stateProgramBus | Input     |

| <u> </u> |                 |                                 |                |          | ,,,, <b>,</b> , | in otasi rogia neus | " por     |

DS95DSP0101 Q4/95

#

**CLKO-CLKI** *Clock* (output/input). These pins act as the clock circuit input and output.

**EXT15-EXT0** *External Data Bus* (input/output). These pins act as the data bus for user-defined outside registers, such as an ADC or DAC. The pins are normally tri-stated, except when the outside registers are specified as destination registers in the instructions. All the control signals exist to allow a read or a write through this bus. If user I/O Port 0 is enabled, these signals function as user Programmable I/O.

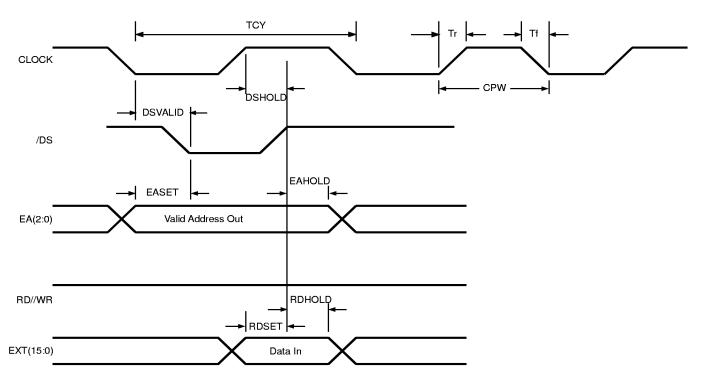

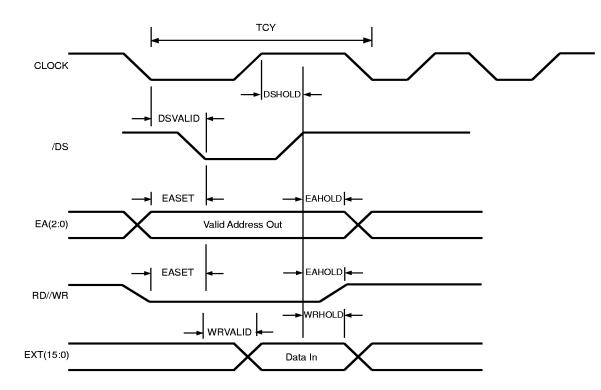

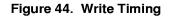

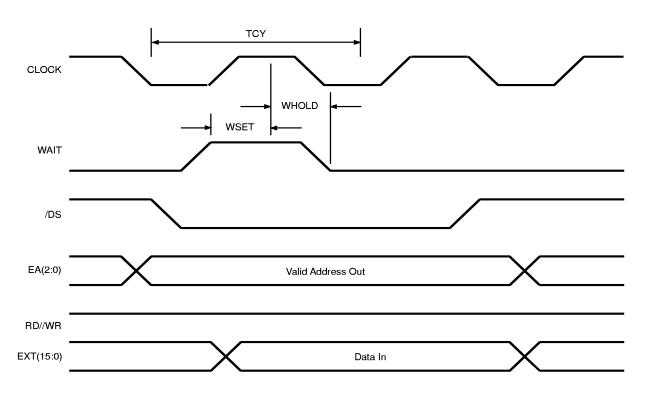

**RD**//**WR** *Read*/*Write Strobe* (output). This pin controls the data direction signal for the EXT-Bus. Data is available from the CPU on EXT15-EXT0 when this signal is Low. EXT-Bus is in input mode (high-impedance) when this signal is High.

**EA2-EA0** *External Address* (output). These pins control the user-defined register address output (latched). One of eight user-defined external registers is selected by the processor with these address pins for read or write operations. Since the addresses are part of the processor memory map, the processor is simply executing internal reads and writes. External Addresses are used internally by the processor if the ADC, bit I/O (Port 0- 2), or SPI are enabled. (See the banks allocation of the EXT registers in Tables 6 and 7.)

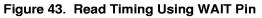

**/DS** *Data Strobe* (output). This pin control the data strobe signal for EXT-Bus. Data is read by the external peripheral on the rising edge of /DS. Data is also read by the processor on the rising edge of CK.

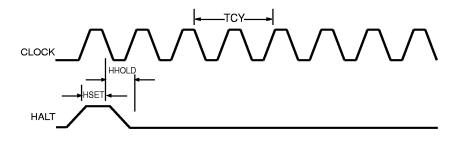

**HALT** *Halt State* (input). This pin controls Stop Execution. The CPU continuously executes NOPs and the program counter remains at the same value when this pin is held High. An interrupt request must be executed (enabled) to exit HALT mode. After the interrupt service routine, the program continues from the instruction after the HALT (active high).

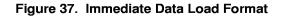

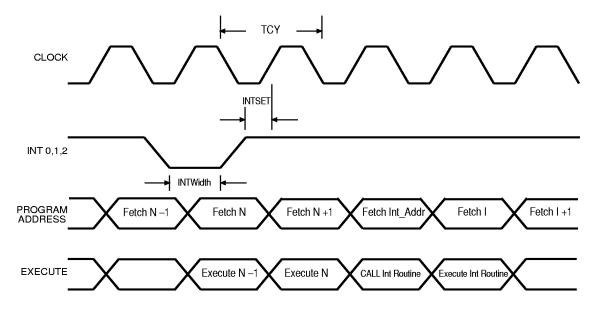

**/INTO-/INT2** Three Interrupts (input, active on rising edge). These pins control interrupt requests 0-2. Interrupts are generated on the rising edge of the input signal. Interrupt vectors for the interrupt service starting address are stored in the following program memory locations:

| Device     | /INT0 | /INT1 | /INT2 |

|------------|-------|-------|-------|

| Z89323/373 | 1FFFH | 1FFEH | 1FFDH |

| Z89393     | FFFFH | FFFEH | FFFDH |

Priority is: INT2 = lowest, INT0 = highest. (**Note**: INT2 pin is not bonded out on the 44-pin QFP or PLCC packages.)

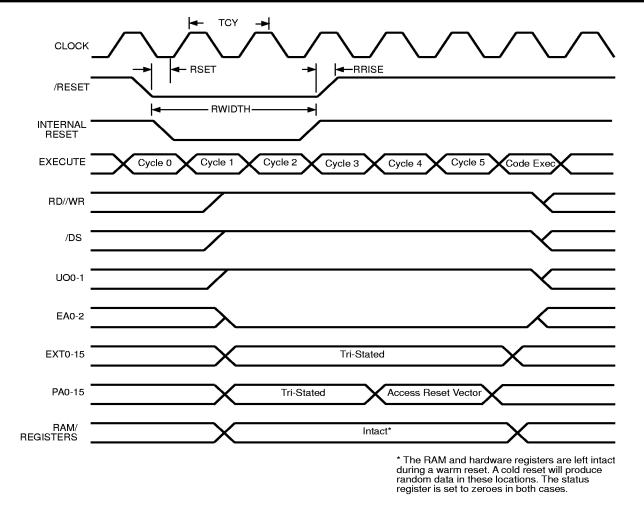

**(RES** *Reset* (input, active Low). This pin controls the asynchronous reset signal. The /RES signal must be kept Low for at least one clock cycle (clock output of the PLL block). The CPU pushes the contents of the Program Counter (PC) onto the stack and then fetches a new PC value from program memory address 0FFCH (or FFFCH for the Z89393) after the reset signal is released.

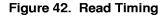

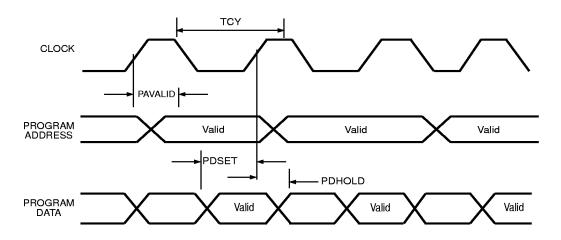

**WAIT** *WAIT State* (input). The wait signal is sampled at the rising edge of the clock with appropriate setup and hold times. The normal write cycle will continue when wait is inactive on a rising clock. A single wait-state can be generated internally by setting the appropriate bits in the wait state register (Bank 15/Ext 3) (active high).

**P00-P015** *Port 0* (input/output). These pins control Port 0 input and output when EXT I/F is not in use.

**P10-P17** *Port 1* (input/output). These pins are used for Port 1 programmable bit I/O when INT2, CLKOUT, SPI, or UI0-1 are not being used.

**P20-P27** *Port 2* (input/output). These pins control Port 2 input or output when UI2, UO0-2 or INT0-INT1 are not being used.

**P30-P37** *Port 3* Port3 (3:0) are four inputs and P3 (7:0) are four outputs.

**Ul1-Ul0** *Two Input Pins* (input). These general-purpose input pins are directly tested by the conditional branch instructions. These are asynchronous input signals that have no special clock synchronization requirements.

**UO1-UO0** *Two Output Pins* (output). These generalpurpose output pins reflect the value of two bits in the status register S5 and S6. These bits have no special significance and may be used to output data by writing to the status register. **Note:** The user output value is the opposite of the status register content.

SIN/SOUT. When enabled, these pins control SPI input and output.

**ANO-AN3.** These pins are used for Analog-to-Digital converter input.

**ANGND and ANVCC.** Analog to Digital ground and power supply.

#### DS95DSP0101 Q4/95

## PIN FUNCTIONS (Continued)

VAHI and VALO. Analog to Digital reference voltages.

**PAZ** *Tri-state Program Bus.* This pin enables the Program Address bus for emulation purposes.

**/EXTEN** *Ext Enable.* This pin enables Ext output continuously for emulation purposes.

**ROMEN** *ROM Enable.* This pin selects internal or external Program Memory.

### ADDRESS SPACE

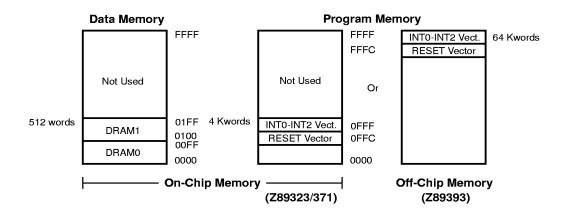

**Program Memory.** Programs of up to 8 Kwords can be masked into internal ROM (OTP for Z89373). Four locations are dedicated to the vector address for the three interrupts (IFFDH-IFFFH) and the starting address following a Reset (IFFCH). Internal ROM is mapped from 0000H to IFFFH, and the highest location for program is IFFBH.

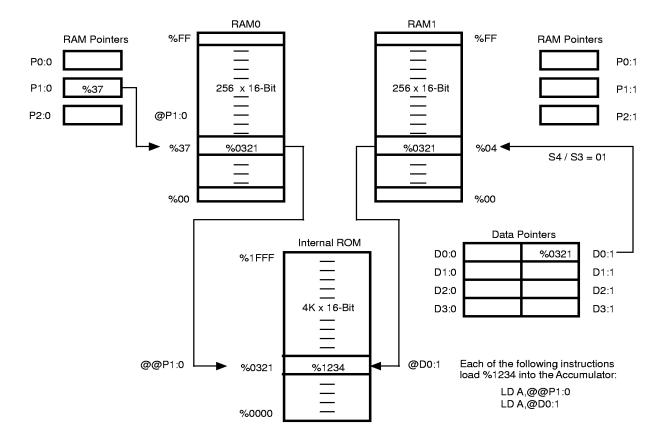

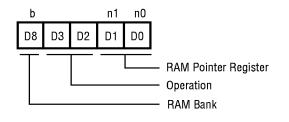

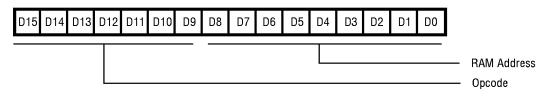

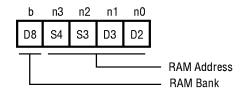

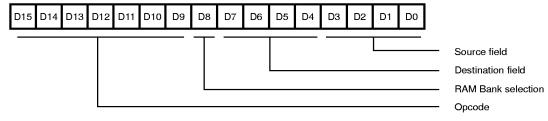

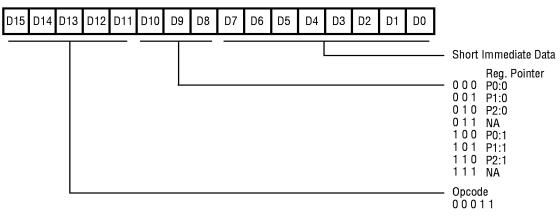

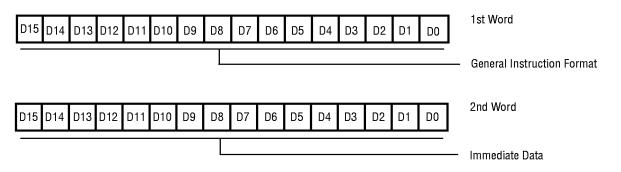

**Internal Data RAM.** The Z89323 has an internal 512 x 16bit word data RAM organized as two banks of 256 x 16-bit words each: RAM0 and RAM1. Each data RAM bank is addressed by three pointers: Pn:0 (n = 0-2) for RAM0 and Pn:1 (n = 0-2) for RAM1. The RAM addresses for RAM0 and RAM1 are arranged from 0-255 and 256-511, respectively. The address pointers, which may be written to, or read from, are 8-bit registers connected to the lower byte of the internal 16-bit D-Bus and are used to perform modulo addressing. Three addressing modes are available to access the Data RAM: register indirect, direct addressing, and short form direct. The contents of the RAM can be read to, or written from, in one machine cycle per word, without disturbing any internal registers or status other than the RAM address pointer used for each RAM. The contents of each RAM can be loaded simultaneously into the X and Y inputs of the multiplier.

**Registers.** The Z89323 has 19 internal registers and eight external registers and a secondary set of 15 peripheral control registers. Both external and internal registers are accessed in one machine cycle. The external registers are used to access the on-chip peripherals when they are enabled.

Figure 6. Memory Map

# ⊗ Silæ

## REGISTERS

The internal registers of the Z89323/373/393 are defined below:

| Register | Register Definition                  |

|----------|--------------------------------------|

| Р        | Output of Multiplier, 24-bit         |

| X        | X Multiplier Input, 16-bit           |

| Y        | Y Multiplier Input, 16-bit           |

| Α        | Accumulator, 24-bit                  |

| SR       | Status Register, 16-bit              |

| Pn:b     | Six Ram Address Pointers, 8-bit each |

| PC       | Program Counter, 16-bit              |

| EXT 0    |                                      |

| EXT 1    |                                      |

| EXT 2    |                                      |

| EXT 3    |                                      |

| EXT 4    |                                      |

| EXT 5    |                                      |

| EXT 6    |                                      |

| EXT7     |                                      |

See Table 6 and Table 7 for the different assignments of EXT7-EXT0 in the different banks.

| Register | Register Definition        |

|----------|----------------------------|

| EXTn     | External Registers, 16-bit |

| BUS      | D-Bus                      |

| Dn:b     | Eight Data Pointers*       |

Note:

\* These data pointers occupy the first four locations in RAM bank.

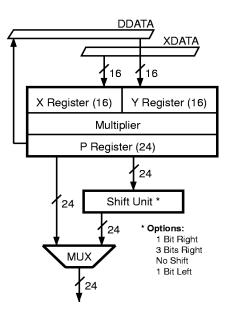

**P** holds the result of multiplications and is read-only.

**X** and **Y** are two 16-bit input registers for the multiplier. These registers can be utilized as temporary registers when the multiplier is not being used.

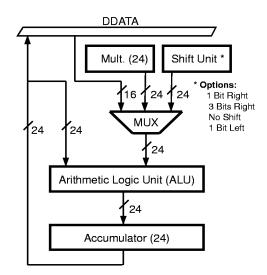

**A** is a 24-bit Accumulator. The output of the ALU is sent to this register. When 16-bit data is transferred into this register, it is placed into the 16 MSBs and the least significant eight bits are set to zero. Only the upper 16 bits are transferred to the destination register when the Accumulator is selected as a source register in transfer instructions.

**Pn:b** are the pointer registers for accessing data RAM, (n = 0,1,2 refer to the pointer number) (b = 0,1 refers to RAM Bank 0 or 1). They can be directly read from or written to, and can point to locations in data RAM or Program Memory.

**EXTn** are external registers (n = 0 to 7). There are eight 16bit registers provided here for mapping external devices into the address space of the processor. Note that the actual register RAM does not exist on the chip, but would exist as part of the internal or external device, such as an ADC.

**BUS** is a read-only register which, when accessed, returns the contents of the D-Bus. Bus is used for emulation only.

**Dn:b** refers to locations in RAM that can be used as a pointer to locations in program memory which is efficient for coefficient addressing. The programmer decides which location to choose from two bits in the status register and two bits in the operand. Thus, only the lower 16 possible locations in RAM can be specified. At any one time, there are eight usable pointers, four per bank, and the four pointers are in consecutive locations in RAM. For example, if S3/S4 = 01 in the status register, then D0:0/D1:0/D2:0/D3:0 refer to register locations 4/5/6/7 in RAM Bank 0. Note that when the data pointers are being written to, a number is actually being loaded to Data RAM, so they can be used as a limited method for writing to RAM.

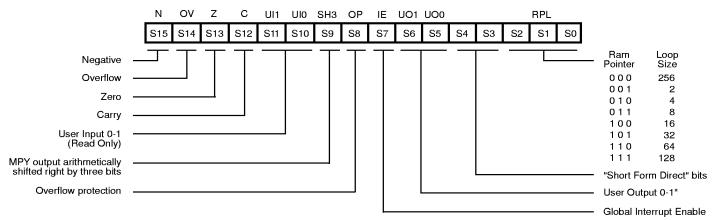

**SR** is the status register (Figure 8) which contains the ALU status and certain control bits (Table 5).

| Table 5. | Status | Register | Bit | Functions |

|----------|--------|----------|-----|-----------|

|----------|--------|----------|-----|-----------|

| Status Register Bit | Function                    |

|---------------------|-----------------------------|

| \$15 (N)            | ALU Negative                |

| S14 (OV)            | ALU Overflow                |

| S13 (Z)             | ALU Zero                    |

| S12 (L)             | Carry                       |

| S11 (UI1)           | User Input 1                |

| \$10 (UI0)          | User Input 0                |

| S9 (SH3)            | MPY Output Arithmetically   |

|                     | Shifted Right by three bits |

| S8 (OP)             | Overflow Protection         |

| S7 (IE)             | Interrupt Enable            |

| S6 (UO1)            | User Output 1               |

| S5 (UO0)            | User Output 0               |

| S4-S3               | "Short Form Direct" bits    |

| S2-S0 (RPL)         | RAM Pointer Loop Size       |

## **REGISTERS** (Continued)

### The Status Register

The status register can always be read in its entirety. S15-S10 are set/reset by hardware and can only be read by software. S9-S0 control hardware looping and can be written by software (Table 8).

| Table 8. RPL Description |    |    |           |  |

|--------------------------|----|----|-----------|--|

| S2                       | S1 | S0 | Loop Size |  |

| 0                        | 0  | 0  | 256       |  |

| 0                        | 0  | 1  | 2         |  |

| 0                        | 1  | 0  | 4         |  |

| 0                        | 1  | 1  | 8         |  |

| 1                        | 0  | 0  | 16        |  |

| 1                        | 0  | 1  | 32        |  |

| 1                        | 1  | 0  | 64        |  |

| 1                        | 1  | 1  | 128       |  |

S15-S12 are set/reset by the ALU after an operation. S11-S10 are set/reset by the user inputs. S6-S0 are control bits described in Table 5. S7 enables interrupts. If S8 is set, the hardware clamps at maximum positive or negative values instead of overflowing. If S9 is set and a multiple/shift option is used, then the shifter shifts the result three bits right. This feature allows the data to be scaled and prevents overflows.

**PC** is the Program Counter. When this register is assigned as a destination register, one NOP machine cycle is added automatically to adjust the pipeline timing.

\* The output value is the opposite of the status register content.

Figure 7. Status Register

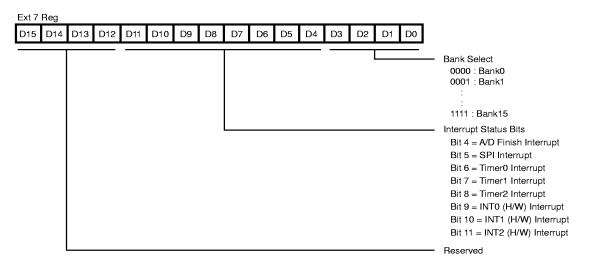

## **EXT Register Assignments**

The EXT registers support is extended in the Z893X3 family: In addition to up to seven external registers, there are 28 internal registers on the EXT bus. There are 16 different pages of EXT registers. The same EXT7 register exist in all the pages and control of the bank switching is done via EXT7 register.

Banks 0 to 5 support different combinations of external registers and internal data registers. The user should use the bank that has the internal data registers and the number of external registers to support his application and to use this bank as a working bank to minimize the number of bank switching. Bank 5 has all the A/D registers. Banks 13 to 15 are control registers bank. These control registers are usually used only in the initialization routines.

#### Table 6. EXT Register Assignments Banks 0-4

| EXT∖Bank | 0               | 1               | 2               | 3               | 4               |

|----------|-----------------|-----------------|-----------------|-----------------|-----------------|

| EXT0     | Ext0-user       | Ext0-user       | Ext0-user       | Ext0-user       | Ext0-user       |

| EXT1     | Ext1-user       | Ext1-user       | Ext1-user       | Ext1-user       | Ext1-user       |

| EXT2     | Ext2-user       | Ext2-user       | Ext2-user       | Ext2-user       | Ext2-user       |

| EXT3     | SPI data        | Ext3-user       | Ext3-user       | SPI data        | Ext3-user       |

| EXT4     | Port0           | Port0           | Ext4-user       | Ext4-user       | Ext4-user       |

| EXT5     | Port1/Port2     | Port1/Port2     | Port3           | Ext5-user       | Ext5-user       |

| EXT6     | A/D_ch0         | A/D_ch1         | A/D_ch2         | A/D_ch3         | Ext6-user       |

| EXT7     | Bank/Int_status | Bank/Int_status | Bank/Int_status | Bank/Int_status | Bank/Int_status |

#### Table 7. EXT Register Assignments Banks 6–15

| EXT\Bank | 5               | 6-12            | 13               | 14               | 15              |

|----------|-----------------|-----------------|------------------|------------------|-----------------|

| EXT0     | A/D_ch1         |                 | A/D control      | Timer2 load      | P0 control      |

| EXT1     | A/D_ch2         |                 | Timer0 control   | Timer1 control   | P1 control      |

| EXT2     | A/D_ch3         |                 | Timer0 load      | Timer1 load      | P2 control      |

| EXT3     | SPI data        |                 | Timer0           | Timer1           | Wait State      |

| EXT4     | Port0           |                 | Timer0 pr. load  | Timer1 pr. load  | SPI control     |

| EXT5     | Port1/Port2     |                 | Timer0 prescaler | Timer1 prescaler | PLL control     |

| EXT6     | A/D_ch0         | A/D_ch0         | A/D_ch0          | A/D_ch0          | Int. Allocation |

| EXT7     | Bank/Int_status | Bank/Int_status | Bank/Int_status  | Bank/Int_status  | Bank/Int_status |

## EXT Register Assignments (Continued)

#### **Interrupt Status Bits**

When read, these bits provide interrupt information to identify the source for INT2, or when the DSP works in Pending Interrupt mode, to warn the DSP of pending interrupts. These bits also clear the interrupt status bits. Writing 1 will clear these bits.

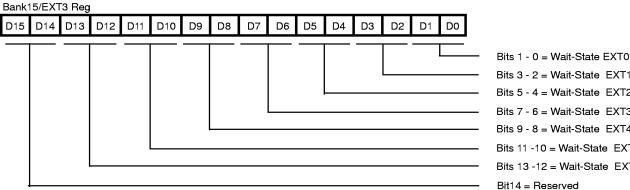

#### Wait-State Register

The Wait-State Control Register enables insertion of Wait States when the DSP needs to access slow, inexpensive peripherals. This software-controlled register enables insertion of one Wait State when accessing EXT bus. (One Wait State gives 100 nsec access time instead of 50 nsec access time with a 20 MHz oscillator.) When more than one Wait State is needed, an input pin (WAIT) coupled with external logic can support more than one Wait State. The Wait-State Control Register enables mapping specific EXT register (from EXT0 to EXT6) and specific operation (read or write) to include insertion of one Wait State. EXT7 is always internal register, therefore no Wait State is needed for EXT7.

#### Note:

When the programmer switches banks it is important to change the Wait State mapping of the EXT registers to match the desired Wait State mapping of the new bank.

Bits 3 - 2 = Wait-State EXT1

- Bits 5 4 = Wait-State EXT2

- Bits 7 6 = Wait-State EXT3

- Bits 9 8 = Wait-State EXT4

- Bits 11 -10 = Wait-State EXT5

- Bits 13 -12 = Wait-State EXT6

Bit14 = Reserved Bit 15 = Test Mode

0 Normal Operation (default) 1 Test Mode: Bits 6-5 of the Status Register drives, P23 and P22, respectively (VO0 and VO1).

Figure 8a. Bank 15/EXT3 Register

## **FUNCTIONAL DESCRIPTION**

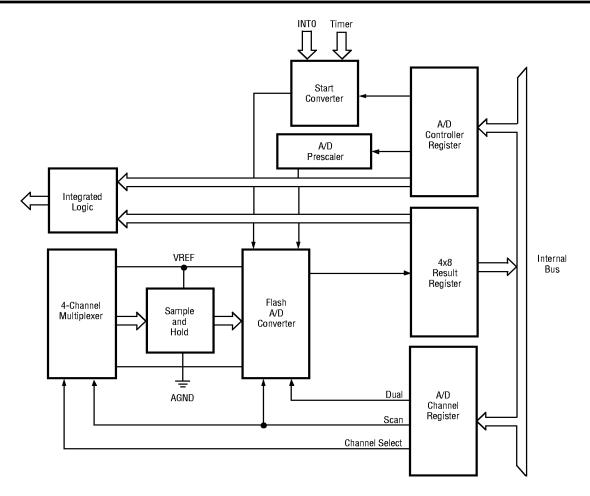

## Analog to Digital Converter (ADC)

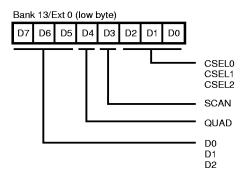

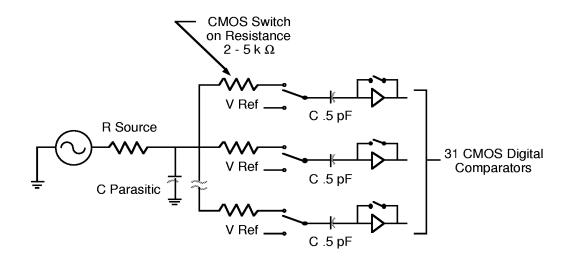

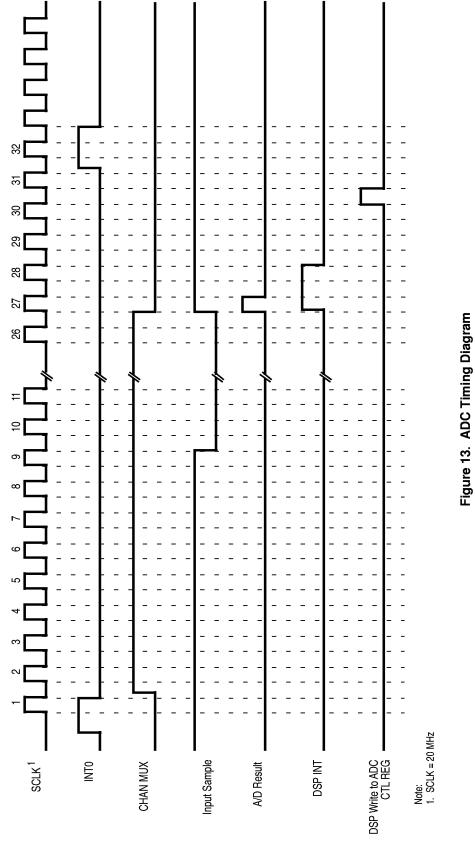

The ADC is an 8-bit half flash converter that uses two reference resistor ladders for its upper 4 bits (Most Significant Bits) and lower 4 bits (Least Significant Bits) conversion. Two reference voltage pins, VA (High) and VA (Low), are provided for external reference voltage supplies. During the sampling period from one of the four channel inputs, the converter is also being auto-zeroed before starting the conversion. The conversion time is dependent on the external clock frequency and the selection of the prescaler value for the internal ADC clock source. The minimum conversion time is 2.0  $\mu$ s. (See Figure 9, ADC Architecture.)

The ADC control register is Bank 13/Ext 0. A conversion can be initiated in one of four ways: by writing to the A/D control register, INT1 input pin, Timer 2 or Timer 0 equal 0. These four are programmable selectable. There are four modes of operation that can be selected: one channel converted four times with the results written to each Result register, one channel continuously converted and one Result channel updated for each conversion, four channels converted once each and the four results written to the Result registers, and four channels repeatedly converted and the Result registers kept updated. The channel to be converted is programmable and if one of the four-channel modes is selected then the programmed channel will be the first channel converted and the other three will be in sequence following with wraparound from Channel 3 to Channel 0.

The start commands are implemented in such a way as to begin a conversion at any time, if a conversion is in progress and a new start command is received, then the conversion in progress will be aborted and a new conversion will be initiated. This allows the programmed values to be changed without affecting a conversion-in-progress. The new values will take effect only after a new start command is received.

The clock prescaler can be programmed to derive a minimum 2  $\mu$ s conversion time for clock inputs from 4 MHz to 20 MHz. For example, with a 20 MHz crystal clock the prescaler should be programmed for divide by 40, which then gives a 2  $\mu$ s conversion rate.

The ADC can generate an Interrupt after either the first or fourth conversion is complete depending on the programmable selection.

The ADC can be disabled (for low power) or enabled by a Control Register bit.

Though the ADC will function for a smaller input voltage and voltage reference, the noise and offsets remain constant during the specified electrical range. The errors of the converter will increase and the conversion time may also take slightly longer due to smaller input signals.

Figure 9. ADC Architecture

## FUNCTIONAL DESCRIPTION (Continued)

Figure 10. ADCTL Register (Low Byte)

#### Prescaler Values (bits 7, 6, 5)

| D2 | D1 | D0 | Prescaler<br>(Crystal divided by) |

|----|----|----|-----------------------------------|

| 0  | 0  | 0  | 8                                 |

| 0  | 0  | 1  | 16                                |

| 0  | 1  | 0  | 24                                |

| 0  | 1  | 1  | 32                                |

| 1  | 0  | 0  | 40                                |

| 1  | 0  | 1  | 48                                |

| 1  | 1  | 0  | 56                                |

| 1  | 1  | 1  | 64                                |

#### Note:

The ADC is currently being characterized. Converter errors are estimated to increase to 2 LSBs (Integral non-linearity), 1 LSB (Differential non-linearity) and 10 mV (Zero error at  $25^{\circ}$ C) if the voltage swing on the reference ladder is decreased to -3V.

#### Modes (bits 4, 3)

| QUAD | SCAN |                                             |

|------|------|---------------------------------------------|

| 0    | 0    | Convert selected channel 4 times then stop. |

| 0    | 1    | Convert selected channel then stop.         |

| 1    | 0    | Convert 4 channels then stop.               |

| 1    | 1    | Convert 4 channels continuously.            |

#### Channel Select (bits 2, 1, 0)

|       | ( , , | ,     |         |

|-------|-------|-------|---------|

| CSEL2 | CSEL1 | CSEL0 | Channel |

| 0     | 0     | 0     | 0       |

| 0     | 0     | 1     | 1       |

| 0     | 1     | 0     | 2       |

| 0     | 1     | 1     | 3       |

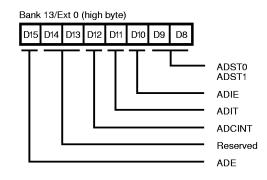

### Figure 11. ADCTL Register (High Byte)

**ADE** (bit 15). A 0 disables any A/D conversions or access–ing any ADC registers except writing to ADE bit. A 1 Enables all ADC accesses.

**Reserved** (bits 14, 13). Reserved for future use.

**ADCINT** (bit 12). This is the ADC Interrupt bit and is Read Only. The ADCINT will be reset any time this register is written.

**ADIT** (bit 11). This bit selects when to set the ADC Interrupt if ADIE=1. A value of 0 sets the Interrupt after the first A/D conversion is complete. A value of 1 sets the Interrupt after the fourth A/D conversion is complete.

**ADIE** (bit 10). This is the ADC Interrupt Enable. A value of 0 disables setting the ADC Interrupt. A value of 1 enables setting the ADC Interrupt.

| START | (bits § | 9, 8) |  |

|-------|---------|-------|--|

|       |         |       |  |

| ADST1 | ADST0 | Mode                                                |

|-------|-------|-----------------------------------------------------|

| 0     | 0     | Conversion starts when<br>this register is written. |

| 0     | 1     | Conversion starts on a rising edge INT1 input pin.  |

| 1     | 0     | Conversion starts when<br>Timer 2 times out.        |

| 1     | 1     | Conversion starts when<br>Timer 0 times out.        |

There are four ADC result registers. For their location in the different banks, see EXT Register Assignments.

Figure 12 shows the input circuit of the ADC. When conversion starts, the analog input voltage from one of the eight channel inputs is connected to the MSB and LSB flash converter inputs as shown in the Input Impedance CKT diagram. This effectively shunts 31 parallel internal resistance of the analog switches and simultaneously charges 31 parallel 0.5 pF capacitors, which is equivalent to seeing a 400 Ohms input impedance in parallel with a 16 pF capacitor. Other input stray capacitance adds about 10 pF to the input load. For input source, resistances up to 2 kOhms can be used under normal operating conditions without any degradation of the input settling time. For larger input source resistance longer conversion cycle time may be required to compensate the input settling time factor.

Figure 12. Input Impedance of ADC

FUNCTIONAL DESCRIPTION (Continued)

22

## TIMER/COUNTERS

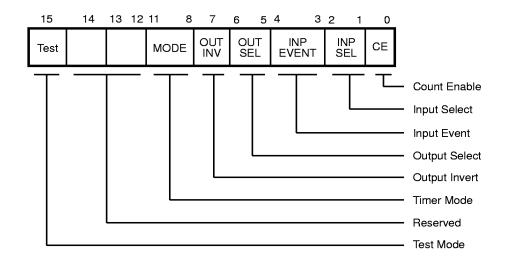

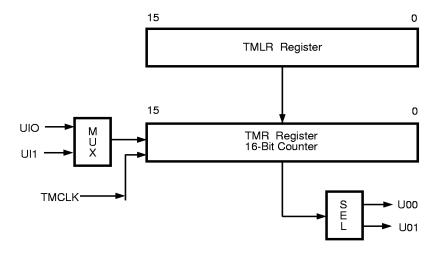

The Z89323/373/393 has two 16-bit Timer/Counters that can be independently configured to operate in various modes. Each is implemented as a 16-bit Load Register (TMLR) and a 16-bit down counter (TMR). Timer/Counter inputs can be selected from among UI0 or UI1 pins and outputs from among UO0 or UO1 pins. The Timer/Counter clock is a scaled version of system clock. Each counter has an 8-bit clock prescaler with divide count controlled by the 16-bit Prescaler Load Register (TPLR). The clock rates of the two timer/counters are independent of each other. External input events occur optionally on the rising edge, the falling edge, or both rising and falling edges of the input. Output actions on external pins can be programmed to occur with either polarity. The Timer/Counter operational modes are selected through the 16-bit Control Register (TCTL). This register defines the operational modes of its companion Timer (Figure 14).

Each Timer contains a set of five 16-bit Registers. The Ext Register Assignment specifies the location of each Timer Registers. All accesses to Timer Registers occur with zero Wait States.

Figure 14. TCTL Register

## TIMER/COUNTERS (Continued)

### Timer Modes

The Timer modes can be categorized as input modes and output modes. In input modes, the Timer/Counter is used for input signals only. In output modes, a selected output pin is driven. If a Timer/Counter is enabled (CE=1) and an output pin, UO0 or UO1, is selected to be driven, the DSP Processor's Status Register bits 5 or 6 does not affect the state of that pin.

### Output Modes

**MODE 0.** The Timer/Counter is configured to generate a continuous square wave of 50% duty cycle. Writing a new value to the TMLR Register takes effect at the end of current cycle unless TMR is written.

**MODE 1.** The Timer/Counter is configured to generate a single pulse of programmable duration. The asserted state may be either logic high or logic low. Retriggering the one-shot before the end of the pulse causes it to continue for the new duration.

**MODE 2.** The Timer/Counter is configured to generate a pulse-width modulated repeating waveform. The duty cycle ranges from 0-100% (0/256 to 255/256) of a cycle in steps of 1/256 of a cycle. The asserted state of the waveform may be either logic high or logic low. Writing a new pulse-width value to the TMLR Register takes effect at the end of current cycle unless TMR is written.

**MODE 3.** The Timer/Counter is configured to generate a pulse-width modulated repeating waveform. The duty cycle ranges from 0-100% (0/65,536 to 65,535/65,536) of a cycle in steps of 1/65,536 of a cycle. The asserted state of the waveform may be either logic high or logic low. Writing a new pulse-width value to the TMLR Register takes effect at the end of current cycle unless TMR is written.

**MODE 4.** The Timer/Counter is configured to generate a series of pulses ranging from 0 to 65,535. The pulses are actually the Timer Clock (TMCLK), which is gated to the output until the counter under flows.

**MODE 5.** The Timer/Counter is configured to generate an output pulse that is asserted under program control, and de-asserted when a programmable number of input edges (up to 65,535) have been counted on an input pin (UI0 or UI1). Assertion may be either logic high or logic low.

**MODE 6.** The Timer/Counter is configured to generate a Hardware Reset on time-out unless retriggered by software.

**MODE 7.** The Timer/Counter is configured to generate a Hardware Reset on time-out unless retriggered by an event on one of the input pins UI0 or UI1.

### **Input Modes**

The input modes use one of the input pins UI0 or UI1. The signals on these pins are synchronized with the internal Timer Clock, TMCLK, before being applied to the Timer. The input signal frequency must be no higher than 1/4th of TMCLK frequency.

**MODE 8.** The Timer/Counter is configured to measure the time for which its input is asserted.

**MODE 9.** The Timer/Counter is configured to measure the period from one rising (falling) edge to the next rising (falling) edge on the input.

**MODE 10.** The Timer/Counter is configured to count the number of input edges (up to 65,535). Input edges may be selected as rising or falling or both.

**MODE 11.** The Timer/Counter is configured to count the number of input edges (up to 65,535) in a time window set by the second timer. Edges are counted until the second timer under flows. Input edges may be selected as rising or falling or both.

Bank 13/EXT1 (Timer0) or Bank 14/EXT1 (Timer1) Timer Control Register (TCTL) 14 13 12 11 10 9 8 7 5 2 0 15 6 4 з 1 Timer/Counter 0 Timer/Counter disabled (default) 1 Timer/Counter enabled Input Select 00 Inputs have no effect 01 Reserved 10 UI0 Pin 11 UI1 Pin Input Event 00 Low Level or Falling Edge 01 High Level or Rising Edge 10 Both Rising and Falling Edges 11 Reserved Output Select 00 Outputs Unaffected 01 Reserved 10 Drive UO0 Pin 11 Drive UO1 Pin Output Invert 0 Output asserted High on Timeout 1 Output asserted Low on Timeout Timer Mode Timer Output Modes 0000 Square Wave Mode 0 0001 One-Shot Mode 1 0010 PWM short (8-bit) Mode 2 0011 PWM long (16-bit) Mode 3 0100 Pulse Count Output Mode 4 Mode 5 0101 Triggered Count 0110 S/W Watch-Dog Mode Mode 6 0111 H/W Watch-Dog Mode Mode 7 **Timer Input Modes** 1000 Gated Count Mode 8 1001 Period Mode 9 1010 Pulse Count Mode 10 1011 Gated Pulse Count Mode 11 Reserved Test Mode\* 0 Normal Operation 1 Factory Test Mode \*Note: The user should always

Figure 15. Register Bit Fields

program this bit to be 0.

## TIMER/COUNTERS (Continued)

### Timer Load Register (TMLR)

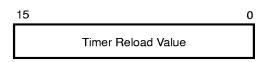

This 16-bit Register holds a value that is reloaded into timer upon timer under flow.

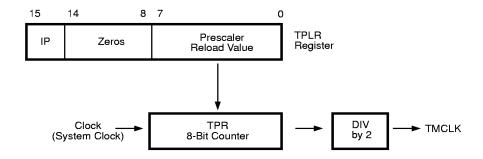

#### **Timer Prescaler Load Register (TPLR)**

The 16-bit TPLR Register holds the prescaler reload value in its lower 8 bits. Bit 15 is the Timer's Interrupt Pending bit. When set, it signifies an interrupt event in its companion timer. The IP bit can only be set by the Timer. It can be cleared only by software when it writes a value to this register with a "1" in bit position 15; a "0" in bit position 15 will have no effect on the state of IP bit. Bits [14:8] must always be written with 0s for future compatibility.

| 15   | 14    | 8 7                       | 0 |

|------|-------|---------------------------|---|

| Test | Zeros | Prescaler<br>Reload Value |   |

### Timer Register (TMR)

TMR is a 16-bit down counter that holds the current Timer/ Counter value. It can be read as any ordinary register. However, writing to TMR is different than writing to an ordinary register. A write to TMR Register causes the contents of TMLR Register to be written into it, causing the Timer to be retriggered. Any data on DSP's Memory Data (MD) Bus is ignored during a write to TMR.

#### **Timer Prescale Register (TPR)**

TPR is an 8-bit down counter that holds the current Prescaler count value. It can be read as any ordinary register. However, writing to TPR is different than writing to an ordinary register. A write to TPR Register causes the lower 8-bit contents of TPLR Register to be written into it, causing the Prescaler to be retriggered. Any data on DSP's Memory Data (MD) Bus is ignored during a write to TPR.

| 7                    | 0 |

|----------------------|---|

| TPR<br>8-Bit Counter |   |

## **Prescaler Operation**

The Timer/Counter Clock (TMCLK) is generated by the output of the prescaler. The Prescaler is an 8-bit down counter, TPR, followed by a divide-by-two flip-flop that generates a 50 percent duty cycle output clock TMCLK. The Prescaler's input clock is the system clock, CLKIN, divided by two. Thus, the maximum prescaler output frequency is 1/4 of the system clock frequency.

Once the prescaler counter is loaded, it decrements at its clocked frequency and generates an output to the divideby-two flip-flop. When the count reaches 0, the counter is reloaded from the lower 8 bits of TPLR Register. The 8-bit prescaler counter is loaded with value in TPLR Register field [7:0] in one of three ways:

- 1. When 8-bit prescaler counter, TPR, decrements to zero.

- 2. By writing to TPR Register.

- 3. When companion Timer/Counter TMR is reloaded upon under flow from its TMLR Register, or retriggered by writing directly to TMR Register.

Figure 16. Prescaler Block Diagram

Figure 17. Counter/Timer Block Diagram

## TIMER/COUNTERS (Continued)

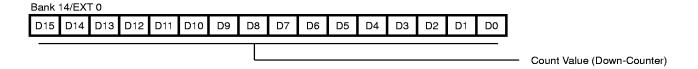

### 16-Bit General-Purpose Timer/Counter T2

The 16-bit timer/counter is available for general-purpose use. When the counter counts down to the zero state, the timer 2 load register loads into timer 2, and if timer 2 interrupt is enabled, an interrupt is received. The counting operation of the counter can be disabled. The timer/ counter clock source can be selected to be system clock/ 2 or UI2. The counter is defaulted to the Enable state. If the system designer does not choose to use the timer, the counter can be disabled.

Figure 18. Timer/Counter 2 Load Register

### I/O Ports

I/O pin allocation for ports in the different package types is designed to provide increased flexibility and support for various modes of operation. The 44-pin package features the special signals, as well as all packages supporting the EXT 16-bit bus. In cases where the application does not require an external EXT bus, these I/O pins can be allocated to 16-bit general-purpose I/O port (P0), the special signals port (P1) or additional port (P3). The 80-pin PQFP package supports up to 40 I/O pins.

| Pin Count<br>Package | 44-Pin<br>PLCC/PQFP | 68-Pin<br>PLCC | 80-Pin<br>PQFP | 100-Pin<br>PQFP⁺ |

|----------------------|---------------------|----------------|----------------|------------------|

| P0[15:8]             | EXT,P0,P1*          | EXT,P0         | EXT,P0         | EXT,P0           |

| P0[7:0]              | EXT,P0              | EXT,P0         | EXT,P0         | EXT,P0           |

| P1[7:0]              |                     | P1*            | P1*            | P1*              |

| P2[7:0]              | P2[4:0]*            | P2*            | P2*            | P2*              |

| P3[7:0]              |                     |                | P3             |                  |

Table 9. Various Package I/O Port Allocation

Note:

\* Ports with special signals: Interrupts inputs, Serial Peripheral Interface

(SPI), CLKOUT and Timers inputs and outputs.

† (ICE chip)

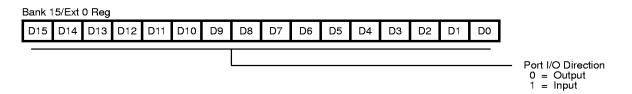

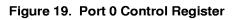

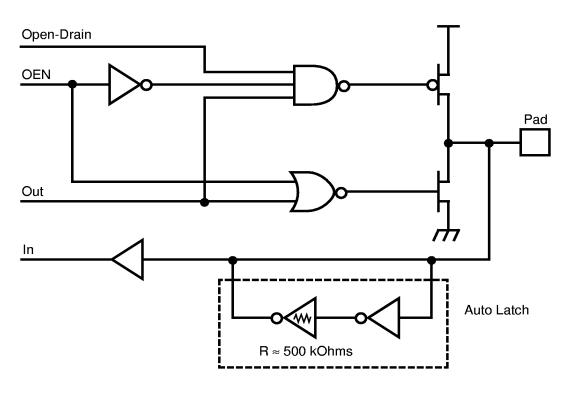

## 16-bit Programmable I/O (Port 0)

When the appropriate bit is set in the Port 1 control register, Port 0 acts as a 16-bit programmable, bidirectional, CMOScompatible port. Each of the 16 lines can be independently programmed as an input or an output, or globally as an open-drain output. When enabled, Bank 0/Ext 4 acts as the data I/O register. Bank 15/Ext 0 serves as the Port 0 direction register while Bank 15/Ext 1, has specified bits to enable Port 0 and determine whether Port 0 is globally configured as open-drain outputs.

Figure 20. Port 0, 1 and 2 Configuration

## 8-Bit Programmable I/O (Port 1)

When the appropriate bit is set in the Port 1 control register, Port 1 acts as an 8-bit programmable, bi-directional, CMOS-compatible port. Each of the eight lines can be independently programmed as an input or an output or globally as an open-drain output. When enabled, Bank0/EXT5 (Least Significant Bit) acts as the data I/O register. Bank15/EXT1 serves as the Port1 direction control register. Port 1 can also be programmed to provide special I/O functions.

| Table 10. Port 1 Bit Function Selection |

|-----------------------------------------|

|-----------------------------------------|

| Port.Bit | IF (Condition Explanation)                               | Then   | Else |

|----------|----------------------------------------------------------|--------|------|

| P1.0     | Bank15/Ext1(3)=1 (Enable External Interrupt Source INT2) | INT2   | P10  |

| P1.1     | Bank15/Ext1(5)=1 (CLKOUT Enable)                         | CLKOUT | P11  |

| P1.2     | Bank15/Ext4(0)=1 (SPI Enable)                            | SIN    | P12  |

| P1.3     | Bank15/Ext4(0)=1 (SPI Enable)                            | SOUT   | P13  |

| P1.4     | Bank15/Ext4(0)=1 (SPI Enable)                            | SS     | P14  |

| P1.5     | Bank15/Ext4(0)=1 (SPI Enable)                            | SK     | P15  |

| P1.6     | Bank13/Ext1(2-1)=10 or Bank14/Ext1(2-1)=10 (UI0 Enable)  | UI0    | P16  |

| P1.7     | Bank13/Ext1(2-1)=11 or Bank14/Ext1(2-1)=11 (UI0 Enable)  | UI1    | P17  |

Figure 21. Bank15/EXT1 Register

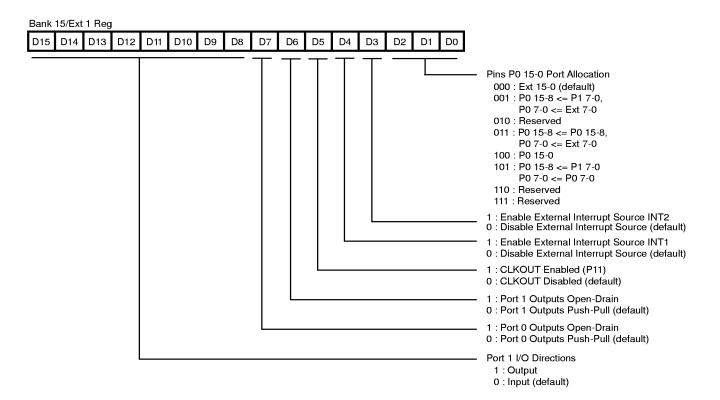

## 8-Bit Programmable I/O (Port 2)

Port 2 is an 8-bit programmable, bidirectional, CMOScompatible port. Each of the eight lines can be independently programmed as an input or an output or globally as an open-drain output. Port 2 can also be programmed to provide special I/O functions. When Port 2 acts as programmable I/O, Bank0/EXT5 (MSB) acts as the data I/O register. Bank15/EXT2 serves as Port 2 control register.

| Table 11. Port 2 Bit Function Selection | Table 11. | Port 2 Bit | Function | Selection |

|-----------------------------------------|-----------|------------|----------|-----------|

|-----------------------------------------|-----------|------------|----------|-----------|

| Port.Bit | IF (Condition Explanation)                               | Then | Else |

|----------|----------------------------------------------------------|------|------|

| P2.0     | Bank15/Ext2(9)=1 (Enable External Interrupt Source INT0) | INT0 | P20  |

| P2.1     | Bank15/Ext1(4)=1 (Enable External Interrupt Source INT1) | INT1 | P21  |

| P2.2     | Bank13/Ext1(6-5)=10 or Bank14/Ext1(6-5)=10 (UO0 Enable)  | UO0  | P22  |

| P2.3     | Bank13/Ext1(6-5)=11 or Bank14/Ext1(6-5)=11 (UO0 Enable)  | UO1  | P23  |

| P2.4     | Bank15/Ext2(14)=1 (UO2 Enable)                           | UO2  | P24  |

| P2.5     | Bank15/Ext2(13)=1 (Timer2 Clock is UI2)                  | UI2  | P25  |

| P2.6     |                                                          | P26  | P26  |

| P2.7     |                                                          | P27  | P27  |

### 8-Bit Programmable I/O (Port 3)

Port 3 is an additional I/O port featured only in the 80-pin PQFP package. P3[3:0] are inputs and P3[7:4] are outputs. The purpose of this additional port is to serve applications that need more than 32 I/O pins. Port 3 enables the user to support up to 40 I/O pins. Port 3 is not

supported in the 100-pin ICE chip PQFP package, therefore this port is not supported in the Z893x3 emulator, and use of this port is not recommended in cases when the other I/O ports can support the I/O requirements.

DS95DSP0101 Q4/95

## **Serial Peripheral Interface**

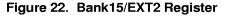

**Serial Peripheral Interface** (SPI). The Z893X3 incorporates a serial peripheral interface for communication with other microcontrollers and peripherals. The SPI includes features such as Master/Slave selection. The SPI consists of two registers; SPI Control Register (SCON), SPI Receive/Buffer Register (RxBUF), and SPI Shift Register (Figure 23). **Note:** The SPI shift register and Receive/Buffer register are one in the same and are shown in Figure 41. SCON is located in bank 15/Ext4 (LSB). This register is a read/write register that controls; Master/Slave selection, SS polarity, clock source and phase selection, and error flag. Bit 0 enables/ disables the SPI with the default being SPI disabled. A 1 in this location enables the SPI, and a 0 disables the SPI.

Bits 1 and 2 of the SCON register in Master Mode selects the clock rate. The user may choose whether internal clock is divide by 2, 4, 8, or 16. In Slave Mode, Bit 1 of this register flags the user if an overrun of the RxBUF Register has occurred.

The RxCharOverrun flag can only be reset by writing a 0 to this bit. In slave mode, bit 2 of the Control Register can disable the data-out I/O function. If a 1 is written to this bit, the data-out pin is tri-stated. If a 0 is written to this bit, the SPI will shift out one bit for each bit received. Bit 3 of the SCON Register is the SS polarity bit. A 0 selects active Low (default) polarity on SS, and a 1 selects active High. Bit 4 signals that a receive character is available in the RxBUF Register. If the associated interrupt enable bit is enabled, an interrupt is generated. Bit 5 controls the clock phase of the SPI. A 1 in Bit 5 allows for receiving data on the clock's falling edge and transmitting data on the clock's rising edge. A 0 allows receiving data on the clock's rising edge and transmitting on the clock's falling edge.

The SPI clock source is defined in bit 6 for Master mode. A 1 uses Timer0 output for the SPI clock, and a 0 uses a division of the internal system clock for clocking the SPI. Bit 7 determines whether the SPI is used as a Master or a Slave. A 1 puts the SPI into Master mode and a 0 puts the SPI into Slave mode.

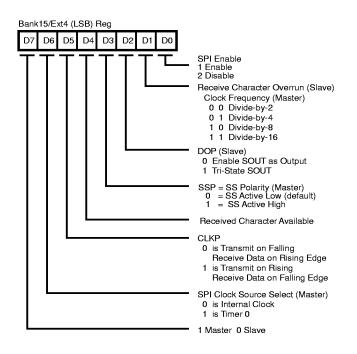

**SPI Operation.** The SPI can be used in one of two modes; either as system slave, or a system master. In the slave mode, data transfer starts when the slave select (SLAVESEL) pin goes Low. Data is transferred into the slave's SPI Shift Register, through the SIN pin, which has the same address as the RxBUF Register. After a byte of data has been received by the SPI Shift Register a Receive Character Available SPI interrupt and flag is generated. The next byte of data may be received at this time, but the RxBUF Register must be cleared, or a Receive Character Overrun (RxCharOverrun) flag is set in the SCON Register and the data in the RxBUF Register is overwritten.

Figure 23. SPI Control Register (SCON)

| Bank | (0/E) | kt 3 (L | .SB) | Reg |    |    |    |

|------|-------|---------|------|-----|----|----|----|

| D7   | D6    | D5      | D4   | D3  | D2 | D1 | D0 |

Figure 24. SPI TXRXDATA Register

When the communication between the master and slave is complete, the SS goes High. Unless disconnected, for every bit that is transferred into the slave through the SIN pin, a bit is transferred out through the SOUT pin on the opposite clock edge. During slave operation, the SPI clock pin (SK) is an input (Figure 25). In master mode, the DSP must first activate a SS through one of it's I/O ports. Next, data is transferred through the master's SOUT pin one bit per master clock cycle. Loading data into the shift register initiates the transfer. In master mode, the master's clock drives the slave's clock. At the conclusion of a transfer, a Receive Character Available SPI interrupt and flag is generated. Before data is transferred through the SOUT pin, the SPI Enable bit in the SCON Register must be enabled. The MSB bit 7 is shifted out first.

**SPI Clock.** The SPI clock can be driven from three sources; with T0, a division of the internal system clock, or an

external master when in slave mode. Bit D6 of the SCON Register controls what source drives the SPI clock. Divided by 2, 4, 8, or 16 can be chosen as the scaler with bits D2, D1 in master mode.

**Receive Character Available and Overrun.** When a complete data stream is received an interrupt is generated and the RxCharAvail bit in the SCON Register is set. The SPI interrupt can be enabled or disabled (default) in the Interrupt Allocation Register (Bank 15/Ext 6). The RxCharAvail bit is available for interrupt polling purposes and is reset when the RxBUF Register is read. RxCharAvail is generated in both master and slave modes. While in slave mode, if the RxBUF is not read before the next data stream is received and loaded into the RxBUF Register, Receive Character Overrun (RxCharOverrun) occurs. Since there is no need for clock control in slave mode, bit D1 in the SPI Control Register is used to log any RxCharOverrun.

Figure 25. SPI Timing

# ⊗ Silæ

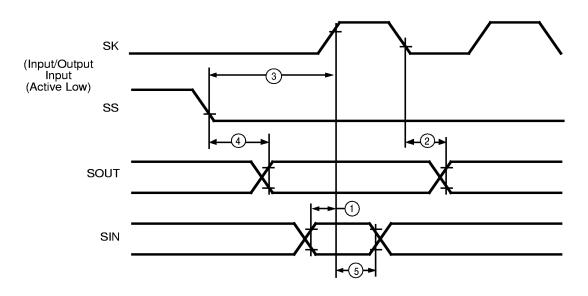

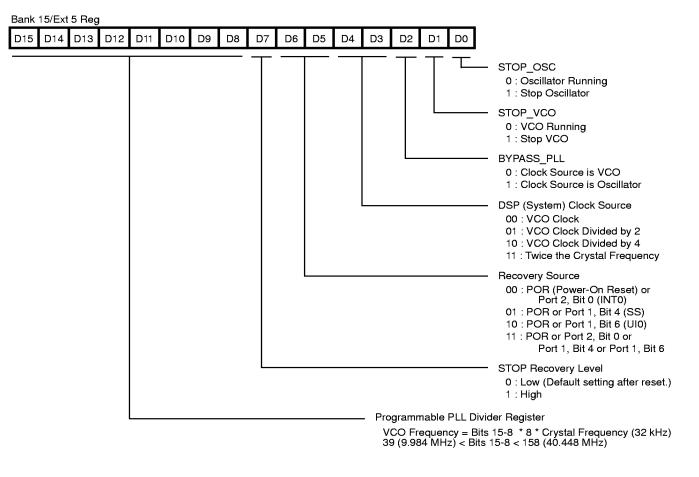

## **CLOCK Circuits**

The clock generator includes Phase-Locked Loop (PLL) circuit to enable use of low frequency crystal. The benefits of using low frequency crystal are low system cost, low power consumption and low EMI. The PLL circuit can be bypass (s/w controlled).

The clock generated by the PLL circuit (VCO clock) is programmable and controlled by the PLL Divider register.

DSP (System) clock source is programmable and can be one of the 4 options: VCO clock, VCO clock divided by 2, VCO clock divided by 4 or twice the crystal frequency.

Whenever the PLL circuit is switched from Stop VCO to Enable VCO, a software delay of 10 msec must be used before switching the system clock from the oscillator to the PLL, in order to give the PLL time to be stable.

|          |          | Table 12. CLO | DCK Modes                                                                                                                                        |

|----------|----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| STOP_OSC | STOP_VCO | BYPASS_PLL    | Mode                                                                                                                                             |

| 0        | 0        | 0             | <ol> <li>Normal - High frequency clock</li> <li>32 Khz - VCO running (fast switching time)**</li> <li>STOP CLOCK - Oscillator running</li> </ol> |

| 0        | 0        | 1             |                                                                                                                                                  |

| 0        | 1        | 0             |                                                                                                                                                  |

| 0        | 1        | 1             | <ol> <li>3) 32 Khz</li> <li>4) STOP CLOCK</li> <li>5) EXTERNAL CLOCK source *</li> </ol>                                                         |

| 1        | 1        | 0             |                                                                                                                                                  |

| 1        | 1        | 1             |                                                                                                                                                  |

Notes:

\* In this clock mode, it is possible to use external clock source instead

of the internal oscillator source.

\*\* Default (power-up) mode of operation.

Figure 26. PLL Functional Block Diagram

## **Power Down**

The Z893X3 supports different levels of power-down modes to minimize device power consumption. The lowest power consumption is at STOP Clock Mode when the Oscillator is turned off (clock modes 2 and 4 when there is no external clock.) The highest power consumption is when the Z893X3 in Normal mode (Clock Mode 0) and there is medium power consumption mode .The SLOW Clock Mode is when the DSP is running with 32 kHz clock (Crystal Clock Modes 1 and 3) and disabling all the peripherals which are not needed in this mode.

### **Slow Mode**

The SLOW mode reduce the chip power consumption by using the 32 kHz clock (Clock Mode 3) of the crystal as a DSP clock and disabling in software all the unnecessary peripherals.

Clock Mode 1 also uses the 32 kHz clock, but in this mode the VCO is still running to enable fast switching (wake up) to the high frequency.

### Stop Mode

The STOP mode provides the lowest possible device standby current. In this mode of operation the on chip oscillator and internal system clock are turned off.

In Clock Mode 2 the Oscillator is running while the system clock is turned off to enable fast switching (wake up) to the high frequency.

STOP mode is exited when the recovery source as defined in Bank4/EXT5[6:5] is toggled to the recovery defined level. In case of Clock Mode 2 the program resumes operation starting from the next instruction after the stop instruction. In case of Clock Mode 4, the program resumes operation starting from the reset vector address after executing operations similar to the Power-On Reset sequence of operations.

## **Interrupt Controller**