# Z90365

## DIGITAL TELEVISION CONTROLLER

### **FEATURES**

| Device | ROM  | RAM*    | PWM     | Voltage     |

|--------|------|---------|---------|-------------|

|        | (KW) | (Words) | (8-Bit) | Range       |

| Z90365 | 32   | 640     | 8       | 4.5 to 5.5V |

Note: \*General-Purpose

- 42-Pin SDIP

- 0°C to +70°C Temperature Range

- Fully Customized Character Set

- Character-Control and Closed-Caption Modes

- Keypad User Control

- TV Tuner Serial Interface

- Direct Video Signals

- Supports Violence Blocking

- Speed: 12 MHz

### **GENERAL DESCRIPTION**

The Z90365 Digital Television Controller is designed to provide complete audio and video control of television receivers, video recorders, and advanced on-screen display facilities. The television controller features a Z89C00 RISC processor core that controls the on-board peripheral functions and registers using the standard processor instruction set.

Character attributes can be controlled through two modes: the on-screen display Character-Control Mode and the Closed-Caption Mode. The Character-Control Mode provides access to the full set of attribute controls, allowing the modification of attributes on a character-by-character basis. The insertion of control characters permits direction of other character attributes. Closed-caption text can be decoded directly from the composite video signal and displayed on-screen with the assistance of the processor's digital signal processing (DSP) capabilities.

The fully customized 512 character set, formatted in two 256 character banks, can be displayed with a host of display attributes that include underlining, italics, blinking, eight foreground/background colors, character position offset delay, and background transparency.

Serial interfacing with the television tuner is provided through the tuner serial port. Other serial devices, such as digital channel tuning adjustments, may be accessed through the industry-standard I<sup>2</sup>C port.

User control can be monitored through the keypad scanning port, or the 16-bit remote control capture register. Receiver functions such as color and volume can be directly controlled by eight 8-bit pulse width modulated ports.

**Notes:** All Signals with a preceding front slash, "/", are active Low. For example, B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device   |

|------------|-----------------|----------|

| Power      | V <sub>CC</sub> | $V_{DD}$ |

| Ground     | GND             | $V_{SS}$ |

# **GENERAL DESCRIPTION** (Continued)

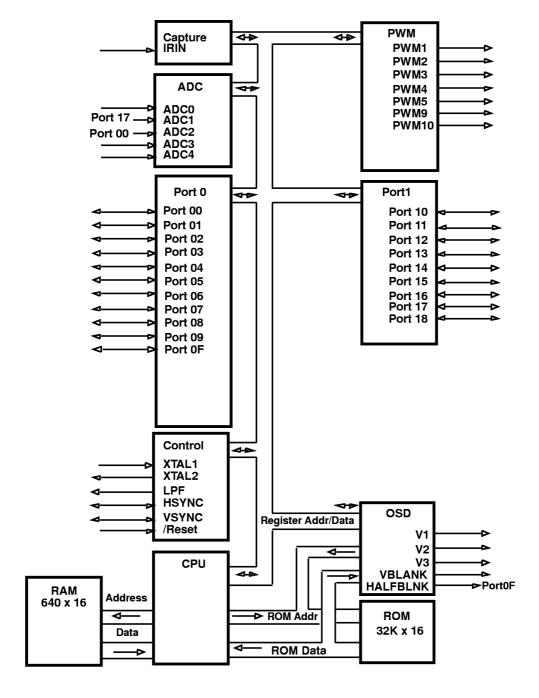

Figure 1. Functional Block Diagram

### PIN DESCRIPTION

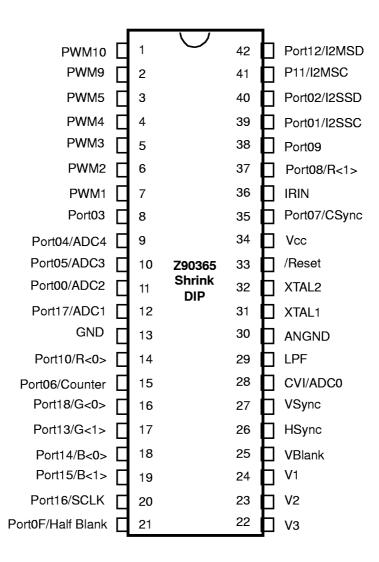

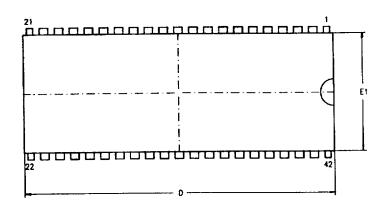

Figure 2. 42-Pin Shrink DIP

# **PIN DESCRIPTION** (Continued)

Table 1. 42-Pin SDIP Pin Identification

| Name                   | Function                                                | Z90365                                                       | Direction | Reset | Notes |

|------------------------|---------------------------------------------------------|--------------------------------------------------------------|-----------|-------|-------|

| V <sub>CC</sub>        | + 5 Volts                                               | 34                                                           | PWR       | _     |       |

| GND                    | 0 Volts                                                 | 13, 30                                                       | PWR       | _     |       |

| IRIN                   | Infrared Remote Capture<br>Input                        | 36                                                           | I         | I     |       |

| ADC[4:0]               | 4-Bit A/D Converter Input                               | 9, 10, 11, 12, 28                                            | Al        | I     |       |

| PWM10, PWM9            | 14-Bit Pulse Width<br>Modulator Output                  | 1, 2                                                         | 0         | 0     |       |

| PWM[5:1]               | 8-Bit Pulse Width Modulator<br>Output                   | 3, 4, 5, 6, 7                                                | 0         | 0     |       |

| Port0[F:0]             | Bit Programmable<br>Input/Output Ports                  | 21, -, -, -, -, -, 38, 37,<br>35, -, -, 15, 8, 40, 39,<br>11 | В         | I     | 1     |

| Port1[8:0]             | Bit Programmable<br>Input/Output Ports                  | 16, 12, 20, 19, 18, 17,<br>42, 41, 14                        | В         | I     |       |

| SCL                    | I <sup>2</sup> C Clock I/O                              | 39 or 41                                                     | BOD       |       | 2     |

| SCD                    | I <sup>2</sup> C Data I/O                               | 40 or 42                                                     | BOD       |       | 3     |

| XTAL1                  | Crystal Oscillator Input                                | 31                                                           | Al        | I     |       |

| XTAL2                  | Crystal Oscillator Output                               | 32                                                           | AO        | 0     |       |

| LPF                    | Loop Filter                                             | 29                                                           | AB        | 0     |       |

| HSYNC                  | H_SYNC                                                  | 26                                                           | В         | I     |       |

| VSYNC                  | V_SYNC                                                  | 27                                                           | В         | I     |       |

| /Reset                 | Device Reset                                            | 33                                                           | I         | I     |       |

| V[3:1]                 | OSD Video Output Typically<br>Drive B, G, and R Outputs | 22, 23, 24                                                   | 0         | 0     |       |

| Blank                  | OSD Blank Output                                        | 25                                                           | 0         | 0     |       |

| HalfBlank              | OSD HalfBlank Output                                    | 21                                                           | 0         |       | 4     |

| RGB Digital<br>Outputs | R[1:0], G[1:0], and B[1:0]<br>Outputs of the RGB Matrix | 37, 14, 17, 16, 19, 18                                       | 0         |       | 5     |

| SCLK                   | Internal Processor SCLK                                 | 20                                                           | 0         |       | 6     |

### Notes:

- 1. SCL I/O pin is shared with Port 0 or Port 11.

- 2. SCD I/O pin is shared with Port 02 or Port 12.

- 3. Half Blank output is a function shared with Port 0F.

- 4. Digital RGB outputs and the internal SCLK are shared with Port 1 [5:0].

- 5. Internal processor SCLK is shared with Port 16. PWM outputs are push/pull

# V1, V2, V3 (R, G, B) ANALOG OUTPUT (PRELIMINARY) $T_A = 0^{\circ}\text{C}$ to $70^{\circ}\text{C}$

|           | Outp                             | Settling Time       |                   |                            |

|-----------|----------------------------------|---------------------|-------------------|----------------------------|

|           | $V_{CC} = 4.75$                  | 5.00V               | 5.25V             | 70% of DC level, 10pF load |

| data = 00 | 0.00v 0.65v                      | 0.00v 0.70v         | 0.00v 0.75v       | 50 ns                      |

| data = 01 | $1.70v \pm 0.20v$                | $1.80v\pm0.20v$     | $1.90v\pm0.20v$   | _                          |

| data = 10 | $2.80v\pm0.25v$                  | $2.90 v \pm 0.25 v$ | $3.00v\pm0.25v$   | _                          |

| data = 11 | $3.90 \text{v} \pm 0.3 \text{v}$ | $4.0v \pm 0.30v$    | $4.10v \pm 0.30v$ | _                          |

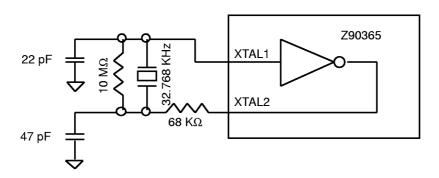

Figure 3. 32 kHz Oscillator Recommended Circuit

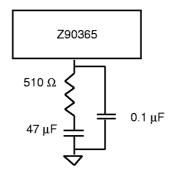

Figure 4. Recommended Low Pass Filter Circuit

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol              | Parameter             | Min  | Max                  | Units | Conditions                       |

|---------------------|-----------------------|------|----------------------|-------|----------------------------------|

| $\overline{V_{CC}}$ | Power Supply Voltage  | 0    | 7                    | V     |                                  |

| $\overline{V_{ID}}$ | Input Voltage         | -0.3 | V <sub>CC</sub> +0.3 | V     | Digital Inputs                   |

| $V_{IA}$            | Input Voltage         | -0.3 | V <sub>CC</sub> +0.3 | V     | Analog Inputs (A/D0A/D4)         |

| $\overline{V_O}$    | Output Voltage        | -0.3 | V <sub>CC</sub> +0.3 | V     | All Push-Pull Digital Output     |

| $\overline{V_O}$    | Output Voltage        | -0.3 | V <sub>CC</sub> +0.3 | V     | Push/Pull PWM Outputs (PWM1PMW8) |

| I <sub>OH</sub>     | Output Current High   |      | -10                  | mA    | One Pin                          |

| I <sub>OH</sub>     | Output Current High   |      | -100                 | mA    | All Pins                         |

| $I_{OL}$            | Output Current Low    |      | 20                   | mA    | One Pin                          |

| I <sub>OL</sub>     | Output Current Low    |      | 200                  | mA    | All Pins                         |

| $T_A$               | Operating Temperature | 0    | 70                   | °C    |                                  |

| $T_A$               | Storage Temperature   | -65  | 150                  | °C    |                                  |

### **DC CHARACTERISTICS**

$T_A = 0^{\circ} C$  to + 70°C;  $V_{CC} = 4.5 V$  to + 5.5V;  $F_{OSC} = 32.768 \; kHz$

| Symbol            | Parameter                | Min                  | Max                  | Typical | Units | Conditions                   |

|-------------------|--------------------------|----------------------|----------------------|---------|-------|------------------------------|

| $\overline{V_IL}$ | Input Voltage Low        | 0                    | 0.2 V <sub>CC</sub>  | 0.4     | V     |                              |

| V <sub>IH</sub>   | Input Voltage High       | 0.7 V <sub>CC</sub>  | V <sub>CC</sub>      | 3.6     | V     |                              |

| V <sub>PU</sub>   | Max. Pull-Up Voltage     |                      | V <sub>CC</sub> +0.3 |         | V     | All Pins                     |

| V <sub>OL</sub>   | Output Voltage Low       |                      | 0.4                  | 0.16    | V     | @ I <sub>OL</sub> = 1 mA     |

| V <sub>OH</sub>   | Output Voltage High      | V <sub>CC</sub> -0.4 |                      | 4.75    | V     | $@ I_{OL} = 0.75 \text{ mA}$ |

| V <sub>XL</sub>   | Input Voltage XTAL1 Low  |                      | 0.3 V <sub>CC</sub>  | 1.0     | V     | External Clock               |

| V <sub>XH</sub>   | Input Voltage XTAL1 High | V <sub>CC</sub> -2.0 |                      | 3.5     | V     | Generator Driven             |

| V <sub>HY</sub>   | Schmitt Hysteresis       | 3.0                  | 0.75                 | 0.5     | V     | On XTAL1 Input Pin           |

| I <sub>IR</sub>   | Reset Input Current      |                      | 150                  | 90      | μΑ    | $V_{RL} = 0V$                |

| I <sub>IL</sub>   | Input Leakage            | -3.0                 | 3.0                  | 0.01    | μΑ    | @ 0V and V <sub>CC</sub>     |

| I <sub>CC</sub>   | Supply Current           |                      | 100                  | 60      | mA    |                              |

| ADC               | Input Current            |                      | 10                   |         | μΑ    |                              |

#### Notes:

- The Z90365 should not be operated for extended periods with the crystal oscillator disconnected, except in the defined powerdown modes. In the event that the Z90365 is operated with the oscillator disconnected, the device may draw higher than typical current

- 2. Each line of the on-screen display can consist of any number of characters, up to a maximum of 30 characters.

### **AC CHARACTERISTICS**

$T_A = 0$ °C to 70°C;  $V_{CC} = 4.5$ V to 5.25V;  $F_{OSC} = 32.768$  kHz

| Symbol            | Parameter                                                          | Min | Typical | Max    | Units |

|-------------------|--------------------------------------------------------------------|-----|---------|--------|-------|

| T <sub>PC</sub>   | Input Clock Period                                                 | 16  | 32      | 100    | μS    |

| $T_{RC}, T_{FC}$  | Clock Input Rise and Fall                                          |     | 12      |        | nS    |

| TD <sub>POR</sub> | Power-On Reset Delay                                               | 8.0 | 1.2     |        | S     |

| TW <sub>RES</sub> | Power-On Reset Minimum Width                                       |     |         | 5 TPC  | μS    |

| TD <sub>HS</sub>  | H-SYNC Incoming Signal Width                                       | 1   | 10      | 15     | μS    |

| TD <sub>VS</sub>  | V-SyYNC Incoming Signal Width                                      | 1   | 200     | 10,000 | μS    |

| TD <sub>ES</sub>  | Time Delay Between Leading Edge of V-SYNC and H-SYNC in EVEN Field | -12 | 0       | +12    | μS    |

| TD <sub>OS</sub>  | Time Delay Between Leading Edge of H-SYNC in ODD Field             | 20  | 32      | 44     | μS    |

| TW <sub>HVS</sub> | H_Sync/V_Sync Edge Width                                           |     | 0.5     | 2.0    | μS    |

**Note:** All timing of the I<sup>2</sup>C bus interface are defined by related specifications of the I<sup>2</sup>C bus interface.

© 1997 by Zilog, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Zilog, Inc. The information in this document is subject to change without notice. Devices sold by Zilog, Inc. are covered by warranty and patent indemnification provisions appearing in Zilog, Inc. Terms and Conditions of Sale only. Zilog, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Zilog, Inc. makes no warranty of merchantability or fitness for any purpose. Zilog, Inc. shall not be responsible for any errors that may appear in this document. Zilog, Inc. makes no commitment to update or keep current the information contained in this document.

Zilog's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the customer and Zilog prior to use. Life support devices or systems are those which are intended for surgical implantation into the body, or which sustains life whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

Zilog, Inc. 210 East Hacienda Ave. Campbell, CA 95008-6600 Telephone (408) 370-8000

FAX 408 370-8056

Internet: http://www.zilog.com

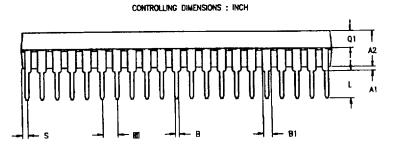

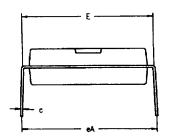

### **PACKAGE INFORMATION**

# **SDIP** (Shrink Dual In-Line Package)

1. Solderability MIL-STD-883C Method 2003.5

Eight Hours Steam Age

2. Mark Permanency 3X soak into Alpha 2110 at 63-70°C.

30 sec. duration each soak. Mech. brush after each soak

| SYMBOL   | MILLIM | ETER     | INC   | Н     |

|----------|--------|----------|-------|-------|

| STMOUL   | MIN    | MAX      | MIN   | MAX   |

| A1       | 0.51   |          | .020  |       |

| A2       |        | 4.32     |       | .170  |

| B        | 0.38   | 0.56     | .015  | .022  |

| Bl       | 0.76   | 1.27     | .030  | .050  |

| С        | 0.20   | 0.30     | .008  | .012  |

| D        | 36.70  | 36.96    | 1.445 | 1.455 |

| E        | 15.24  | 15.88    | .600  | .625  |

| E١       | 13.72  | 14.22    | .540  | .560  |

| <u> </u> | 1.78   | 1.78 TYP |       | TYP   |

| 64       | 15.49  | 16.76    | .610  | .660  |

| L        | 3.05   | 3.43     | .120  | .135  |

| QI       | 1.65   | 1.91     | .065  | .075  |

| 5        | 0.51   | 0.76     | .020  | .030  |

42-Lead Shrink Dual-In-Line Package (SDIP)