# Z90T366 ROM and Z90T361 OTP

# eZVision 64 KWord Television Controller with OSD

Product Specification PS005901-1100

ZiLOG WORLDWIDE HEADQUARTERS • 910 E. HAmilton Avenue • Campbell, CA 95008 Telephone: 408.558.8500 • Fax: 408.558.8300 • www.ZiLOG.com

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact

ZiLOG Worldwide Headquarters

910 E. Hamilton Avenue Campbell, CA 95008 Telephone: 408.558.8500 Fax: 408.558.8300 www.ZiLOG.com

Windows is a registered trademark of Microsoft Corporation.

### **Document Disclaimer**

© 2000 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

# Table of Contents

| 1 | Over  | view                                                    | 1  |

|---|-------|---------------------------------------------------------|----|

|   | 1.1   | Block Diagram                                           | 3  |

|   | 1.2   | Pin Assignments                                         | 4  |

|   | 1.3   | Pin Descriptions                                        | 5  |

|   | 1.4   | Development Tools                                       | 7  |

| 2 | Oper  | ation                                                   | 8  |

|   | 2.1   | CPU Description                                         | 8  |

|   | 2.2   | Memory (ROM and RAM)                                    | 14 |

|   | 2.3   | Clock Circuit Description                               | 16 |

|   | 2.4   | Reset Conditions                                        |    |

|   | 2.5   | Power Management                                        | 20 |

|   | 2.6   | I/O Port Configurations                                 | 20 |

|   | 2.7   | Interrupts                                              | 22 |

|   | 2.8   | Timers                                                  | 23 |

|   | 2.9   | ADC                                                     | 24 |

|   | 2.10  | Pulse Width Modulation                                  |    |

|   | 2.11  | I2C Interface                                           | 27 |

|   | 2.12  | On-Screen Display (OSD)                                 | 32 |

|   | 2.13  | Cursor                                                  |    |

|   | 2.14  | Color Palette Assignment                                | 43 |

|   | 2.15  | Other Functions                                         | 44 |

| 3 | Regis | ster Groups                                             | 46 |

|   | 3.1   | Register Description                                    | 47 |

|   | 3.2   | Bank0 (I/O Ports, I2C Interface, PLL Frequency, Cursor) |    |

|   |       | Control Registers                                       |    |

|   | 3.3   | Bank1 (Control Registers)                               | 53 |

|   | 3.4   | Bank2 (PWM Registers)                                   | 67 |

|   | 3.5   | Bank3 (On Screen Display [OSD] registers)               | 69 |

| 4 | Instruction Set      |                             |     |  |

|---|----------------------|-----------------------------|-----|--|

|   | 4.1                  | Instruction Summary         | 81  |  |

|   | 4.2                  | Instruction Operands        |     |  |

|   | 4.3                  | Instruction Format          |     |  |

|   | 4.4                  | Instruction Bit Codes       |     |  |

|   | 4.5                  | Instruction Format Examples | 91  |  |

|   | 4.6                  | Instruction Timing          |     |  |

|   | 4.7                  | Instruction Op Codes        |     |  |

| 5 | Syste                | m Design Considerations     | 169 |  |

| 6 | Electr               | ical Characteristics        | 171 |  |

|   | 6.1                  | DC Peripherals              |     |  |

|   | 6.2                  | AC Characteristics          |     |  |

|   | 6.3                  | ANALOG RGB                  |     |  |

| 7 | Packaging17          |                             |     |  |

| 8 | Ordering Information |                             |     |  |

# List of Figures

| 1  | Block Diagram                                  | 3    |

|----|------------------------------------------------|------|

| 2  | 52-Pin SDIP Pinout                             | 4    |

| 3  | Code Development Environment                   | 7    |

| 4  | AR Register Format                             |      |

| 5  | RAM, ROM, and Pointer Architecture             | 14   |

| 6  | ROM Мар                                        | 15   |

| 7  | RAM Allocation                                 | 16   |

| 8  | Clock Switching Block Diagram (8 -16 MHz)      | 17   |

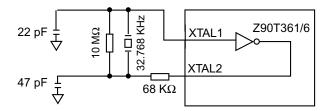

| 9  | 32 KHz Oscillator Recommended Circuit          | 17   |

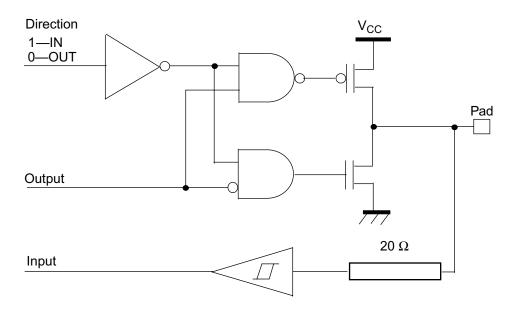

| 10 | Bidirectional Port Pins                        | 21   |

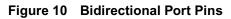

| 11 | Bidirectional Pins Multiplexed with I2C Port   | 21   |

| 12 | Bidirectional Pins Multiplexed with ADC Inputs | 22   |

| 13 | IR Capture Register Block Diagram              |      |

| 14 | Z90T361/6 ADC Block Diagram                    |      |

| 15 | ADC Data Packing                               |      |

| 16 | Master Mode                                    |      |

| 17 | Slave Mode                                     | 31   |

| 18 | Data Flow                                      | 33   |

| 19 | Blank and R, G, B Outputs in Digital Mode      | 33   |

| 20 | R, G, and B Outputs in Analog (Palette) Mode   |      |

| 21 | Character Expansion                            |      |

| 22 | Table Settings                                 |      |

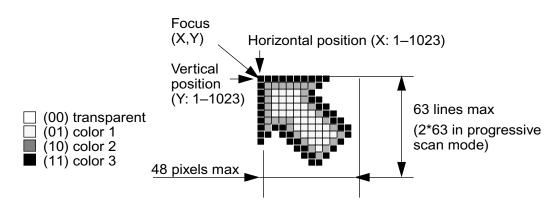

| 23 | Cursor                                         |      |

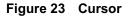

| 24 | Programmable Palette Control at AR Register    | 43   |

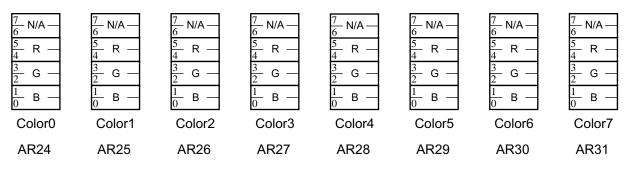

| 25 | IR Capture Register Input                      |      |

| 26 | Loop Filter Pin Configuration                  | 44   |

| 27 | Pipeline Execution                             |      |

| 28 | System Block Diagram                           | .170 |

| 29 | Recommended Application Schematics             |      |

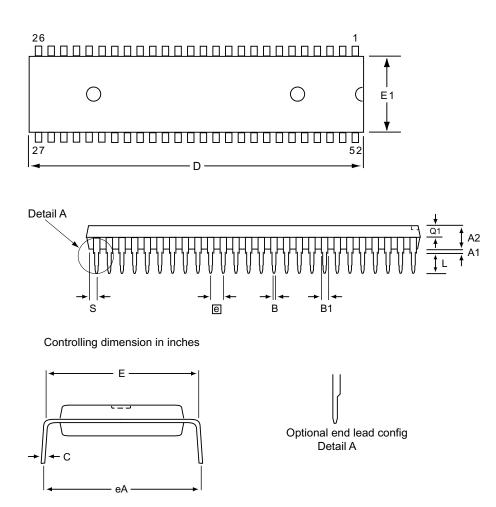

| 30 | 52-Pin SDIP Package Dimensions                 |      |

# List of Tables

| 1  | Z90T366 or Z90T361 Pin Description                    | 5  |

|----|-------------------------------------------------------|----|

| 2  | Internal Registers                                    | 9  |

| 3  | Status Register                                       | 9  |

| 4  | Ram Pointer Loop Description                          |    |

| 5  | Additional Control Registers                          | 13 |

| 6  | Reset Conditions                                      | 18 |

| 7  | ADC Inputs Typical Range                              | 24 |

| 8  | Master I2C Bus Bit Rates                              | 27 |

| 9  | Master I2C Bus Interface Commands                     | 28 |

| 10 | Slave I2C Bus Interface Commands                      | 29 |

| 11 | Character Expansion Register                          |    |

| 12 | Attribute Assignment                                  |    |

| 13 | Cursor Parameters                                     | 40 |

| 14 | Memory Allocation for Cursor Bitmap                   | 41 |

| 15 | Fixed Palette Color Assignment                        | 43 |

| 16 | R4(1) <e:d> Settings</e:d>                            | 45 |

| 17 | Register Summary                                      | 46 |

| 18 | Bank Assignments                                      | 47 |

| 19 | Register1, Bank0, Cursor Palette                      | 48 |

| 20 | Register2, Bank0, PLL Frequency Data Register         | 48 |

| 21 | Register3, Bank0, I2C Interface Register              | 50 |

| 22 | Register5, Bank0, Port 1 Data Register                | 51 |

| 23 | Register4, Bank0, Port 0 Data Register                | 51 |

| 24 | Register6, Bank0, Port 0 Direction Register           | 52 |

| 25 | Register7, Bank0, Port 1 Direction Register           | 52 |

| 26 | Register0, Bank1, Clamp Position Register             | 53 |

| 27 | Register1, Bank1, Speed Control Register              | 55 |

| 28 | Register2, Bank1, WDT/STOP (write only) and           |    |

|    | 9-bit Counter (read only) Control Register            |    |

| 29 | Register3, Bank1, Standard Control Register           | 58 |

| 30 | Register4, Bank1, ADC Control Register                |    |

| 31 | Register5, Bank1, Timer Control Register              | 61 |

| 32 | Register6, Bank1, Clock Switch Control Register       |    |

| 33 | Register7, Bank1, Interrupts/WDT/SMR Control Register |    |

| 34 | Interrupt Priority                                    | 67 |

| 35       | Register0–Register5, Bank 2, PWM 1–6 Registers                                                         | 67 |

|----------|--------------------------------------------------------------------------------------------------------|----|

| 36       | Register6, Bank 2, Shadow Control Register                                                             | 68 |

| 37       | Register7, Bank 2, CGROM Offset Register                                                               | 69 |

| 38       | Register0–Register1, Bank 3, Write Operation, Shift Registers                                          | 70 |

| 39       | Register0–Register2, Bank 3, Read Operation,                                                           |    |

|          | Character Multiple Registers                                                                           | 70 |

| 40       | Register2, Bank 3, Attributes Register, Write Operation                                                | 71 |

| 41       | Register3, Bank 3, Write Operation, Attribute Data Register                                            | 73 |

| 42       | Register3, Bank 3, Read Operation, Attributes Register                                                 | 73 |

| 43       | Register 3, Bank 3, Display Character Format for                                                       |    |

|          | Attribute Data Register, OSD Mode Write Operation                                                      | 74 |

| 44       | Register 3, Bank 3, Control Character Format for                                                       |    |

|          | Attribute Data Register, OSD Mode Write Operation                                                      | 75 |

| 45       | Register 3, Bank 3, Display Character Format for                                                       | 70 |

| 40       | Attribute Data Register, Write Operation CCD Mode                                                      | 76 |

| 46       | Register 3, Bank 3, Control Character Format for<br>Attribute Data Register, CCD Mode, Write Operation | 76 |

| 47       |                                                                                                        |    |

|          | Register4, Bank 3, OSD Control Register                                                                |    |

| 48<br>40 | Register5, Bank 3, Capture Register, Read Operation                                                    |    |

| 49<br>50 | Register6, Bank 3, Palette Control Register                                                            |    |

| 50<br>51 | Register7, Bank 3, Output Palette Control Register                                                     |    |

|          | Instruction Format Mnemonics                                                                           |    |

| 52<br>52 | Accumulator Modification Instructions                                                                  |    |

| 53       | Arithmetic Instructions                                                                                |    |

| 54<br>57 | Bit Manipulation Instructions                                                                          |    |

| 55       | Load Instructions                                                                                      |    |

| 56       | Logical Instructions                                                                                   |    |

| 57       | Program Control Instructions                                                                           |    |

| 58       | Rotate and Shift Instructions                                                                          |    |

| 59       | Instruction Operand Summary                                                                            |    |

| 60       | Instruction Mnemonics/Operands                                                                         |    |

| 61       | Condition Code Bits                                                                                    |    |

| 62       | Accumulator Modification Bits                                                                          |    |

| 63       | Flag Modification Bits                                                                                 |    |

| 64       | Register Pointer/ Data Pointer Bits                                                                    |    |

| 65       | Register Bits                                                                                          |    |

| 66       | General Instruction Format                                                                             |    |

| 67       | Accumulator Modification Format                                                                        |    |

| 68       | Flag Modification Format                                                                               | 94 |

| 69 | Direct Internal Addressing Format    | 95 |

|----|--------------------------------------|----|

| 70 | Short Immediate Addressing Format    |    |

| 71 | Long Immediate Addressing Format     |    |

| 72 | Jump and Call Instruction Formats    |    |

| 73 | Instruction Op Codes                 |    |

| 74 | Instruction Descriptions             |    |

| 75 | Instruction Format Mnemonics         |    |

| 76 | Absolute Maximum and Minimum Ratings |    |

| 77 | DC Characteristics                   |    |

| 78 | R, G, and B Analog Output            |    |

| 79 | ADC0/Small Range*                    |    |

| 80 | AC Characteristics                   |    |

| 81 | ADC1-ADC4/Full range                 |    |

| 82 | RGB Voltage Specification            |    |

| 83 | RGB Time Specification               |    |

| 84 | Controlling Dimensions               |    |

# **Z90T366 ROM and Z90T361 OTP eZVision** 64 KWord Television Controller with OSD

### 1 Overview

The eZVision Z90T366 and Z90T361 are the ROM and one-time programmable (OTP) versions of a Television Controller with On-Screen Display (OSD) that contains 64 KWords of program memory and 1 Kword of RAM.

ZiLOG's eZVision Z90T366 TV controller with On-Screen Display (OSD) is a highly-integrated solution for television design. The Z90T366 boasts a high-speed 16-bit, advanced Digital Signal Processor (DSP) and powerful OSD engine. Flexible and sophisticated, the OSD includes video display attributes, semi-transparency, programmable color palettes, and a hardware cursor for easy user interface. The Z90T366 supports parental control, closed captioning, and Extended Data System (XDS).

The Z90T366 is an ideal choice for mainstream television sets for both PAL and NTSC standards.

The Z90T36x family consists of the following two basic devices:

- the Z90T366 masked ROM

- the Z90T361 One Time Programmable (OTP) device

In addition, Zilog provides a comprehensive development suite for television system developers including an emulator capable of OTP programming, OSD evaluation board, C-compiler, Application Programmer Interface (API), ZiLOG's Developer Studio (ZDS) software, and Graphics User Interface (GUI) OSD screen design tools. These tools enable TV developers to work efficiently and effectively to bring new products to market.

- The eZVision **Z90T361** is the OTP controller used to develop code and prototypes for specific television applications or initial limited production. Program ROM and Character Generation ROM (CGROM) in the Z90T361 are both programmable.

- The eZVision **Z90T366** incorporates the ROM code developed by the customer with the Z90T361. Customer code is masked into both program ROM and CGROM.

The Z90T366 Television Controller with OSD is based on ZiLOG's Z89C00 processor core. The Z89C00 is a 16-bit, fractional, two's complement CMOS Digital Signal Processor (DSP). Most instructions are accomplished in a single clock cycle. This processor features a 24-bit Arithmetic Logic Unit (ALU) and a 24-bit Accumulator. The processor also contains a six-level stack and three vectored interrupts.

The Z90T366 contains 64 KWords of program ROM and 1 KWord of on-chip data RAM. Program ROM space can hold an unlimited number of characters with a 16x16, 16x18, and 16x20 programmable matrix in relocated Character Generation ROM (CGROM), which is only restricted by the available ROM. In addition, the Z90T366 contains four external register banks with eight registers each. Additional Control Registers (AR) are available to control new peripherals like palette banks and memory management.

An internal 24-MHz/2 system clock has a Phase Lock Loop (PLL) driven by an external 32.768-KHz crystal.

Six-channels of 4-bit Analog to Digital Converters (ADC) support the following:

- Analog control front panel buttons

- Audio level input

- Vertical Blank Interval (VBI) data capture

Six Pulse Width Modulator (PWM) outputs allow low-cost digital-to-analog conversion. The PWMs have 8-bit resolution to control video and audio attributes.

A Master/Slave I<sup>2</sup>C (Inter Integrated Circuit) bus interface provides serial system interconnect to common peripheral functions.

Twenty-four programmable I/O pins provide flexibility for other digital input/output functions.

An IR (InfraRed) remote capture register facilitates reliable remote data capture.

On-chip Horizontal Synchronization ( $H_{SYNC}$ ) and Vertical Synchronization ( $V_{SYNC}$ ) circuits generate a video time base (typically used for VCR and set-top applications) in the absence of an available video signal.

Micro-programmable OSD generation logic provides flexibility to tailor OSD features and functions. In addition to normal OSD functions, Closed Caption is supported in accordance with FCC Report and Order on GEN Docket No. 91-1, dated April 12, 1991. Expanded Data Service (XDS) capability is supported as well.

The Z90T366 is packaged in a 52-pin SDIP package.

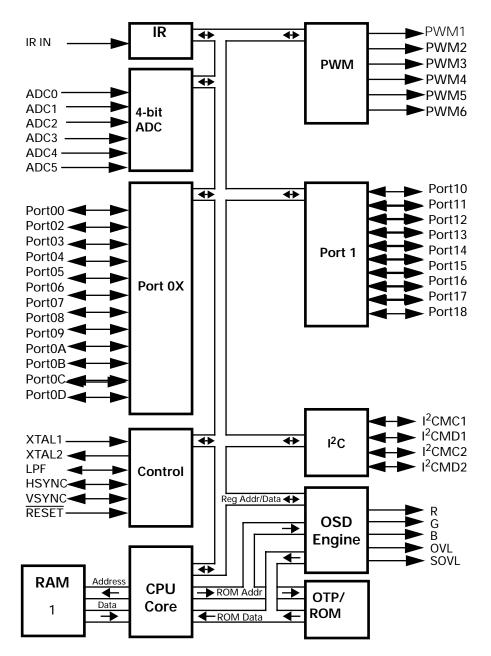

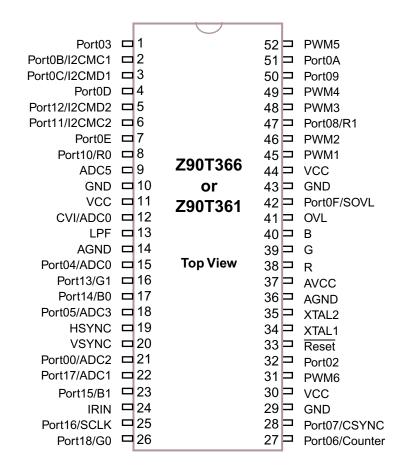

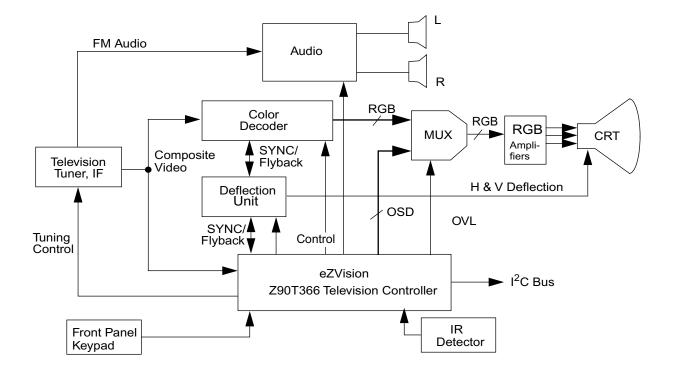

Figure 1 is a block diagram of the internal structure of the chip. Figure 2 illustrates the pin locations, and Table 1 describes the function of each pin.

## 1.1 Block Diagram

Figure 1 Block Diagram

## 1.2 Pin Assignments

Figure 2 52-Pin SDIP Pinout

For simplicity, both the Z90T366 and Z90T361 will be referred to as the Z90T366.

# 1.3 Pin Descriptions

### Table 1 Z90T366 or Z90T361 Pin Description

| Symbol                       | Pin #                        | Function                                  | Direction |

|------------------------------|------------------------------|-------------------------------------------|-----------|

| Port03 1                     |                              | Port 03                                   | I/O       |

| Port0B/I <sup>2</sup> CMC1 2 |                              | Port 0B or Master1 I <sup>2</sup> C clock | I/O       |

| Port0C/I <sup>2</sup> CMD1   | 3                            | Port 0C or Master1 I <sup>2</sup> C data  | I/O       |

| Port0D                       | 4                            | Port 0D                                   | I/O       |

| Port12/I <sup>2</sup> CMD2   | 5                            | Port 12 or Master2 I <sup>2</sup> C data  | I/O       |

| Port11/I <sup>2</sup> CMC2   | 6                            | Port 11 or Master1 I <sup>2</sup> C clock | I/O       |

| Port0E                       | 7                            | Port 0E                                   | I/O       |

| Port10/R0                    | 8                            | Port 10 or digital RGB output, red        | I/O       |

| ADC5                         | 9                            | ADC5 input                                | I         |

| GND                          | 10                           | Digital ground                            | Power     |

| VCC                          | 11                           | Digital Vcc                               | Power     |

| CVI/ADC0                     | 12                           | ADC0 input or Composite Video Input       | AI        |

| LPF                          | 13                           | Loop filter                               | AI/AO     |

| AGND                         | 14                           | Analog ground                             | Power     |

| Port04/ADC0                  | DC0 15 Port 04 or ADC0 input |                                           | I/O or Al |

| Port13/G1                    | 16                           | Port 13 or digital RGB output, green      | I/O       |

| Port14/B0 17                 |                              | Port 14 or digital RGB output, blue       | I/O       |

| Port05/ADC3 18               |                              | Port 05 or ADC3 input                     | I/O or Al |

| HSYNC                        | 19                           | Horizontal sync                           | I/O       |

| VSYNC                        | 20                           | Vertical sync                             | I/O       |

| Port00/ADC2                  | 21                           | Port 00 or ADC2 input                     | I/O or AI |

| Port17/ADC1                  | 22                           | Port 17 or ADC1 input                     | I/O or Al |

| Port15/B1                    | 23                           | Port 15 or digital RGB output, blue       | I/O       |

| IRIN                         | 24                           | Infrared remote capture input             | I         |

| Port16/SCLK                  | 25                           | Port 16 or internal process SCLK          | I/O       |

| Port18/G0                    | 26                           | Port 18 or digital RGB output, green      | I/O       |

| Port06/CNTR 27               |                              | Port 06 or counter input                  | I/O       |

| Symbol                    | Pin #                    | Function                                        | Direction |

|---------------------------|--------------------------|-------------------------------------------------|-----------|

| Port07/CSYNC 28           |                          | Port 07 or composite sync output                | I/O       |

| GND                       | 29                       | Digital ground                                  | Power     |

| VCC                       | 30                       | Digital Vcc                                     | Power     |

| PWM6                      | 31                       | 8-bit PWM output                                | 0         |

| Port02                    | 32                       | Port 02                                         | I/O       |

| RESET                     | 33                       | Reset                                           | I         |

| XTAL1                     | 34                       | Crystal oscillator input                        | AI        |

| XTAL2                     | 35                       | Crystal oscillator output                       | AO        |

| AGND                      | 36                       | Analog ground                                   | Power     |

| AVCC                      | 37                       | Analog Vcc                                      | Power     |

| R                         | 38                       | OSD video output to drive Red                   | O/AO      |

| G                         | 39                       | OSD video output to drive Green                 | O/ AO     |

| В                         | 40                       | 40 OSD video output to drive Blue               |           |

| OVL 41 OSD overlay output |                          | 0                                               |           |

| Port0F/SOVL               | 42                       | Port 0F or OSD semi-transparency overlay output | I/O       |

| GND                       | 43                       | Digital ground                                  | Power     |

| VCC                       | 44                       | Digital Vcc                                     | Power     |

| PWM1                      | 45                       | 8-bit PWM output                                | 0         |

| PWM2                      | 46                       | 8-bit PWM output                                | 0         |

| Port08/R1                 | 47                       | Port 08 or digital RGB output, red              | I/O       |

| PWM3                      | 48                       | 8-bit PWM output                                | 0         |

| PWM4                      | PWM4 49 8-bit PWM output |                                                 | 0         |

| Port09                    | 50                       | Port 09                                         | I/O       |

| Port0A 51                 |                          | Port 0A                                         | I/O       |

| PWM5                      | 52                       | 8-bit PWM output                                | 0         |

### Table 1 Z90T366 or Z90T361 Pin Description (Continued)

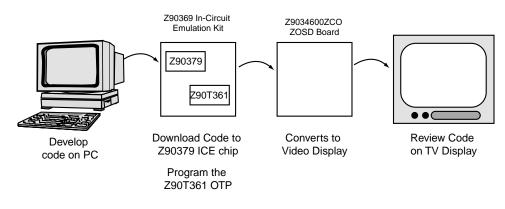

## 1.4 Development Tools

The Z90T361 requires ZiLOG's Z90369ZEM Emulator with its proprietary ZiLOG Developer Studio (ZDS) software for programing. To view code effects, the emulator uses a ZiLOG On-Screen Display (ZOSD) board that connects directly to a television screen. Refer to Figure 3.

Figure 3 Code Development Environment

## 2 Operation

### 2.1 CPU Description

The Z89C00 core is a high-performance DSP that has a modified Harvard-type architecture with separate program and data memories. The design has been optimized for processing power.

The Z89C00 used in the Z90T366 device has been modified. The multiplier is disabled. However, the X and Y registers in the multiplier are still available and can be used as general-purpose registers. Refer to ZiLOG's Z89C00 documentation.

### ALU

The 24-bit ALU has two input ports, one of which is connected to the output of the 24-bit Accumulator. The other input is connected to the 24-bit P-Bus; the upper 16 bits are connected to the 16-bit D-Bus.

### **Instruction Timing**

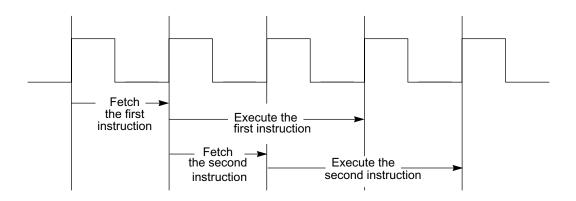

Several instructions are executed in one machine cycle. Lenghty immediate instructions and Jump or Call instructions are executed in two machine cycles. When the program memory is referenced in internal RAM indirect mode, it requires three machine cycles. An additional machine cycle is required if the program counter (PC) is selected as the destination of a data transfer instruction. This only occurs with a register indirect branch instruction.

### **Hardware Stack**

A six-level hardware stack is connected to the D-Bus to hold subroutine return addresses or data. The CALL instruction pushes PC+2 onto the stack. The RET instruction returns the contents of the stack to the program counter.

### **CPU Registers**

The Z90T366 has 11 physical internal registers and four banks of eight external registers. In addition, it has nine virtual registers. The 11 internal registers are defined in Table 2, and the status register is defined in Table 3.

### **Internal Registers**

#### Table 2 Internal Registers

| Register Definition      | Size                                                                                                               |

|--------------------------|--------------------------------------------------------------------------------------------------------------------|

| General purpose register | 16 bits                                                                                                            |

| General purpose register | 16 bits                                                                                                            |

| Accumulator              | 24 bits                                                                                                            |

| Status Register          | 16 bits                                                                                                            |

| Six RAM Address Pointers | 8 bits each                                                                                                        |

| Program Counter          | 16 bits                                                                                                            |

|                          | General purpose register<br>General purpose register<br>Accumulator<br>Status Register<br>Six RAM Address Pointers |

### Table 3 Status Register

| Bit/Field              | Bit Position | R/W | Description                                                                          |

|------------------------|--------------|-----|--------------------------------------------------------------------------------------|

| Ν                      | 15           | R   | ALU Negative                                                                         |

| OV                     | 14           | R   | ALU Overflow                                                                         |

| Z                      | 13           | R   | ALU Zero                                                                             |

| С                      | 12           | R   | Carry                                                                                |

| Reserved               | 11           | R   | Reserved                                                                             |

| Reserved               | 10           | R   | Reserved                                                                             |

| Reserved               | 9            | R   | Reserved                                                                             |

| OP                     | 8            | R/W | Overflow Protection                                                                  |

| IE                     | 7            | R/W | Interrupt Enable                                                                     |

| Register Bank Selector | 6,5          | R/W | 00 Register Bank 0<br>01 Register Bank 1<br>10 Register Bank 2<br>11 Register Bank 3 |

| SFD                    | 4,3          | R/W | "Short Form Direct" Bits                                                             |

| RPL                    | 2-0          | R/W | RAM Pointer Loop Size                                                                |

X and Y are 16-bit general purpose registers.

**A** is a 24-bit Accumulator. The output of the ALU is sent to this register. When 16-bit data are transferred into this register, it goes into the 16 MSBs and the least

significant eight bits are set to zero. Only the upper 16 bits are transferred to the destination register when the Accumulator is selected as a source register in transfer instruction.

**SR** is the Status Register that contains the ALU status and the control bits listed in Table 3. The status register is always read in its entirety. S15-S12 are set/reset by the hardware and can only be read through software. They are set or reset by the ALU after an operation.

S8-S0 can be written by software. S8, if 0 (reset), allows the hardware to overflow. If S8 is set, the hardware clamps at maximum positive or negative values instead of overflowing. S7 enables interrupts. S6–S5 are used for "short form direct" addresses, which are described below. The definitions of S2-S0 are listed in Table 4.

| S2 | S1 | <b>S</b> 0 | Loop Size |

|----|----|------------|-----------|

| 0  | 0  | 0          | 256       |

| 0  | 0  | 1          | 2         |

| 0  | 1  | 0          | 4         |

| 0  | 1  | 1          | 8         |

| 1  | 0  | 0          | 16        |

| 1  | 0  | 1          | 32        |

| 1  | 1  | 0          | 64        |

| 1  | 1  | 1          | 128       |

#### Table 4 Ram Pointer Loop Description

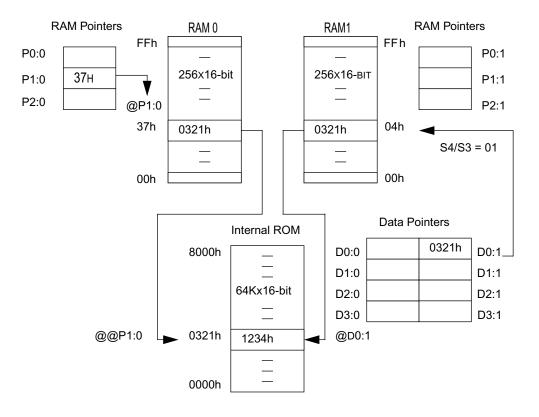

**Pn:b** are the pointer registers for accessing data RAM.

(n= 0, 1, 2 refer to the pointer number)

(b = 0, 1 refers to RAM bank 0 or 1).

They can be read from or written to directly and can point directly to locations in data RAM or indirectly to Program Memory.

**PC** is the Program Counter. When this register is assigned as a destination register, one NOP machine cycle is automatically added to adjust the pipeline timing.

### **External Registers**

The Z90T366 module is capable of accessing eight external registers directly using only the three external register address signals that are normally available. Two user bits (Status register S6-S5) are combined with the register address signals to provide the ability to address four banks of eight registers each. The registers most critical for speed are located together in Bank 3. In this specification, all external registers are referred to

RX(Y) < Z >

where:

X is a register number within a register bank;Y is a bank number; andZ is a bit field number

An external register bank can be selected by setting bits 6 and 5 in the status register to define the bank, then specifying the address of the register on the external register address bus.

External registers reside on the chip and are used to control the operation of all the peripheral modules in the device. By reading or writing to the fields in the external registers, the user can interact with the peripheral devices on the chip.

### **Virtual Registers**

**BUS** is a read-only register that, when accessed, returns the contents of the D-Bus. It is a virtual register. (Physical RAM does not exist on the chip.)

**Dn:b** These eight data pointers refer to possible locations in RAM that can be used as pointers to locations in program memory. The programmer decides which location to choose two bits from in the status register and which two bits in the operand. This means only the lower 16 possible locations in RAM can be specified. At any one time there are eight usable pointers, four per bank, and the four pointers are in consecutive locations in RAM.

For example, if S3/S4 = 01 in the status register, then D0:0/D1:0/D2:0/D3:0 refers to locations 4/5/6/7 in RAM bank 0.

**Note:** When the data pointers are being written to, a number is actually being loaded to Data RAM, so they can be used as a limited method for writing to RAM.

### Additional Control Registers (AR)

Additional Control Registers (AR) control new peripheral blocks like palette banks and memory management. To activate ARs, R0(1)<b> must be set to "1." ARs can

be disabled by setting RO(1) < b > = 0, (POR) for software backward compatibility or if access to RAM location 1FFh is required.

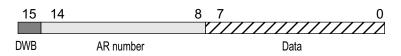

The 128 eight-bit control registers (referred as AR or ARx<y:z>) use RAMmapped I/O access. Location 1FFh in RAM is used to address up to 128 bytewidth ARs. The AR number and written data are encoded into the data field as illustrated in Figure 4.

### Figure 4 AR Register Format

When writing to address 1FFh, the Data Write Bit (DWB) and AR number are latched, depending on whether the DWB data field is either written to the selected port (latched) or discarded (not latched). The AR number and corresponding data are read after reading from the previously latched DWB address 1FFh.

To write to the AR, the data must be written to address 1FFh; DWB must be set to "1," the port number must be specified in bits 8–14, and actual data must be specified in bits 0–7.

### Example

LD A, #(%8000 | 29 <<8 | %57); write 57 (hex) into the AR29 LD %1FF, A;

The DWB and port number are latched for further reading if necessary.

To read from the AR, the address must be previously latched by writing it to address 1FFh with DWB set to "0." Bits 0–7 have no meaning. Because the bits are not going to be written in this mode, only the port number is latched.

### Example

- LD A, #(%0 | 30<<8 | %0); DWB=0, latch AR30, data is not written

- LD %1FF, A;

- LD A, %1FF; read from AR30-%1EXX, where XX is current content

At least one cycle delay (NOP) is required between two consecutive accesses to the AR. If access is performed by a two-cycle instruction, no delay is necessary.

External memory must exhibit access times of less than 60 ns. Table 5 lists the additional control registers.

| AR #   | Name        | Bit position | Data      | Function                                                           |

|--------|-------------|--------------|-----------|--------------------------------------------------------------------|

| 0      | Palette_8   | 76           | Dh        | Reserved                                                           |

|        |             | 543210       | DDh       | Palette8/Color0—R1R0G1G0B1B0                                       |

| 1      | Palette_8   | 76           | Dh        | Reserved                                                           |

|        |             | 543210       | DDh       | Palette8/Color1—R1R0G1G0B1B0                                       |

| 2      | Palette_8   | 76           | Dh        | Reserved                                                           |

|        |             | 543210       | DDh       | Palette8/Color2—R1R0G1G0B1B0                                       |

| 3      | Palette_8   | 76<br>543210 | Dh<br>DDh | Reserved<br>Palette8/Color3—R1R0G1G0B1B0                           |

|        | Delette 9   |              |           |                                                                    |

| 4      | Palette_8   | 76<br>543210 | Dh<br>DDh | Reserved<br>Palette8/Color4—R1R0G1G0B1B0                           |

| 5      | Palette_8   | 76           | Dh        | Reserved                                                           |

| 5      |             | 543210       | DDh       | Palette8/Color5—R1R0G1G0B1B0                                       |

| 6      | Palette_8   | 76           | Dh        | Reserved                                                           |

|        |             | 543210       | DDh       | Palette8/Color6—R1R0G1G0B1B0                                       |

| 7      | Palette_8   | 76           | Dh        | Reserved                                                           |

|        |             | 543210       | DDh       | Palette8/Color7—R1R0G1G0B1B0                                       |

| 8–15   | Palette_9   | 76543210     | DDh       | Same as AR 0–7 for Palette9                                        |

| 16–23  | Palette_10  | 76543210     | DDh       | Same as AR 0–7 for Palette10                                       |

| 24–31  | Palette_11  | 76543210     | DDh       | Same as AR 0–7 for Palette11                                       |

| 32–39  | Palette_12  | 76543210     | DDh       | Same as AR 0–7 for Palette12                                       |

| 40–47  | Palette_13  | 76543210     | DDh       | Same as AR 0–7 for Palette13                                       |

| 48–55  | Palette_14  | 76543210     | DDh       | Same as AR 0–7 for Palette14                                       |

| 56–63  | Palette_15  | 76543210     | DDh       | Same as AR 0–7 for Palette15                                       |

| 64–123 |             |              |           | Reserved                                                           |

| 124    | PgLocation0 | 7            | 0         | Page0 is located internally–POR                                    |

|        |             |              | 1         | Page0 is located externally                                        |

|        |             | -6           | 0<br>1    | Internal ROM is enabled–POR<br>Internal ROM is disabled (low power |

|        |             |              | •         | consumption)                                                       |

|        |             | 543210       | DDh       | Page0—external (physical) page number                              |

| 125    | PgLocation1 | 7            | 0         | Page1 is located internally–POR                                    |

|        |             | -6           | 1<br>0    | Page1 is located externally<br>Reserved                            |

|        |             | 543210       | 1         | Page1—external (physical) page number                              |

|        |             | 010210       | DDh       |                                                                    |

| 126    | PgLocation2 | 76543210     | DDh       | Same as above for Page2                                            |

|        |             |              |           |                                                                    |

### Table 5 Additional Control Registers

#### Table 5 Additional Control Registers (Continued)

| AR # | Name        | Bit position | Data | Function                |  |  |  |  |  |

|------|-------------|--------------|------|-------------------------|--|--|--|--|--|

| 127  | PgLocation3 | 76543210     | DDh  | Same as above for Page3 |  |  |  |  |  |

### RAM Addressing

The addresses in RAM can be specified in one of three ways: RAM, ROM, Pointers. Refer to Figure 5.

Figure 5 RAM, ROM, and Pointer Architecture

### 2.2 Memory (ROM and RAM)

The Z90T366 has 64K words of Read Only Memory (ROM) and 1K words of Random Access Memory (RAM).

### ROM

The 64K words mask ROM is designed to provide storage for both program codes and Character set Graphic pixel matrices (CGROM). The address boundary between these applications is dependent on the storage required for character graphics.

The Program ROM (PGMROM) section can, in theory, be accessed anywhere in the addressable ROM space; however, because CGROM usually starts at location 0000h, program ROM resides in the higher address locations. The maximum available ROM space for program memory depends on the ROM reserved for CGROM (for an application).

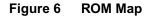

CGROM can be placed anywhere in the 64K ROM address space by setting the CGROM address offset register R7(2). This offset is added to the character address before accessing ROM. By modifying the CGROM offset, several fonts can be accessed (limited by ROM size only). When reset, R7(2) =0 (no offset) for backward compatibility with existing software. Refer to Figure 6.

| 64K        | Int0 vector                                                  | FFFFh                  |

|------------|--------------------------------------------------------------|------------------------|

|            | Int1 vector                                                  | FFFEh                  |

|            | Int2 vector                                                  | FFFDh                  |

|            | Reset vector                                                 | FFFCh                  |

|            | Program ROM or CGROM                                         | FFFBh                  |

| Up to 5K   |                                                              | <u>140</u> 0h          |

| - <b>I</b> | CGROM—Bank 0, Scan lines 19, 20                              | 13FFh                  |

|            | or Bank1 or Program ROM                                      | 1000                   |

| Up to 4.5K | OODOM Dark 0. Or or lives 47, 40                             | <u>120</u> 0h<br>11FFh |

|            | CGROM—Bank 0, Scan lines 17, 18<br>or Bank 1, or Program ROM |                        |

| 4K         | <b>3</b>                                                     | 1000h<br>0FFFh         |

|            | Program ROM                                                  | •••••                  |

| Up to 4K   | CCDOM Dank 0 (n Charactern)                                  | <u>10∗n</u> h          |

|            | CGROM-Bank 0 (n Characters)<br>Scan lines 1-16               | 10*nh-1                |

|            |                                                              | 0000h                  |

### RAM

The 1K words RAM is organized in four banks of 256 words consisting of 16 bits each. Bank1.0 is always accessible. Bank0.0 is mapped to other bank(s); only one page from 0.X is active through bit selection. See Figure 7.

Figure 7 RAM Allocation

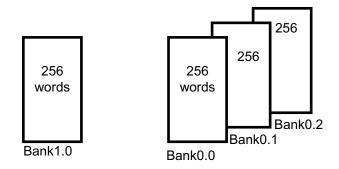

## 2.3 Clock Circuit Description

The processor is able to operate from several clock sources:

- Primary Phase Lock Loop VCO source (PVCO)

- Secondary Phase Lock Loop (SVCO)

- 32.768-KHz oscillator clock (OSC)

In addition, the processor clock can be halted temporarily to select the clock source or access ROM without disrupting normal operation of the processor.

An external crystal controls the internal 32.768-KHz oscillator. The crystal is used as the clock reference for the internal Phase Locked Loop (PLL). The PLL provides the internal PVCO clock for processor operation. The System Clock (SCLK) is generated internally by dividing the frequency of an appropriate oscillator (PVCO) by 2. The frequency of the SCLK after Power On Reset (POR) is 12.058 MHz.

The SCLK signal can be sent to the Port16 output pin under software control by setting bit 9 in register R3(1). The SVCO must be used as the system clock when the OSD is generated.

The clock switch control register R6(1) defines the source of the SCLK for the Z90T366 core. The block diagram in Figure 8 represents the clock switch circuit.

**Note:** Clock switching is not recommended. This feature is only for advanced users.

Figure 8 Clock Switching Block Diagram (8 -16 MHz)

**Note:** Clock switching is discouraged. It is only for advanced users.

### Input/Drive Circuits

The 32 KHz oscillator circuit in Figure 9 is suggested for proper clock operation.

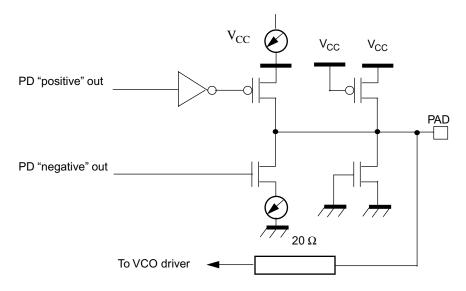

Figure 9 32 KHz Oscillator Recommended Circuit

## 2.4 Reset Conditions

Reset conditions including addresses and registers are listed in Table 6.

| Addr  | Register             |    |    |    |    |    |    | Re | set | Cor | diti | on |   |   |   |   |   | Comments                            |

|-------|----------------------|----|----|----|----|----|----|----|-----|-----|------|----|---|---|---|---|---|-------------------------------------|

|       |                      | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8   | 7   | 6    | 5  | 4 | 3 | 2 | 1 | 0 |                                     |

| R0(0) | reserved             | х  | x  | х  | х  | х  | х  | x  | x   | х   | х    | х  | х | х | х | х | х | Not available                       |

| R1(0) | Cursor Palette       | х  | х  | 0  | 0  | х  | х  | х  | х   | х   | х    | х  | х | х | х | х | х | Cursor palette<br>gauge             |

| R2(0) | pll_freq             | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0   | 0   | 1    | 1  | 1 | 0 | 0 | 0 | 0 | PLL frequency control               |

| R3(0) | I <sup>2</sup> C_int | 0  | 0  | 0  | 0  | 0  | 1  | х  | х   | х   | х    | х  | х | х | х | х | х | I <sup>2</sup> C interface register |

| R4(0) | port0                | х  | х  | х  | х  | х  | х  | х  | х   | х   | х    | х  | х | х | х | х | х | 16-bit I/O port 0                   |

| R5(0) | port1                | х  | х  | х  | х  | х  | х  | х  | х   | х   | х    | х  | х | х | х | х | х | 9-bit I/O port 1                    |

| R6(0) | dir0                 | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1   | 1    | 1  | 1 | 1 | 1 | 1 | 1 | 16-bit port 0<br>direction          |

| R7(0) | dir1                 | х  | x  | х  | х  | х  | х  | х  | 1   | 1   | 1    | 1  | 1 | 1 | 1 | 1 | 1 | 9-bit port 1 direction              |

| R0(1) | clamp_pos            | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0   | 0   | х    | х  | х | х | х | х | х | position of video<br>clamp pulse    |

| R1(1) | sclk_freq            | х  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | х   | х    | х  | 0 | 0 | 0 | 0 | 0 | Stop/sleep/normal mode              |

| R2(1) | 9-bit cntr           | х  | х  | х  | х  | х  | х  | х  | х   | х   | 0    | 0  | 0 | 0 | 0 | 0 | 0 | Stop and WDT, 9-<br>bit counter     |

| R3(1) | standard_ctl         | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0    | 0  | х | х | х | 0 | 0 | Output H/VSYNC/<br>Blink Control    |

| R4(1) | ADC_ctl              | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0    | 0  | 0 | х | х | х | х | A/D converter control               |

| R5(1) | cap_1s_ctl           | х  | х  | х  | х  | 0  | 0  | х  | х   | х   | х    | х  | х | х | х | х | х | Counter timers control              |

| R6(1) | clock_ctl            | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0    | 0  | 1 | х | х | х | х | Clock control<br>(switch VCO/DOT)   |

| R7(1) | wdt_smr_ctl          | х  | х  | х  | х  | х  | х  | х  | х   | 0   | х    | х  | х | х | х | х | х | SMR and WDT control/interrupt       |

### Table 6Reset Conditions

| Addr  | Register       |    |    |    |    |    |    | Re | set | Сог | nditi | on |   |   |   |   |   | Comments                                               |

|-------|----------------|----|----|----|----|----|----|----|-----|-----|-------|----|---|---|---|---|---|--------------------------------------------------------|

|       |                | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8   | 7   | 6     | 5  | 4 | 3 | 2 | 1 | 0 |                                                        |

| R0(2) | pwm_data1      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | х   | х     | х  | х | х | х | х | х | 8-bit PWM 1 data                                       |

| R1(2) | pwm_data2      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | х   | х     | х  | х | х | х | х | х | 8-bit PWM 2 data                                       |

| R2(2) | pwm_data3      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | х   | х     | х  | х | х | х | х | х | 8-bit PWM 3 data                                       |

| R3(2) | pwm_data4      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | х   | х     | х  | х | х | х | х | х | 8-bit PWM 4 data                                       |

| R4(2) | pwm_data5      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | х   | х     | х  | х | х | х | х | х | 8-bit PWM 5 data                                       |

| R5(2) | pwm_data6      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | х   | х     | х  | х | х | х | х | х | 8-bit PWM 6 data                                       |

| R6(2) | Shadow Ctrl    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | х   | х     | х  | х | х | х | х | х | Shadow color ctrl                                      |

| R7(2) | CGROM offset   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0     | 0  | 0 | 0 | 0 | 0 | 0 | CGROM offset register                                  |

| R0(3) | hi_x2_hi_x3    | х  | х  | х  | х  | х  | х  | х  | х   | х   | х     | х  | х | х | х | х | х | Character multiple/<br>current data                    |

| R1(3) | lo_x2_mid_x3   | х  | х  | х  | х  | х  | х  | х  | х   | х   | х     | х  | х | х | х | х | х | Character multiple/<br>next or previous<br>data        |

| R2(3) | Ch_x1_lo_x3    | х  | х  | х  | х  | х  | х  | х  | х   | х   | х     | х  | х | х | х | х | х | Character multiple/<br>character graphics<br>attribute |

| R3(3) | attr_data      | х  | х  | х  | х  | х  | х  | х  | х   | х   | х     | х  | х | х | х | х | х | Character attribute/<br>video RAM data                 |

| R4(3) | osd_cntl       | х  | х  | х  | х  | х  | х  | х  | х   | х   | х     | х  | х | х | х | х | х | On screen display<br>control                           |

| R5(3) | cap_data       | х  | х  | х  | х  | х  | х  | х  | х   | х   | х     | х  | х | х | х | х | х | Capture register<br>data                               |

| R6(3) | palette_color  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0     | 0  | 0 | 0 | 0 | 0 | 0 | Display palette<br>color/underline<br>color            |

| R7(3) | output palette | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0     | 0  | 0 | 0 | 0 | 0 | 0 | Output palette                                         |

### Table 6 Reset Conditions (Continued)

### 2.5 Power Management

There are two low-power operating modes for Z90T366: SLEEP mode and STOP mode.

### SLEEP Mode

In SLEEP mode, the controller uses the 32.768-KHz clock for the SCLK to reduce power consumption.

### **STOP Mode**

In STOP mode, the processor is suspended, and the power consumption is minimized.

### 2.6 I/O Port Configurations

User control can be monitored either through the front panel keypad scanning port or the 16-bit remote control capture register.

Two input/output port blocks are available for general-purpose digital I/O application. Each port bit can be programmed to be either an input or output port. To conserve the device pin count, some port pins are mapped to provide I/O to the ADC converter block and  $I^2C$  interface block.

The 24 configurable I/O pins are general-purpose pins for functions such as serial data I/O, LED On/Off control, key scanning, power control and monitoring, and  $I^2C$  serial data communications.

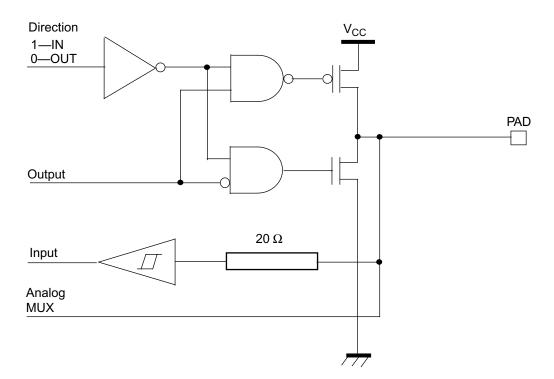

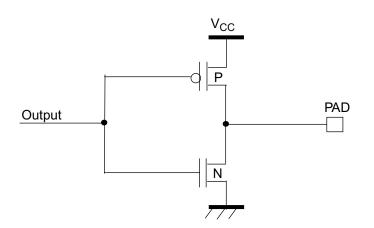

Port 0 and 1 directions are defined in R6(0) and R7(0), respectively. R4(0) and R5(0) are data registers for both Ports 0 and 1. Figure 10, Figure 11, and Figure 12 indicate I/O configuration and sharing with other functional units.

**Note:** Port01 must be configured as an input in the user mode even though it is not called out in the device specification.

Figure 11 Bidirectional Pins Multiplexed with I<sup>2</sup>C Port

Figure 12 Bidirectional Pins Multiplexed with ADC Inputs

### 2.7 Interrupts

•

•

The Z90T366 has three external interrupt signals. There are four interrupt sources as follows:

- Horizontal sync (H<sub>SYNC</sub>)

- Vertical sync (V<sub>SYNC</sub>)

IR Capture timer

External event (Port09) multiplexed

All interrupts are vectored. The capture timer and Port09 are multiplexed to the same interrupt.

Interrupt priorities are programmable. Each interrupt can be masked by setting fields in the external registers.

When the Z90T366 receives an interrupt request from one of the interrupt sources, it executes the interrupt service routine directly for that source.

External register R7(1) controls interrupts.

### 2.8 Timers

### Watch-Dog Timer

The watch-dog timer resets the CPU when it times out.

External register R7(1) controls the watch-dog timer.

### **Real Time Clock**

A clock timer, in real time, generates ticks every 1000, 250, 62.5 or 15.625 ms. External register R5(1) controls the real time clock.

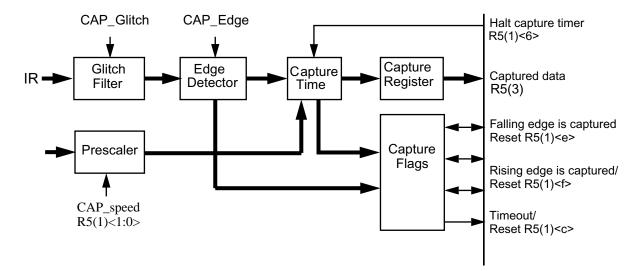

### **IR Capture Timer**

A capture timer measures time between edges of the IR signal. This timer can be programmed to measure timing from rising-to-rising, falling-to-rising, rising-to-falling, or falling-to-falling edges.

The IR capture timer is controlled by External register R5(1). Figure 13 is a block diagram of the IR capture register structure.

Figure 13 IR Capture Register Block Diagram

## 2.9 ADC

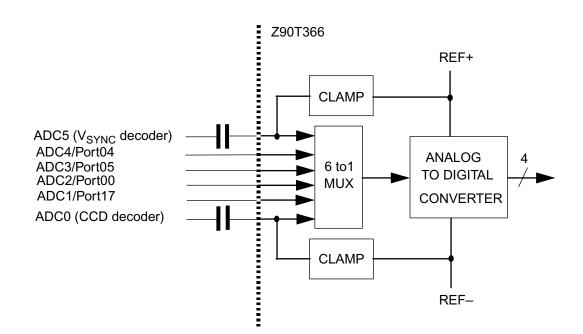

This function employs a 4-bit resolution, flash A-to-D converter. The six-to-one analog input multiplexor and conversion start circuits are controlled by the user program. The 4-bit conversion result is available to be read by the CPU at the end of each conversion.

One input channel (ADC0) is dedicated for quantizing VBI (vertical blanking interval) data for subsequent digital signal processing. Another channel, ADC5, is typically used for V<sub>SYNC</sub> separation from the composite TV signal. These channels (ADC0 and ADC5) feature a special video clamp circuit that provides DC restoration of the composite video input signal. Typical VBI applications include Line 21 Closed Caption, Electronic Data Services, and StarSight Telecast. The range of ADC0 and ADC5 is from 1.5 to 2.0 V.

The four remaining channels of ADC (ADC1, ADC2, ADC3, and ADC4) are general purpose. They are typically used for tuner automatic frequency control and analog key entry. The range of ADC1–ADC4 is from 0 to 5.0 V.

The 4-bit ADC in the Z90T366 features six multiplexed inputs.

The allowed range for input signals differs for various ADC inputs according to Table 7.

| Input       | Range (V) | Clamping   | Typical application                      |

|-------------|-----------|------------|------------------------------------------|

| CVI/ADC0    | 1.5–2.0   | Yes (Ref–) | CCD sampling input                       |

| ADC1/Port17 | 0–5.0     | No         | AFC input                                |

| ADC2/Port00 | 0–5.0     | No         | Key scanning input                       |

| ADC3/Port05 | 0–5.0     | No         | Key scanning input                       |

| ADC4/Port04 | 0–5.0     | No         | Key scanning input                       |

| ADC5        | 1.5–2.0   | Yes (Ref+) | V <sub>SYNC</sub> decoder sampling input |

### Table 7 ADC Inputs Typical Range

Reference voltages that have been generated internally define the maximum range of the input signal for the ADC.

Nominal values are as follows:

Ref+ = 2.0 V Ref- = 1.5 V @  $V_{CC}$  = 5.0 V

For other V<sub>CC</sub> values, the reference voltages must be prorated as follows:

Ref+ =  $0.4 * V_{CC}$ Ref- =  $0.3 * V_{CC}$

The maximum sampling rate of the ADC converter is 3 MHz. It takes 4 SCLK cycles for valid output data from the ADC to become available. This is especially important if the application uses the single-shot mode.

The ADC exhibits monotonous conversion characteristics with a nonlinearity of less than 0.5 LSB. ADC0. The ADC has a range of 0.5V (from 1.5V to 2.0V) and is directly multiplexed to the input of the ADC. The remaining ADC inputs (ranging from 0V to 5V) use AGND and AV<sub>CC</sub> voltage as a reference.

Figure 14 is a block diagram of the ADC inner structure, and Figure 15 illustrates ADC input circuits.

Figure 14 Z90T361/6 ADC Block Diagram

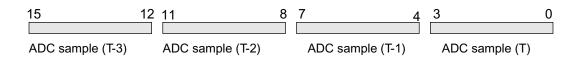

### **ADC Data Packing**

Up to four 4-bit ADC data samples can be packed into one 16-bit word without software overhead. If R4(1)<9> = 1, every reading of R4(1) returns the result, where the High 12 bits are the three previous ADC samples and the Low 4 bits are the current one, as illustrated in Figure 15.

### Figure 15 ADC Data Packing

The following routine shows ADC packing:

- LD SR,%#20; select RegBank1

- LD A,EXT4; turn "ADC data packing" mode on

- OR A, #%0200; set R4(1)<9>

- LD EXT4, A;

- LD A, EXT4; read first ADC sample, A = %0005

- LD A, EXT4; read second ADC sample, A = %005E

- LD A, EXT4; read third ADC sample, A = %05E7

- LD A, EXT4; read forth ADC sample, A= %5E74

- LD A, EXT4; read fifth ADC sample, first sample is thrown away, A = %E741

The ADC is controlled by the external register R4(1).

### 2.10 Pulse Width Modulation

Pulse Width Modulation (PWM) is used in conjunction with external low-pass filters to perform digital-to-analog conversion. Six PWMs (8-bit resolution each) generate signals for the control for video and sound attributes. In case of a chassis employing a frequency synthesis tuner, these PWMs can also control video or sound attributes. PWM's can also be used to acknowledge tones for remote or keyboard commands.

Each PWM circuit features a data register whose contents are set under program control. The data in the register determines the ratio of PWM High to PWM Low time. PWM data registers are not initialized when reset. In order to eliminate a potential glitch on a PWM output, it is recommended to initialize PWM data registers before enabling the VCOs.

External registers R0(2) to R5(2) are data registers for PWM1 to PWM6 accordingly.

# 2.11 I<sup>2</sup>C Interface

There are two hardware modules that support standard  $I^2C$  bus protocol according to the  $I^2C$  bus specification published by Philips in 1992, titled  $I^2C$  *Peripherals for Microcontrollers Data Handbook*.

The first module, the Master, can be configured for fast (400 KHz) or slow (100 KHz) bit rates and can be used in applications with a single master.

The Z90T366 adds two additional non-standard bit rates (50 KHz and 10 KHz) and an additional multiplexed master port that is controlled by the  $I^2CM_mux$  control bit.

Table 8 lists the bit rates for the Master  $I^2C$  Bus.

| Mode    | I <sup>2</sup> C mode | Bit Rate  | Actual Bit Rate |

|---------|-----------------------|-----------|-----------------|

| LO/Slow | _                     | 0–10 KHz  | 10 KHz          |

| HI/Slow | _                     | 0–50 KHz  | 44 KHz          |

| LO/Fast | Slow                  | 0–100 KHz | 91 KHz          |

| HI/Fast | Fast                  | 0–400 KHz | 334 KHz         |

Table 8

Master I<sup>2</sup>C Bus Bit Rates

To suppress possible problems on both data (SDA) and clock (SCL) lines, digital filters are available for all inputs of the I<sup>2</sup>C bus interface. These filters exhibit a time constant equal to  $3T_{SCLK} = 250$  ns.

If the Master  $I^2C$  interface is enabled, corresponding I/Os, Port11 and Port12, must be assigned as outputs.

Master and Slave modules cannot be used simultaneously because of the shared  $I^2C$  data register (see the Register 3(0) data field). The software activates  $I^2C$  modules by writing appropriate commands into the control register. To control the  $I^2C$  bus interface, the control register R3(0) toggle bit <c> must point to an appropriate interface (Master or Slave).

**M\_disable** or **S\_disable** bits allow either the Master or Slave  $I^2C$  interface to be disabled so as not to interfere with any activity associated with the Port pins. At Power-on Reset (POR), both  $I^2C$  interfaces are enabled. To use the  $I^2C$  interface,

the corresponding Port pin (multiplexed with the  $I^2C$  Data and Clock) must be configured as an output, while M\_disable or S\_disable bits must be reset to 0.

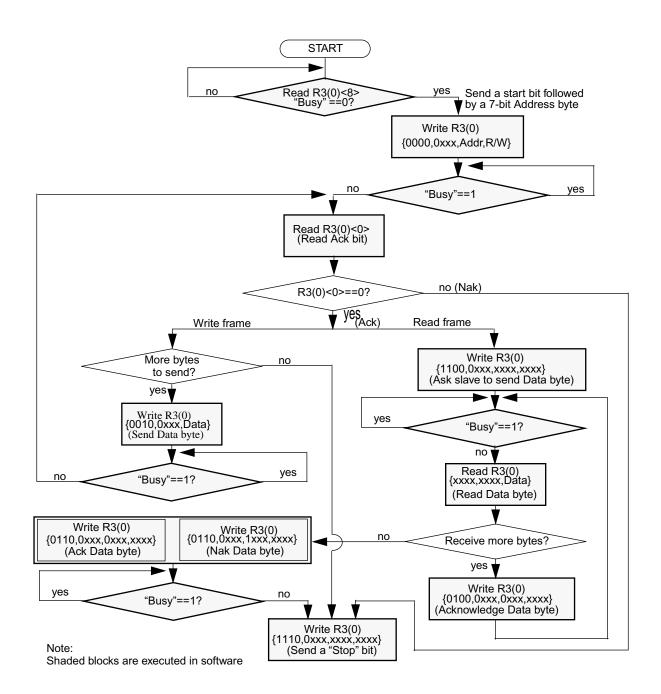

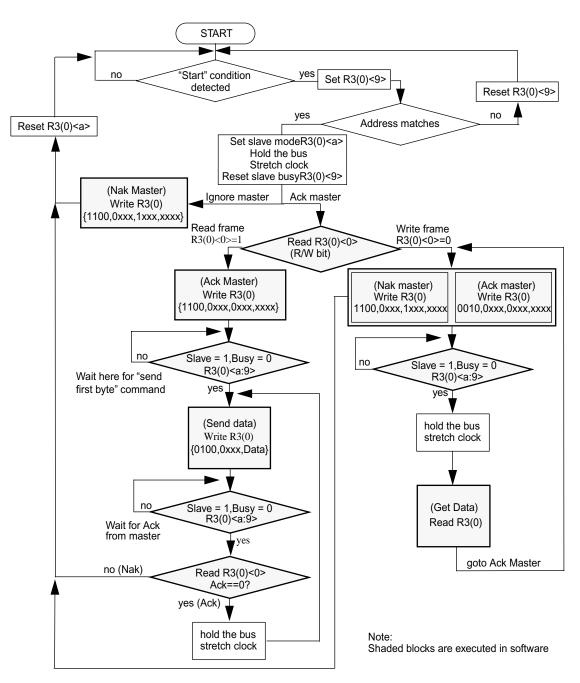

External register R3(0) controls the  $I^2C$ . Table 9 lists the Master  $I^2C$  bus interface commands. Table 10 lists the Slave  $I^2C$  bus interface commands. Figure 16 and Figure 17 are flow charts of the Master and Slave modes.

### Table 9 Master I<sup>2</sup>C Bus Interface Commands

| Command    | Notes/Function                                                                                                                                                                                                                                              |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000        | This command sends a start bit, followed by an address byte specified in the "data" field (bits <7:0>), then fetches an acknowledgment in bit <0>. This command initializes communication and generates 9 SCL cycles.                                       |

| 001        | This command sends one byte of data specified in the "data" field (bits <7:0>), then fetches an acknowledgment in bit <0>. This command is used in a WRITE frame and generates 9 SCL cycles.                                                                |

| 010        | This command sends bit <7> as an acknowledgment (ACK = 0, NAK = 1), then receives a data byte. This command is used in a READ frame when the next data byte is expected and generates 9 SCL cycles. Received data appears in the "data" field (bits <7:0>). |

| 011        | This command sends bit <7> as an acknowledgment (ACK = 0, NAK = 1). This command is used in a READ frame to terminate data transfer and generates one SCL cycle.                                                                                            |

| 100<br>101 | A NULL operation. This command must be used with a "RESET" bit <b><br/>and/or a "TOGGLE" bit <c>.<br/>Using the "RESET" and/or "TOGGLE" bits with any other command<br/>interferes with the logic of the I<sup>2</sup>C interface.</c></b>                  |

| 110        | This command receives one data byte. It is used in a READ frame to receive the first data byte after the address byte is transmitted. It generates 8 SCL cycles.                                                                                            |

| 111        | This command sends a stop bit and generates one SCL cycle.                                                                                                                                                                                                  |

## Table 10 Slave I<sup>2</sup>C Bus Interface Commands

| Command        | Notes/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0 0          | Reserved. Cannot be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0 0 1          | This command sends bit <7> as an acknowledgment (ACK = 0 only), then receives one data byte. This command is used in a WRITE frame and requires 9 SCL cycles. Received data is read as a "data" field (bits <7:0>).                                                                                                                                                                                                                                                                                                                    |

| 0 1 0          | This command sends one byte of data specified in a "data" field (bits <7:0>), then fetches an acknowledgment in bit <0>. This command is used in a READ frame and requires 9 SCL cycles.                                                                                                                                                                                                                                                                                                                                               |

| 0 1 1          | Reserved. Cannot be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1 0 0<br>1 0 1 | A NULL operation. This command must be used with a "RESET" bit <b><br/>and/or "TOGGLE" bit <c>.<br/>Using the "RESET" and/or "TOGGLE" bits with any other command<br/>interferes with the logic of the I<sup>2</sup>C interface.</c></b>                                                                                                                                                                                                                                                                                               |

| 1 1 0          | This command sends a bit <7> as a not acknowledgment (NAK = 1 only)<br>in a WRITE or READ frame. This command terminates I <sup>2</sup> C<br>communication and requires one SCL cycle. The "Sulfonamide" bit <a><br/>is automatically reset when a "busy" bit &lt;9&gt; goes Low.<br/>This command sends a bit &lt;7&gt; as an acknowledgment (ACK = 0 only) in<br/>a READ frame and requires one SCL cycle. The Send data command<br/>(010) must be executed next. This command acknowledges an address<br/>byte in a READ frame.</a> |

| 1 1 1          | Reserved. Cannot be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## Z90T366 ROM and Z90T361 OTP eZVision 64 KWord Television Controller with OSD

Figure 16 Master Mode

## Z90T366 ROM and Z90T361 OTP eZVision 64 KWord Television Controller with OSD

If a "Stop" condition is detected at any point, the hardware resets the "Slave" bit (R3(0)<a>) and releases the  $l^2C$  bus.

Figure 17 Slave Mode

## 2.12 On-Screen Display (OSD)

The Z90T366 provides sophisticated on-screen display features. On-Screen Display has the following two modes:

- OSD Used to generate TV control OSD

- CCD Used to display Closed Caption information

OSD mode provides access to the full set of control attributes including latched and unlatched attributes. Unlatched attributes can be modified on a character-bycharacter basis. Control characters change latched attributes.

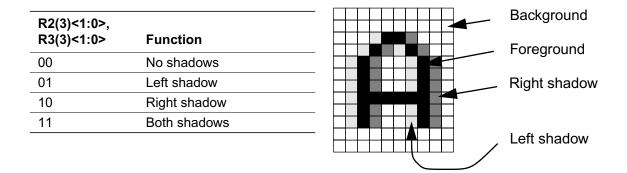

Any 256-character set can be displayed with many display attributes, including underlining, italics, blinking, eight foreground and background colors, character position offset delay, and background transparency. A 16-bit display character represents foreground color, background color, and underline attributes, which can be modified character by character. In addition, the Z90T361 supports eight fixed plus eight programmable color palettes out of 64 colors, independent left and right shadows with color control. Shadows are available on transparent and nontransparent backgrounds. Semi-transparency is supported on a character-by-character basis. A character's pixel array is stored as 16, 18, or 20 words in Character Generation ROM (CGROM).

Additional hardware provides the capability to display characters at two and three times normal size. The smoothing logic contained in the on-screen display improves the appearance of two and three times normal size characters. Shadows can be activated to improve the visibility of characters by adding a border (one pixel wide) on each side.

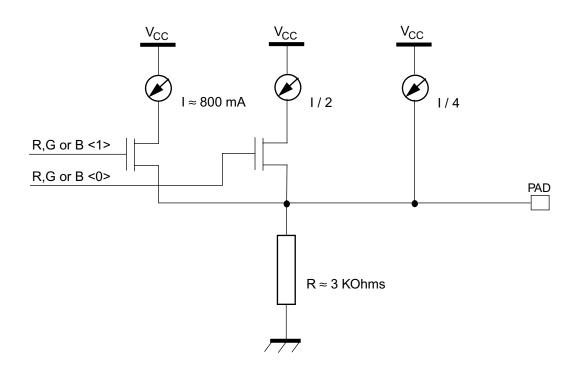

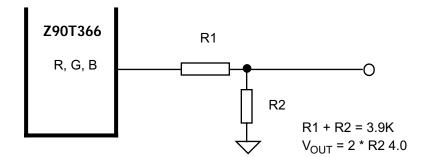

The Z90T366 provides RGB signals and a video blank signal. RGB outputs are available in two modes: digital and analog. In digital mode, the output RGB signals correspond to a primary colors palette. Analog mode supports 15 different palettes, which can be chosen under software control. In analog mode, each RGB output is generated by a 2-bit digital-to-analog converter. The user can switch the 2-bit digital inputs of the digital-to-analog converter to Port pins (Port10, Port13, Port14, Port15, Port18 and Port08) under software control by setting bit9 in register R3(1).

Video synchronization is normally obtained from H\_FLYBACK and V\_FLYBACK but can be generated by the Z90T366 and driven to the external deflection unit using the bidirectional  $H_{SYNC}$  and  $V_{SYNC}$  ports when external video synchronization signals are not present.

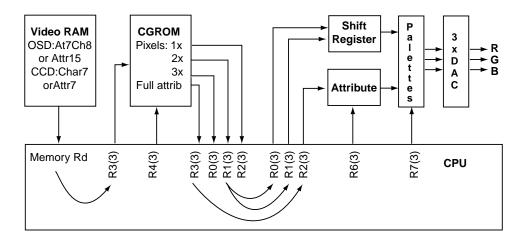

OSD is completely software controlled. Hardware supports the optimum generation of the character-based OSD; however, the CPU can bypass it and

generate pixels and attributes directly. The block diagram in Figure 18 illustrates the OSD data flow.

Figure 19 and Figure 20 indicate the R, G, B, and Blank output circuits.

Figure 19 Blank and R, G, B Outputs in Digital Mode

## Z90T366 ROM and Z90T361 OTP eZVision 64 KWord Television Controller with OSD

Figure 20 R, G, and B Outputs in Analog (Palette) Mode

## **Closed Caption Data Capture**

Closed-caption text can be decoded directly from the composite video signal using the processor's digital signal processing capabilities and displayed on the screen. The character representation in this mode provides simple attribute control by inserting control characters. Each word of video RAM specifies two displayed characters.

The 4-bit flash A/D converter, with proper clamping, provides the ability to receive the composite video signal directly and process the closed-caption text embedded in the signal. Signal processing can be applied directly to the signal to improve decoder performance.

#### **CGROM** Relocation

CGROM can be placed anywhere in the 64K ROM address space by setting the CGROM address offset register R7(2). This offset is added to the CGROM address before accessing the ROM. By modifying the CGROM offset, several

fonts can be accessed (limited only by ROM size). When reset, R7(2) = 0 (no offset), making the Z90T366 backward-compatible with existing OSD control software.

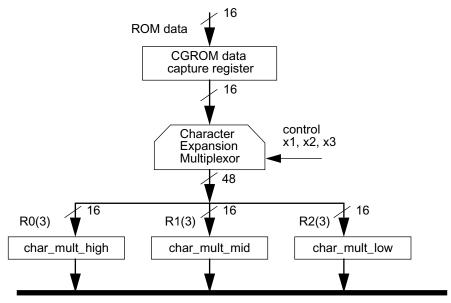

The character scan line from CGROM addressed by the character register is fetched and stored into the CGROM capture register. If a pixel is set to 1, it displays the foreground color. If a pixel is set to 0, it displays the background color. The scan line can be stretched by the character multiplier to be two or three times normal character size by duplicating each bit in the word.

## **Controlling Character Expansion**

The character size can be stretched to two or three times the size of the scan line. Hardware fetches data from CGROM and stretches the data to be read from registers R0(3), R1(3), and R2(3). Figure 21 is a block diagram of the structure of the character expansion multiplexor, and Table 11 lists bit functions.

Processor EXTERNAL bus

Figure 21 Character Expansion

| Capture<br>Register<br>Contents | Char_mult_high   | Char_mult_mid    | Char_mult_low    |

|---------------------------------|------------------|------------------|------------------|

| x1 operation                    | abcdefghijklmnop |                  |                  |

| x2 operation                    | aabbccddeeffgghh | iijjkkllmmnnoopp |                  |

| x3 operation                    | aaabbbcccdddeeef | ffggghhhiiijjjkk | klllmmmnnnoooppp |

#### Table 11 Character Expansion Register

## **Displayed Data Formats**

The Z90T366 hardware supports the following two different data formats:

- OSD mode, R4(3)<d> = 1 supports a standard OSD with full set of features.

- **CCD mode**, **R4(3)**<**d> = 0** supports reduced features which comply with the recommendations of the FCC on Closed Caption support.

In CCD mode, the background color of the characters *cannot* be changed and is always preset to BLACK.

## **OSD Mode**

In OSD mode, each character occupies a 16-bit word in VRAM. There are two possible character formats defined: a "display" character and a "control" character. The code stored in "display" character format defines a character code and up to 7 attributes of the character.