#### Product Features

- Output Frequency up to 125MHz

- Supports Power PC TM, and Pentium TM Processors

- 15 Clock Output: Frequency Configurable

- Two Reference Clock Inputs for Dynamic Toggling

- Output Tri-State Control

- Spread Spectrum Compatible

- 3.3V Power Supply

- Pin Compatible with MPC974

- Industrial Temp. Range: -40°C to +85°C

- 52 Pin TQFP Package

#### **Feedback Ratio Selection Table**

|         | Inputs  | Outputs |        |

|---------|---------|---------|--------|

| VCO_Sel | fselFB0 | fselFB1 | QFB    |

| 0       | 0       | 0       | VCO/8  |

| 0       | 0       | 1       | VCO/12 |

| 0       | 1       | 0       | VCO/16 |

| 0       | 1       | 1       | VCO/24 |

| 1       | 0       | 0       | VCO/16 |

| 1       | 0       | 1       | VCO/24 |

| 1       | 1       | 0       | VCO/32 |

| 1       | 1       | 1       | VCO/48 |

Table 1

### **Product Description**

The Z9974 is a low cost 3.3V zero delay clock driver for high speed signal buffering and redistribution.

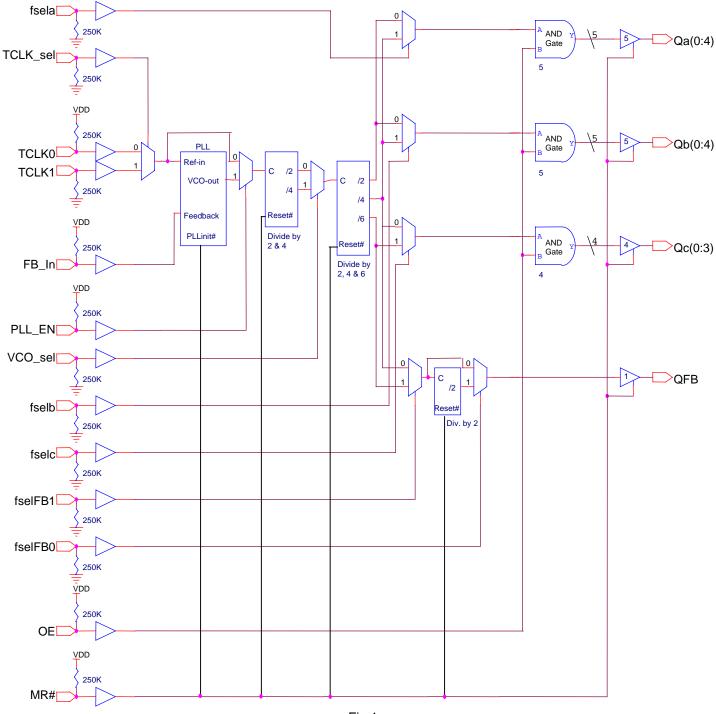

It provides the designer with the flexibility of selecting various Output/Input Frequency ratios selected by fsela, fselb, fselc, fselFB(0:1), and VCO sel input settings.

The Z9974 integrates PLL technology for Zero delay propagation from Input to Output. The PLL feedback is externally available for propagation delay tuning and divide ratio alternatives as per table 1.

The Z9974 has three banks of outputs with independent divider stages. These dividers allow the banks to have different frequencies as per table 2.

TCLK0 and TCLK1 one are selectable input reference clocks and may be toggled dynamically during operation to provide modulation and phase shifting designs.

This device includes a Master Reset signal, which disables the outputs into Tristate (Hi-Z) mode, and reset all internal digital circuitry (excluding the PLL).

An Output Enable, OE, input pin is available for shutting Qa(0:4), Qb(0:4), and Qc(0:3) outputs in a low state. All outputs are held low with input clock turned off.

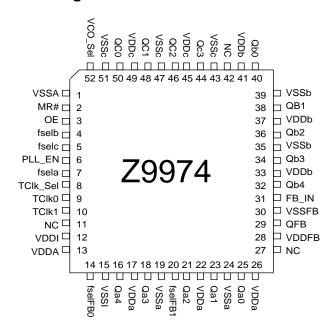

### **Pin Configuration**

## **Block Diagram**

**Output Frequency Selection Table**

|         | Inpu  | ıts   |       | Outputs | <b>;</b> |         |

|---------|-------|-------|-------|---------|----------|---------|

| VCO_sel | fsela | fselb | fselc | Qa(0:4) | Qb(0:4)  | Qc(0:3) |

| 0       | 0     | 0     | 0     | VCO/4   | VCO/4    | VCO/8   |

| 0       | 0     | 0     | 1     | VCO/4   | VCO/4    | VCO/12  |

| 0       | 0     | 1     | 0     | VCO/4   | VCO/8    | VCO/8   |

| 0       | 0     | 1     | 1     | VCO/4   | VCO/8    | VCO/12  |

| 0       | 1     | 0     | 0     | VCO/8   | VCO/4    | VCO/8   |

| 0       | 1     | 0     | 1     | VCO/8   | VCO/4    | VCO/12  |

| 0       | 1     | 1     | 0     | VCO/8   | VCO/8    | VCO/8   |

| 0       | 1     | 1     | 1     | VCO/8   | VCO/8    | VCO/12  |

| 1       | 0     | 0     | 0     | VCO/8   | VCO/8    | VCO/16  |

| 1       | 0     | 0     | 1     | VCO/8   | VCO/8    | VCO/24  |

| 1       | 0     | 1     | 0     | VCO/8   | VCO/16   | VCO/16  |

| 1       | 0     | 1     | 1     | VCO/8   | VCO/16   | VCO/24  |

| 1       | 1     | 0     | 0     | VCO/16  | VCO/8    | VCO/16  |

| 1       | 1     | 0     | 1     | VCO/16  | VCO/8    | VCO/24  |

| 1       | 1     | 1     | 0     | VCO/16  | VCO/16   | VCO/16  |

| 1       | 1     | 1     | 1     | VCO/16  | VCO/16   | VCO/24  |

Table 2

### **PIN DESCRIPTION**

| PIN No.            | Pin Name    | I/O | Description                                                                                                                                                                                                                                                          |

|--------------------|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                  | MR#         | I   | Active low Master Reset pin. It has a $250 \text{K}\Omega$ internal pull-up. When forced low, all outputs are Tri-stated (high impedance) and internal ratio dividers are reset.                                                                                     |

| 3                  | OE          | I   | Active high Output Enable pin. It has a $250K\Omega$ internal pull-up. When forced low, Qa(0:4), Qb(0:4), and Qc(0:3) outputs are stopped in a low state. QFB is not effected by this signal.                                                                        |

| 7,4, 5             | Fsel(a,b,c) | I   | Input select pins for setting the output dividers at Qa(0:4), Qb(0:4), and Qc(0:3) respectively. Each pin has an internal 250K $\Omega$ pull-down. See table 2, page 3.                                                                                              |

| 6                  | PLL_EN      | I   | Input pin for bypassing the PLL. It has an internal $250 \text{K}\Omega$ pull-up. When forced low, the input reference clock (applied at TCLK0, or TCLK1) bypasses the PLL and drives the dividers, typically for device testing. In this case, the PLL is disabled. |

| 8                  | TCLK_sel    | I   | Input pin for selecting TCLK0 or TCLK1 as input reference. When TCLK_sel = 0, TCLK0 is selected, when TCLK_sel = 1, TCLK1 is selected. This pin has a $250K\Omega$ internal pull-down.                                                                               |

| 9,10               | TCLK(0:1)   | I   | Input pins for applying a reference clock to the PLL. The active input is selected by TCLK_sel, pin# 8. TCLK0 has a 250K $\Omega$ internal pull-down. TCLK1 has a 250K $\Omega$ internal pull-up.                                                                    |

| 14, 20             | FselFB(0:1) | I   | Input select pins for setting the Feedback divide ratio at QFB output, pin#29. See table 1, page1. Each of these pins has a $250K\Omega$ internal pull-down.                                                                                                         |

| 25,23,21,<br>18,16 | Qa(0:4)     | 0   | High drive, Low Voltage CMOS, Output clock buffers, Bank Qa. Their divide ratio is programmed by fsela, pin#7.                                                                                                                                                       |

| 29                 | QFB         | 0   | Low Voltage CMOS output feedback clock to the internal PLL. The divide ratio for this output is set by fselFB(0:1). A delay capacitor, or trace may be applied to this pin in order to control the Input Reference/Output Banks phase relationship.                  |

| 31                 | FB_In       | I   | Feedback input pin. Typically connects to the QFB output for accessing the Feedback to the PLL. It has a $250 \mathrm{K}\Omega$ internal pull-up.                                                                                                                    |

#### **PIN DESCRIPTION (Cont.)**

| PIN No.            | Pin Name      | 1/0 | Description                                                                                                                                                                                                                                                                        |  |

|--------------------|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 40,38,36,<br>34,32 | Qb(0:4)       | 0   | High drive, Low Voltage CMOS, Output clock buffers, Bank Qb. Their divide ratio is programmed by fselb, pin#4.                                                                                                                                                                     |  |

| 50,48,46,<br>44    | Qc(0:3)       | 0   | High drive, Low Voltage CMOS, Output clock buffers, Bank Qc. Their divide ratio is programmed by fselc, pin#5.                                                                                                                                                                     |  |

| 52                 | VCO_Sel       | I   | Input select pin for setting the divider of the VCO output. It has a $250 \text{K}\Omega$ internal pull-down. If VCO_sel = 0, then the PLL VCO output is divided by 2. If VCO_sel = 1, then the PLL VCO output is divided by 4. See fig.1, page2; table 1, page1, table 2, page 3. |  |

| 11,27,42           | n/c           | -   | These pins are not connected internally. They may be attached to a ground plane.                                                                                                                                                                                                   |  |

| 12                 | VDDI          | Ρ   | Power for input logic circuitry.                                                                                                                                                                                                                                                   |  |

| 15                 | VSSI          | Ρ   | Ground for input logic circuitry.                                                                                                                                                                                                                                                  |  |

| 13,                | VDDA          | Р   | Power and Ground supply pins for internal Analog circuitry.                                                                                                                                                                                                                        |  |

| 17,22,26           | VDDa          | Р   | 3.3V supply for Qa(0:4) output bank, and fselFB1 input.                                                                                                                                                                                                                            |  |

| 19,24              | VSSa          | Р   | Common ground for Qa(0:4) output bank, and fselFB1 input.                                                                                                                                                                                                                          |  |

| 28, 30             | VDDFB / VSSFB | Р   | Power and ground supply pins for QFB output and FB_In input pins and digital circuitry.                                                                                                                                                                                            |  |

| 33,37,41           | VDDb          | Р   | 3.3V supply for Qb(0:4) output bank.                                                                                                                                                                                                                                               |  |

| 35,39              | VSSb          | Р   | Common ground for Qb(0:4) output bank.                                                                                                                                                                                                                                             |  |

| 45,49              | VDDc          | Р   | 3.3V supply for Qc(0:3) output bank and VCO_sel pin.                                                                                                                                                                                                                               |  |

| 43,47,51           | VSSc          | Р   | Common ground for Qc(0:3) output bank and VCO_sel pin.                                                                                                                                                                                                                             |  |

| 1                  | VSSA          | Р   | Analog Ground                                                                                                                                                                                                                                                                      |  |

A bypass capacitor  $(0.1\mu F)$  should be placed as close as possible to each positive power pin (<0.2"). If these bypass capacitors are not close to the pins their high frequency filtering characteristic will be cancelled by the lead inductances of the traces.

### **Glitch-Free Output Frequency Transitions**

Customarily when zero delay buffers have their internal counter's changed "on the fly' their output clock periods will:

- A. Contain short or "runt" clock periods. These are clock cycles in which the cycle(s) are shorter in period than either the old or new frequency that is being transitioned to.

- B. Contain stretched clock periods. These are clock cycles in which the cycle(s) are longer in period than either the old or new frequency that is being transitioned to.

This device specifically includes logic to guarantee that runt and stretched clock pulses do not occur if the device logic levels of any or all of the following pins changed "on the fly" while it is operating: Fsela, Fselb, Fselc, and VCO\_Sel

### **Maximum Ratings**

Input Voltage Relative to VSS: VSS-0.3V

Input Voltage Relative to VDD: VDD+0.3V

Storage Temperature: -65°C to + 150°C

Operating Temperature: -40°C to +85°C

Maximum Power Supply: 5.5V

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, Vin and Vout should be constrained to the range:

VSS<(Vin or Vout)<VDD

Unused inputs must always be tied to an appropriate logic voltage level (either VSS or VDD).

#### **DC Parameters**

| Characteristic                              | Symbol | Min | Тур | Max  | Units | Conditions                          |  |

|---------------------------------------------|--------|-----|-----|------|-------|-------------------------------------|--|

| Input Low Voltage                           | VIL    | VSS | -   | 0.8  | Vdc   | Applicable to all input signals.    |  |

| Input High Voltage                          | VIH    | 2.0 | -   | VDD  | Vdc   | - Applicable to all imput digitals. |  |

| Input Low Current                           | IIL    |     |     | -100 | μA    |                                     |  |

| Input High Current                          | IIH    |     |     | 100  | μΑ    |                                     |  |

| Output Low Voltage                          | VOL    |     |     | 0.5  | V     | IOL = 20 mA                         |  |

| Output High Voltage                         | VOH    | 2.4 |     |      | V     | IOH = - 20mA                        |  |

| Quiescent Supply Current                    | Idd    | -   | -   | 20   | mA    |                                     |  |

| Input Pin Capacitance                       | Cin    | -   | -   | 8    | pF    | Per input                           |  |

| VDD* =3.3V <u>+</u> 5%, TA = -40°C to +85°C |        |     |     |      |       |                                     |  |

### **PLL AC Parameters**

| Characteristic                        | Symbol     | Min    | Тур | Max    | Units | Conditions                                                      |  |

|---------------------------------------|------------|--------|-----|--------|-------|-----------------------------------------------------------------|--|

| Maximum PLL Lock Time                 | tLOCK      |        |     | 10     | mS    | Stable power supply & valid clocks presented on TCLK(0:1) pins. |  |

| VCO Lock Range                        | fVCO       | 200    |     | 500    | MHz   | FselFB(0:1) = /4 to /12                                         |  |

| TCLK(0:1) input rise / fall time      | Tinr, Tinf |        |     | 3      | nS    |                                                                 |  |

| Input Reference frequency             | fREF       | Note 1 |     | Note 1 | MHz   |                                                                 |  |

| Input Reference duty cycle            | fREFpw     | 25     |     | 75     | %     |                                                                 |  |

| VDD* = 3.3V + 5%. TA = -40°C to +85°C |            |        |     |        |       |                                                                 |  |

Document#: 38-07090 Rev. \*A

Note 1: Input Reference Frequency is limited by the divider selection and the VCO lock range.

#### **AC Parameters**

| Characteristic                               | Symbol          | Min               | Тур                      | Max               | Units | Conditions                     |  |

|----------------------------------------------|-----------------|-------------------|--------------------------|-------------------|-------|--------------------------------|--|

| Output Duty Cycle                            | Tpw             | Tcycle/2<br>- 800 | Tcycle/2<br><u>+</u> 500 | Tcycle/2<br>+ 800 | ps    | Measured @ VDD/2               |  |

| Rise Time / Fall Time                        | $T_{r,}T_{f}$   | 0.15              | -                        | - 1.5 ns N        |       | Measured between 0.8V and 2.0V |  |

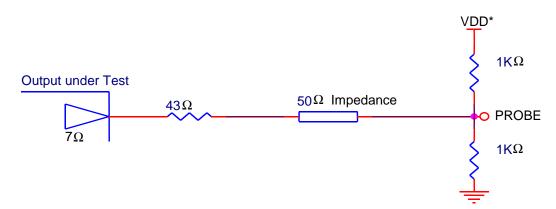

| Output Impedance                             | Z <sub>o</sub>  |                   | 7                        | 10                | Ω     |                                |  |

| Output to Output Skew                        | T <sub>s</sub>  | -                 | -                        | 250               | ps    | All output equally loaded      |  |

| Propagation Delay,<br>TCLK(0:1) to FBIN      | T <sub>pd</sub> | -250              | -                        | 100               | ps    | Measured for 50MHz at VDD/2    |  |

| Cycle to Cycle Jitter                        | tj              | -                 | <u>+</u> 100             | -                 | ps    | Measured for 50 MHz at VDD/2   |  |

| Output Disable Time                          | tPLZ,<br>tPHZ   | 2                 | -                        | 10                | ns    | After MR# goes low             |  |

| Output Enable Time                           | tPZL            | 2                 | -                        | 10                | ns    | After MR# goes High            |  |

| Maximum Output                               | Fout            | -                 | -                        | 125               | MHz   | Q (÷2)                         |  |

| Frequency                                    |                 |                   |                          | 63                |       | Q (÷4)                         |  |

|                                              |                 |                   |                          | 42                |       | Q (÷6)                         |  |

| VDD* = 3.3V <u>+</u> 5%, TA = -40°C to +85°C |                 |                   |                          |                   |       |                                |  |

Note: Parameters are guaranteed by design and characterization. Not 100% tested in production. All parameters specified with loaded outputs. Z9974 outputs can drive series or parallel terminator 50  $\Omega$  (or 50  $\Omega$  to VDD/2).

## **Test Circuit Diagram**

NOTE: All buffer outputs are tied to a common 3.3 Volt VDD (VDD\*) for testing purposes

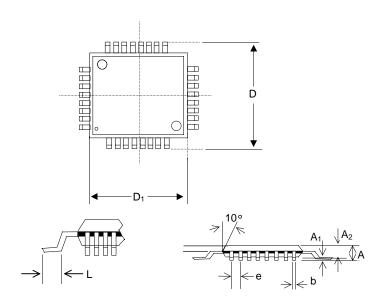

### Package Drawing and Dimensions (52 TQFP)

### **52 Pin TQFP Outline Dimensions**

Document#: 38-07090 Rev. \*A

|                |       | INCHES    |       | MII    | LLIMETE  | RS   |

|----------------|-------|-----------|-------|--------|----------|------|

| SYMBOL         | MIN   | NOM       | MAX   | MIN    | NOM      | MAX  |

| А              | -     | -         | 0.047 | -      | -        | 1.20 |

| A <sub>1</sub> | 0.002 | -         | 0.006 | 0.05   | -        | 0.15 |

| A2             | 0.037 | -         | 0.041 | 0.95   | -        | 1.05 |

| D              | -     | 0.472     | 1     | -      | 12.00    | 1    |

| D <sub>1</sub> | -     | 0.394     | ı     | -      | 10.00    | 1    |

| b              | 0.009 | -         | 0.015 | 0.22 - |          | 0.38 |

| е              |       | 0.026 BS0 |       |        | 0.65 BSC | ;    |

| L              | 0.018 | -         | 0.030 | 0.45   | -        | 0.75 |

| Ordering Information                     |         |                            |  |  |  |

|------------------------------------------|---------|----------------------------|--|--|--|

| Part Number Package Type Production Flow |         |                            |  |  |  |

| Z9974CA                                  | 52 TQFP | Industrial, -40°C to +85°C |  |  |  |

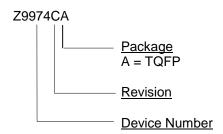

Note: The ordering part number is formed by a combination of device number, device revision, package style, and screening as shown below.

Marking: Example: CYPRESS

Z9974CA

Date Code, Lot #

#### **Notice**

Cypress Semiconductor Corp. reserves the right to make changes to its products in order to improve design, performance or reliability. Cypress Semiconductor Corp. assumes no responsibility for the use of its products in life supporting and medical applications where the failure or malfunction of the product could cause failure of the life supporting and medical systems. Products are not authorized for use in such applications unless a written approval is requested by the manufacturer and an approval is given in writing by Cypress Semiconductor Corp. for the use of its products in the life supporting and medical applications.

|      | <b>Document Title:</b> Z9974 3.3V, 125 MHz Multi-Output Zero Delay Buffer <b>Document Number</b> : 38-07090 |          |     |                                  |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------|----------|-----|----------------------------------|--|--|--|--|

| Rev. | Rev. ECN Issue Orig. of Description of Change                                                               |          |     |                                  |  |  |  |  |

| **   |                                                                                                             |          |     |                                  |  |  |  |  |

| *A   | 108068                                                                                                      | 07/03/01 | NDP | Changed Commercial to Industrial |  |  |  |  |