# D2744/ZAD2754

14-Bit High-Speed A/D Converters

# Solutions for Data Conversion

Analog Solutions' ZAD2744 and ZAD2754 offer premium 14-bit performance for exacting applications. The use of specially selected low temperaturecoefficient thin-film resistors insure that no codes are missing over temperature.

The ZAD2744 and ZAD2754 are the solution to your 14-bit A/D conversion needs.

## General Description

The ZAD2744 and 2754 are high-speed analog-todigital converters packaged in small 2.0"×4.0"×0.4" metal cases. They perform complete 14-bit conversions in 25 µs (ZAD2744) or 100 µs (ZAD2754). Utilizing the exclusive mono-bit ladder network, drift and accuracy problems normally associated with binary-weighted networks are virtually eliminated.

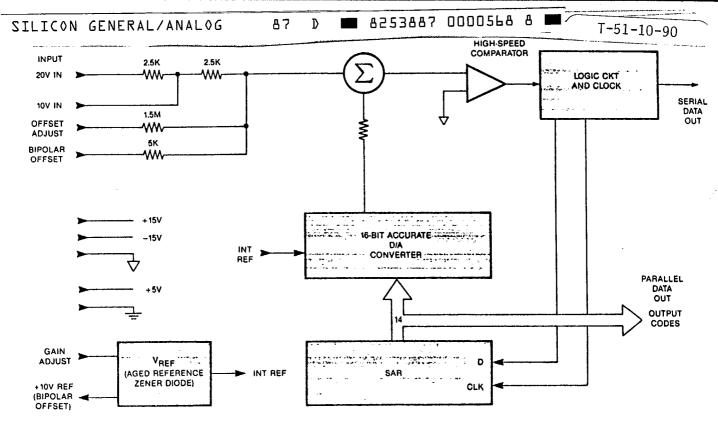

## Description of Converter

The ZAD2744 and 2754 provide premium 14-bit converter performance. Using the successive approximation technique, these units convert analog input voltages into natural binary, offset binary, or two's complement coded outputs. The use of specially selected lowtemperature coefficient thin-film resistors in our proven 16-bit accurate monobit ladder network insures that no codes are missing over temperature.

# **Applications**

- □ Wide Band Data Digitizing

- ☐ Multi-Channel Computer Interface

- ☐ High Accuracy Data Acquisition

- □ Computed Tomography

- □ Seismic Instrumentation

# **Key Features**

- ☐ 14-Bit Resolution and Accuracy

- ☐ Fast 25 μs Conversion Time (ZAD2744)

- □ Low 1 ppm/°C Worst Case Differential Linearity T.C. (ZAD2754)

- User Selectable Input Range

- □ No Missing Codes—Guaranteed

- ☐ Monotonicity—Guaranteed

- □ Low Supply Current

- ☐ Low Cost

- ☐ AD1130 Pin Compatibility with **Enhanced Performance**

The combination of the successive approximation technique and the proven monobit ladder provides up to four times more allowance for component variation and drift than conventional 1, 2, 4, 8, ladder designs.

The converters provide four user-selectable analog input ranges:  $\pm 5V$ ,  $\pm 10V$ , 0 to +10V and 0 to +20V.

# Analog Input Characteristics:

The input circuit of the ZAD2744 and ZAD2754 is shown in figure 3. No offset current is applied to the comparator input because pin 19 is left open circuit when the converter is connected in the unipolar mode.

A 0 to +4mA output current is developed by the 0 to +10V input signal which is applied to pin 6. The +4mA output is compared to the 0 to -4mA output of the internal D/A converter. (The 0 to +20V input signal is applied to pin 5).

The zero point (offset of the converter) can be adjusted by ±40 LSB by applying to pin 20 any voltage between +15V and -15V from the wiper of a 100 kΩ potentiometer (figure 3).

# PERFORMANCE SPECIFICATIONS ZAD2744/ZAD2754 14-BIT HIGH-SPEED A/D CONVERTERS

|                                   | ZAD2744                                | ZAD2754      |                                    | ZAD2744 2                                        | AD275 |

|-----------------------------------|----------------------------------------|--------------|------------------------------------|--------------------------------------------------|-------|

| ANALOG INPUT                      |                                        |              | DIGITAL CONTROLS                   |                                                  |       |

| Full-Scale Range (FSR)            | 0 to +10V, ±5V,<br>0 to +20V, ±10V     | *            | Control Compatibility <sup>4</sup> | TTL, HCMOS<br>logic levels                       | *     |

| Input Impedance                   | 5 kΩ, 2.5 kΩ                           | *            | Trigger (positive pulse):          |                                                  |       |

|                                   |                                        |              | Fan In<br>Width                    | 1 TTL unit load<br>Positive Pulse,               | *     |

| REFERENCE                         |                                        |              |                                    | 200 ns min<br>400 ns max                         |       |

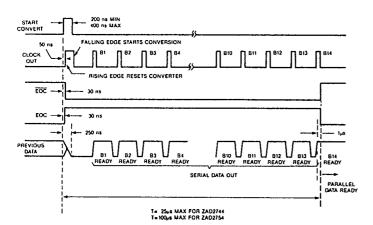

| Reference                         | +10V, 4 mA max.                        | *            |                                    | Rising edge resets registers. Falling            | *     |

| ACCURACY                          | -                                      |              |                                    | edge starts<br>conversion. (Refer                |       |

| Resolution                        | 14 bits                                | *            |                                    | to Timing Diagram)                               |       |

| Quantization Error                | ±0.5 LSB                               | *            |                                    |                                                  |       |

| Relative Accuracy <sup>2</sup>    |                                        |              | DIGITAL OUTPUTS                    |                                                  |       |

| at 25°C                           | ±0.005%                                | ±0.003%      | Compatibility                      | LSTTL                                            | *     |

|                                   | FSR max                                | FSR max      | Parallel Data:                     |                                                  |       |

| 0-50°C                            | ±0.008%                                | ±0.006%      | Fan Out                            | 2 TTL unit loads/line                            | *     |

| Gain Error                        | FSR max<br>±0.05% FSR³ max             | FSR max      | Coding                             | Binary (unipolar)                                | *     |

| Offset Error                      | ±0.05% FSR³ max                        | •            |                                    | Offset binary, (bipolar)                         |       |

| Differential Linearity            | ±0.5 LSB typical                       | -            | Ford of Community (500)            | 2's complement                                   | _     |

| onoroniai Emounty                 | ±0.75 LSB max                          | ±0.5 LSB max | End of Conversion (EOC) Fan Out    | · ·                                              | •     |

| Monotonicity                      | Guaranteed                             | *            | Serial Data                        | 2 TTL unit loads Positive true                   |       |

| Zero Code (0° to 50°C)            | Continuous and monotonic               | *            | Fan Out                            | 2 TTL unit loads                                 | *     |

| Missing Codes                     | through zero No missing codes          | *            | POWER                              |                                                  |       |

|                                   | tto thioding codes                     |              | +15 V ±3%                          | 40 mA typical                                    | *     |

|                                   |                                        |              | -15 V ±3%                          | 40 mA typical                                    |       |

|                                   |                                        |              | + 5 V ±5%                          | 120 mA typical                                   | •     |

| STABILITY                         | ** · · · · · · · · · · · · · · · · · · |              | ENVIRONMENTAL                      |                                                  |       |

| Temperature Coefficient           |                                        |              | Temperature Range:                 |                                                  |       |

| of Differential Linearity         | ±2 ppm                                 | ±1 ppm       | Rated Performance                  | 0°C to 70°C                                      | *     |

| Tomporatura Coofficient           | FSR/°C max                             | FSR/°C max   | Storage                            | -25°C to 85°C                                    | *     |

| Temperature Coefficient of Gain   | ±12 ppm/°C max                         | *            | Relative Humidity                  | 0 to 85% non-condens                             | ing * |

| Temperature Coefficient of Offset | are ppini o max                        |              |                                    | up to 40°C                                       |       |

| Unipolar                          | ±3 ppm FSR/°C m                        | nax *        | MECHANICAL                         |                                                  |       |

| Bipolar                           | ±7 ppm FSR/°C m                        | nax          | Packaging:                         |                                                  |       |

| Power Supply Sensitivity:         |                                        |              | Dimensions                         | 2"×4"×0.4"                                       | * .   |

| Gain and Offset                   | ±0.001% for each<br>% change in powe   |              | Shielding                          | Electromagnetic 5 sides<br>Electrostatic 6 sides | s *   |

| Warm-up Time                      | supply<br>10 minutes                   | *            | Case Potential                     | Analog ground                                    | *     |

| AC CHARACTERISTICS                |                                        |              |                                    |                                                  |       |

| A/D Conversion Time               | 25 μs max                              | 100 µs max   |                                    |                                                  |       |

Same as ZAD2744

### NOTES:

- Specifications typical at 25 °C and rated supply voltage unless otherwise specified.

- Relative accuracy measured by using best-fit straight line.

- 3. Offset and Full Scale Errors are adjustable to Zero by external potentiometers. Adjust Zero at offset adjust FS @ gain adjust.

- 4. Digital input circuit contains HCMOS devices and is guaranteed to be free of "LATCH-UP" conditions.

- 5. Unit contains CMOS devices and should be handled with standard CMOS safety precautions.

Figure 1 · Block Diagram

Figure 2 · Timing Diagram

## Gain and Offset Adjustments

The ZAD2744 and ZAD2754 are factory calibrated to have less than  $\pm 0.05\%$  FSR gain and offset error. External potentiometers may be connected as shown in figure 3 to cancel these errors. Pins 1 and 20 should be left open if external potentiometers are not used.

NOTE - A jumper is connected between PIN 19 and PIN 22 for bipolar operation; PIN 19 must be left open for unipolar operation.

### Offset Adjustment Table

|             | Input<br>PIN | Jumper<br>PIN 19<br>to | Set<br>Input<br>Voltage to | Adjust External<br>Offset Pot at PIN 20<br>Until Output Code is at |

|-------------|--------------|------------------------|----------------------------|--------------------------------------------------------------------|

| 0 to 10V    | 6            | ı                      | +0.0003                    | 00000 to 00001                                                     |

| 0 to 20V    | 5            | _                      | +0.0006                    | 00000 to 00001                                                     |

| -5 to +5V   | 6            | 22                     | -4.9997                    | 00000 to 00001                                                     |

| -10 to +10V | 5            | 22                     | - 9.9994                   | 00000 to 00001                                                     |

### Gain Calibration

For  $\pm 10V$  units, set the input voltage precisely to +9.9982V. For  $\pm 5V$  units set to +4.9991V. Set to +9.9991V for 0 to +10V units and for 0 to +20V units, set to +19.9982V.

Adjust the gain potentiometer until two's complement coded units are nearly switching from 011...10 to 011...11 and binary or offset binary coded units are nearly switching from 11...0 to 11...1.

### Range Selection Table

| Full Scale<br>Input Rg. | Analog<br>Input PIN | Jumper<br>PIN 19 to |

|-------------------------|---------------------|---------------------|

| ±10V                    | 5                   | 22                  |

| 0 to +20V               | 5                   |                     |

| ±5V                     | 6                   | 22                  |

| 0 to +10V               | 6                   | _                   |

Figure 3 - Typical Configuration

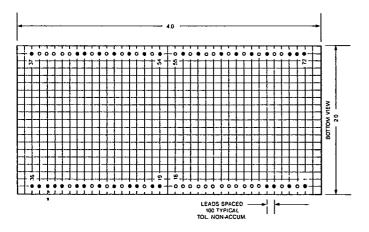

### Physical Outline

Contact the factory for mechanical details.

### Custom Products

We invite customers to take full advantage of our custom design capability to provide the optimum product solution. Please contact our sales department for further information.

#### Ordering Guide

To Order Specify: ZAD2744/ZAD2754 14-Bit High-Speed Sampling A/D Converters

To place your order, contact Analog Solutions

### Pin Connections

| 1.  | GAIN ADJUST     | 37. | SHORT CYCL   |

|-----|-----------------|-----|--------------|

| 3.  | AN GND*         | 43. | EOC          |

| 5.  | AN IN (20V)     | 44. | BIT 14 (LSB) |

| 6.  | AN IN (10V)     | 46. | BIT 13       |

| 19. | BIPOLAR OFFSET  | 48. | BIT 12 ·     |

| 20. | OFFSET ADJUST   | 50. | BIT 11       |

| 22. | +10V REF OUT    | 52. | BIT 10       |

| 23. | AN GND*         | 54. | BIT 9        |

| 25. | -15V            | 56. | BIT 8        |

| 27. | +15V            | 58. | BIT 7        |

| 29. | +5V             | 61. | BIT 6        |

| 30. | DIG. GND        | 63. | BIT 5        |

| 32. | SERIAL OUT      | 65. | BIT 4        |

| 33. | EOC             | 67. | BIT 3        |

| 34. | CONVERT COMMAND | 70. | MSB          |

| 35. | CLOCK IN        | 71. | BIT 2        |

| 36. | CLOCK OUT       | 72. | BIT 1 (MSB)  |

|     |                 |     |              |

\* NOTE: PIN 3 and PIN 23 must both be connected to analog gnd.

SHORT CYCLE CONDITIONS - When the A/D operates at 14-Bit resolution, leave PIN 37 open: If it is to perform conversions of less than 14-Bits, connect PIN 37 to the N+1-Bit output.

CLOCK - For Internal Clock, jumper PIN 35 to PIN 36. When External Clock is used, connect clock to PIN 35. Synchronize start convert with External Clock.

#### Additional Products from Analog Solutions

Precision A/D and D/A Converters

Precision 16-bit and 18-bit D/A Converters

High-Performance Sample/Hold Amplifiers

Logarithmic, Isolation and Special-Purpose Amplifiers

High-Speed Telecommunications A/D and D/A Systems

Precision Load Cell and Strain-Gage Sub-Systems

High Speed Industrial Control Interfaces

3M 9/86 Data subject to change without notice.

### Analog Solutions

940 Detroit Avenue, Concord, California 94518 Telephone: 415-686-6660 Telex: 284238 ANSOL UR

Fax: 415-671-2374

European Sales Office London, England Telephone: 0372-377779

Telex: 897628 Fax: (0372)376848