T-51-09-08

# **ZN438E/J** 8-BIT MICROPROCESSOR COMPATIBLE D-A CONVERTER

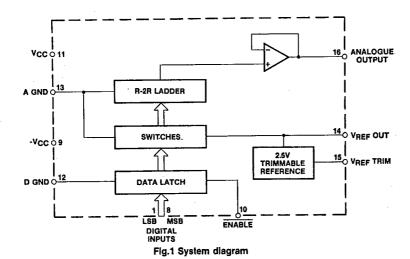

The ZN438 is a monolithic 8-bit D-A converter with input latches to facilitate updating from a data bus and a buffer amplifier to give a low analogue output impedance. The latch is transparent when ENABLE is low and the data is held when ENABLE is taken high.

The ZN438 also contains a trimmable 2.5V reference which is internally connected to the R-2R ladder switches and to VREF OUT.

#### **FEATURES**

- On-Chip High Speed Output Buffer Amplifier

- 1.25 microseconds Settling Time to ±0.5 LSB

- Trimmable Bandgap Reference

- Microprocessor, TTL and 5V CMOS Compatible

- Guaranteed Monotonicity over the Full Operating Temperature Range

- Commercial and Military Temperature Ranges

#### 16 TANALOGUE OUTPUT VALE OUT DBs 14 VALE TRIM DB2 [ 13 AMALOGUE GROUND DB<sub>3</sub>[ 12 DIGITAL GROUND DB4 [ D8s [ 10 ENABLE nre f (MSB) ZN438E (DP16) ZN438J (DC16)

Pin connections (top view)

#### **ORDERING INFORMATION**

| Device type | Operating temperature | Package |  |  |

|-------------|-----------------------|---------|--|--|

| ZN438E      | 0°C to +70°C          | DP16    |  |  |

| ZN438J      | -55°C to +125°C       | DC16    |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

Supply voltage +Vcc Supply voltage -Vcc +77 -9V Logic input voltage Operating temperature range 0°C to +70°C (ZN438E) -55°C to +125°C (ZN438J) -55°C to +125°C Storage temperature range ±200mV Analogue ground to digital ground

229

**ELECTRICAL CHARACTERISTICS** (at  $+V_{CC} = 5V$ ,  $-V_{CC} = -5V$ ,  $T_{amb} = 25$  °C with internal reference unless otherwise stated).

| uniess otherwise stated).         |                           |          |                            |      |       | <del></del> | T-51-09-08                                               |

|-----------------------------------|---------------------------|----------|----------------------------|------|-------|-------------|----------------------------------------------------------|

| Parameter***                      | T <sub>amb</sub> = + 25°C |          | Over specified temp. range |      | Units | Conditions  |                                                          |

|                                   | Min.                      | Тур.     | Max.                       | Min. | Max.  |             |                                                          |

| D-A converter                     |                           |          |                            |      |       |             |                                                          |

| Resolution                        | 8                         | _        | _                          | 8    | _     | Bits        |                                                          |

| Accuracy                          | . 8                       | -        | _                          | 8    | _     | Bits        |                                                          |

| Linearity error                   | _                         | _        | ±0.5                       | _    | ±0.5  | LSB         | ·                                                        |

| Differential linearity error      | -                         | ±0.5     | -                          | -    | ± 1   | LSB         |                                                          |

| Linearity error T.C.              | -                         | ±3       | _                          | _    | _     | ppm/°C      |                                                          |

| Differential linearity error T.C. | -                         | ±6       | _                          | _    | -     | ppm/°C      |                                                          |

| Offset error                      | -                         | 2        | 8                          | -    | 10    | mV          |                                                          |

| Offset error T.C.                 | _                         | ±8       | _                          | _    | -     | μV/°C       |                                                          |

| Gain error                        |                           | -        | ± 0.5                      | -    | _     | LSB         | ງ With V <sub>REF</sub> =                                |

| Gain T.C.                         | _                         | 60       | -                          | _    | 150   | ppm/°C      | } 2.50V See note 1                                       |

| Analogue output voltage           | 0                         | _        | + 2.7                      | 0    | + 2.7 | v           | Note 2                                                   |

| Current                           | -3                        | <b> </b> | +4                         | -3   | +4    | mA          | $V_{out} = 0$ to $V_{ref}$                               |

| Analogue output impedance         | -                         | 6        | 10                         | -    | -     | Ω           |                                                          |

| Settling time to 0.5LSB           |                           |          |                            |      |       |             | $V_{REF} = 2.50V$ $C_{LOAD} = 470pF$ $R_{L} = 690\Omega$ |

|                                   | -                         | 1.25     | -                          | -    | -     | μs          | 1LSB major<br>transition                                 |

|                                   | -                         | 2        |                            | -    | -     | μs          | All bits ON to all bits OFF                              |

|                                   | -                         | 2        | _                          | -    | -     | μs          | All bits OFF to all bits ON                              |

#### NOTE 1

For operation below  $-\,50\,^{\rm o}$  C the full-scale temperature coefficient may become significantly worse if  $V_{CC}$  is allowed to fall below 5V.

#### Note 2

In some cases the reference may be trimmed to give  $A_{out}$  greater than 2.7V. However, this should be avoided because the  $A_{out}$  may not be 8 bit accurate at voltages above this.

# ELECTRICAL CHARACTERISTICS (Cont.)

PLESSEY SEMICONDUCTORS

T-51-09-08

| [=J1-03-00                         |                         |            |                            |      |       |                       |                                                  |

|------------------------------------|-------------------------|------------|----------------------------|------|-------|-----------------------|--------------------------------------------------|

| Parameter                          | $T_{amb} = +25$ °C $te$ |            | Over specified temp. range |      | Units | Conditions            |                                                  |

|                                    | Min.                    | Тур.       | Max.                       | Min. | Max.  |                       |                                                  |

| Internal voltage reference         |                         |            |                            |      |       |                       |                                                  |

| Output voltage                     | 2.450                   | 2.500      | 2.550                      | -    | -     | V                     | $R_L = 1.5K\Omega$ $C_L = 100nF$                 |

| Maximum trim range                 | -                       | <u>±</u> 5 | _                          | _    | -     | % of V <sub>ref</sub> | $R_{TRIM} = 10K\Omega$                           |

| Output voltage T.C.                | -                       | 30         | 100                        | _    | -     | ppm/°C                |                                                  |

| Reference current                  | 1                       | -          | 5                          | 1    | 5     | mA                    |                                                  |

| Slope resistance                   | -                       | 0.75       | 2                          | -    | -     | Ω                     |                                                  |

| Digital inputs                     |                         |            |                            |      |       | ,                     |                                                  |

| High level input voltage           | 2                       | _          | _                          | -    | _     | V                     |                                                  |

| Low level input voltage            | _                       | _          | 8,0                        | _ '  | _     | v                     |                                                  |

| High level input current           | _                       | -          | 60                         | -    | -     | μΑ                    | $V_{in} = 5.5V$<br>$V_{CC} = Max.$               |

| High level input current           | _                       | _          | 20                         | -    | -     | μΑ                    | $V_{in} = 2.4V$<br>$V_{CC} = Max.$               |

| Low level input current            | _                       | _          | – 5μΑ                      | _    | -     | μΑ                    | V <sub>in</sub> = 0.4V<br>V <sub>CC</sub> = Max. |

| Input clamp diode voltage          | _                       | - 1.5      | _                          | _    | -     | V                     | I <sub>in</sub> = -8mA                           |

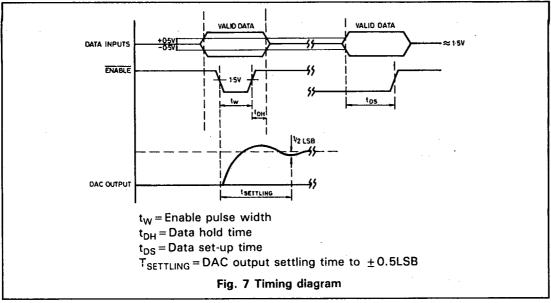

| Enable pulse width t <sub>W</sub>  | 100                     | _          | -                          | -    | _     | ns                    | ]                                                |

| Data set up time t <sub>DS</sub>   | 150                     | _          | -                          | -    | _     | ns                    | Refer to Fig. 7                                  |

| Data hold time t <sub>DH</sub>     | 10                      | _          | -                          | -    | -     | ns                    | IJ                                               |

| Power supplies                     |                         |            |                            | 1    |       |                       |                                                  |

| Supply voltage (+V <sub>CC</sub> ) | 4.5                     | 5          | 5.5                        | 4.5  | 5.5   | V                     |                                                  |

| Supply voltage (-V <sub>CC</sub> ) | -4.5                    | -5         | -5.5                       | -4.5 | - 5.5 | V                     |                                                  |

| Supply current (+1 <sub>CC</sub> ) | -                       | 35         | -                          | -    | -     | mA                    |                                                  |

| Supply current (-I <sub>CC</sub> ) | -                       | 12         | -                          | -    | -     | mA                    |                                                  |

| Power consumption                  | -                       | 235        | -                          | _    | _     | mW                    |                                                  |

data latch.

#### **D-A CONVERTER**

T-51-09-08

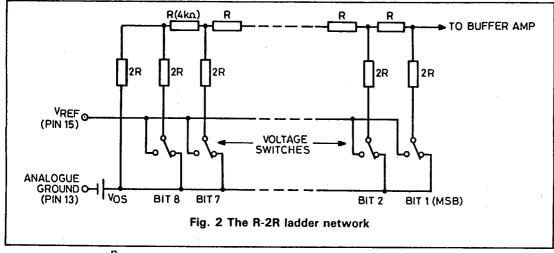

The converter is of the voltage switching type and uses an R-2R ladder network as shown in Fig. 2. Each 2R element is connected to OV or  $V_{REF\ IN}$  by transistor voltage switches specially designed for low offset voltage (<1mV). A binary weighted voltage is produced at the output of the R-2R ladder.

D-A output =

$$\frac{n}{256} (V_{REF IN} - V_{OS}) + V_{OS}$$

where n is the digital input to the D-A from the

Vos is a small offset voltage produced by the D-A switch currents flowing through the package lead resistance. The value of Vos is typically 1mV. This offset will normally be removed by the setting up procedure.

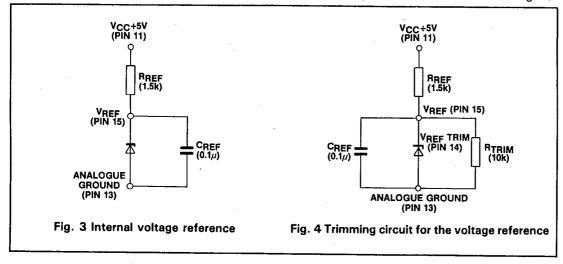

#### REFERENCE

The internal reference is an active bandgap circuit which is equivalent to a 2.5V Zener diode with a very low slope impedance (Fig. 3). A resistor (R<sub>REF</sub>) should be connected between +V<sub>CC</sub> (pin 11) and pin 15. The recommended value of 1K5 will supply a nominal reference current of (5-2.5)/1500 = 1.7mA. A stabilising decoupling capacitor  $C_{REF} = 0.1 \mu F$  is required between pins 15 and 13.

The reference voltage can be trimmed by  $\pm 5\%$ with a 10K potentiometer (as shown in Fig. 4).

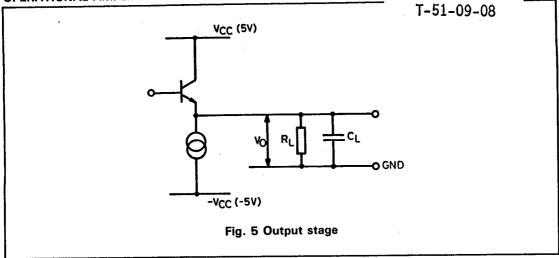

## **OPERATIONAL AMPLIFIER SECTION**

The D-A converter output is buffered by a unity gain, non-inverting amplifier with negligible offset error. Typically this buffer amplifier will develop 2.50V across an external load, and can drive capacitive loads of up to 470pF without a degredation of speed. The amplifier output can source 4mA and sink 3mA. The output stage of this amplifier consists of a bipolar transistor from the  $V_{CC}$  line and a current load to  $-V_{CC}$  (the negative supply for the output amplifier). This output stage is shown in Fig. 5.

The power supply voltages can be increased, resulting in an improved performance in some parameters e.g. switching speed.

#### **LOGIC**

Input coding is binary for unipolar operation and offset binary for bipolar operation. When the enable input is low the data inputs drive the D-A directly. When enable goes high the input data word is held in the data latch.

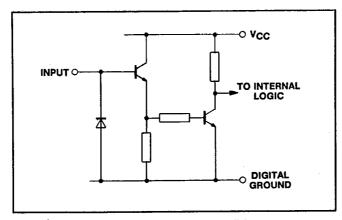

The equivalent circuit for the data and clock inputs is shown in Fig. 6.

The ZN438 is provided with seperate analogue and digital ground connections. The circuit will operate correctly with as much as ± 200mV between the two grounds.

Fig. 6 Equivalent circuit of all inputs

#### **TIMING AND CONTROL**

The ZN438 has input data latches to simplify connection to a microprocessor data bus. The enable control line is used to control the condition of the latches. If enable is low the latches become transparent and the D-A converter responds to the digital inputs. If enable is taken high then the latches retain the data

T-51-09-08

which was present on the digital inputs just prior to enable assuming a high state. While enable is high the analogue output remains at the value corresponding to the data held in the latches.

The function table is given in table 1 below.

| Input data | Enable | Latch output  | Latch condition |

|------------|--------|---------------|-----------------|

| 0          | 0      | 0             | Transparent     |

| 1          | 0      | 1             | Transparent     |

| 0          | J      | 0             | Latching        |

| 1          | 7      | 1             | Latching        |

| ×          | 1      | Previous data | Latched         |

X = Don't care

$\int$  = Low to high level transition

Table 1 ZN438 control logic function table

### **GROUNDING**

AC or transient voltages between analogue ground (pin 13) and digital ground (pin 12) can cause noise at the analogue output (pin 16). Digital systems are a source of noise which can be removed by connecting AGND and DGND

together at the ZN438 or as close as possible to it. It is important that the voltage difference between AGND and DGND should not exceed 200mV.

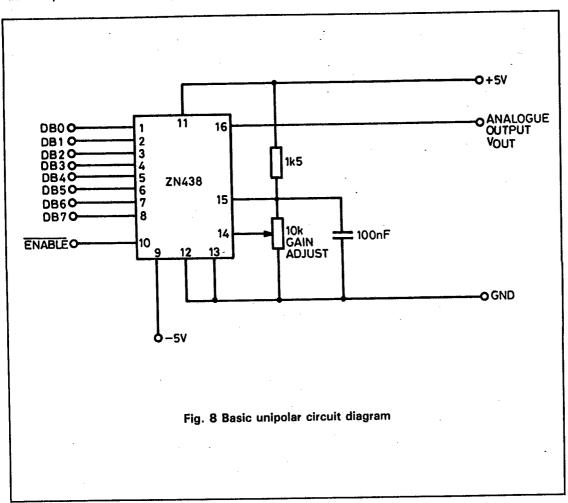

## (1) UNIPOLAR OPERATION

The nominal output range of the ZN438 is OV to  $(V_{REF}-1LSB)$  where  $V_{REF}$  is typically 2.50V. A circuit diagram showing the minimum external components required to give this output range is shown in Fig. 8. The reference trim input is used to provide the necessary gain adjustment

T-51-09-08

by allowing variations of the internal reference voltage by  $\pm 5\%$ .

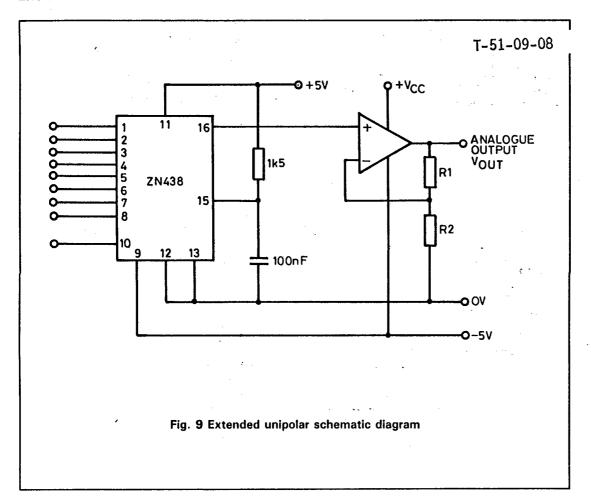

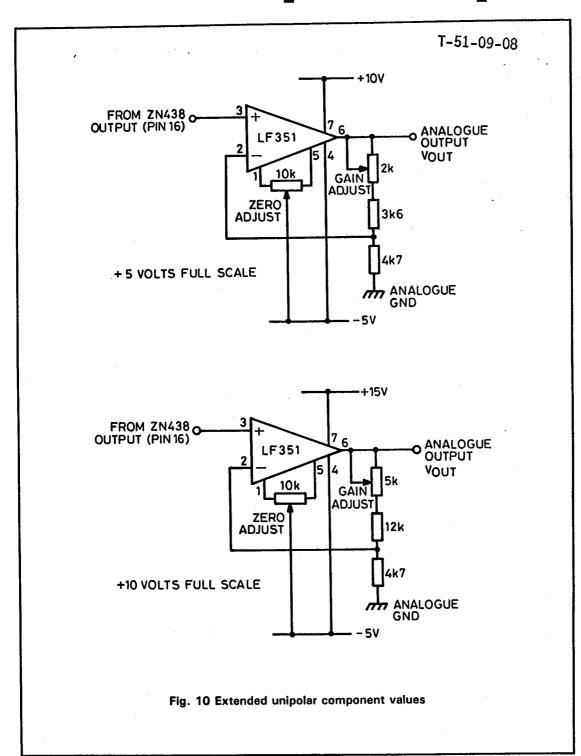

For unipolar output ranges greater than 2.50V an external amplifier is required. A general schematic diagram is shown in Fig. 9.

The full-scale range of Fig. 9 is given by the equation:

$$V_{OUT FS} = \left(1 + \frac{R_1}{R_2}\right) (V_{REF} - 1LSB)$$

$$= G.(V_{REF} - 1LSB)$$

The circuit diagrams of Fig. 10 give typical component values for full-scale outputs of +5 and + 10V. Zero offset adjustment is provided by use of the op-amp offset null capability. Gain adjustment is made by varying the value of R1.

The LF351 is a low cost JFET operational amplifier pin compatible with the industry standard 741. It features a high slew rate of 13  $V/\mu s$  which gives a typical settling time for all bits on to all bits off (or vice versa) of  $2\mu$ s for a 10V full-scale output. If a fast settling time is not required a 741 could be used as a direct replacement for the LF351. This would result in a typical settling time of 20µs for the conditions quoted above.

It can be seen from the gain equation that it is the relative and not the absolute value of the feedback resistors that is important. The values given here have been chosen to give minimum ringing on the output of the LF351 op-amp. As with all fast slew rate op-amps this can be a problem due to the minimal internal compensation used to achieve the fast slew rate. With lower slew rate amplifiers this will not be as much of a problem and hence the value of the feedback components could be increased if desired.

It should be noted that the  $V_{\text{REF}}$  trim potentiometer is no longer required as the gain adjustment is now provided by varying the opamp feedback resistor R1.

## Unipolar adjustment procedure

T-51-09-08

- Set all bits to OFF (low) with enable low and adjust zero until  $V_{OUT} = 0.0000V$ . (Not applicable to Fig. 8 as no offset adjustment is available)

- Set all bits ON (high) and adjust gain until  $V_{OUT} = FS - 1LSB.$

## Unipolar setting up points

| Output range, +FS | LSB    | FS - 1LSB |

|-------------------|--------|-----------|

| + 2.50V           | 9.8mV  | 2.4902V   |

| + 5V              | 19.5mV | 4.9805V   |

| + 10V             | 39.1mV | 9.9609V   |

$$1LSB = \frac{FS}{256}$$

#### Unipolar logic coding

| Input code<br>(Binary)                                 | Analogue output<br>(Nominal value)                                                               |  |  |  |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|

| 1111111<br>11111110<br>11000000<br>10000001<br>1000000 | FS - 1LSB<br>FS - 2LSB<br>0.75FS<br>0.5FS + 1LSB<br>0.5FS<br>0.5FS - 1LSB<br>0.25FS<br>1LSB<br>0 |  |  |  |

| 00000000                                               | 0                                                                                                |  |  |  |

#### (2) BIPOLAR OPERATION

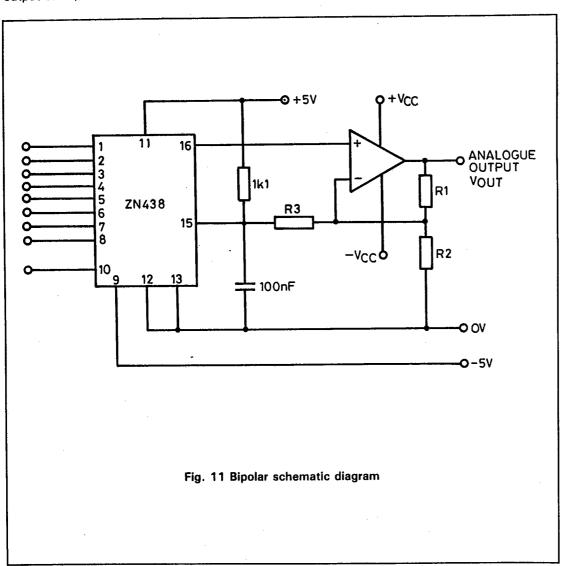

For bipolar operation the output from the ZN438 is offset by half full-scale by connecting a resistor between  $V_{\text{REF}}$  out and the inverting input of the external amplifier. A general schematic diagram is shown in Fig. 11.

When the digital input to the ZN438 is zero its analogue output will be zero resulting in an output of -full-scale from the external amplifier. An input of all ones will give a ZN438 output of + (V<sub>REF</sub> -1LSB) and a resulting amplifier output of + (full-scale - 1LSB).

T-51-09-08

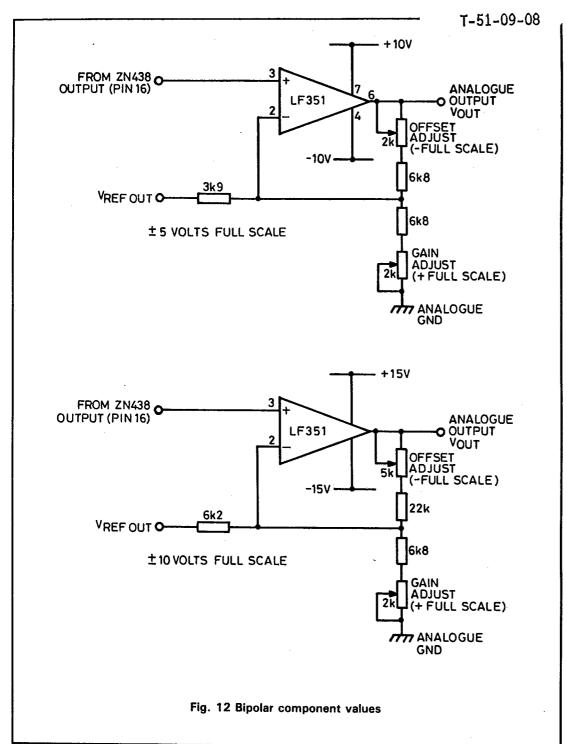

Practical circuit diagrams are given in Fig. 12 with typical component values for full-scale ranges of  $\pm 5$  and  $\pm 10$ V. Note, the  $V_{REF}$ dropper resistor has been reduced from 1K5 to 1K1 to supply the amplifier feedback resistor current. Minus full-scale (offset) is set by adjusting R1 about its nominal value relative to R3. Plus full-scale (gain) is set by adjusting R2 relative to R1.

A bipolar output range of  $\pm V_{REF}$  (which corresponds to the basic unipolar range 0 to  $V_{REF}$ ) is obtained if  $R_1=R_3=3K9$  and  $R_2=\infty$ .

## Bipolar adjustment procedure

PLESSEY SEMICONDUCTORS

- Set all bits to OFF (low) with enable low and adjust offset until the amplifier output reads - full-scale.

- Set all bits ON (high) and adjust gain until the amplifier output reads + (full-scale 1LSB).

T-51-09-08

#### Bipolar setting up points

| Output range, ±FS | LSB    | -FS        | +FS - 1LSB |

|-------------------|--------|------------|------------|

| ± 2.50V           | 19.5mV | - 2.5000V  | + 2.4805V  |

| ± 5V              | 39.1mV | -5.0000V   | +4.9609V   |

| ± 10V             | 78.1mV | - 10.0000V | +9.9219V   |

$1LSB = \frac{2FS}{256}$

### **Bipolar logic coding**

| Input code<br>(Offset binary)                         | Analogue output<br>(Nominal value)                                                                     |  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| 1111111<br>1111110<br>11000000<br>10000001<br>1000000 | + (FS - 1LSB)<br>+ (FS - 2LSB)<br>+ 0.5FS<br>+ 1LSB<br>0<br>- 1LSB<br>- 0.5FS<br>- (FS - 1LSB)<br>- FS |  |