#### **PRELMINARY**

# **Motion JPEG Controller**

#### **Features**

- Implements the control logic for a robust, low-cost motion JPEG compression and expansion system for video capture boards, based on the ZR36050 JPEG Image Compression Processor

- Two speed grades available: 21 MHz, 29.5 MHz

- Performs real-time JPEG compression or expansion of NTSC and PAL square pixel or CCIR video formats in the following resolutions:

- Full resolution

- Half resolution with vertical decimation

- Half resolution with horizontal decimation

- Quarter resolution

- User defined active video area, enables compression of a cropped region of the input video

- In expansion, supports internal or external video synchronization

- Supports fast still-image compression and expansion for video editing

- Implements one-pass compression with the ZR36050's exclusive bit rate control feature. Automatically keeps the compressed data rate virtually constant

- In compression, interfaces directly to the digital video and sync outputs of a YUV 4:2:2 digital video format decoder (e.g., the Philips SAA7110 for square pixel, the SAA7111 for CCIR format or any other compatible decoder or digital video source)

- In expansion, outputs the same YUV 4:2:2 video format, and interfaces directly to the digital video and sync input of common video overlay controllers, such as the Trident PCView+, MCT MVM121/MVP131, AuraVision VxP500/501, and common digital video encoders such as the Fuji MD0207, Philips SAA7188 and SAA7199, and others

- I/O-mapped ISA bus interface to strip buffer, code buffer and control registers

- Software support includes a Windows DLL and sample Video for Windows Capture and Codec drivers

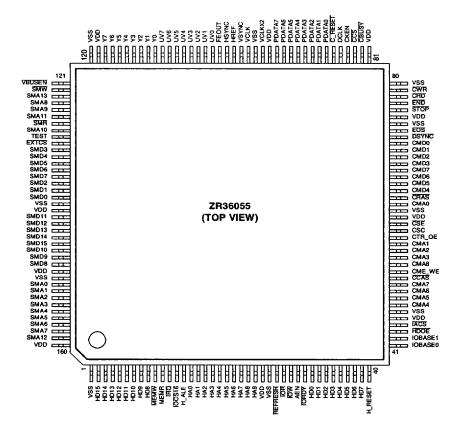

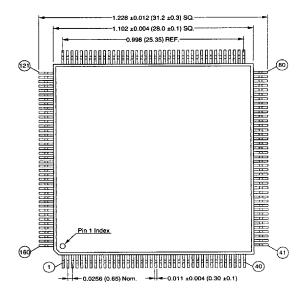

- 160-pin PQFP package

- Low-power CMOS, 5V

# **Applications**

- Full-motion video capture and playback on personal computers

- Video conferencing over local area and wide area networks

- Security systems

- Digital VCR

- Low-cost video editing systems

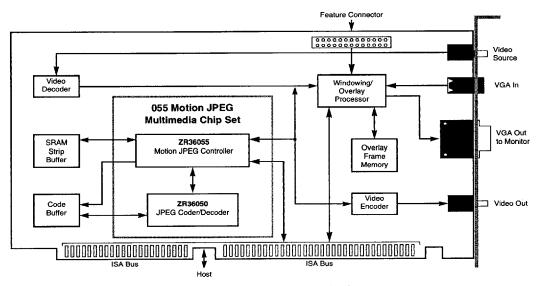

Figure 1. Typical PC Video System Block Diagram

#### INTRODUCTION

The ZR36055 Motion JPEG Controller integrates the control logic for the ZR36050 JPEG Processor, needed to implement a low-cost, low-parts-count motion JPEG capture and playback subsystem on the PC. A ZR36050 and ZR36055, together with the associated memory for strip buffers and code buffers, is known as the "055 subsystem." This subsystem adds a highly effective compression capability to a video capture board, by significantly increasing the image resolution and frame rate that can be supported in a typical PC system. A system based on the 055 Motion JPEG Multimedia Chip Set (ZR36050+ZR36055; for brevity, the "055 Chip Set") supports the YUV 4:2:2 digital video data format of the Philips SAA7110, SAA7111 or compatible live video decoders. In addition, for compatibility with a previous Zoran product, the 045 Motion JPEG Multimedia Chip Set, it supports expansion of motion JPEG images compressed using YUV 4:1:1 subsampling. An 055 Chip Set-based system performs real-time JPEG compression and expansion at up to the full resolution of PAL and NTSC digital video standards, for both CCIR and square pixel formats. In addition, the 055 Chip Set supports high speed still image compression and expansion in compliance with the JPEG baseline standard.

The 055 Chip Set makes use of a unique and patented feature built into the ZR36050 JPEG Image Compression Processor: Zoran Bit Rate Control. With this feature, a nearly constant bit rate is maintained along the video sequence with only small variations around the desired bit rate. In the worst case situation of a scene cut, i.e., when there is an abrupt change in the statistics of the sequence, the 055 Chip Set indicates that such an event occurred, enabling the control software to drop a field if necessary, and conceal the anomaly by duplicating the previous field. Only one field must be duplicated, thus ensuring continuity of the video.

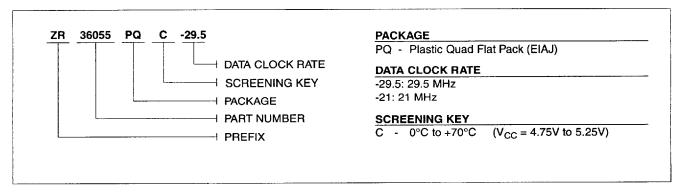

There are two versions of the ZR36055: the ZR36055-21 and the ZR36055-29.5. The ZR36055-21 with ZR36050-21 comprise the "Low-End" 055 Chip Set or, with associated memory, "Low-End" 055 subsystem, which supports half resolution with horizontal decimation and quarter resolution. The ZR36055-29.5 with ZR36050-29.5 comprise the "High-End" 055 Chip Set or, with associated memory, "High-End" 055 subsystem, which supports all the resolutions (See Table 2).

Note that the -21 designation of the ZR36055-21 only signifies that it is intended to be used in conjunction with the ZR36050-21; it does not indicate the master clock frequency rating of the

ZR36055. The ZR36055 in both the Low End and the High End chip sets operates with the same master clock frequency, of twice the video pixel frequency. The difference between them is that the ZR36055-21 is rated to operate only in the SLOW mode (see the description of Command Register 0 on page 10), whereas the ZR36055-29.5 is rated to operate in both the FAST and SLOW modes. Only the SLOW mode is suitable for use with the ZR36050-21.

A block diagram of a typical multimedia add-in board for video display, capture and playback employing the 055 Chip Set is shown in Figure 1. Analog video (PAL or NTSC) from a video source (camcorder, VCR or any other video source) is input to a video decoder. The digital video from the video decoder is transferred simultaneously to the windowing/overlay device and the video encoder for display, and to the ZR36055 for compression. The ZR36055 then performs, when required, horizontal decimation followed by raster to block conversion. Next, YUV blocks are routed to the ZR36050 where each 8x8 sample block is compressed according to the JPEG baseline algorithm, yielding the coded image. The compressed JPEG data is subsequently stored in the code buffer, from where it is read by the ZR36055 and transferred across the ISA bus to the system memory and from there to the hard disk. Repetition at 50/60 fields (25/30 frames) per second yields full motion real time video capture capability. The parameters needed for compression of the next field are automatically updated by the ZR36050 after the completion of the current field, thus controlling the bit rate of the compressed video sequence.

For motion video playback, the inverse operation is performed, with the expanded image being routed to the windowing/overlay processor for display on the PC monitor. Simultaneously, the expanded image may be routed to a video encoder for recording by a VCR or for display on a video monitor.

For still image compression, the image is input to the ZR36055 through the ISA bus in block order: the control software must perform color space conversion, if needed, and the raster to block operation. The ZR36055 transfers these blocks to the ZR36050 which performs the JPEG baseline compression, yielding the coded image. The compressed JPEG bit stream is stored in the code buffer, from where it is transferred by the host software across the ISA bus to the system memory. For still image expansion, the inverse operation is performed by the 055 Chip Set and the control software.

#### **FUNCTIONAL OVERVIEW**

The ZR36055 Motion JPEG controller performs the following functions:

- Interfacing to a YUV 4:2:2 format digital video decoder (e.g., Philips SAA7110 or SAA7111).

- Interfacing to a standard overlay processor (e.g., devices supplied by Trident, MCT, Auravision, or compatible), and standard video encoder (e.g., Fuji MD0207, Philips SAA7199 or SAA7188).

- · Interfacing to a standard ISA bus

- Interfacing to an external VRAM (the "code buffer," for compressed data)

- Interfacing to an external SRAM (the "strip buffer," for pixel data)

- Control of the ZR36050 JPEG Image Compression Processor

- Raster to block and block to raster conversions of YUV 4:2:2 digital video.

- Optional video sync generation, in expansion, for display devices (e.g., video encoders and overlay processors)

- Raster to raster conversion, enabling support for fast still compression and expansion (with appropriate software support)

- Horizontal decimation, with optional filtering, of the input image

- Horizontal interpolation, with optional filtering, of the reconstructed image

- Vertical interpolation of the reconstructed image, by field duplication

- Conversion of YUV 4:1:1 format reconstructed pictures into YUV 4:2:2 format digital video, in order to support YUV 4:1:1 playback (for compatibility with a previous Zoran product, the 045 Chip Set)

The ZR36055 supports (i.e., accepts in compression and outputs in expansion) digital video in CCIR 601 or square pixel formats, following either NTSC or PAL video standard. The parameters of these formats are summarized in the following table:

Table 1: Formats Supported by the ZR36055

| Pixel format | Video<br>standard | Pixei Rate  | Image size | Frame rate |

|--------------|-------------------|-------------|------------|------------|

| CCIR         | PAL               | 13.5 MHz    | 720x576    | 25 fr/sec. |

|              | NTSC              | 13.5 MHz    | 720x480    | 30 fr/sec. |

| Square       | PAL               | 14.75 MHz   | 768x576    | 25 fr/sec. |

| Pixel        | NTSC              | 12.2727 MHz | 640x480    | 30 fr/sec. |

For each of the above mentioned formats, the 055 Chip Set can be configured to compress or expand the following resolutions:

Table 2: Resolutions Supported by the ZR36055

|                 | CCIR601   |           | Square Pixel |           |

|-----------------|-----------|-----------|--------------|-----------|

| Resolution      | PAL       | NTSC      | PAL          | NTSC      |

| Full            | 720 x 576 | 720 x 480 | 768 x 576    | 640 x 480 |

| Half Horizontal | 360 x 576 | 360 x 480 | 384 x 576    | 320x 480  |

| Half Vertical   | 720 x 288 | 720 x 240 | 768 x 288    | 640 x 240 |

| Quarter         | 360 x 288 | 360 x 240 | 384 x 288    | 320 x 240 |

When performing horizontal decimation or interpolation, in the Half Horizontal and Quarter resolution modes, the ZR36055 supports optional filtering.

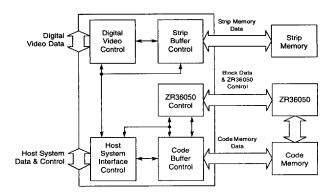

Figure 2 depicts the ZR36055 functional block diagram.

Figure 2. Conceptual Block Diagram of ZR36055 Including Major External Components of an 055 Subsystem

The ZR36055 can be conceptually partitioned into five major functional blocks:

- · Digital Video Control

- · Strip Buffer Control

- ZR36050 Control

- Code Buffer Memory Control

- · Host System Interface Control

#### **Digital Video Control**

The Digital Video Control block is responsible for controlling the flow of data on the Digital Video interface, and generating timing and control signals for other modules based on the incoming clocks and syncs from the video decoder. In compression, it detects the incoming vertical and horizontal sync signals and provides the appropriate timing information to the Strip Buffer Control module. In expansion, when the optional internal sync mode is used, it acts as a vertical and horizontal sync signal generator, whereas in external sync mode, the ZR36055 outputs the digital video in synchronization with the sync signals of an external source. Other tasks performed by the module are conversion to and from the time multiplexed chrominance data format, and horizontal decimation and interpolation of the video, with optional filtering.

#### **Strip Buffer Control**

The Strip Buffer Control block manages the strip buffer SRAM memory, which stores two strips (one strip = 8 lines) of the image for the raster to block conversion. By suitably addressing the strip memory, the strip buffer memory control performs the conversions between raster and block data organization, as required for JPEG compression and expansion. For still compression and expansion a raster to raster mechanism is implemented. Thus, for still compression or expansion the raster to block operation must be done in software.

#### ZR36050 Control

The ZR36050 Control block implements the control signals and handshake required by the ZR36050. It also controls the flow of coded (compressed) data between the ZR36050 and the code buffer.

#### **Code Buffer Control**

The Code Buffer Control block manages the code buffer VRAM memory. It implements a code buffer consisting of four individual buffer "pages" in compression, and two buffer "pages" in expansion. In compression, each of the four pages contains one compressed field, and the software is responsible for reading every compressed field or every other compressed field, in accordance with whether the chosen resolution requires vertical decimation or not. In expansion, each of the two pages contains either a compressed field or a compressed frame (that is, two fields), in accordance with the setting of the Vertical Decimation bit (see Command Register 1 - Table 11), depending on the vertical decimation mode of the encoder that was used to code these files. Host system access to the code memory is mediated by this module, which arbitrates between host accesses, VRAM transfer cycles, and code memory refresh cycles.

#### **Host System Interface**

The Host System Interface block provides an interface to the host (ISA) bus and software. It contains the control registers that allow the host to set the operating modes and obtain status information. It decodes addresses for the various resources accessible by the host, and generates a "frame ready" interrupt signal in compression.

# **Interface Signal Descriptions**

# **Table 3: Host System Interface**

| Name        | Туре | Description                                                                                                                                                                                                                                       |

|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HD(15:0)    | I/O  | 16-bit bidirectional data bus, used for: - accessing the internal registers of the ZR36055, - accessing the code buffer, - accessing the strip buffer in still image compression or expansion.                                                    |

| MEMW        | ı    | Memory write strobe. Should be connected directly to the ISA signal MEMW. Since the host accesses to the ZR36055 are all I/O, this signal is used only to prevent the ZR36055 from adding wait states during memory cycles on the Host (ISA) bus. |

| MEMR        | 1    | Memory read strobe. Should be connected directly to the ISA signal MEMR. Since the host accesses to the ZR36055 are all I/O, this signal is used only to prevent the ZR36055 from adding wait states during memory cycles on the Host (ISA) bus.  |

| IOCS16      | 0    | I/O chip select 16, indicates a 16 bit I/O access cycle.                                                                                                                                                                                          |

| H_ALE       | 1    | Host address latch enable. Should be connected to ISA bus BALE.                                                                                                                                                                                   |

| AEN         | ı    | Address enable. Differentiates between I/O and DMA cycles. Should be connected to ISA bus AEN.  0 - Valid I/O cycle  1 - DMA cycle  The ZR36055 responds to the host access only when AEN is LOW                                                  |

| IORDY       | 0    | I/O ready. Indicates to the host that the current cycle should be extended with wait states. (e.g, when the host is trying to access the code buffer while it is busy).                                                                           |

| HA(3:0)     | 1    | The four (4) LSBs of the host address bus, used to select the internal resource accessed.                                                                                                                                                         |

| HA(9:4)     | 1    | The six (6) MSBs of the host address bus, used for decoding access to the ZR36055, thus determining the I/O base address for the ZR36055.                                                                                                         |

| IOBASE(1:0) | ŧ    | Two bits which select the I/O base address for the ZR36055.                                                                                                                                                                                       |

| REFRESH     | 1    | Refresh signal. Commands the ZR36055 to generate a refresh cycle to the code buffer VRAM.                                                                                                                                                         |

| IOR         | 1    | I/O read strobe.                                                                                                                                                                                                                                  |

| IOW         | 1    | I/O write strobe.                                                                                                                                                                                                                                 |

| IRQ         | 0    | Interrupt request line. The width of the IRQ pulse is in the range 390 ns to 500 ns.                                                                                                                                                              |

| H_RESET     | 1    | Host reset. When active, causes the ZR36055 to immediately three-state all bidirectional drivers and enter the reset condition. (Active HIGH).                                                                                                    |

| HDOE        | 0    | Host data output enable. Enables the external data bus transceivers. This signal is active during host access to the ZR36055.                                                                                                                     |

| IACS        | 0    | Internal memory address latch chip select. Strobe signal for an external latch, to latch the ZR36050 address for host access to its internal memory.                                                                                              |

| EXTCS       | ı    | External chip select. Used in cases where it is required to decode more than 10 host address bits to determine the base address of the ZR36055.                                                                                                   |

# **Motion JPEG Controller**

# Table 4: Digital Video Interface

| Name    | Туре | Description                                                                                                                                                                                                                                                                                                               |

|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCLKX2  | 3    | Clock input, at double the frequency of the video data clock. The frequency depends on the format and standard chosen: 29.5 MHz, square pixel PAL 24.5454 MHz, square pixel NTSC 27 MHz, CCIR PAL and NTSC This is the master clock for the ZR36055, in compression and expansion.                                        |

| VCLK    |      | Video data clock, at half the frequency of VCLKX2. 14.75 MHz, square pixel PAL 12.2727 MHz, square pixel NTSC 13.5 MHz, CCIR PAL and NTSC This is the pixel clock, in compression and expansion.                                                                                                                          |

| VSYNC   | 1/0  | Vertical synchronization. Indicates the vertical position of the picture. Active high pulse.                                                                                                                                                                                                                              |

| HREF    | 1/0  | Horizontal reference. Indicates active image data on the digital YUV bus. The positive edge marks the beginning of a new active line. Normally active (high) for 768 Y samples in square pixel PAL, 640 Y samples in square pixel NTSC, or for 720 Y samples for CCIR. HREF is also present during the vertical blanking. |

| HSYNC   | 0    | Horizontal synchronization. Indicates the horizontal position of the picture. Active high pulse, generated in expansion in internal sync mode.                                                                                                                                                                            |

| FEOUT   | 0    | Fast enable output. In compression (or IDLE) enables the digital video source bus. In expansion disables the digital video source bus by forcing the decoder to set its Y and UV outputs to the high impedance state.                                                                                                     |

| VBUSEN  | 0    | Video bus enable. Enable signal for external transceivers on the Y and UV digital data buses.                                                                                                                                                                                                                             |

| Y(7:0)  | 1/0  | 8-bit luminance data. Input in compression, output in expansion.                                                                                                                                                                                                                                                          |

| UV(7:0) | I/O  | 8-bit multiplexed chrominance data. Input in compression, output in expansion.                                                                                                                                                                                                                                            |

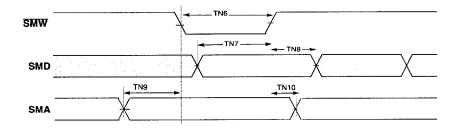

## **Table 5: Strip Buffer Interface**

| Name      | Туре | Description                      |  |

|-----------|------|----------------------------------|--|

| SMD(15:0) | 1/0  | 16-bit strip memory data bus.    |  |

| SMA(13:0) | 0    | 14-bit strip memory address bus. |  |

| SMR       | 0    | Strip memory read strobe.        |  |

| SMW       | 0    | Strip memory write strobe.       |  |

# **Table 6: Code Memory Interface**

| Name     | Туре | Short Description                                                                                     |  |

|----------|------|-------------------------------------------------------------------------------------------------------|--|

| CMD(7:0) | 1/0  | 8-bit code memory data bus.                                                                           |  |

| CMA(8:0) | 0    | 9-bit code memory address bus.                                                                        |  |

| CME_WE   | 0    | Code memory mask enable/write enable. High during a code memory read cycle, low during a write cycle. |  |

| CTR_OE   | 0    | de memory transfer enable/output enable. High during a transfer cycle, low during a read cycle.       |  |

| CCAS     | 0    | Code memory CAS.                                                                                      |  |

| CRAS     | 0    | Code memory FAS.                                                                                      |  |

| CSE      | 0    | Code memory serial clock enable.                                                                      |  |

| csc      | 0    | Code memory serial clock.                                                                             |  |

## Table 7: ZR36050 Interface

| Name       | Туре | Short Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CKEN       | 0    | Clock enable. Enables the data clock and the internal PLL of the ZR36050. Must be connected to the CLKEN pin of the ZR36050.                                                                                                                                                                                                                                                                                                  |

| DCLK       | 0    | Data clock. Must be connected to CLK_IN of the ZR36050. The frequency is determined by the video standard and pixel format, and the FAST bit of Command Register 0.                                                                                                                                                                                                                                                           |

| END        | ı    | End of process. Indicates the end of a frame encoding or decoding. Must be connected to the END pin of the ZR36050.                                                                                                                                                                                                                                                                                                           |

| C_RESET    | 0    | ZR36050 RESET. The ZR36055 issues a RESET to the ZR36050 when H_RESET or the GRESET bit in Command Register 0 is active. Must be connected to the RESET pin of the ZR36050.                                                                                                                                                                                                                                                   |

| STOP       | I/O  | Stop sending/receiving image data. In Compression - input from the ZR36050, indicating to the ZR36055 that it should stop transferring data to the ZR36050 at the end of the current block.  In Expansion - output to the ZR36050 indicating that the raster to block module is busy and expects the ZR36050 to stop delivering image data at the end of the current block. Must be connected to the STOP pin of the ZR36050. |

| PDATA(7:0) | I/O  | Pixel data bus of the ZR36050. In Compression - output from the ZR36055 to the ZR36050. In expansion - input from the ZR36050.                                                                                                                                                                                                                                                                                                |

| DSYNC      | I/O  | Data synchronization pulse. The pulse width is one DCLK cycle. In compression - output signal indicating to the ZR36050 the start of an 8x8 block. It appears one DCLK before the first image data of a block. In expansion - input from the ZR36050 that appears one DCLK before the first data sample of a block.  Must be connected to the DSYNC pin of the ZR36050.                                                       |

| EOS        | I/O  | End of scan pulse. The pulse width is one DCLK cycle. In Compression - output signal indicating the last image data sample of each scan entering the ZR36050. In expansion - input from the ZR36050 indicating the last image data sample of each scan.  Must be connected to the EOS pin of the ZR36050.                                                                                                                     |

| CBUSY      | 0    | Compressed data memory busy. Must be connected to the CBUSY pin of the ZR36050.                                                                                                                                                                                                                                                                                                                                               |

| CCS        | ı    | Code memory chip select. Indicates that a data read or write operation between the ZR36050 and the code memory is in progress. Must be connected to the CCS pin of the ZR36050.                                                                                                                                                                                                                                               |

| CRD        | 0    | ZR36050 internal memory read. Must be connected to the RD pin of the ZR36050.                                                                                                                                                                                                                                                                                                                                                 |

| CWR        | 0    | ZR36050 internal memory write. Must be connected to the WR pin of the ZR36050.                                                                                                                                                                                                                                                                                                                                                |

## Table 8: Power & Test

| Name            | Type  | Short Description                                                                               |  |  |

|-----------------|-------|-------------------------------------------------------------------------------------------------|--|--|

| Test            | ı     | Factory Test pin. In normal operation must be connected to ground potential (V <sub>SS</sub> ). |  |  |

| V <sub>DD</sub> | Power | 5 Volt power supply.                                                                            |  |  |

| V <sub>SS</sub> | Power | Power supply ground.                                                                            |  |  |

#### **INTERFACES**

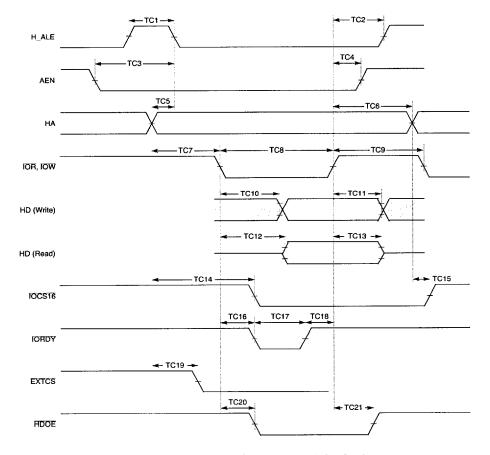

#### **Host System Interface**

The ZR36055 Host System Interface is designed to support the ISA bus with minimal glue logic. All host accesses to the ZR36055 internal resources (the control registers), and to the external resources controlled by the ZR36055 (internal memory of the ZR36050, the code buffer, and the strip buffer) are mapped into the ISA bus I/O space. The Base Address of the ZR36055, decoded from HA[9:4], can be assigned by the two input pins IOBASE(1:0) according to Table 9.

Table 9: I/O Base Address

| IOBASE 1 | IOBASE 0 | Base Address |

|----------|----------|--------------|

| 0        | 0        | 200h         |

| 0        | 1        | 280h         |

| 1        | 0        | 300h         |

| 1        | 1        | 380h         |

The ZR36055 consumes 16 consecutive addresses in the ISA bus I/O space, starting from the Base Address.

Host accesses are 8 bits or 16 bits wide, depending on the resource accessed. When an access to one of the 16-bit resources is decoded, IOCS16 is driven low by the ZR36055. Note that since IOCS16 is not an open-drain output, an external buffer is needed to drive the ISA bus.

Ten ISA bus address bits are decoded by the ZR36055 to provide a glueless interface to the ISA bus. Decoding of the ISA address bits is done only while EXTCS is active (LOW), and AEN is LOW. In cases where more than ten bits must be decoded to determine the base address, the EXTCS pin can be used as a qualifier, generated by external decoding of higher address bits.

Under the assumption that the host data bus of the ZR36055 is connected to the system data bus by means of bidirectional transceivers, the ZR36055 generates a transceiver enable signal, HDOE. HDOE is activated when EXTCS is active and AEN is LOW, one of the I/O commands (IOW or IOR) is active, and the Base Address is decoded on HA[9:4].

IORDY is driven low only during host accesses to the code memory, if the code memory is temporarily unavailable. IORDY goes low after the falling edge of H\_ALE. The ZR36055 cannot, however, distinguish between an I/O and a memory access cycle at this point, so if MEMR or MEMW goes active, IORDY is immediately driven high. MEMR and MEMW have no function in the ZR36055 other than this. IORDY, like IOCS16, is not an open drain output, so an external buffer is needed to drive the ISA bus.

The IRQ output has to be connected to the selected interrupt request line of the ISA bus, through an external buffer. It is an active LOW signal which indicates that the compression of a field

has been completed. The  $\overline{\text{IRQ}}$  signal pulse width ranges between 390 ns and 500 ns.

#### **Digital Video Interface**

The Digital Video Interface of the ZR36055 conforms to the defacto standard established by the Philips SAA7110 and SAA7111 decoders.

In compression, it can interface directly to the data and sync outputs of these decoders, or any other decoder or digital video source that provides equivalent clock, synchronization and video signals. VSYNC, the vertical sync signal, and HREF, the horizontal blanking signal, are inputs to the ZR36055 in compression.

In expansion, the ZR36055 can work in two synchronization modes, internal sync mode, and external sync mode. In internal sync mode, the ZR36055 generates data and sync signals that emulate those of the video decoder, and can therefore drive directly the video input of any scaling, display-overlay or composite video encoding device that accepts signals in this format. The exact periods of the synchronization signals (HREF, HSYNC and VSYNC) can be programmed to match the format used (CCIR or Square pixel, PAL or NTSC). VSYNC is driven high at the start of each field, for a period equivalent to six video lines. HREF is driven high during the active-pixels interval of each line; the exact interval is programmable to correspond to the pixel format and video standard being used. HSYNC, the horizontal synchronization signal, is a programmable output signal generated in internal sync mode; this signal is required by some of the overlay processors. In external sync mode, the ZR36055 outputs the data in synchronization with the sync signals provided by an external device (e.g., the video decoder or a video encoder).

VCLKX2 and VCLK provide the reference for digital video interface signal timing. Both of these clock signals are required inputs in compression and in expansion.

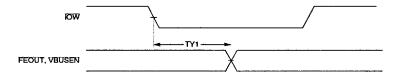

FEOUT and VBUSEN are output signals that can be used to control external three-state buffers and bidirectional data transceivers for the digital video and sync signal lines. The truth table for these signals is shown in Table 10.

Table 10: Truth Table for FEOUT and VBUSEN

| Operating Mode | FEOUT | VBUSEN [1] |

|----------------|-------|------------|

| Compression    | Low   | Low        |

| Expansion      | High  | Low        |

VBUSEN is in the HIGH state after activation of H\_RESET and before the ZR36055 is commanded to be active by the ACTIVE bit of the COM1 register, and driven LOW only after the ACTIVE command. It is driven high again only by activation of H\_RESET.

FEOUT and VBUSEN change state at most 5 VCLKX2 periods after the falling edge of  $\overline{IOW}$  in the write cycle to the COM0 or COM1 register that caused the change.

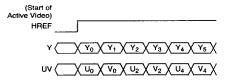

The form of the component digital video signal expected in compression and output in expansion is shown in Figure 3.

Figure 3. Digital Video Component Sequence

#### Strip Memory Interface

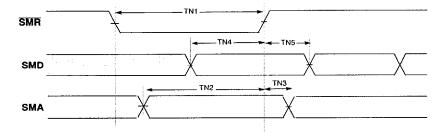

The Strip Memory Interface supports an 8KWord strip memory composed of 2 x 8K x 8 SRAM for a system based on the ZR36055-21 (Low End system), and a 32KWord strip memory consisting of 2 x 32K x 8 SRAM for a system based on the ZR36055-29.5 (High End system). The timing of the interface signals is consistent with the specification of typical SRAMs of 15ns or faster speed (for example, Micron Technologies MT5C2568-15). The strip buffer interface is composed of a 13-bit address bus for the Low End systems and a 14-bit address bus for the High End systems, a 16-bit data bus, and read and write control signals. The raster-to-block and block-to-raster operations are performed by suitable addressing of the SRAM address bus, along with appropriate read or write commands.

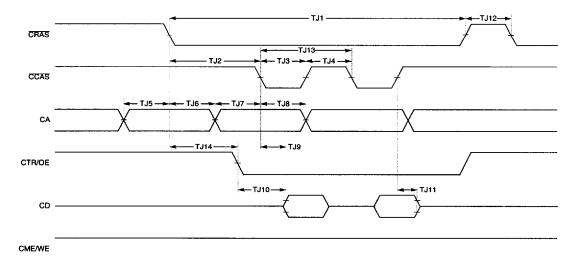

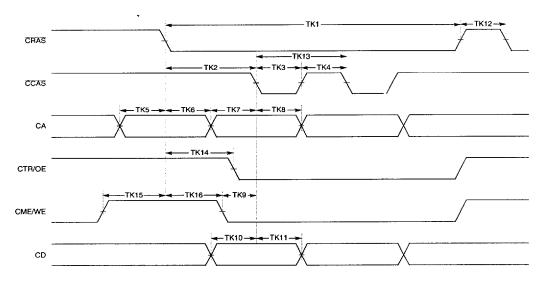

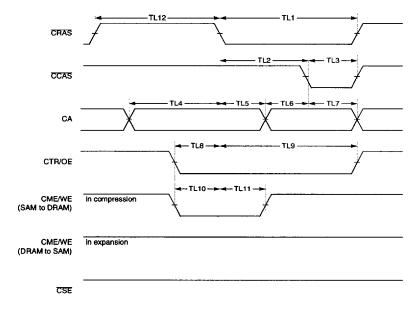

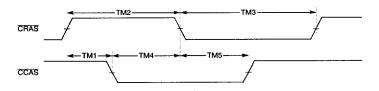

### Code Memory Interface

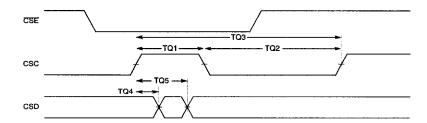

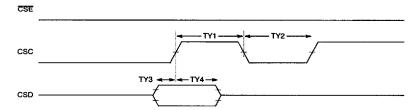

The Code Memory Interface supports a 128Kbyte code memory consisting of a 128K x 8 VRAM (with 128K x 8 DRAM and 256 x 8 SAM) for the Low End subsystem based on the ZR36055-21, and a 256KByte code memory consisting of a 256K x 8 VRAM (with 256K x 8 DRAM and 512 x 8 SAM) for the High End subsystem based on the ZR36055-29.5. The timing of the interface signals is consistent with the specifications of typical VRAMs (such as Micron Technologies MT42C8128 or MT42C8256) of 70ns or faster speed. The VRAM used must have bidirectional serial ports.

The serial port of the VRAM is used for the compressed data flowing between the code memory and the ZR36050. The parallel port is used for accesses to the code memory by the host system. Since the host system bus is 16 bits wide and each host access translates to two code memory accesses to sequential locations in the same page, the parallel port accesses are always implemented as fast page mode cycles. Note that the ZR36055 does not require Extended Data Out (EDO) in page mode reads.

In compression, the ZR36055 performs a "Write Transfer (SAM-to-DRAM Transfer)" cycle to transfer the Serial Access Memory to a page of DRAM. In expansion, the ZR36055 performs a "Real

Time Read Transfer (DRAM-to-SAM Transfer)" cycle to transfer a DRAM page to the Serial Access Memory.

Code Memory VRAM refresh is timed by the REFRESH input signal of the Host System Interface. Refresh cycles are of the CAS-before-RAS type.

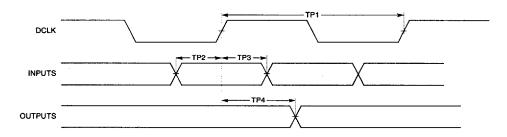

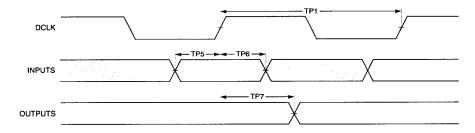

#### ZR36050 Interface

The ZR36050 interface performs the following operations: It produces the clocks and general control signals for the ZR36050, handles the ZR36050 internal memory access, controls the image data transfer between the ZR36055 and ZR36050, and controls the ZR36050 access to the compressed data memory (code buffer).

The ZR36050 clocks and general control signals are:

- DCLK, the data clock of the ZR36050 (connected to its CLK\_IN pin) is produced by the ZR36055.

- CLKEN (enabling the internal ZR36050 PLL) is controlled by the host through the COM1 register.

- C\_RESET resets the ZR36050 during the initialization stage.

- END coming from the ZR36050 signals the end of a compression or expansion process. During continuous compression or expansion, activation of END initiates the next GO to the ZR36050.

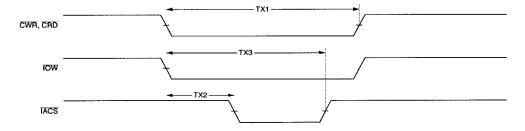

A special mechanism in the ZR36055 allows the host to access the ZR36050's internal memory. Two of the control ports implemented by the ZR36055 are dedicated to providing the control signals for the data and address paths, which are external to the ZR36055. When the host performs a write access to the ZR36050\_Address port, the host data bus is latched into an external address register by the IACS control signal. When the host subsequently accesses the ZR36050\_Data port, the ZR36055 drives CRD or CWR as appropriate, to perform a host read or write access to the ZR36050 internal memory at the address stored in the external address register.

The Pixel interface of the ZR36050 is handled by the ZR36055 as follows:

- In compression, the PDATA bus is used to transfer the image data into the ZR36050. The DSYNC (Data Synchronization) signal preceding each block is produced, as well as the EOS (End Of Scan) signal at the end of the image, together with the last pixel of the last block of the image. The ZR36055 checks that the STOP signal of the ZR36050 is not active before sending out a block.

- In expansion, DSYNC and EOS change from output to input signals, and STOP changes from an input to an output signal. The ZR36055 receives the image data a block at a time on the PDATA bus. Each block is preceded by a DSYNC, and the last pixel of the last block of the image is accompanied by the EOS signal. STOP is activated when the ZR36055 is not ready to accept any more blocks.

The ZR36050 access (Read or Write) to the compressed data is controlled using the CCS and CBUSY signals. In compression, an active CCS signal initiates a write cycle to the code buffer VRAM serial port. Note that the CODE bus of the ZR36050 must be programmed to work during compression at 1 clock per write cycle (CFIS=0). During expansion, an active CCS signal initiates a read cycle from the code buffer VRAM serial port. The CODE bus of the ZR36050 must be programmed to work during expansion at 2 clocks per read cycle (CFIS=1). CBUSY is activated when the code buffer VRAM is not available to the ZR36050 (during refresh or transfer cycles for example).

#### **CONTROL REGISTERS**

This section describes the ZR36055's control registers and control ports, which consist of:

- · Three Command registers, used by the host to set the operating mode of the ZR36055 and to control its operation. Command Register 2 is a hybrid, in that it also contains a readable hard-coded "ZR36055 ID" field.

- · One Status register, typically read after each frame is processed (in either expansion or compression), indicates the

- · Three Information registers, read after each frame is processed (in either expansion or compression), provide information needed by the software to track the operation of the subsystem.

- Two ZR36050 access ports provide a means for the host software to access the internal memory and registers of the ZR36050.

- · Two ZR36055 data registers, used to transfer information between the host and the ZR36055.

- An indexed array of registers known collectively as the SIZE register, hold numerical data used to control operation of the ZR36055.

Table 11 lists the control registers of the ZR36055 along with their address offsets relative to the I/O base address, read/write accessibility, and widths.

**Table 11: Host Access Address Map**

| Accessed Resource        | Offset<br>Address | Read/<br>Write | Width  |

|--------------------------|-------------------|----------------|--------|

| Command Register 0, COM0 | 09 h              | R/W            | 8-bit  |

| Command Register 1, COM1 | 0A h              | R/W            | 8-bit  |

| Command Register 2, COM2 | 08 h              | R/W            | 8-bit  |

| Status Register, STATUS0 | 05 h              | R              | 8-bit  |

| Field Count, FCNT        | 0B h              | R              | 8-bit  |

| Length Register 0, LEN0  | 06 h              | R              | 8-bit  |

| Length Register 1, LEN1  | 07 h              | R              | 8-bit  |

| ZR36050_Data             | 04 h              | R/W            | 8-bit  |

| ZR36050_Address          | 02 h              | w              | 16-bit |

| Strip buffer Data        | 0C h              | R/W            | 16-bit |

| Code buffer Data         | 00 h              | R/W            | 16-bit |

| SIZE                     | 0E h              | w              | 16-bit |

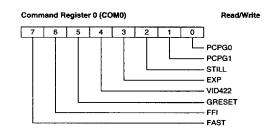

### Command Register 0 (COM0), Read/Write

| Field               | Name                                 | Description                                                                                                                                                                                                                                                                                                                                                              | Reset<br>state |

|---------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| FAST <sup>[1]</sup> | ZR36050 clock<br>speed range         | SLOW clock (12.27,13.5,14.75 MHz for square pixel NTSC, CCIR, square pixel PAL respectively).     FAST clock (24.5,27,29.5 MHz for square pixel NTSC, CCIR, square pixel PAL respectively)                                                                                                                                                                               | 1              |

| FFI                 | First Field ID                       | O: The first expanded field is field II 1: The first expanded field is field I (field II is the field in which the trailing edge of VSYNC falls in the middle of a line) Not applicable for compression mode                                                                                                                                                             | 1              |

| GRESET              | Global Reset                         | 0: Resets the internal ZR36055 circuits, activates the C_RESET signal to reset the ZR36050                                                                                                                                                                                                                                                                               | 0              |

| VID422              | Digital video format                 | Expand YUV 411 digital video format     Expand YUV 422 digital video format     Not applicable for compression mode                                                                                                                                                                                                                                                      | 1              |

| EXP                 | Compression or<br>Expansion Mode     | 0: Compression mode<br>1: Expansion mode                                                                                                                                                                                                                                                                                                                                 | 0              |

| STILL               | Still image mode                     | Continuous compression or expansion     Still compression or expansion                                                                                                                                                                                                                                                                                                   | 0              |

| PCPG[1:0]           | Code buffer page<br>selected by host | Using this field, the Host selects the code buffer page to load in expansion or unload in compression. In compression mode, both bits are used; the code buffer is partitioned into 4 pages. In expansion, only PCPG is used; the code buffer is partitioned into 2 pages Note: the ZR36055 will not compress into or expand from the code buffer page selected by PCPG. | 00             |

1. The FAST bit determines the frequency of DCLK, the data clock for the ZR36050. When 1 (FAST clock), the frequency of DCLK is the same as that of VCLKX2, and when 0 (SLOW clock), the frequency of DCLK is one half that of VCLKX2.

FAST clock can be used with the high-end 055 chip-set in all resolution, decimation and cropping modes.

SLOW clock can be used only if it is known that the ZR36050 is able to process the image when operating at this clock frequency. Generally, this means that SLOW clock can be used only if the compressed image width is equal to or smaller than one-half of the full digitized image width, that is, in Quarter or Half Horizontal resolution:

· when the image is decimated horizontally (HOR\_DEC of COM1 is 1), or

· when the image is cropped to half the original width or smaller.

SLOW clock must be used with the low-end chip-set (ZR36050-21 and ZR36055-21).

### Command Register 1 (COM1), Read/Write

####

| Field     | Name                                       | Description                                                                                                                                                                                                                                                              | Reset<br>state |

|-----------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| VID_FMT   | Video Format                               | Determines the sync signals structure in expansion mode with internal sync 0: PAL video format 1: NTSC video format                                                                                                                                                      | 1              |

| INT_EN    | Interrupt<br>Enable                        | Enables the ZR36055 interrupt line 0: Disable, 1: Enable                                                                                                                                                                                                                 | 0              |

| CLK_EN    | Clock Enable                               | Enables the ZR36050 clock 0: Disable, 1:Enable This bit directly controls the CKEN pin                                                                                                                                                                                   | 0              |

| SNC_SRC   | Sync Source                                | Synchronization source in Expansion 0: External Synchronization, 1: Internal Synchronization                                                                                                                                                                             | 0              |

| HOR_DEC   | Horizontal<br>Decimation,<br>Interpolation | In compression mode- selects 2:1 horizontal decimation In expansion mode- selects 1:2 horizontal interpolation 0: no decimation or interpolation, 1: with decimation or interpolation                                                                                    | 0              |

| VER_DEC   | Vertically<br>Decimated<br>Frame           | In compression mode - not applicable [1] In expansion mode - defines 1:2 vertical decimation (i.e., defines whether the expanded frame contains 1 or 2 fields) 0: not decimated (2 fields) 1: decimated (1 field) If 1, the ZR36055 expands each field twice, on average | 0              |

| CBUF_SIZE | Code Buffer<br>Size                        | Defines the code buffer and page sizes 0: code buffer size=128KBytes VRAM, page size=32 KBytes in compression, 64KBytes in expansion 1: code buffer size=256KBytes VRAM, Page size=64 KBytes in compression 128 KBytes in expansion                                      | 1              |

| ACTIVE    | Active                                     | O: Activated by the software, to initiate a compression or expansion sequence.     I: Inactive                                                                                                                                                                           | 1              |

In continuous compression mode, the 055 subsystem always compresses every field. Vertical decimation (for quarter and half vertical resolutions), is accomplished entirely by the host software, by skipping every other code buffer page. The data in the unwanted pages is not read out by the host, and is not transferred through the host data bus. (The host must, however, read out the status information of each page.)

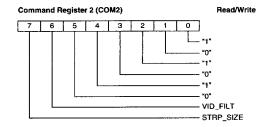

### Command Register 2 (COM2), Read/Write

| Field     | Name         | Description                                                                                                        | Reset<br>state |

|-----------|--------------|--------------------------------------------------------------------------------------------------------------------|----------------|

| STRP_SIZE | Strip Size   | Defines the strip buffer size<br>0: 8KBytes SRAM<br>1: 32 KBytes SRAM                                              | 1              |

| VID_FILT  | Video Filter | Defines optional filter when doing Horizontal Decimation/Interpolation [1] 0: no filtering 1: use internal filters | 1              |

| Bits 5:0  | ID           | ZR36055 ID field, 15 hex                                                                                           |                |

The decimation filter is a 3-tap filter with coefficients (0.25, 0.5, 0.25). The

first pixel in a line is copied as is. The interpolation filter is a 2-tap filter with

coefficients (0.5, 0.5). The last pixel in a line is duplicated.

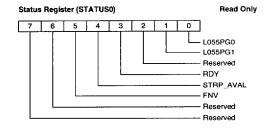

### Status Register (STATUS0), Read Only

| Field       | Name                      | Description                                                                                                                                                                              | Reset<br>state |

|-------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| FNV         | Field Not<br>Valid        | When 1, indicates that the last compressed field was invalid (i.e., its size exceeded the size of a page in the code buffer or when the data in the strip buffer was overwritten).       | 0              |

| STRP_AVAL   | Strip Buffer<br>Available | Used only in still compression or expansion mode: when 1, indicates that the ZR36055 is ready for a strip to be written or read by the host.                                             | 0              |

| RDY         | Ready                     | Active High: Set when the ZR36050 asserts the END (end of process) signal. Cleared when the host reads Length Register 1 (LEN1).                                                         | 0              |

| L055PG[1:0] | Last 055<br>Page          | Reflects the number of the last code buffer page processed by the ZR36055 in compression or expansion. In expansion, since there are only two code buffer pages, L055PG1 can be ignored. | 0.0            |

### **Information Registers**

| Name | Description                                                                                                                                                                                                      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FCNT | Fields/Pages counter register, 8 bit, Read only. Provides a running modulo 256 count of fields compressed or code buffer pages expanded, enabling the host software to keep track of dropped or skipped frames.  |

| LEN0 | Low byte of the code buffer page length, 8 bit, read only.                                                                                                                                                       |

| LEN1 | High byte of the code buffer page length, 8 bit, read only. LEN1 and LEN0 indicate the actual size in bytes of the compressed field in the code buffer page defined by the L055PG field of the STATUSO register. |

#### **ZR36050 Access Ports**

| Name                | Description                                                                                                                                                                                               |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ZR36050_<br>Address | ZR36050 internal memory address port, 16 bit, write only. The access to this port activates the IACS signal to latch the host data bus in an external register connected to the ZR36050 host address bus. |  |  |  |

| ZR36050_Data        | ZR36050 internal memory data port, 8 bit, read/<br>write. Accesses to this port are directed to the<br>ZR36050 host data port.                                                                            |  |  |  |

#### **ZR36055 Data Registers**

| Name                 | Description                                                                                                                                                                               |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Strip Buffer<br>Data | Strip buffer data, 16 bit, read only in expansion, write only in compression. The ZR36055 automatically increments the strip buffer address on successive accesses to this port.          |

| Code Buffer<br>Data  | Code buffer compressed data, 16 bit, read only in compression, write only in expansion. The ZR36055 automatically increments the code buffer address on successive accesses to this port. |

When accessing the 16-bit Code Buffer Data register, the earlier byte of the JPEG stream is on the lower byte (bits 7:0) of the data bus. Similarly, when accessing the Strip Buffer Data register, the earlier sample is on the lower byte of the data bus.

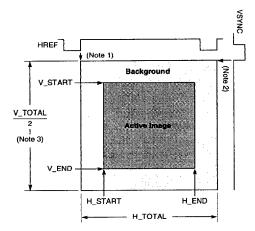

### **SIZE Registers**

This indexed array of registers defines the desired size of the processed image, numerical data used by the internal sync generator, and the background color when images smaller then the full resolution image are displayed. The register index is specified by the 4 MSBs, while the value is defined by the 11 LSBs. Bit 11 is not used in most of the SIZE registers; in the background color registers it extends the index, while in the NBLK register it indicates the last strip.

Table 12: SIZE Register Description [1] [2] [3] [4] [5] [6] [7]

|                                                       | Bits    |                                     |                   |                           |

|-------------------------------------------------------|---------|-------------------------------------|-------------------|---------------------------|

|                                                       | (15:12) |                                     | Bits              | Reset                     |

| Name                                                  | (index) | Bit 11                              | (10:0)            | state                     |

| Horizontal Image<br>START <sup>[8]</sup><br>(H_START) | Oh      | Х                                   | Value<br>(Pixels) | 0                         |

| Horizontal Image<br>END<br>(H_END)                    | 1h      | Х                                   | Value<br>(Pixels) | 0                         |

| Horizontal Image<br>TOTAL<br>(H_TOTAL)                | 2 h     | . x                                 | Value<br>(Pixels) | 0                         |

| Hsync START<br>(HS_START)                             | 3 h     | ×                                   | Value<br>(Pixels) | 0                         |

| Hsync END<br>(HS_END)                                 | 4 h     | х                                   | Value<br>(Pixels) | 0                         |

| BLANK_START                                           | 5 h     | Х                                   | Value<br>(Pixels) | 0                         |

| Vertical Image<br>START<br>(V_START)                  | 8 h     | Х                                   | Value<br>(Lines)  | 0                         |

| Vertical Image<br>END<br>(V_END)                      | 9 h     | Х                                   | Value<br>(Lines)  | 0                         |

| Vertical Image<br>TOTAL <sup>[9]</sup><br>(V_TOTAL)   | Ah      | Х                                   | Value<br>(Lines)  | 0                         |

| Number of MCU's<br>per line - 1<br>(NMCU)             | Ch      | х                                   | Value             | 0                         |

| Number of blocks<br>per strip - 1<br>(NBLK)           | Dh      | last strip =1<br>not last strip = 0 | Value             | 0                         |

| Y component<br>Background<br>(YBG)                    | Eh      | 0                                   | Value             | 11001000<br>(200 decimal) |

| U/V component<br>Background<br>(UVBG)                 | Eh      | 1                                   | Value             | 10110100<br>(180 decimal) |

- In continuous compression mode, H\_START, H\_END, H\_TOTAL, V\_START, V\_END, V\_TOTAL and NMCU are required.

- In continuous expansion mode, H\_START, H\_END, H\_TOTAL, V\_START, V\_END, V\_TOTAL and NMCU are required. HS\_START, HS\_END and BLANK\_START are required only in internal sync mode.

- 3. In still compression and expansion modes, only NBLK is required.

- H\_START, H\_END, BLANK\_START, HS\_START and HS\_END are measured from the rising edge of HREF.

- 5. V\_START and V\_END are measured from the falling edge of VSYNC.

- In compression, (H\_END H\_START) must be a multiple of 16 pixels if horizontal decimation is not used, and a multiple of 32 pixels if horizontal decimation is used.

In expansion, (H\_END - H\_START) must equal the compressed image width if horizontal interpolation is not used, and twice the compressed image width if horizontal interpolation is used. The compressed image width must be a multiple of 16 if the format is YUV 4:2:2, or a multiple of 32 if the format is YUV 4:1:1.

- In compression, (V\_END VSTART) must be a multiple of 8 lines.

In expansion, (V\_END VSTART) must equal the height of the compressed field, which must be a multiple of 8.

- 8. H\_START must have an even value.

- V\_TOTAL is the number of lines in the full interlaced frame. It must have an odd value.

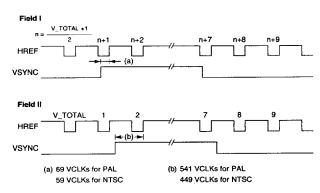

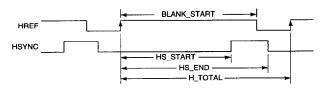

The following diagrams further describe the video synchronization parameters.

Notes: 1. Rise of HREF signal marks the beginning of a video line.

- The falling edge of VSYNC marks the beginning of a field, and is the reference point for V\_START and V\_END.

- 3. V\_TOTAL applies to the full frame size (625 lines for PAL, 525 for NTSC).

- 4. The diagram depicts the active image portion of each field.

Figure 4. Definition of Active Image and Background Regions

Figure 5. Definition of Field I and Field II

Figure 6. Definition of Horizontal Sync and Blanking Signals in Internal Sync Mode

#### **OPERATING MODES**

The 055 Chip Set has four operating modes:

- · Continuous compression

- · Continuous expansion

- · Still compression

- · Still expansion

This section describes the operation of the chip set in each of the above modes. An Application Note, giving a more detailed step-by-step account of the procedures the host software must perform, including a specific example, is available. For a detailed description of the registers mentioned in this section, see the Control Registers section.

#### **Continuous Compression (Capture)**

An 055 subsystem can compress any video sequence consisting of YUV 4:2:2 video frames, at full, half and quarter resolutions, for both CCIR and square pixel frame sizes. The actual frame size compressed in each of the available resolutions can be reduced from its nominal value by cropping.

After compression is activated (by setting the ACTIVE bit of the COM0 register to 0), the first field to be compressed by the ZR36055 is field II, which is defined to be the field in which the trailing edge of VSYNC falls in the middle of a line.

The ZR36055 receives the YUV 4:2:2 digital video through the digital video bus, and performs, when required, horizontal decimation with optional filtering. Next, the raster to block conversion is performed using the external double strip buffer. The ZR36055 then routes the YUV blocks to the ZR36050, where each 8x8 pixel block is compressed according to the JPEG baseline algorithm, yielding the coded (compressed) image. The compressed JPEG data is subsequently stored in the code buffer.

Note that in compression, the code buffer is composed of 4 pages of size equal to 1/4 of the code buffer size. Each page contains 1 compressed field.

At the end of each compression pass by the ZR36050, the ZR36055 detects the END signal, and starts a new compression pass by writing a GO command to the ZR36050. In parallel, it checks the state of the RDY bit in the STATUS0 register. If RDY = 0, indicating that the status and information registers associated with the previously compressed field have been read by the host software, the ZR36055 sets the RDY bit to 1, updates the information registers for the current field, and activates the interrupt to the host. If RDY = 1 when checked, indicating that the host did not respond to the previous interrupt, and the previous status and information registers were not yet read by the host software, the ZR36055 does not perform the update, and does not activate the interrupt. Thus the status information associated with the newly compressed field is lost. Host software can keep track of lost fields of this type by means of the FCNT register.

The RDY bit is cleared when the host has read the complete set of status and information registers (STATUS0, FCNT, LEN0, LEN1, in this order).

The host software reads out the contents of a code buffer page by setting the PCPG field in the COM0 register to the selected buffer page number; the selected page is mapped to an ISA bus I/O port. Normally, the ZR36055 fills the code buffer pages sequentially; however, if the next page in sequence is currently selected by PCPG, the ZR36055 does not advance to this page and overwrites the previous page instead. To prevent this, the host must keep up with the ZR36055 by responding to the interrupts and reading the code buffer in a timely manner.

#### **Continuous Expansion (Playback)**

An 055 subsystem can expand a JPEG Baseline compressed video sequence consisting of frames of any supported resolution in YUV 4:2:2 format. In addition, for backward compatibility with the 045 Chip Set, the 055 Chip Set supports expansion of YUV 4:1:1 format JPEG compressed video, at up to Quarter resolution. The sequence is not required to have been compressed by the 055 subsystem, as long as each compressed frame is fully JPEG compliant, and its size does not exceed the code buffer page size (Code buffer page size limit is 128 KBytes for the High End ZR36055-29.5 chip set and 64KBytes for the Low End ZR36055-21 chip set respectively).

In expansion, the code buffer is partitioned into two pages, each equal to one half of the code buffer memory size. Each page can contain either one field or two fields, depending on whether the compressed frames consist of one field (Quarter and Half Vertical resolutions) or two fields (Full and Half Horizontal resolutions) each.

To expand a compressed video sequence, the host software loads the compressed data a frame at a time, via the ZR36055, into the two available code buffer pages, and the 055 subsystem automatically expands them alternately. When expansion of a frame is complete, the ZR36055 checks the PCPG field of the COM0 register to determine whether the other code buffer page is available, that is, not selected by PCPG. If it is available, it starts expanding the new frame, otherwise, it expands the previous page again (In full or half horizontal resolution, it reexpands both fields of the compressed frame before checking PCPG again. In half vertical or quarter resolution it checks PCPG after each re-expansion of the field). In parallel, it sets the RDY bit of the STATUS0 register to 1. The host software must poll the RDY bit to determine when a code buffer page is ready for a new frame to be written into it. The RDY bit is cleared by the ZR36055 as soon as the host has acknowledged the ready indication by reading the complete set of status and information

Each expanded field is transferred onto the digital video bus for display. In case of Half Vertical and Quarter resolution modes,

each compressed frame comprises one field, and therefore each page in the code buffer contains one field; each field is expanded twice on average, yielding a 50 or 60 fields per second output video sequence.

When the reconstructed image line length is less than or equal to half of the original line length of each video standard and format (see Table 1), optional horizontal interpolation with or without filtering may by used. Thus, the expanded frames are transformed by the ZR36055 back to their original format (CCIR 601 or square pixel at the desired resolution).

For a coded bit stream originating from a YUV 4:1:1 sequence, the ZR36055 interpolates the chrominance components, thus generating a YUV 4:2:2 digital video output.

In expansion, horizontal blanking, horizontal sync, and vertical sync signals may be generated by the ZR36055 when working in internal sync mode, or horizontal blanking and vertical sync can be supplied by an external source in external sync mode.

After it has finished expanding a frame, the 055 subsystem expands the next valid frame in the code buffer. If there are no more valid frames, owing to the host system lagging behind, the 055 subsystem repeats expansion of the last valid frame, and continues to do so until a new frame is written into the code buffer by the host. Thus, the 055 subsystem transparently handles expansion of a sequence that was recorded at a frame rate of less than the standard 25 or 30 frames per second, or one in which frames were dropped at arbitrary intervals.

#### **Still Compression**

In the Still Compression mode of operation, the image to be compressed is provided to the ZR36055 through the host interface, rather than through the video interface. The ZR36055 does not perform raster-to-block reordering of the pixels in this case, rather, it transfers the data samples to the ZR36050 in the order they are received from the host. For this reason, the still compression mode of operation of the ZR36055 can also be used to

implement lossless compression (with some additional circuitry), component interleave, compression of more than three color components and larger resolutions, in the ZR36050.

When using the still compression mode for JPEG baseline compression, the raster-to-block operation, and color space conversion if needed, must be performed by the host software.

The host feeds the image data to the ZR36055 a strip at a time, with handshake based on host software polling of the STRP\_AVAL status bit. The last strip of the image is handled as a special case: if bit 11 of the NBLK SIZE register is 1, the ZR36055 activates EOS to the ZR36050 at the end of the strip. At the end of the process, the compressed image resides in the code buffer. When the ZR36050 activates END, the ZR36055 generates an interrupt to the host indicating that the image can be read from the code buffer.

### Still Expansion

As is the case for Still Compression, in the Still Expansion mode of operation the ZR36055 does not perform the block to raster function, and provides the expanded data to the host in the block format supplied by the ZR36050. The host software must perform the block-to-raster reordering of the pixels, as well as color space conversion, if necessary.

The ZR36055 controls the operation by allowing the ZR36050 to expand a strip at a time. As in the case of Still Compression, the STRP\_AVAL status bit indicates when a new strip is ready to be read out by the host. Note that the host software must identify the last data word of the last strip by calculation based on the image size.

Note: When the ZR36055 is operated in still compression or expansion mode, a square-pixel video decoder must be programmed for PAL mode rather than NTSC, to provide the highest possible clock frequency to the ZR36055. Otherwise there is a possibility of timing violations on the ISA bus interface to the strip buffer, causing incorrect data transfers.

# **Motion JPEG Controller**

## **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                | 65 C to +150 C   |

|------------------------------------|------------------|

| Supply Voltage to Ground           | 0.5V to +7.0V    |

| DC Output Voltage                  | 0.5V to VCC+0.5V |

| DC Input Voltage                   | 0.5V to VCC+0.5V |

| DC Input Current, any single input | 25 mA to +25 mA  |

DC Output Current, any single output..... -25 mA to +25 mA

NOTE: Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above those limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

### **OPERATING RANGE**

| Ambient Temperature | 0 C to +70 (  | C |

|---------------------|---------------|---|

| Supply Voltage      | 4.75V to 5.25 | ٧ |

## **DC CHARACTERISTICS**

| Symbol          | Parameter                  | Min | Тур | Max        | Units    | Test Conditions                                             |

|-----------------|----------------------------|-----|-----|------------|----------|-------------------------------------------------------------|

| V <sub>IL</sub> | Input Low Voltage          |     |     | 0.8        | V        |                                                             |

| V <sub>IH</sub> | Input High Voltage         | 2.0 |     |            | V        |                                                             |

| V <sub>OL</sub> | Output Low Voltage         |     |     | 0.4        | V        | I <sub>OL</sub> = 4 mA, all outputs except VCLK and VCLKX2  |

|                 |                            |     |     |            |          | I <sub>OL</sub> = 16 mA, VCLK and VCLKX2                    |

| V <sub>OH</sub> | Output High Voltage        | 3.7 |     |            | V        | I <sub>OH</sub> = -4 mA, all outputs except VCLK and VCLKX2 |

|                 |                            |     |     |            |          | I <sub>OH</sub> = -16 mA, VCLK and VCLKX2                   |

| I <sub>LI</sub> | Input Leakage Current      |     |     | ±20        | μА       | V <sub>IN</sub> = V <sub>CC</sub> or GND                    |

| loz             | Output Leakage Current     |     |     | ±20        | μА       | V <sub>OUT</sub> = V <sub>CC</sub> or GND, output disabled  |

| C <sub>IN</sub> | Input Capacitance          |     |     | 10         | pF       |                                                             |

| C <sub>IO</sub> | Output and I/O capacitance |     |     | 15         | pF       |                                                             |

| Icc             | Power Supply Current       |     |     | 390<br>290 | mA<br>mA | 29.5MHz<br>21MHz                                            |

# **AC CHARACTERISTICS**

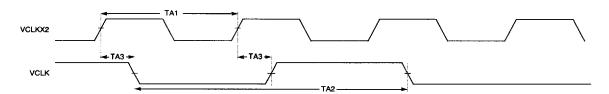

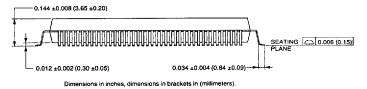

# Digital Video Interface, Clocks

#### Input Requirements

| Symbol | Parameter              | Min | Max   | Unit |                       |

|--------|------------------------|-----|-------|------|-----------------------|

| TA1    | VCLKX2 period          | 32  |       | ns   | 40% to 60% duty cycle |

| TA2    | VCLK period            | 2   | * TA1 |      |                       |

| TA3    | VCLK after VCLKX2 skew | 1   | 8     | ns   |                       |

Figure 7. Digital Video Interface, VCLK and VCLKX2

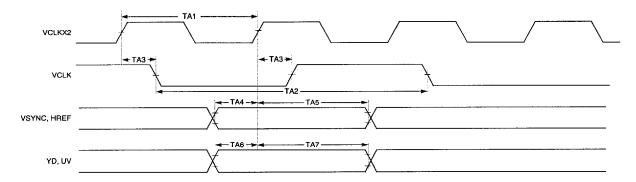

## Digital Video Interface, Compression, Input mode

### Input Requirements

| Symbol | Parameter                    | Min | Max | Unit |  |

|--------|------------------------------|-----|-----|------|--|

| TA4    | VSYNC, HREF setup to VCLKX2  | 4   |     | ns   |  |

| TA5    | VSYNC, HREF hold from VCLKX2 | 8   |     | ns   |  |

| TA6    | YD, UV setup to VCLKX2       | 4   |     | ns   |  |

| TA7    | YD, UV hold from VCLKX2      | 8   |     | ns   |  |

Figure 8. Digital Video Interface, Compression

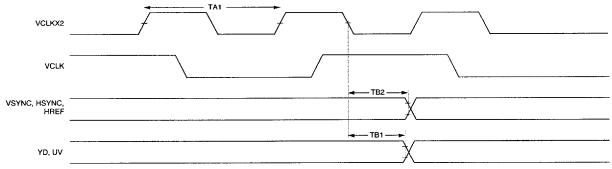

## Digital Video Interface, Expansion, VSYNC and HREF in Output Mode

### **Output Characteristics**

|   | Symbol | Parameter                                 | Min | Max | Unit | notes |

|---|--------|-------------------------------------------|-----|-----|------|-------|

| Ī | TB1    | VCLKX2 to Y, UV output delay              | 0   | 29  | ns   |       |

| Ī | TB2    | VCLKX2 to VSYNC, HSYNC, HREF output delay | 0   | 29  | ns   |       |