DATA SHEET

# PROGRAMMABLE DIGITAL AUDIO PROCESSOR

### **FEATURES**

- Standard High Performance Functions in ROM

- Dolby Digital AC-3, 5.1 channel and 2 channel decoding up to 640 Kbits per second

- Dolby Pro Logic encoding and decoding

- MPEG1 and MPEG2 two channel decoding with MPEG2 PES stream parsing, PTS decoding and SCR handling

- Downloadable SiliconSoftware™ Functions

- Aureal A3D, Dolby Virtual Surround, Harman VMAx

- QSound QSurround™, Spatializer N-2-2™, Home THX

- SRS TruSurround, Music Modes

- Bass Management and multi-channel downmix

- Flexible Input/Output

- Serial and/or parallel data stream I/O

- Serial SPI, serial Z2C or 8-bit parallel host interface

- 3 serial input data ports and 4 serial data output ports

- Formatted S/PDIF receiver with up to 96 kHz sample rate

- Sample rates: 32 kHz, 44.1 kHz, 48 kHz or 96 kHz

- Formatted S/PDIF AC-3 and MPEG transmitter output

- Low System Cost

- Host-less operation with no glue chips

- Separate internal PLLs for DSP core and audio I/O

- No external RAM required for 5.1 Dolby AC-3/MPEG2

- Wait-state generation for low-cost external memory

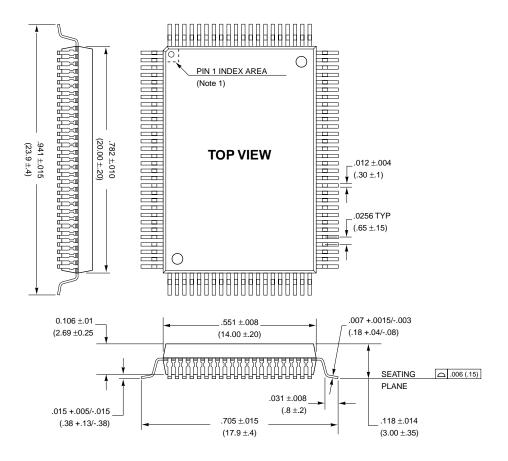

- 100-pin Plastic Quad Flat Pack (PQFP) packaging

- 3.3 V supply with 5 V compatible I/O for low power

- Software and Hardware PC Development Environment

- Assembler/Linker/Simulator

- On-chip ICE support with direct PC connection

- ZR38600DB Demonstration Board with 6 analog outputs, microphone and line inputs, and optional PC connection

### **DESCRIPTION**

The Zoran ZR38601 is a high performance programmable digital audio signal processor capable of real-time single-chip decoding of Dolby Digital AC-3 5.1-channel and MPEG2 digital surround algorithms. It is the fourth generation decoder made by Zoran, being based on the proven ZR38000, ZR38500 and ZR38600 architectures. Hardware block floating-point makes it optimum for Dolby AC-3 and complex digital audio signal processing applications.

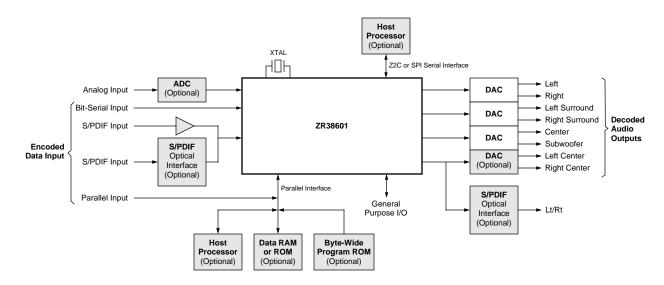

Because of its programmable high performance and high level of integration, the ZR38601 is unusually flexible in meeting a wide range of system requirements at the lowest possible system cost. At the low end it can provide standard fixed decoding functions with only a DAC and an optical interface for the S/PDIF input in addition to the oscillator crystal. At the high end it can

provide eight channels of output, analog input, long-delay memories, custom operating features and the ability to be upgraded with downloaded  $SiliconSoftware^{TM}$  product enhancements. Yet all of this flexibility comes without design complexity. Highly configurable standard functions with a simple command structure minimize software development, while a full set of development tools are available for the highly-custom product developer.

The ZR38601 is suitable for primarily audio applications such as Audio/Visual home theater receivers, Digital Audio Broadcast (DAB), 3-D audio, six-channel speaker systems and Karaoke processors; primarily video applications like SDTV and HDTV stereo television receivers, digital cable and satellite TV set-top boxes; and multimedia applications with both audio and video like Multimedia PCs and the Digital Video Disk (DVD) players.

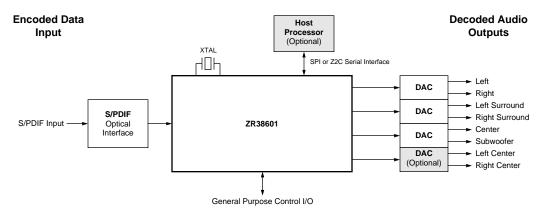

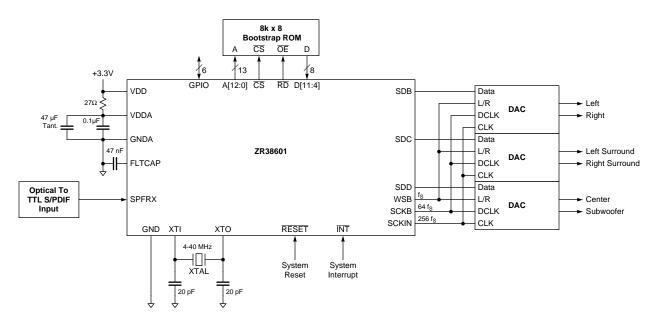

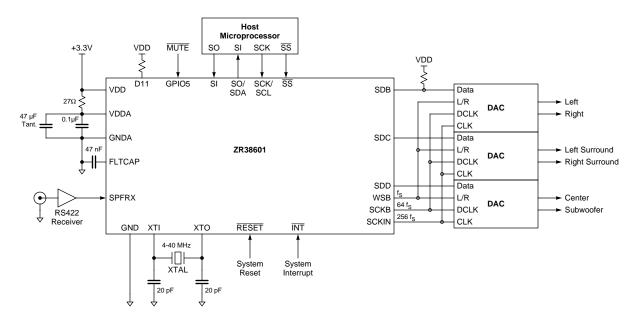

Figure 1. A Typical Low-Parts-Count ZR38601 System

### **GENERAL DESCRIPTION**

The Zoran ZR38601 is the latest digital audio processing member of the ZR38000 high performance programmable digital signal processor product line. It is especially configured with peripherals, I/O capability and software for digital audio. Today, quality digital audio starts with a primary decoding function and adds appropriate data stream protocols and interfaces with I/O configurations to match the application. The ZR38601 has these primary decode and protocol software functions and yet has processing cycles left for additional product-distinguishing features. The ZR38601 also has the necessary flexibility in system I/O and hardware configuration.

The ZR38601 is pin and instruction-set compatible with the earlier ZR38600, but with a higher 50-MIPS processing rate and larger internal program and data RAMs and ROM. These give new 96-kHz sample rate S/PDIF decoding and increased processing cycles and memories for additional functions. New hardware features are a programmable timer, a Z2C serial host interface and more support for the 24-bit I/O data formats.

### **Functions**

AC-3 and MPEG with variations are the primary decoding functions in use today. The ZR38601 has these and their associated test function with the required set-up, operation and system functions to make them usable in an end-user product. In addition, an ever increasing number of *SiliconSoftware* functions can add special enhancing and differentiating features to products.

#### **Primary Decoding and Test Functions**

#### AC-3

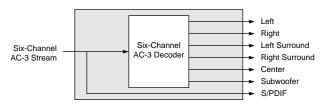

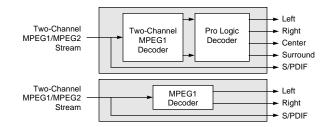

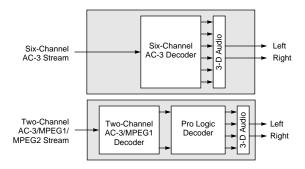

The figure shows the simultaneous S/PDIF input and 5.1 channel DAC (Digital-to-Analog Converter) outputs of this primary digital audio function, the six-channel AC-3 decoder.

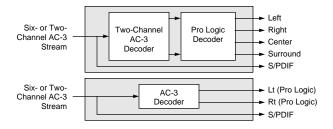

Or with four channels of Pro Logic output in either of two DAC forms: four channels directly or to an analog Pro Logic decoder.

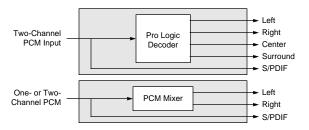

#### PCM + Pro Logic

With two-channel PCM inputs the choice of functions is fourchannel Pro Logic decoding or two-channel stereo mixing, including upmixing from only one input channel to two.

#### **MPEG**

The MPEG1 decoder accepts either MPEG1 or MPEG2 input streams and produces either Pro Logic DAC outputs or two-channel stereo in DAC form.

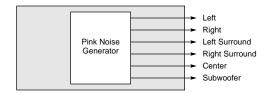

### Pink Noise

A six-channel pink pseudo-random noise generator function is included for user testing of speaker balance in their listening space. Individual speakers can be enabled in any combination.

#### SiliconSoftware™ Functions

SiliconSoftware is a group of additional functions for the ZR38601 provided by Zoran or third-party suppliers that can add special features now or provide new functions in the future.

### 3-D Audio

Currently there are six providers of 3-D audio which gives the effect of a three-dimensional sound field with only two speakers. These functions are Aureal A3D, Dolby Virtual Surround, Harman VMAx, QSound QSurround<sup>TM</sup>, Spatializer N-2-2<sup>TM</sup> and

SRS TruSurround. They work with either two- or six-channel inputs and the AC-3 or MPEG decoders.

### Bass Management

Selected low-frequencies can be redirected to different speakers with Bass Management. Useful with all types of decoding to compensate for the types of speakers used.

#### DVD - Linear PCM

Special provisions are included for data formats and synchronization for AC-3/MPEG decoding with 3-D audio and bass management for Digital Video Disk (DVD) applications.

#### Hall Effects/Music Modes

Adds the natural acoustical effects of a performance environment to the original recording environment.

#### Home THX5.1

Theater THX for use in consumer home entertainment systems.

### Karaoke Processing

Voice cancellation, pitch-shifting and echo and reverberation.

#### Custom Functions, Etc.

Product designers can always add custom functions and variations, often with very simple software additions.

### **Operation and Set-Up Functions**

These control the simple start and stop operation of the decoding functions and determine the initial hardware operation and configuration.

### System Functions

These functions control the real-time operation including interface transactions, program loading and in-circuit testing.

# **System Configurations**

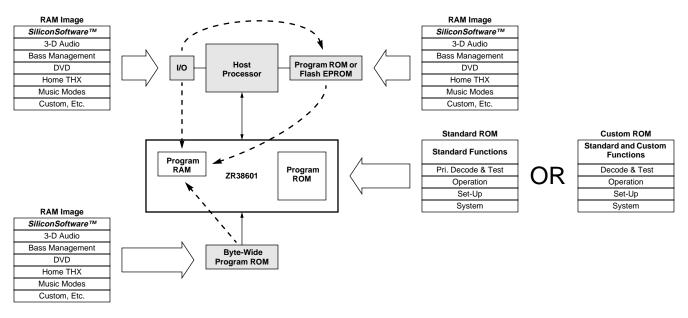

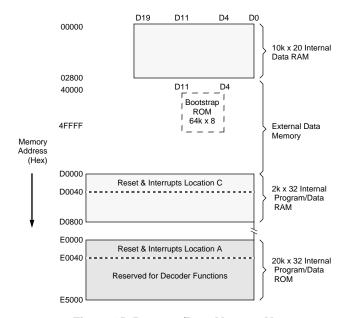

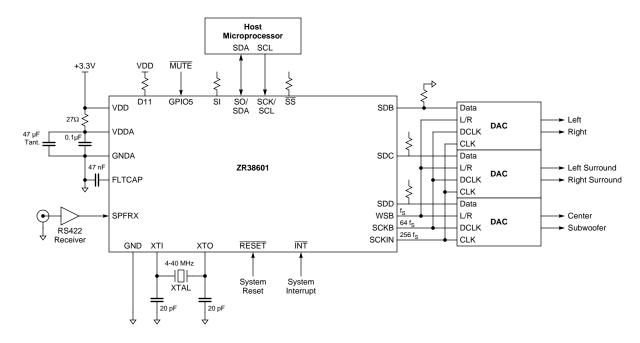

The ZR38601 is highly self-contained and can work with few external parts as shown in Figure 1. However it is very flexible in accommodating the needs of larger, higher performance systems. Figure 2 shows all of the possible options that are supported to make a complete system.

#### Hosts

The ZR38601 does not require a host microprocessor but if there is one in the system it may be used to advantage. Either the bit-serial SPI (Small Peripheral Interface) or Z2C interface, or a byte-wide parallel interface may be used.

#### Data Input/Output

The encoded digital input data stream can use a bit-serial or byte-parallel interface or S/PDIF receiver with the ZR38601 either a master or slave. Up to six-channels of analog signals can be input in bit-serial ADC (Analog-to-Digital Converter) formats in a master or slave mode.

Figure 2. ZR38601 Composite System Block Diagram

Decoded audio outputs can be up to eight channels in bit-serial DAC formats or six encoded channels from the S/PDIF transmitter.

### Memory

External memory is not normally needed but can be added for program and/or digital audio data. Additional program storage

gives different or additional functions when a host is not used and allows a choice of ROM technologies to be employed for future upgradability. External data memory may be required for functions with long acoustical delays, input buffering or large data tables. Program memory interfaces are byte-wide to provide minimum cost and parts count.

### **FUNCTIONAL DESCRIPTION**

A more complete description of the ZR38601 software's operation and configurations and its hardware configurations follows.

# **Software - Operation**

One of the major benefits of the ZR38601 is its ease of use for the system developer under a broad range of system requirements. Standard functions are easy to use, yet custom features can be added without falling back to custom software development with complicated real-time operating system considerations or detailed I/O protocols. This follows from the fact that all software functions are supplied with a common command and response sequence for use with a host or an API (Application Programming Interface) for calling from an internal program. And each provides for adding custom functions in not just one but a series of ways which depend upon the complexity of the custom function.

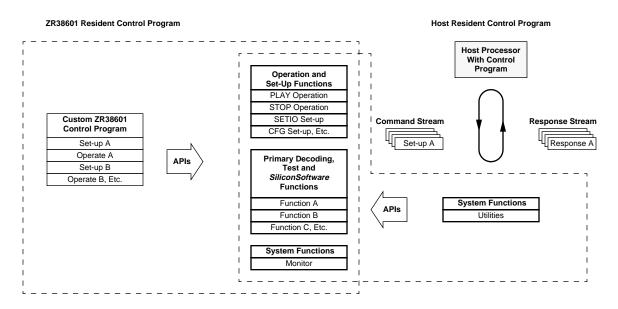

This is shown schematically in Figure 3 where the operation, set-up, primary, and *SiliconSoftware* functions are shown in the middle. Using the system utilities to maintain the communications with the host, the host can issue a sequence of commands

with responses to control the ZR38601's operation. The utilities issue API calls to the functions. All of the software development can be limited to the host microprocessor even when feature types of variations in operation are based on getting information back from the ZR38601's operation.

Alternatively, the control information in the commands can be entered in a sequence of API calls issued from a custom program running internally on the ZR38601 processor. Now no host is required.

With either a host command/response stream or API calls, custom functions in native ZR38001 code can be added without losing the benefits of the ease of use in the common structure.

Table 1 is a summary of the commands and responses for the standard primary, operation and set-up functions. Note there are read and write commands to the ZR38601 and responses back from the ZR38601 to the host. Responses are due to commands during normal operations that are in progress or from certain specific commands with read commands following.

Figure 3. ZR38601 Operation Control: Commands from a Host or Calls from a ZR38601 Resident Program

**Table 1: Standard Function Command and Response Summary**

| Class Name            |            | Description                                                                                          |  |  |  |  |  |

|-----------------------|------------|------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Write Command         |            | Commands to ZR38601 to perform a specific function                                                   |  |  |  |  |  |

| Primary Decoding      | AC3        | Select AC-3 or AC-3 + Pro Logic decoder function                                                     |  |  |  |  |  |

| And Test<br>Functions | PCMPROL    | Select PCM or Pro Logic decoder functions with PCM input and mixer function                          |  |  |  |  |  |

| Functions             | MPEG       | Select MPEG or MPEG + Pro Logic decoder function                                                     |  |  |  |  |  |

|                       | PNG        | Select pink noise generator function                                                                 |  |  |  |  |  |

|                       | USER       | Select user defined function                                                                         |  |  |  |  |  |

| Operation             | PLAY       | Resume selected function operation and unmute audio output                                           |  |  |  |  |  |

| Functions             | MUTE       | Mute audio output without stopping the selected operation                                            |  |  |  |  |  |

|                       | UNMUTE     | Restore muted audio output while continuing the selected operation                                   |  |  |  |  |  |

|                       | STOP       | Stop operation, retain data in input buffer and mute audio output                                    |  |  |  |  |  |

|                       | STOPF      | Stop operation, flush the data in the input buffer and mute audio output                             |  |  |  |  |  |

|                       | STAT       | Return decoder status information using the READ command                                             |  |  |  |  |  |

|                       | SPDIFSTAT  | Return the S/PDIF input channel status                                                               |  |  |  |  |  |

|                       | GETPTC     | Return the PTC and STC values for timing synchronization                                             |  |  |  |  |  |

|                       | NOP        | Not a command, does not affect operation. Will return a Progress response.                           |  |  |  |  |  |

| Set-Up Functions      | PLLTAB     | Set the PLL programmable registers                                                                   |  |  |  |  |  |

|                       | PLLCFG     | Define the PLL configuration                                                                         |  |  |  |  |  |

|                       | CFG        | Configure the ZR38601 I/O to the specific system hardware                                            |  |  |  |  |  |

|                       | SETSTC     | Set the system time clock and video delay                                                            |  |  |  |  |  |

|                       | VER        | Return 32-bit ROM version number using the READ command                                              |  |  |  |  |  |

|                       | BOOT       | Load and execute the N parameter words of bootstrap program                                          |  |  |  |  |  |

|                       | SPDIFCS    | Write the S/PDIF output channel status                                                               |  |  |  |  |  |

|                       | PARAM      | Define parameters for special functions                                                              |  |  |  |  |  |

|                       | INTRP      | Interpret: load and execute four parameter words as a ZR38001 instruction                            |  |  |  |  |  |

|                       | SETIO      | Set, test and return general purpose single-bit I/O registers                                        |  |  |  |  |  |

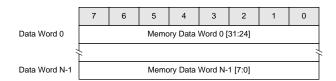

|                       | POKE       | Load N 32-bit words to the core processor RAM at the given start address                             |  |  |  |  |  |

|                       | PEEK       | Read N 32-bit words from core processor RAM at the given start address                               |  |  |  |  |  |

| Read Command          |            | Commands to ZR38601 to return Reply words to the host                                                |  |  |  |  |  |

|                       | READ       | Command to ZR38601 to return a Reply word after specific commands                                    |  |  |  |  |  |

| Reply Response        |            | Data words returned to the host as the result of sending specific commands followed by READ commands |  |  |  |  |  |

|                       | AC3STATR   | Status and information about the AC-3 stream                                                         |  |  |  |  |  |

|                       | PCMPROLR   | Status and information about the PCM or Pro Logic stream                                             |  |  |  |  |  |

|                       | MPEGSTATR  | Status and information about the MPEG stream                                                         |  |  |  |  |  |

|                       | PNGSTATR   | Status and information about the PNG stream                                                          |  |  |  |  |  |

|                       | VERR       | Four byte version number of ROM read by VER command                                                  |  |  |  |  |  |

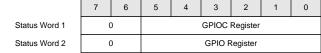

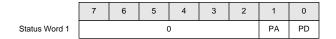

|                       | SETIOR     | Two words of GPIOC and GPIO registers                                                                |  |  |  |  |  |

|                       | PLLR       | Two bits which indicate the PLL lock status                                                          |  |  |  |  |  |

|                       | PEEKR      | N 32-bit words from core processor RAM specified by PEEK command                                     |  |  |  |  |  |

|                       | SPDIFSTATR | S/PDIF input channel status                                                                          |  |  |  |  |  |

|                       | GETPTCR    | PTC and STC values of 32 bits each                                                                   |  |  |  |  |  |

| Progress Response     | •          | Data words returned to host in the normal process of sending any command                             |  |  |  |  |  |

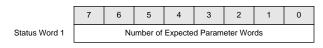

|                       | EXPECT     | Expected number of parameter words still to be received from host                                    |  |  |  |  |  |

|                       | ISTATUS    | Interpreter status                                                                                   |  |  |  |  |  |

#### **Software - Functions**

### Primary Decoding and Test Functions

### AC-3

The major modes of operation of the Dolby Digital AC-3 decoder function are summarized in Table 2. Choices are for input and output ports and their formats including operation with audio/video synchronization (AVS), constant or request driven PES packetized inputs and the linear PCM of DVD.

AC-3 input decoding rates are up to 640 kbits per second. Full selection can be made for speaker configuration, dynamic range compression, downmixing, delays, filtering and error concealment strategy. The Karaoke downmixing is also supported including with downloaded Karaoke coefficients.

### PCM + Pro Logic

With two-channel PCM inputs, the choice of functions is fourchannel Pro Logic decoding or two-channel stereo mixing. Selection can be made for speaker configuration, downmixing, delays and surround filtering.

#### **MPEG**

The MPEG1 decoder function accepts either MPEG1 or MPEG2 input streams and produces either Pro Logic or two-channel stereo outputs in DAC form. Selection can be made for speaker configuration, dynamic range compression, downmixing, delays and surround filtering.

### Pink Noise

This is a six-channel pink (equal energy per constant proportional bandwidth) pseudo-random noise generator test function. It is for user testing of speaker balance in a listening space. The six

individual speakers can be enabled in any combination at a single adjustable level, with or without a band-limiting filter.

### SiliconSoftware™ Functions

#### 3-D Audio

There are six third-party providers of 3-D audio using the ZR38601. This function gives the effect of a three-dimensional sound field with only two speakers. These certified functions are Aureal A3D, Dolby Virtual Surround, Harman VMAx, QSound QSurround<sup>™</sup>, Spatializer N-2-2<sup>™</sup> and SRS TruSurround. They work with either two- or six-channel inputs and the AC-3, MPEG and Pro Logic decoders as shown in Table 3.

### Bass Management

Depending upon the speakers used in a listening area, it can be desirable to alter the distribution of the bass frequencies between speakers. A choice of speaker configurations is provided and of low-pass cut-off frequencies for 80, 100 or 120 Hertz in the simplest form. The full function allows the low-pass and high-pass filter coefficients to be downloaded along with individual speaker sound levels.

Bass management works with either two- or six-channel inputs and the AC-3, MPEG and Pro Logic decoders. It does not work with 3-D audio although some 3-D audio functions include certain bass management features.

#### DVD - Linear PCM

In addition to the audio/video synchronization (AVS) and request driven PES packetized input features of the standard decode functions, this DVD function has 3-D audio capability and bass management. It works with two-, six- or eight-channel PCM inputs and the AC-3, MPEG and Pro Logic decoders.

Table 2: Primary Decoding and Test Function Options Summary

|                                         |                            |                                       | Input |                            | Output                   |                             |                     |               |

|-----------------------------------------|----------------------------|---------------------------------------|-------|----------------------------|--------------------------|-----------------------------|---------------------|---------------|

| Primary<br>Decoding Or<br>Test Function | Data<br>Stream             | Serial Port<br>A, S/PDIF,<br>Parallel | AVS   | MPEG2<br>PES<br>Packetized | DVD<br>PES<br>Packetized | Function                    | Serial DAC<br>Ports | S/PDIF Port G |

| AC3                                     | 6-Channel                  | SA, S/P, P                            | Yes   | Yes                        | Yes                      | 6-Channel AC-3              | B,C,D               | Input Stream  |

|                                         | AC-3                       |                                       |       |                            |                          | 2-Channel Pro Logic encoded | В                   |               |

|                                         | 2-Channel                  | SA, S/P, P                            | Yes   | Yes                        | Yes                      | 4-Channel Pro Logic         | B,C,D               |               |

|                                         | AC-3                       |                                       |       |                            |                          | 2-Channel AC-3              | В                   |               |

| PCM + Pro Logic                         | 2-Channel                  | SA, S/P, P                            | No    | No                         | No                       | 4-Channel Pro Logic         | B,C,D               | Input Stream  |

|                                         | PCM                        |                                       |       |                            |                          | 2-Channel PCM Mixed         | В                   | 1             |

| MPEG                                    | MPEG1                      | SA, S/P, P                            | Yes   | Yes                        | Yes                      | 4-Channel Pro Logic         | B,C,D               | Input Stream  |

|                                         |                            |                                       |       |                            |                          | 2-Channel MPEG1             | В                   |               |

|                                         | MPEG2 SA, S/P, P Yes Yes Y |                                       | Yes   | 4-Channel Pro Logic        | B,C,D                    |                             |                     |               |

|                                         |                            |                                       |       |                            |                          | 2-Channel MPEG1             | В                   |               |

| PNG                                     | -                          | -                                     | -     | -                          | -                        | 6-Channel Pink Noise        | B,C,D               | -             |

### Hall Effects/Music Modes

Short and long term delays and reverberation are added to multichannel PCM inputs with this function. Delay coefficients are downloaded to simulate various acoustical environments (concert halls, churches, stadiums, etc.)

#### Home THX5.1

This function, when used in a two-chip set connected in cascade, provides the sound of the Lucasfilm theater THX in the home listening environment. The input chips runs all of the standard decoding functions and passes its PCM outputs to the second chip for the THX5.1 processing which included full bass management, decorrelation, timbre matching and re-equalization and individually programmable channel delays.

#### Karaoke Processing

In addition to the Karaoke input mixing features of the standard decode functions, this is true Karaoke processing with voice cancellation, pitch shifting, voice echo and reverberation and bass management. External data memory may be required for this function.

# Operation and Set-Up Functions

Custom Functions, Etc.

The User function allows developers to easily add custom functions using their own native ZR38001 code, yet retain the ease of control of the command and response structure of the ZR38601.

The operation functions, summarized in Table 1, are the realtime start and stop commands needed for system control once the primary decoding function has been selected. Also included are commands to get the input channel and decoding status to monitor on-going operation. The PTC and STC time clocks can also be monitored to insure audio and video synchronization.

The set-up functions configure both the hardware and software before operation starts or as major operational changes are made. Hardware configuration and initialization includes the phase-locked loops (PLLs), system clocks and the input/output (I/O). Software can be put in place through the host processor from its I/O or memory system. It may be in the form of custom commands and their parameters or directly executable native code for the core DSP processor.

Table 3: SiliconSoftware Function Options Summary

|                          |                        |                                               | Input                                      | C                                                                               | Output              |                                     |

|--------------------------|------------------------|-----------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------|---------------------|-------------------------------------|

| SiliconSoftware Function |                        | Serial Port A,<br>E or F, S/PDIF,<br>Parallel | Standard Function<br>Source                | Function                                                                        | Serial DAC<br>Ports | S/PDIF Port G                       |

| 3-D Audio: Aureal A3D    |                        | SA, S/P, P                                    | AC-3, AC-3 + Pro Logic,                    | 2-Channel 3-D Audio                                                             | В                   | Input Stream                        |

|                          | Dolby Virtual Surround |                                               | PCM + Pro Logic, MPEG,<br>MPEG + Pro Logic |                                                                                 |                     |                                     |

|                          | Harman VMAx            |                                               | MPEG + PIO LOGIC                           |                                                                                 |                     |                                     |

|                          | QSound QSurround™      |                                               |                                            |                                                                                 |                     |                                     |

|                          | Spatializer N-2-2™     |                                               |                                            |                                                                                 |                     |                                     |

|                          | SRS TruSurround        |                                               |                                            |                                                                                 |                     |                                     |

| Bass Manag               | ement                  | SA, S/P, P                                    | All of the above                           | Redirect low frequencies to different speakers                                  | B, C, D             | Input Stream                        |

| DVD                      |                        | SA, P                                         | All of the above + 8-<br>Channel PCM       | Decoding, 3-D and bass management                                               | B, C, D, G          | Input Stream<br>Unless 8-Ch.<br>PCM |

| Hall Effects/I           | Music Modes            | SA, S/P, P                                    | PCM                                        | Add room effects                                                                | B, C, D             | Input Stream                        |

| Home                     | Decoding Chip          | SA, S/P, P                                    | AC-3, AC-3+Pro Logic,                      | Two chip set decodes and                                                        | B, C, D             | Input Stream                        |

| THX5.1                   | THX Processing Chip    | SA, SE, SF                                    | PCM+Pro Logic, MPEG,<br>MPEG + Pro Logic   | produces THX outputs                                                            | B, C, D             | -                                   |

| Karaoke Processing       |                        | S/P & SF or SA<br>& SF                        | AC-3, PCM, MPEG                            | Voice cancellation, pitch shifting, echo and reverberation and bass management. | B, C, D             | Input Stream                        |

### System Functions

The remaining portion of the standard ZR38601 functions that reside in every program ROM are the system functions, shown schematically in Figure 4.

#### Monitor

This is the simple real-time operating system mini-kernel used by all ZR38601 functions in normal operation.

#### Utilities

System utilities maintain operation of the various I/O interfaces that are shared between functions. These include the serial audio data ports, the serial SPI or Z2C host interface and the parallel host interface for commands and responses. The utilities also include the initial and reset bootstrap routine that determines the start-up ROM and executes its initialization process.

### ICE Debug

For In-Circuit Emulation debugging using the ZR38000 Family Simulator, the monitor is used in a mode for single-step and breakpoint execution of programs.

# **Software - System Configurations**

As a result of the ZR38601's ability to be configured from a low-cost, fixed-function device to a very flexible, full capability audio processor, there are many choices as to how the software is

configured which are related to the system hardware configuration. Important considerations are if a host is used and if only standard commands are to be used. Table 4 summarizes the most common configurations and their relative benefits.

Figure 4 illustrates possible sources and residences of the software for different hardware configurations. Starting with the on-chip program ROM, it can be either the standard version or with custom functions as shown. Custom and *SiliconSoftware* functions can be available for downloading into the on-chip program RAM from three sources as indicated by the dashed arrows. If there is no host they must be loaded from the external byte-wide program ROM. With a host it may be from the host's own non-volatile memory (ROM or flash EPROM typically) or through its I/O peripherals such as on-line links or movable memory media like floppy disks.

# **Hardware - System Configurations**

All of the hardware shown in Figure 2, the composite system block diagram on page 3, is supported in the ZR38601. The choices for host, data input and output, and external memory are summarized in Table 5. Those that are supported by the standard functions with the standard commands are noted. Individual *SiliconSoftware* functions support additional configurations. For example, the Karaoke Processing supports the bit-serial ADC data input and the external data RAM required for pitch correction and voice reverberation.

**Table 4: Software Configurations**

| Configu                                                                        | ration                                         | Description                                                                                                                                    | Benefits                                                                                                                               |  |

|--------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| Host Operation Using Standard Commands                                         | Internal Standard ROM                          | Download program RAM with <i>SiliconSoftware</i> for additional current and future functions.                                                  | Moderate flexibility for current and future functions with only host S/W development.                                                  |  |

| Host Operation Using<br>Standard and Custom<br>Commands and APIs               | Internal Standard ROM                          | Download program RAM with <i>SiliconSoftware</i> from host with current, future and custom functions.                                          | Moderate customization and flexibility for current and future functions. Moderate host overhead.                                       |  |

|                                                                                | Internal Standard ROM +<br>External Custom ROM | Download program RAM with <i>SiliconSoftware</i> from external ROM for current and custom functions or from host for future functions.         | Maximum customization with maximum flexibility for current and future functions. Low host overhead except for future functions.        |  |

|                                                                                | Internal Custom ROM                            | Download program RAM with SiliconSoftware from host for future functions.                                                                      | Moderate customization with moderate flexibility for future functions. Minimum cost and low host overhead except for future functions. |  |

| Stand Alone (No Host)<br>Operation Using Standard<br>and Custom Functions with | Internal Standard ROM +<br>External Custom ROM | Standard and custom functions with control through GPIO port.                                                                                  | Low cost, maximum customization. Broad choice of ROM technologies for flexibility for future.                                          |  |

| APIs                                                                           | Internal Custom ROM                            | Standard and custom functions with control through GPIO port. No future flexibility without internal ROM non-recurring engineering (NRE) cost. | Lowest recurring cost with maximum customization.                                                                                      |  |

#### Hosts

A host microprocessor is not required for the ZR38601's operation. A custom program, in either the internal ROM or an external ROM with the standard internal ROM, is sufficient. Control of the operation is then through the GPIO (General Purpose Input/Output) ports.

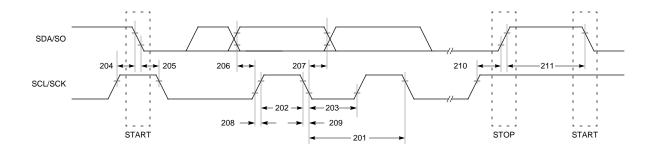

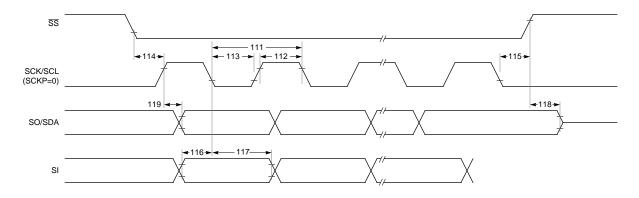

However, the greatest flexibility is available if a host is used. The least costly in external hardware is a serial host interface. The four-wire SPI (Small Peripheral Interface) or two-wire Z2C signals (see Table 6) connect directly to most low-cost micro-controllers. There is no speed penalty with a host serial interface and it leaves the parallel interface free for use with external memories.

The ZR38601's parallel interface can be used for a byte-wide connection to a microprocessor host along with byte-wide I/O with the standard command support. The full 16-bits of the parallel interface can be used for an I/O connection if called in the developer's software. Note that the parallel interface can not be used concurrently for the host and I/O while it is being used for external data or program memory.

#### Data Input/Output

The primary data input is the single-wire digital audio interface receiver. This conforms fully to S/PDIF, IEC-958, AES/EBU and EIAJ CP-340 consumer standards. All standard sampling rates are supported for raw or packetized bitstreams as well as the data driven master operation using the  $\overline{\mbox{DREQ}}$  signal on the GPIO0 port. Serial port A or the byte-wide parallel interface may alternately be used for the channel bitstream as master or slave. The parallel interface also provides data driven master operation, but it can not be used concurrently with external memory in the system.

Up to six channels of bit-serial ADC data can be input as master or slave in a wide variety of industry formats when required by SiliconSoftware functions.

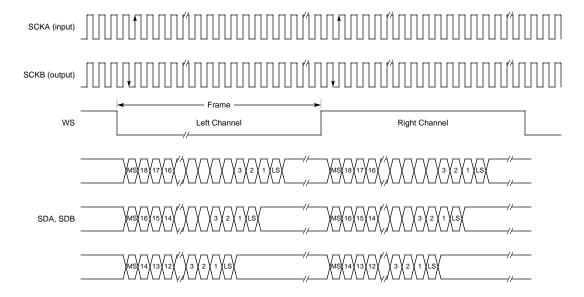

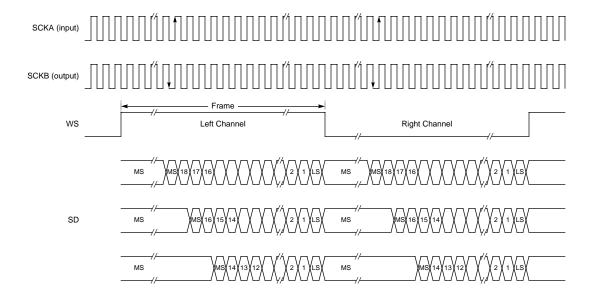

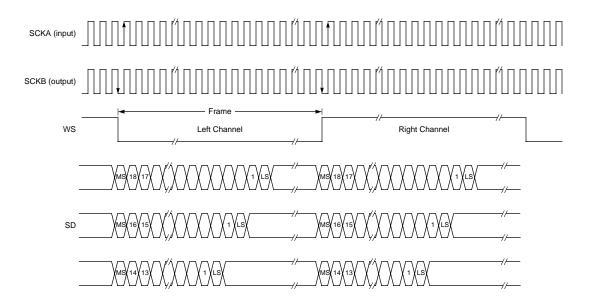

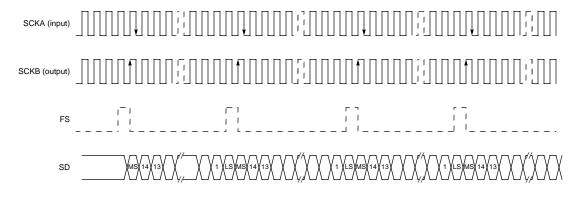

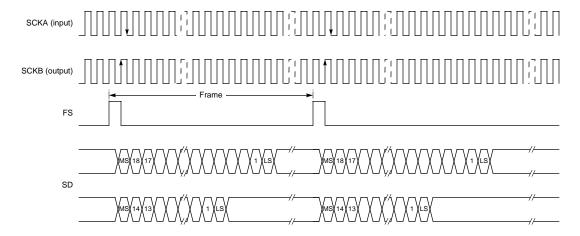

Up to eight channels of bit-serial DAC data can be output as master or slave in the same variety of industry formats including I<sup>2</sup>S and EIAJ with word, frame and frameless synchronization. Ports B,C and D are used by standard 6-channel functions with Port G in addition for 8-channel *SiliconSoftware* functions. Otherwise Port G serves as a S/PDIF master transmitter.

#### **External Memory**

The 20 address and 16 data lines of the parallel port allow a wide choice of external memory for program and data storage if needed for *SiliconSoftware* functions or for future flexibility. Variable wait-states are supported for slower, lower cost memories. Not used concurrently with parallel host or I/O interfaces.

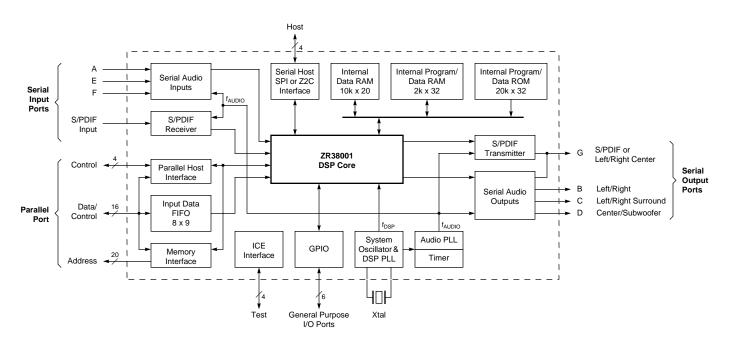

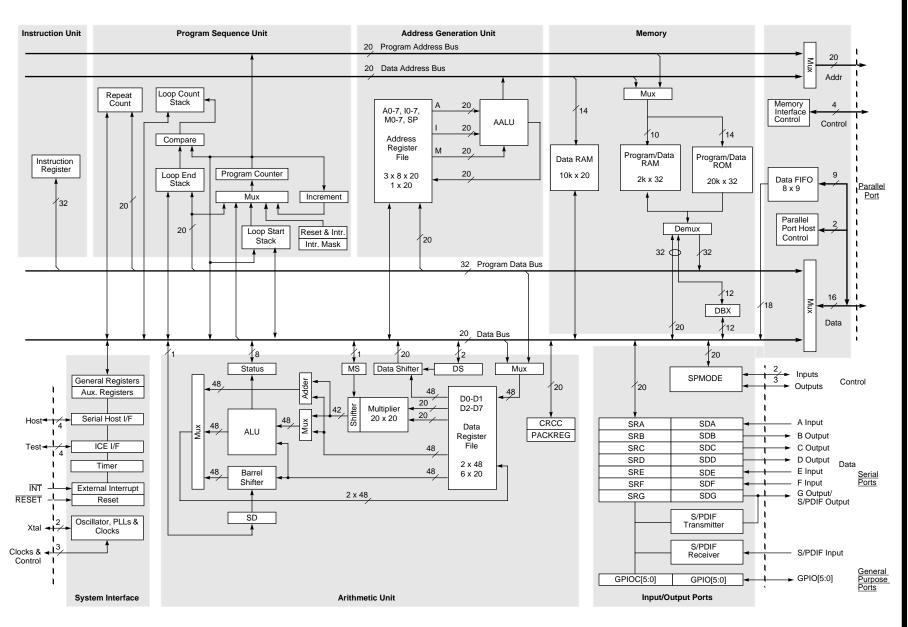

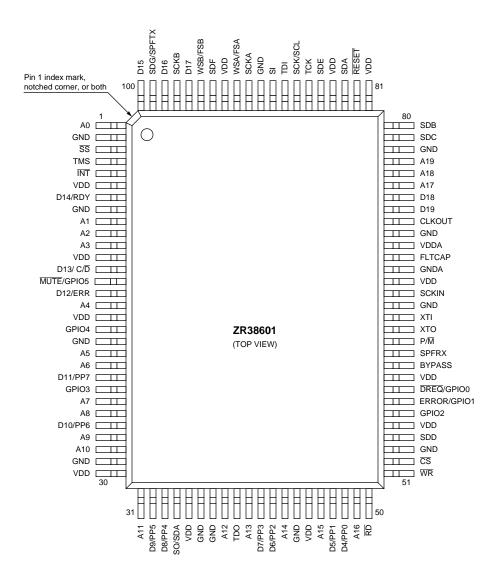

# **Hardware - Digital Audio Processor**

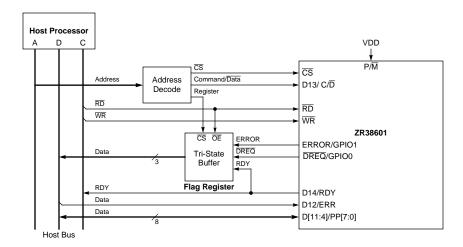

The ZR38601 is composed of the interfaces, memories and system clocks that surround the ZR38001 DSP core shown in Figure 5. The individual signals of each of the interfaces and power supply connection are summarized in Table 6.

The figure illustrates the sharing of the serial output port G with the S/PDIF transmitter and the multiple functions of the parallel port for the external host, I/O and memories. Note from Table 6 how the un-used of the 16-bit memory data lines are utilized for additional control when the parallel byte-wide interface is employed for the external host and I/O.

Using standard functions, three of the six GPIO signals are dedicated as a MUTE input, an I/O data request output, DREQ, and an I/O error output, ERROR.

Figure 4. Software Memory Configurations

**Table 5: System Hardware Configurations and Standard Command Support**

| Hardwai     | re Configuration     | Hardware Configuration Description                                                                          | Standard Command Support                                |  |  |

|-------------|----------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|

| Host        | None                 | Custom program using parallel and/or GPIO interface for control.                                            | None. Requires custom internal or external program ROM. |  |  |

|             | Bit-serial Interface | Industry standard four-wire SPI duplex or two-wire Z2C half-duplex.                                         | Yes.                                                    |  |  |

|             | Parallel Interface   | Byte-wide selectable for I/O and Commands. Not possible concurrent with external memory.                    | Yes.                                                    |  |  |

| Data Input  | S/PDIF Channel       | Standard single-wire receiver.                                                                              | Yes.                                                    |  |  |

|             | Bit-serial Channel   | Serial Port A is a flexible slave or data driven master with DREQ.                                          | Yes.                                                    |  |  |

|             | Parallel Channel     | Byte-wide master, slave or data-driven master with DREQ. Not possible concurrent with external memory.      | Yes.                                                    |  |  |

|             | ADC bit-serial       | Up to six channels as a flexible master or slave.                                                           | No.                                                     |  |  |

| Data Output | DAC bit-serial       | Up to eight channels on Ports B, C, D and G as flexible master or slave.                                    | Yes for 6-channel ports B, C and D.                     |  |  |

|             | S/PDIF Channel       | Standard single-wire transmitter on Port G. Master only.                                                    | Yes, Port G.                                            |  |  |

| External    | Program ROM          | Byte-wide or 16-bit-wide loading of internal 32-bit program RAM.                                            | Yes, byte-wide only.                                    |  |  |

| Memory      | Data RAM and/or ROM  | Up to 16-bit wide memory for custom functions requiring large delay memory (RAM) or parameter tables (ROM). | Not required for standard functions.                    |  |  |

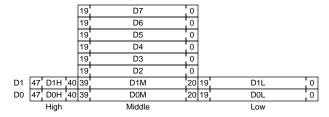

Internal memories are large: the 20-kwords of 32-bit program/data ROM is augmented with an addition 2-kwords of down-loadable RAM. The data only memory is a 10-kword RAM in the 20-bit data word precision.

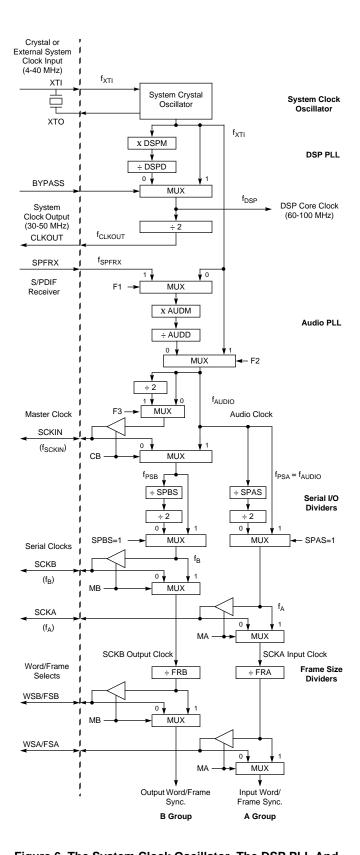

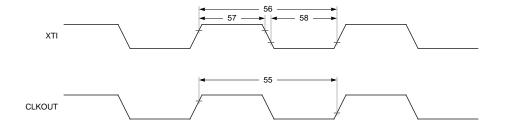

The two programmable phase-locked-loops (PLLs), one for the DSP core ( $f_{DSP}$ ) and one for the audio serial ports ( $f_{AUDIO}$ ) allow independent selection of these two critical internal clock rates. This is particularly important when the ZR38601 system oscillator is not determined by its own external crystal, but rather from

a predetermined system clock frequency. Having two PLLs lets the DSP core synchronously operate at its maximum 50 MIPS rate ( $f_{DSP} = 100$  MHz) for processing while the serial I/O operates at the standard sample rates of 32, 44.1, 48 or 96 kHz, regardless of whether the predetermined system clock frequency is a common sub-multiple.

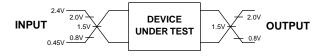

The power supply is 3.3 Volts for lower power consumption, yet all I/O signals are 5.0 Volt tolerant for use in 5.0-Volt systems.

Figure 5. ZR38601 Simplified Block Diagram

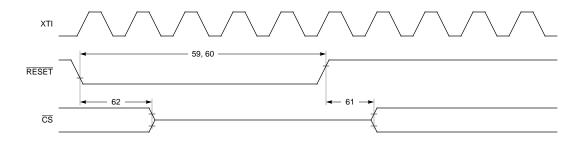

Table 6: ZR38601 Signal Description Summary

| Name            | Number   | Type [1] | Description                                                                                                                         |  |  |  |  |

|-----------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                 |          | •        | Parallel Port (40)                                                                                                                  |  |  |  |  |

| A[19:0]         | 20       | 0        | Address bus of parallel port                                                                                                        |  |  |  |  |

| D[19:15]        | 5        | I/O      | Data bus of parallel port when selected for external memory $(P/\overline{M} = 0)$                                                  |  |  |  |  |

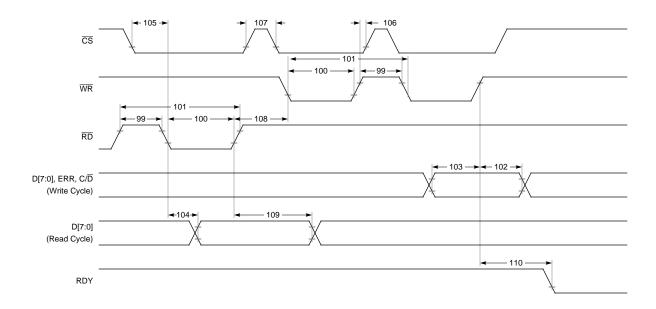

| D14/RDY         | 1        | I/O or O | Data bus $(P/\overline{M} = 0)$ or Ready output signal of parallel port when selected for parallel I/O $(P/\overline{M} = 1)$       |  |  |  |  |

| D13/ C/D        | 1        | I/O or I | Data bus $(P/\overline{M} = 0)$ or Command/Data select input of parallel port when selected for parallel I/O $(P/\overline{M} = 1)$ |  |  |  |  |

| D12/ERR         | 1        | I/O or I | Data bus $(P/\overline{M} = 0)$ or Error input signal of parallel port when selected for parallel I/O $(P/\overline{M} = 1)$        |  |  |  |  |

| D[11:4]/PP[7:0] | 8        | I/O      | Data bus of parallel port when selected for external memory ( $P/\overline{M} = 0$ ) or Parallel Port I/O ( $P/\overline{M} = 1$ )  |  |  |  |  |

| CS              | 1        | I/O      | Chip Select output for external memory or Chip Select input for parallel I/O                                                        |  |  |  |  |

| RD              | 1        | I/O      | Read enable output for external memory or Read enable input for parallel I/O                                                        |  |  |  |  |

| WR              | 1        | I/O      | Write enable output for external memory or Write enable input for parallel I/O                                                      |  |  |  |  |

| P/M             | 1        | I        | Parallel I/O or Memory select for parallel port. Determined at time of RESET.                                                       |  |  |  |  |

|                 |          | ı        | Serial Ports (13)                                                                                                                   |  |  |  |  |

| SPFRX           | 1        | I        | S/PDIF Receiver input port                                                                                                          |  |  |  |  |

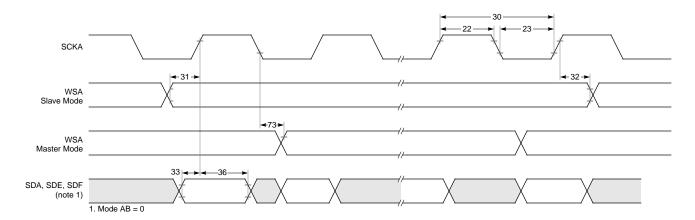

| SDA, SDE, SDF   | 3        | ı        | Serial Data inputs. Ports A, E and F.                                                                                               |  |  |  |  |

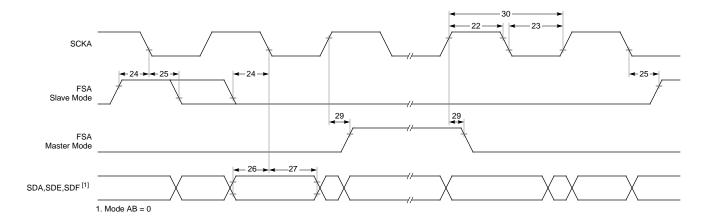

| WSA/FSA         | 1        | I/O      | Word Select or Frame Synchronization for input ports. An output when a master, an input when a slave.                               |  |  |  |  |

| SCKA            | 1        | I/O      | Serial Clock for input ports. An output when a master, an input when a slave.                                                       |  |  |  |  |

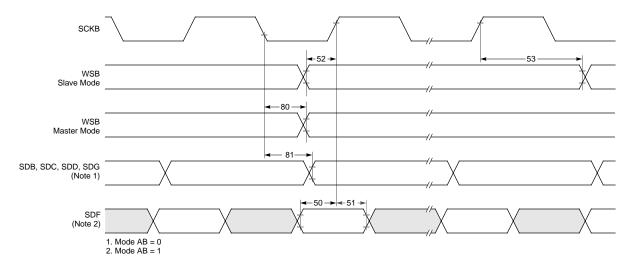

| SDB             | 1        | 0        | Serial left and right Data output. Port B. Also, at RESET defines SPI/ZZC for host serial interface.                                |  |  |  |  |

| SDC             | 1        | 0        | Serial left and right surround Data output. Port C. Also, at RESET defines Z2CADR[0] of Z2C address.                                |  |  |  |  |

| SDD             | 1        | 0        | Serial center and sub-woofer Data output. Port D. Also, at RESET defines Z2CADR[1] of Z2C address.                                  |  |  |  |  |

| SDG/SPFTX       | 1        | 0        | Serial Data output. Port G or S/PDIF Transmitter port. Also, at RESET defines the SCKP value.                                       |  |  |  |  |

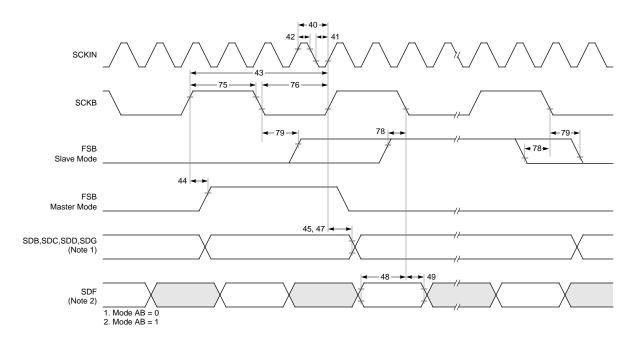

| WSB/FSB         | 1        | I/O      | Word Select or Frame Synchronization for output ports. An output when a master, an input when a slave.                              |  |  |  |  |

| SCKB            | 1        | I/O      | Serial Clock for output ports. An output when a master, an input when a slave.                                                      |  |  |  |  |

| SCKIN           | 1        | I/O      | Serial master Clock output or master clock Input for output ports                                                                   |  |  |  |  |

| CORIT           | <u>'</u> | 1/0      | General Purpose Ports (6)                                                                                                           |  |  |  |  |

| MUTE/GPIO5      | 1        | I or I/O | Mute input signal or can be programmed as General Purpose Input/Output 5                                                            |  |  |  |  |

| GPIO[4:2]       | 3        | 1/0      | Can be programmed as General Purpose Input/Output 4, 3 and 2                                                                        |  |  |  |  |

| ERROR/GPIO1     | 1        | O or I/O | Error output signal or can be programmed as General Purpose Input/Output 1                                                          |  |  |  |  |

| DREQ/GPI00      | 1        | O or I/O | Data Request output signal or can be programmed as General Purpose Input/Output 0                                                   |  |  |  |  |

| DREQ/GFIO0      | <u>'</u> | 0 01 1/0 | Serial Host Interface (4)                                                                                                           |  |  |  |  |

| SI              | 1        |          | Host Serial interface data Input. Also, at RESET defines Z2CADR[5] of Z2C address.                                                  |  |  |  |  |

| SO/SDA          | 1        | I/O/T    | SPI host Serial interface data Output or Serial Data for Z2C                                                                        |  |  |  |  |

| SCK/SCL         | 1        | 1/0/1    | SPI host Serial interface Clock input or Slave Clock input for Z2C                                                                  |  |  |  |  |

| SS              | 1        | ı        | SPI host serial interface Slave Select input. Also, at RESET defines Z2CADR[4] of Z2C address.                                      |  |  |  |  |

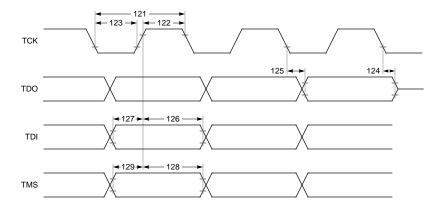

| 33              | ļ        | Į.       | ICE Interface (4)                                                                                                                   |  |  |  |  |

| TDI             | 1        | 1        | ICE Test interface Data Input                                                                                                       |  |  |  |  |

| TDO             | 1        | O/T      | ICE Test interface Data Output                                                                                                      |  |  |  |  |

| TCK             | 1        | I I      | ICE Test interface Clock input                                                                                                      |  |  |  |  |

| TMS             | 1        | i i      | ICE Test interface Glock input                                                                                                      |  |  |  |  |

| TIVIS           | ı        | !        | System Interface (7)                                                                                                                |  |  |  |  |

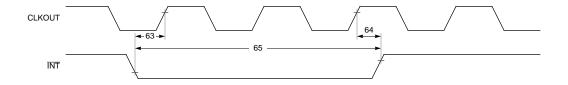

| ĪNT             | 1        | 1        | External Interrupt request input                                                                                                    |  |  |  |  |

| RESET           | 1        | ı        | Reset input to start operation in known state                                                                                       |  |  |  |  |

| XTI             | 1        |          | External system clock Input or connection to external crystal, at frequency f <sub>XTI</sub>                                        |  |  |  |  |

|                 |          | 1        | 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7                                                                                             |  |  |  |  |

| XTO             | 1        | 0        | Output connection to external crystal                                                                                               |  |  |  |  |

| CLKOUT          | 1        | 0        | Clock Output from the ZR38601 at frequency f <sub>DSP</sub> /2                                                                      |  |  |  |  |

| BYPASS          | 1        |          | Bypass internal DSP core PLL to use external system clock input on XTI                                                              |  |  |  |  |

| FLTCAP          | 1        | l        | External Filter Capacitor connection for PLL. A value of 47nF is recommended.                                                       |  |  |  |  |

| \/DD            | 40       | D        | Power (26)                                                                                                                          |  |  |  |  |

| VDD             | 12       | Power    | +3.3 volt power supply                                                                                                              |  |  |  |  |

| VDDA            | 1        | Power    | +3.3 volt power supply, Analog for PLL                                                                                              |  |  |  |  |

| GND             | 12       | Power    | Power supply Ground                                                                                                                 |  |  |  |  |

| GNDA            | 1        | Power    | Power supply Ground, Analog for PLL                                                                                                 |  |  |  |  |

|                 |          |          | Total (100)                                                                                                                         |  |  |  |  |

<sup>1.</sup> O = Output, I = Input, T = Tri-state in normal use. May be different at Reset time as shown in Table 23 on page 42.

# STANDARD FUNCTIONS DESCRIPTION

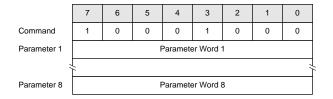

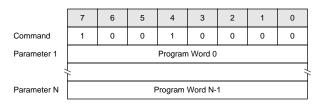

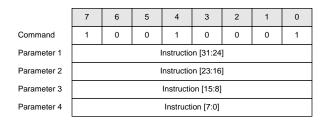

The ZR38601 standard functions are selected and controlled by the commands and responses shown in Tables 7 and 8. These are the commands, parameters and responses sent and received by a microprocessor over the serial host interface or the parallel host interface when a parallel host is used. The Applications Program Interfaces (APIs) for the AC-3, Pro Logic, Pink Noise, etc. functions are similar. These APIs are used by a developers program executing on the core processor.

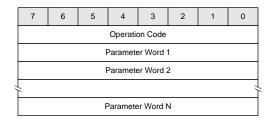

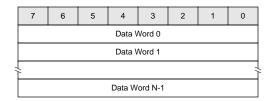

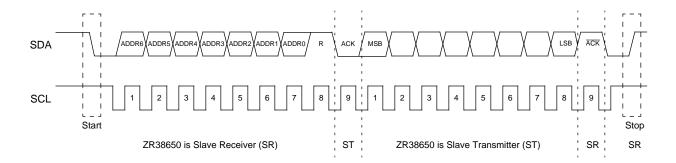

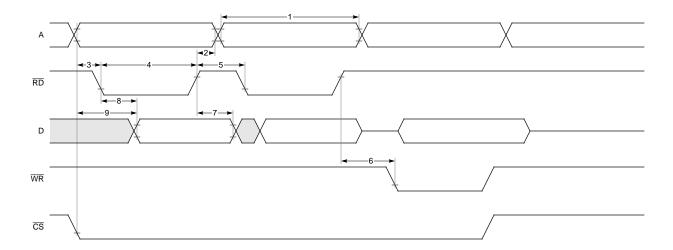

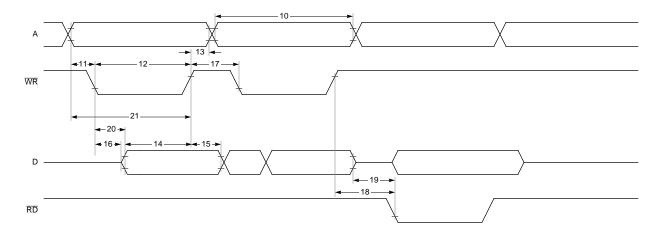

Transfers between a host and the ZR38601 with the SPI are full-duplex with the host being the master. For every command sent a word is received back from the ZR38601. Transfers with the parallel host interface or the serial Z2C interface are half-duplex with the host master. Then the host must initiate the read for the response after each command is sent. The commands are sent only from the host and are in the general form shown.

There are two classes of commands: those that Write to the decoder and those that Read back from the decoder. The Write commands may have parameter words in addition to the basic operation code. The Write commands are of three types as shown in Table 7: those that choose primary decoding and test functions (e.g., AC3), those that govern operation (e.g., STOP or PLAY) and those that set-up operation (e.g., CFG).

Table 7: Standard Function Command Summary (Host to ZR38601 Transfers)

| Class                | Name      | Operation code (Hex) | Number of parameter words | Description                                                                   |

|----------------------|-----------|----------------------|---------------------------|-------------------------------------------------------------------------------|

| Write Comma          | and       |                      | 1                         | Commands to ZR38601 to perform a specific function or operation               |

| Primary              | AC3       | 85                   | 8                         | Select AC-3 and Pro Logic decoder function, either six- or two-channel output |

| Decoding<br>And Test | PCMPROL   | 86                   | 8                         | Select PCM or Pro Logic decoder functions with PCM input and mixer function   |

| Functions            | MPEG      | 87                   | 8                         | Select MPEG or MPEG + Pro Logic decoder function                              |

|                      | PNG       | 83                   | 8                         | Select pink noise generator function                                          |

|                      | USER      | 88                   | 8                         | Select user defined function                                                  |

| Operation            | PLAY      | 8A                   | 0                         | Resume selected function operation and unmute audio output                    |

| Functions            | MUTE      | 8B                   | 0                         | Mute audio output without stopping the selected operation                     |

|                      | UNMUTE    | 89                   | 0                         | Restore muted audio output while continuing the selected operation            |

|                      | STOP      | 8C                   | 0                         | Stop operation, retain data in input buffer and mute audio output             |

|                      | STOPF     | 8D                   | 0                         | Stop operation, flush the data in the input buffer and mute audio output      |

|                      | STAT      | 8E                   | 0                         | Return decoder status information using the READ command                      |

|                      | SPDIFSTAT | 8F                   | 0                         | Return the S/PDIF input channel status                                        |

|                      | GETPTC    | 9A                   | 0                         | Return the PTC and STC values                                                 |

|                      | NOP       | 80                   | 0                         | Not a command, does not affect operation. Will return a Progress response.    |

| Set-Up               | PLLTAB    | 98                   | 6                         | Set the PLL programmable registers                                            |

| Functions            | PLLCFG    | 99                   | 1                         | Define the PLL configuration                                                  |

|                      | CFG       | 82                   | 8                         | Configure the ZR38601 I/O to the specific system hardware                     |

|                      | SETSTC    | 97                   | 7                         | Set the system time clock and video delay                                     |

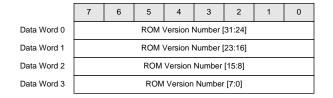

|                      | VER       | 81                   | 0                         | Return 32-bit ROM version number using the READ command                       |

|                      | BOOT      | 90                   | N                         | Load and execute the N parameter words of bootstrap program                   |

|                      | SPDIFCS   | 95                   | 4                         | Write the S/PDIF output channel status                                        |

|                      | PARAM     | 96                   | N                         | Define parameters for special functions                                       |

|                      | INTRP     | 91                   | 4                         | Interpret: load and execute four parameter words as a ZR38001 instruction     |

|                      | SETIO     | 92                   | 4                         | Set, test and return general purpose single-bit I/O registers                 |

|                      | POKE      | 93                   | 7+4N                      | Load N 32-bit words to the core processor RAM at the given start address      |

|                      | PEEK      | 94                   | 7                         | Read N 32-bit words from core processor RAM at the given start address        |

| Read Comma           | and       |                      | 1                         | Commands to ZR38601 to return Reply words to the host                         |

|                      | READ      | 00                   | 0                         | Command to ZR38601 to return a Reply word after specific commands             |

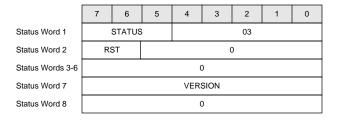

The words received back from the ZR38601 when the host initiates a transfer will be of the form:

The responses are of two types, a Reply to READ commands following specific Write commands or the Progress responses to each Write command. The Progress response is always the number of still expected parameters (EXPECT) and/or READs, followed by the response and interpreter status (ISTATUS).

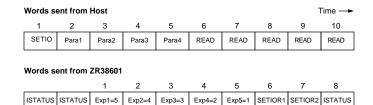

All responses to commands sent on the SPI are delayed by two words as shown in the example of the SETIO command which has both parameter words (Para 1-4) and two Reply data words (SETIOR). Note that the initial ISTATUSes returned are a response to previous READs sent by the host. There are no delays on the parallel host interface or the serial Z2C interface in the normal alternating single-byte transmit/receive protocol.

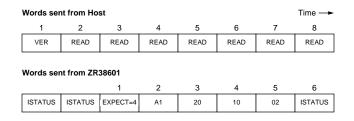

The second example below shows the response to the VER command. The EXPECT value tells the host how many bytes of information are returned by the command.

See Table 9 on page 23 for a summary of the sequence of commands, parameters, reads, responses and status.

The following descriptions explain the ZR38601's standard functions as well as the specifics of the commands used and their responses. They are in the same order as Tables 7 and 8.

Note that the descriptions on the following pages are meant to be inclusive of all functions that are currently available on the ZR38601. Some functions require that additional code be downloaded into program RAM. Likewise, note that command parameter tables are all inclusive.

Individual program and ROM release documents should be consulted to determine the exact functionality for the ROM version and program release that is being used.

Table 8: Standard Function Response Summary (ZR38601 to Host Transfers)

| Class                | Name        | Response operation code (Hex) | Number of data words | Description                                                                                          |

|----------------------|-------------|-------------------------------|----------------------|------------------------------------------------------------------------------------------------------|

| Reply Response       |             |                               |                      | Data words returned to the host as the result of sending specific commands followed by READ commands |

| Primary              | AC3STATR    | 05                            | 16                   | Status and information about the AC-3 stream                                                         |

| Decoding<br>And Test | PCMPROLR    | 04/06                         | 8                    | Status and information about the PCM or Pro Logic stream                                             |

| Functions            | MPEGSTATR   | 07                            | 12                   | Status and information about the MPEG stream                                                         |

|                      | PNGSTATR    | 03                            | 8                    | Status and information about the PNG stream                                                          |

| Set-Up               | VERR        | -                             | 4                    | Four byte version number of ROM read by VER command                                                  |

| Functions            | SETIOR      | -                             | 2                    | Two words of GPIOC and GPIO registers                                                                |

|                      | PLLR        | -                             | 1                    | Two bits which indicate the PLL lock status after a PLLCFG command                                   |

|                      | PEEKR       | -                             | 4N                   | N 32-bit words from core processor RAM specified by PEEK command                                     |

| Operation            | SPDIFSTATR  | -                             | 4                    | S/PDIF input channel status                                                                          |

| Functions            | GETPTCR - 8 |                               | 8                    | PTC and STC values of 32 bits each                                                                   |

| Progress Re          | esponse     |                               |                      | Data words returned to host in the normal process of sending any command                             |

|                      | EXPECT      | -                             | 1                    | Expected number of parameter words still to be received from host                                    |

|                      | ISTATUS     | -                             | 1                    | Interpreter status                                                                                   |

### **Function Commands**

# AC-3 Decoder + Pro Logic Function

AC3

|             | 7                  | 6       | 5   | 4     | 3    | 2 | 1   | 0 |

|-------------|--------------------|---------|-----|-------|------|---|-----|---|

| Command     | 1                  | 0       | 0   | 0     | 0    | 1 | 0   | 1 |

| Parameter 1 | PR                 | LG      | SIF | 0     | COMP |   | DMM |   |

| Parameter 2 | SF AB BCFG SW OCFG |         |     |       |      |   |     |   |

| Parameter 3 |                    | CDLY    |     | SRDLY |      |   |     |   |

| Parameter 4 |                    | HDYNRNG |     |       |      |   |     |   |

| Parameter 5 |                    |         |     | LDYN  | IRNG |   |     |   |

| Parameter 6 |                    | DSN     |     | 0     | KAR  |   | RPC |   |

| Parameter 7 | PCMSFH             |         |     |       |      |   |     |   |

| Parameter 8 |                    |         |     | PCM   | 1SFL |   |     |   |

The AC-3 Decoder function includes normal six-channel AC-3 and the two-channel AC-3 with Pro Logic output. Selection is made in the command for speaker configuration, dynamic range compression, downmixing, delays and error concealment strategy.

| PRLG | <b>Pro Logic</b> output: 0 = Off, 1 = On, 2 = Selected automatically based on input stream information.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIF  | <b>Serial Input Format</b> : 0 = Non-formatted, 1 = AC-3 S/PDIF protocol.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| COMP | <b>Compression</b> and Dialog Normalization: 0 = Custom mode 0, 1 = Custom mode 1, 2 = Line mode (dialog normalization plus high level compression), 3 = RF modulation mode (peak level compression).                                                                                                                                                                                                                                                                                                                                                      |

| DMM  | Dual Mono Mode output selection when the two input channels are unrelated: 0 = Stereo, 1 = Mono channel 0 to both, 2 = Mono channel 1 to both, 3 = Mono channels 0 and 1 summed and scaled to both.                                                                                                                                                                                                                                                                                                                                                        |

| SF   | Surround Filter for Pro Logic: 0 = Filter enabled,<br>1 = Filter (LP+NR) disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AB   | Auto-Balance for Pro Logic output: 0 = On, 1 = Off.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BCFG | Bass Redirection Configuration: 0 = No redirection, 1 = Redirect left, center, right to subwoofer for Pro-logic. All channels to subwoofer for AC-3, 2 = Redirect center to subwoofer for Pro-logic. Center, left surround and right surround to subwoofer for AC-3, 3 = Reserved.                                                                                                                                                                                                                                                                         |

| BCFG | 1 = Redirect left, center, right to subwoofer for Pro-logic.<br>All channels to subwoofer for AC-3, 2 = Redirect center to subwoofer for Pro-logic. Center, left surround and                                                                                                                                                                                                                                                                                                                                                                              |

|      | 1 = Redirect left, center, right to subwoofer for Pro-logic. All channels to subwoofer for AC-3, 2 = Redirect center to subwoofer for Pro-logic. Center, left surround and right surround to subwoofer for AC-3, 3 = Reserved.                                                                                                                                                                                                                                                                                                                             |

| sw   | 1 = Redirect left, center, right to subwoofer for Pro-logic. All channels to subwoofer for AC-3, 2 = Redirect center to subwoofer for Pro-logic. Center, left surround and right surround to subwoofer for AC-3, 3 = Reserved.  Subwoofer output channel: 0 = Off, 1 = On.  Output Speaker Configuration of Front/Surround number of speakers (for Pro Logic only OCFG 3-7 can be used): 0 = 2/0 Surround Compatible, 1 = 1/0, 2 = 2/0 Normal, 3 = 3/0, 4 = 2/1, 5 = 3/1, 6 = 2/2, 7 = 3/2. In 2/0 configurations, a mono input is directed to both output |

| HDYNRNG | High Dynamic Range scale factor controlling the depth of high-level compression. A two's complement fraction between 0.00 and 0.FE where 00 is no high-level compression and 7F is full compression. |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDYNRNG | Low Dynamic Range scale factor controlling the depth of low-level compression. A two's complement fraction between 0.00 and 0.FE where 00 is no low-level compression and 7F is full compression.    |

| DSN     | Data Stream Number for S/PDIF input. Selects which stream to decode. Range 0 -7. Normally zero.                                                                                                      |

| KAR     | Karaoke mode: 0 = Disabled, 1 = Enabled.                                                                                                                                                             |

| RPC     | Repeat Count before muting. Maximum number of consecutive block repeats before muting output.                                                                                                        |

| PCMSFH  | PCM Scale Factor High. Output scale factor, 16-bit two's complement fraction between 0.0000 and 0. FFFE. The high byte. 0000 equals zero, 7FFF equals gain of one.                                   |

| PCMSFL  | PCM Scale Factor Low. Output scale factor low byte.                                                                                                                                                  |

# PCM + Pro Logic Decoder Function

**PCMPROL**

|             | 7      | 6    | 5  | 4   | 3      | 2 | 1    | 0 |

|-------------|--------|------|----|-----|--------|---|------|---|

| Command     | 1      | 0    | 0  | 0   | 0      | 1 | 1    | 0 |

| Parameter 1 |        | (    | )  |     | DE DMM |   | им   |   |

| Parameter 2 | SF     | AB   | ВС | FG  | SW     |   | OCFG |   |

| Parameter 3 |        | CDLY |    |     | SRDLY  |   |      |   |

| Parameter 4 |        |      |    | (   | )      |   |      |   |

| Parameter 5 |        |      |    | (   | )      |   |      |   |

| Parameter 6 | 0      |      |    |     |        |   |      |   |

| Parameter 7 | PCMSFH |      |    |     |        |   |      |   |

| Parameter 8 |        |      |    | PCM | ISFL   |   |      |   |

The PCM or Pro Logic Decoder function decodes two-channel PCM into four-channel Pro Logic output or transfers to two-channel PCM output. Selection is made in the command for speaker configuration, scale factor, mixing and delay. The parameter descriptions are the same as for the AC3 command except for OCFG and with the addition of DE.

| DE   | <b>De-Emphasis filter:</b> 0 = Filter is disabled, 1 = Filter is enabled, 2 = Filter is enabled if pre-emphasis is defined in the channel status of the S/PDIF input stream. |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|