# TECHNICAL MANUAL

ZSP400 Digital Signal Processor Architecture

December 2001

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

Document DB14-000121-03, Fourth Edition (December 2001)

This document describes LSI Logic Corporation's ZSP400 Digital Signal Processing Architecture and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 1999–2001 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design, CoreWare, and ZSP are trademarks or registered trademarks of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

GL

To receive product literature, visit us at http://www.lsilogic.com.

For a current list of our distributors, sales offices, and design resource centers, view our web page located at

http://www.lsilogic.com/contacts/na\_salesoffices.html

# **Preface**

This book is the primary reference and Technical Manual of the LSI Logic ZSP400 Digital Signal Processor Architecture. It contains a functional description of the architecture and details the instruction set.

#### **Audience**

This document assumes that you have some familiarity with microprocessors and related support devices. The people who benefit from this book are:

- Engineers and managers who are evaluating the ZSP400 architecture for possible use in a system

- Engineers who are designing a device based on the ZSP400 architecture into a system

- Engineers who are programming a device based on the ZSP400 architecture

## Organization

This document has the following chapters and appendixes:

- Chapter 1, Introduction, introduces the features of the ZSP400 DSP architecture and the instruction set.

- Chapter 2, **ZSP400 Architecture Overview**, briefly describes the functional blocks that make up a ZSP400 device.

- Chapter 3, Control Registers, describes the control registers and mode bits of a ZSP400 device.

- Chapter 4, Pipeline Control Unit, describes the pipeline operation, the control register file, interrupts, and instruction grouping.

- Chapter 5, Instruction Unit, describes the instruction control unit, which is responsible for fetching instructions from memory and forwarding them to the pipeline.

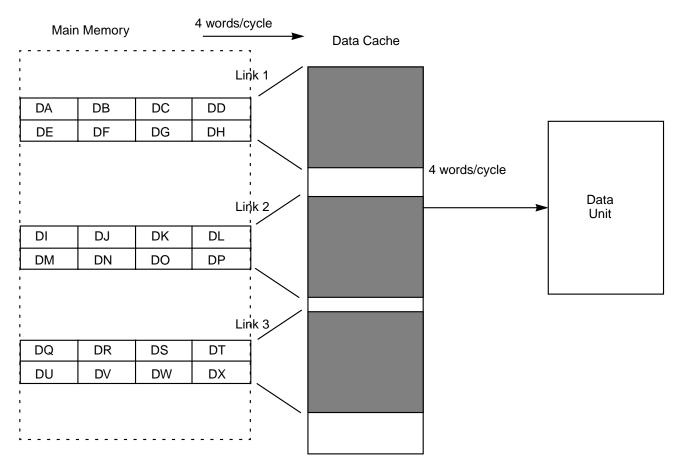

- Chapter 6, Data Unit, describes the data unit, which is responsible for fetching data from memory and forwarding it to the pipeline. The data unit also handles data linking.

- Chapter 7, Execution Unit, describes the arithmetic logic units and multiply/accumulate units.

- Chapter 8, ZSP400 Instruction Set, describes the ZSP400 instruction set in detail.

#### **Related Publications**

LSI402Z Digital Signal Processor User's Guide, document number DB15-000131-01

#### **Conventions Used in This Manual**

The first time a word or phrase is defined in this manual, it is *italicized*.

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive. Signals that are active LOW end in an "n."

Hexadecimal numbers are indicated by the prefix "0x" —for example, 0x32CF. Binary numbers are indicated by the prefix "0b" —for example, 0b0011.0010.1100.1111.

# **Contents**

| Chapter 1 | Intro | duction                                             |      |

|-----------|-------|-----------------------------------------------------|------|

| -         | 1.1   | ZSP400 Architecture Overview                        | 1-1  |

|           | 1.2   | Instruction Set Highlights                          | 1-3  |

|           | 1.3   | Available Implementations                           | 1-5  |

| Chapter 2 | ZSP4  | 00 Architecture Overview                            |      |

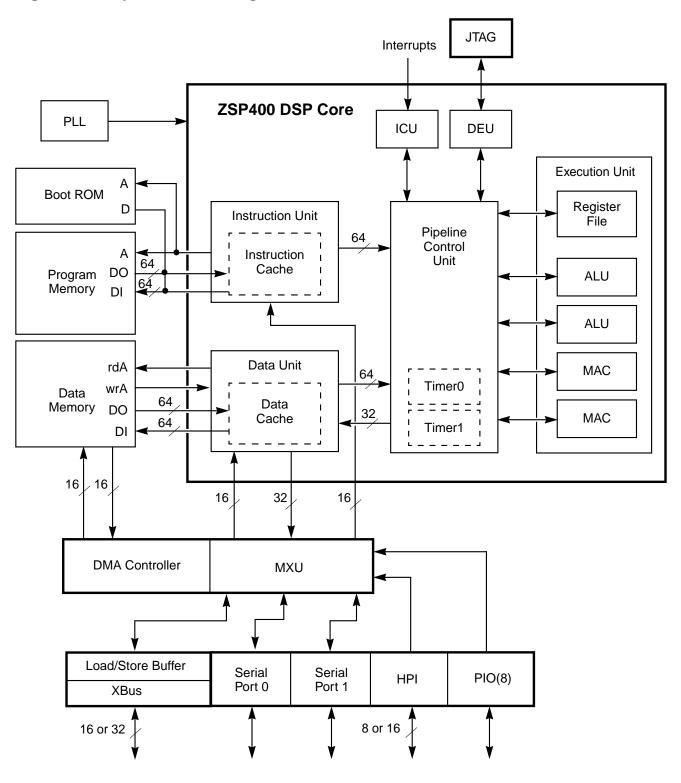

|           | 2.1   | Typical ZSP400 System                               | 2-1  |

|           | 2.2   | Control Register File                               | 2-3  |

|           | 2.3   | Pipeline Control Unit                               | 2-3  |

|           | 2.4   | Instruction Unit                                    | 2-3  |

|           | 2.5   | Data Unit                                           | 2-4  |

|           | 2.6   | Execution Unit                                      | 2-4  |

|           | 2.7   | Device Emulation Unit                               | 2-4  |

| Chapter 3 | Cont  | rol Registers                                       |      |

|           | 3.1   | Introduction                                        | 3-2  |

|           | 3.2   | Address Mode Register (%amode)                      | 3-4  |

|           | 3.3   | Circular Buffer 0 Begin Address Register (%cb0_beg) | 3-5  |

|           | 3.4   | Circular Buffer 0 End Address Register (%cb0_end)   | 3-6  |

|           | 3.5   | Circular Buffer 1 Begin Address Register (%cb1_beg) | 3-6  |

|           | 3.6   | Circular Buffer 1 End Address Register (%cb1_end)   | 3-7  |

|           | 3.7   | Device Emulation Data Register (%ded)               | 3-7  |

|           | 3.8   | Device Emulation Instruction Register (%dei)        | 3-7  |

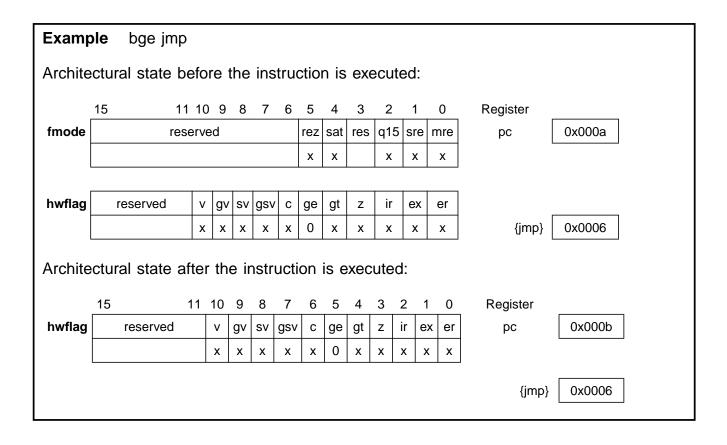

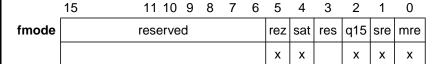

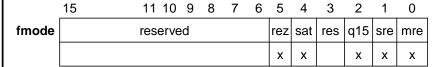

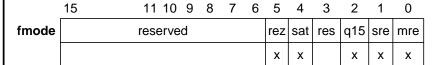

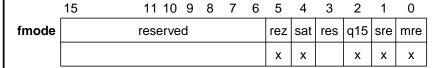

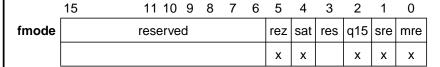

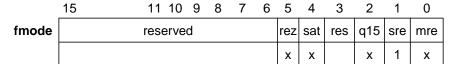

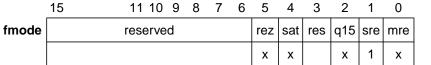

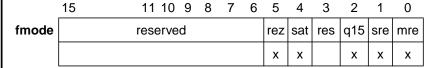

|           | 3.9   | Functional Mode Register (%fmode)                   | 3-8  |

|           | 3.10  | Guard Bits for {r1 r0} and {r3 r2}                  | 3-9  |

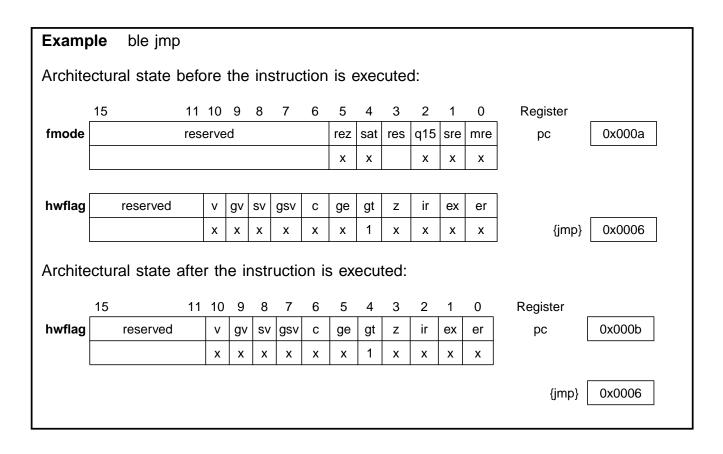

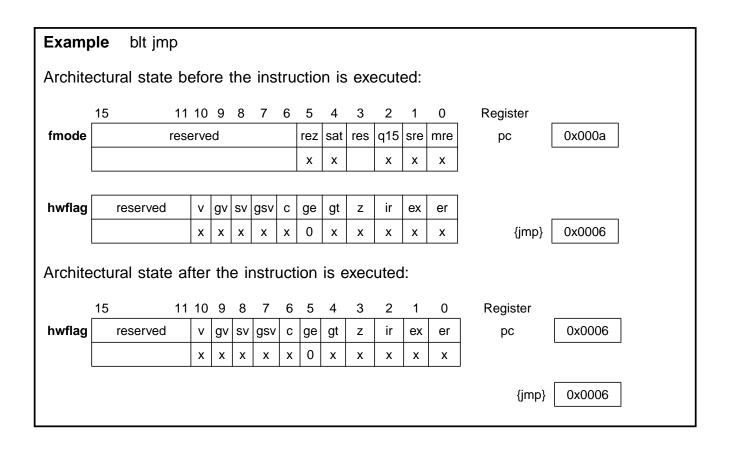

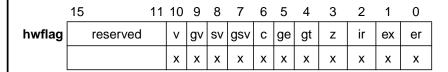

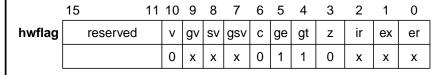

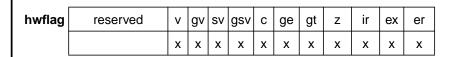

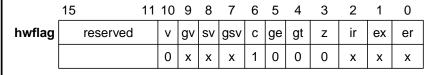

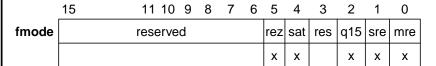

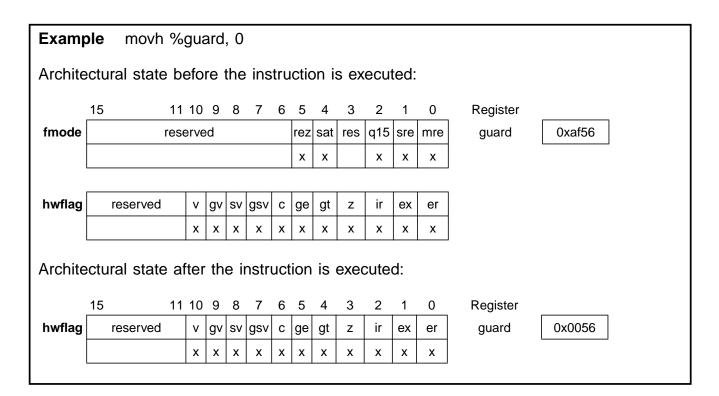

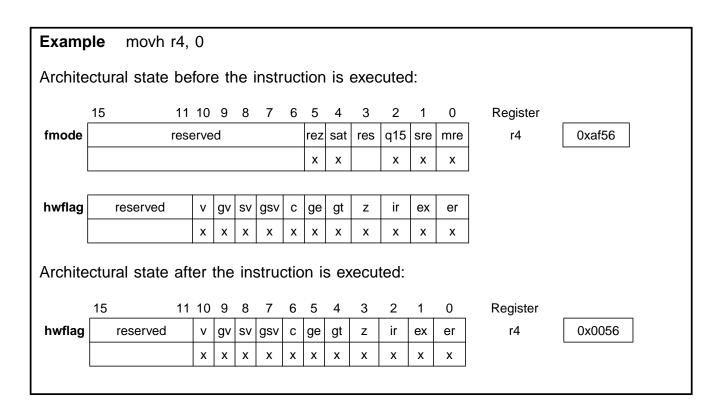

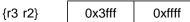

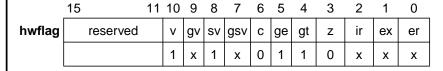

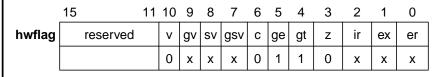

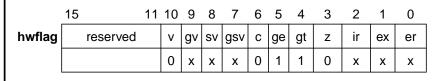

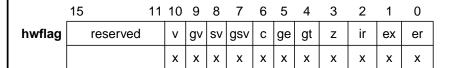

|           | 3.11  | Hardware Flag Register (%hwflag)                    | 3-10 |

|           | 3.12  | Interrupt Mask Register (%imask)                    | 3-12 |

|           | 3.13  | Interrupt Priority Register 0 (%ip0)                | 3-14 |

|           | 3.14  | Interrupt Priority Register 1 (%ip1)                | 3-15 |

| Chapter 7  |                  | ution Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |  |  |  |  |  |

|------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|--|--|

|            | 0.0              | Troverse Garry Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-10       |  |  |  |  |  |  |

|            | 6.6              | Reverse Carry Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-10       |  |  |  |  |  |  |

|            | 6.5              | Circular Buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6-8        |  |  |  |  |  |  |

|            | 6.3<br>6.4       | Data Linking Setup  Data Unit Stores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6-5<br>6-6 |  |  |  |  |  |  |

|            | 6.2              | Data Cache, Data Prefetcher, and Data Linking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-2        |  |  |  |  |  |  |

|            | 6.1              | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-1        |  |  |  |  |  |  |

| Chapter 6  | Data             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.4        |  |  |  |  |  |  |

| Ob anton C | Dete             | H-tr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |  |  |  |  |  |  |

|            | 5.3              | Branch Prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-9        |  |  |  |  |  |  |

|            |                  | 5.2.3 Issue Rate Slower than Prefetch Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-7        |  |  |  |  |  |  |

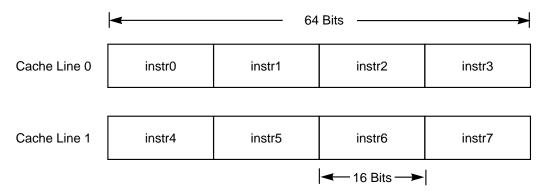

|            |                  | 5.2.2 Cache Line Straddling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-5        |  |  |  |  |  |  |

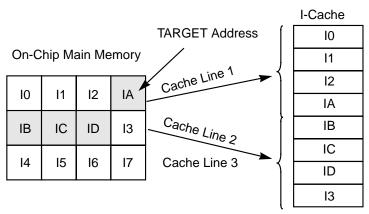

|            |                  | 5.2.1 Cache Miss Penalty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-2        |  |  |  |  |  |  |

|            | 5.2              | Instruction Cache and Prefetcher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-1        |  |  |  |  |  |  |

|            | 5.1              | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-1        |  |  |  |  |  |  |

| Chapter 5  | Instruction Unit |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |  |  |  |  |  |  |

|            | 4.5              | Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-15       |  |  |  |  |  |  |

|            | 4.4              | Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-11       |  |  |  |  |  |  |

|            | 4.3              | Grouping Rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-2        |  |  |  |  |  |  |

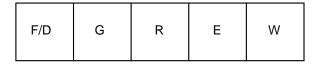

|            | 4.2              | Interlocking Pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-2        |  |  |  |  |  |  |

|            | 4.1              | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-1        |  |  |  |  |  |  |

| Chapter 4  | Pipel            | ine Control Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |  |  |  |  |  |  |

|            | 3.24             | Viterbi Traceback Register (%vitr)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-24       |  |  |  |  |  |  |

|            | 3.23             | Trap Return Program Counter Register (%tpc)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-24       |  |  |  |  |  |  |

|            | 3.22             | Timer 1 Register (%timer1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-23       |  |  |  |  |  |  |

|            | 3.21             | Timer 0 Register (%timer0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-23       |  |  |  |  |  |  |

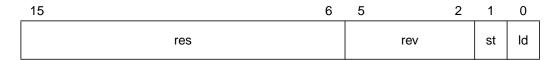

|            | 3.20             | Timer Control Register (%tc)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-22       |  |  |  |  |  |  |

|            | 3.19             | System Mode Register (%smode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-18       |  |  |  |  |  |  |

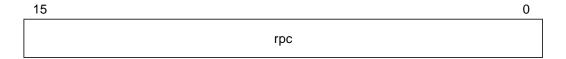

|            | 3.18             | Return Program Counter Register (%rpc)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-18       |  |  |  |  |  |  |

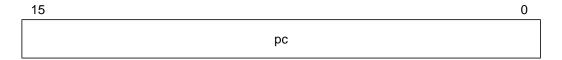

|            | 3.17             | Program Counter Register (%pc)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-18       |  |  |  |  |  |  |

|            | 3.16             | Loop Counter Registers (%loop0, %loop1, %loop2, %loop1, %loop2, %loop1, %loop2, %loop1, %loop2, %loop1, %loop2, %loop2, %loop3, %loop3 | oop3) 3-17 |  |  |  |  |  |  |

|            | 3.15             | Interrupt Request Register (%ireq)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-16       |  |  |  |  |  |  |

|           | 7.2 | Arithm                 | etic Logic Units (ALU)           | 7-2  |  |  |  |  |  |  |

|-----------|-----|------------------------|----------------------------------|------|--|--|--|--|--|--|

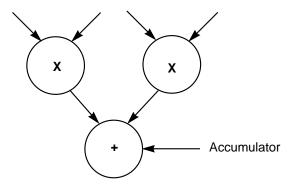

|           | 7.3 | Multipl                | y Accumulate Units (MAC)         | 7-3  |  |  |  |  |  |  |

|           | 7.4 | Genera                 | al Purpose Register File         | 7-4  |  |  |  |  |  |  |

|           | 7.5 | Shado                  | w Registers                      | 7-5  |  |  |  |  |  |  |

| Chapter 8 | ZSP | ZSP400 Instruction Set |                                  |      |  |  |  |  |  |  |

|           | 8.1 | Function               | onal and Execution Unit Usage    | 8-1  |  |  |  |  |  |  |

|           | 8.2 | Contro                 | Register–Instruction Interaction | 8-7  |  |  |  |  |  |  |

|           |     | 8.2.1                  | Move Instructions                | 8-10 |  |  |  |  |  |  |

|           |     | 8.2.2                  | MAC Instructions                 | 8-11 |  |  |  |  |  |  |

|           |     | 8.2.3                  | Arithmetic Instructions          | 8-13 |  |  |  |  |  |  |

|           |     | 8.2.4                  | Bitwise Logical Instructions     | 8-17 |  |  |  |  |  |  |

|           |     | 8.2.5                  | Bit Manipulation Instructions    | 8-18 |  |  |  |  |  |  |

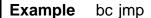

|           |     | 8.2.6                  | Branch Instructions              | 8-19 |  |  |  |  |  |  |

|           |     | 8.2.7                  | Memory Reference Instructions    | 8-23 |  |  |  |  |  |  |

|           |     | 8.2.8                  | NOP Instruction                  | 8-24 |  |  |  |  |  |  |

|           |     | 8.2.9                  | Synthetic Instructions           | 8-25 |  |  |  |  |  |  |

|           | 8.3 | Instruc                | tion Coding                      | 8-26 |  |  |  |  |  |  |

|           |     | 8.3.1                  | Instruction Opcode               | 8-26 |  |  |  |  |  |  |

|           | 8.4 | ZSP40                  | 0 Instruction Set                | 8-36 |  |  |  |  |  |  |

|           |     |                        |                                  |      |  |  |  |  |  |  |

**Customer Feedback**

Contents

# **Figures**

| 2.1 | System Block Diagram                                     | 2-2  |

|-----|----------------------------------------------------------|------|

| 3.1 | Low-Overhead Looping Construct Code Example              | 3-17 |

| 4.1 | ZSP400 Pipeline                                          | 4-1  |

| 4.2 | Interrupt Processing Flow                                | 4-14 |

| 5.1 | Cache Line Organization                                  | 5-2  |

| 5.2 | Instruction Cache Miss Penalty                           | 5-4  |

| 5.3 | Cache and Prefetcher Solve Data Alignment Dilemma        | 5-6  |

| 5.4 | Example of Prefetcher Staying Slightly Ahead of Instruct | ion  |

|     | Consumption                                              | 5-8  |

| 5.5 | Explanation of Branch Misprediction Penalties            | 5-11 |

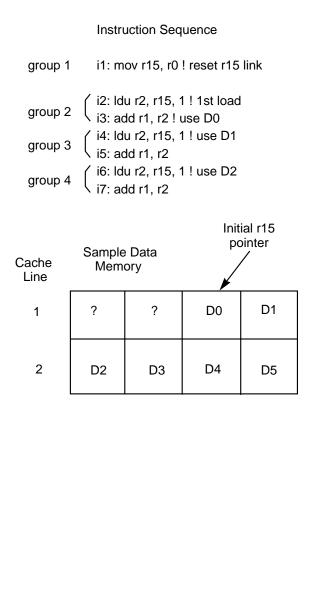

| 6.1 | Data Linking in Detail                                   | 6-4  |

| 6.2 | Example of Data Linking Setup                            | 6-6  |

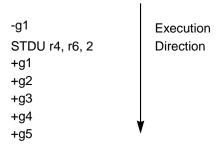

| 6.3 | Double Operand Store Straddling Two Cache Lines          | 6-7  |

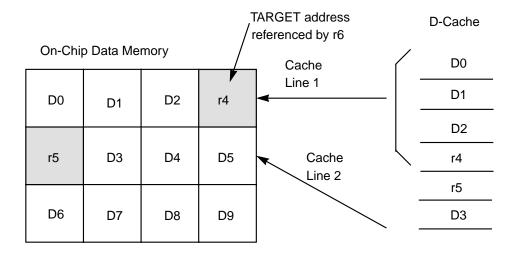

| 7.1 | Execution Unit Datapath                                  | 7-2  |

| 7.2 | Dual MAC                                                 | 7-3  |

| 7.3 | General Purpose Register File                            | 7-4  |

## **Tables**

| 3.1  | ZSP400 Control Registers                              | 3-2  |

|------|-------------------------------------------------------|------|

| 5.1  | Static Branch Prediction Rules                        | 5-9  |

| 6.1  | Circular Buffer 0 (cb0) Load Operations               | 6-8  |

| 6.2  | Circular Buffer 0 (cb0) Store Operations              | 6-9  |

| 8.1  | Instruction Functional Unit Usage and Execution Stage | 8-2  |

| 8.2  | Notational Conventions                                | 8-8  |

| 8.3  | Move Instructions                                     | 8-10 |

| 8.4  | MAC Instructions                                      | 8-11 |

| 8.5  | Arithmetic Instructions                               | 8-13 |

| 8.6  | Bitwise Logical Instructions                          | 8-17 |

| 8.7  | Bit Manipulation Instructions                         | 8-18 |

| 8.8  | Branch Instructions                                   | 8-20 |

| 8.9  | Memory Reference Instructions                         | 8-23 |

| 8.10 | NOP Instruction                                       | 8-24 |

| 8.11 | Synthetic Instructions                                | 8-25 |

| 8.12 | Instruction Set Opcode Summary                        | 8-27 |

| 8.13 | Condition Field                                       | 8-29 |

| 8.14 | op0 Field                                             | 8-30 |

| 8.15 | op1 Field                                             | 8-31 |

| 8.16 | op2 Field                                             | 8-32 |