# Bt8970

## Single-Chip HDSL Transceiver

The Bt8970 is a full-duplex 2B1Q transceiver based on Rockwell's High-Bit-Rate Digital Subscriber Line (HDSL) technology. It supports transmission of more than 18,000 feet over 26 AWG copper telephone wire without repeaters. Small size and low power dissipation makes the Bt8970 ideal for line-powered digital access, voice pairgain, and HDSL systems.

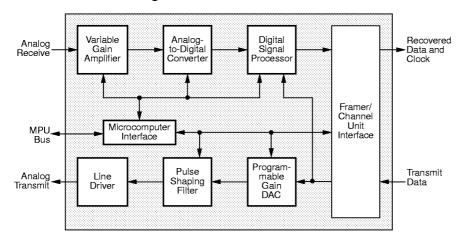

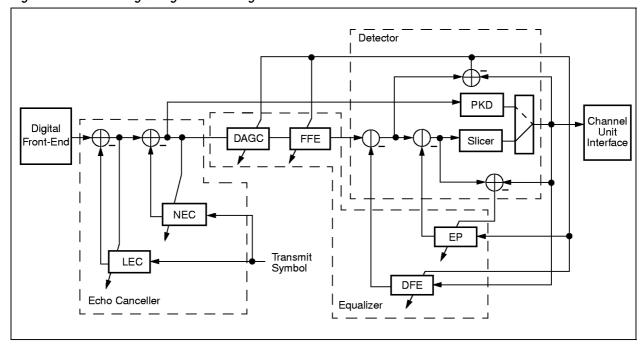

The Bt8970 is a highly integrated device that includes all of the active circuitry needed for a complete 2B1Q transceiver. In the receive portion of the Bt8970, a variable gain amplifier optimizes the signal level according to the dynamic range of the analog-to-digital converter. Once the signal is digitized, sophisticated adaptive echo cancellation, equalization, and detection DSP algorithms reproduce the originally transmitted far-end signal.

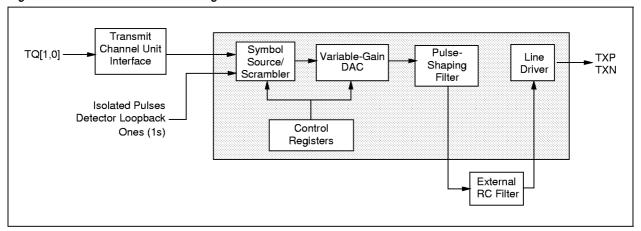

In the transmitter, the transmit source and scrambler operation is programmable via the microcomputer interface. A highly linear digital-to-analog converter with programmable gain sets the transmission power for optimal performance. A pulse-shaping filter and a low-distortion line driver generate the signal characteristics needed to drive a large range of subscriber lines at low-bit error rates.

Startup and performance monitoring operations are controlled via the microprocessor interface. C-language source code supporting these operations is supplied under a no-fee license agreement from Rockwell. The Bt8970 includes a glueless interface to both Intel and Motorola microprocessors.

#### **Functional Block Diagram**

#### **Distinguishing Features**

- · Single-chip 2B1Q transceiver solution

- All 2B1Q transceiver functions integrated into a single monolithic device

- Receiver gain control and A/D converter

- DSP functions including echo cancellation, equalization, timing recovery, and symbol detection

- Programmable gain transmit DAC, pulse-shaping filter, and line driver

- Supports operation from 160 to 1552 kbps

- Capable of transceiving over the ANSI T1E1.4/94-006 and ETSI ETR 152 HDSL test loops

- Flexible Monitoring and Control

- Glueless interface to Intel 8051 and Motorola 68302 processors

- Access to embedded filters, performance meters and timers

- Backwards compatible with Bt8952 and Bt8960 software API commands

- · Pin compatible with Bt8960

- JTAG/IEEE Std 1149.1-1990 compliant

- Single +5 V power supply operation with option for 3.3 V to reduce power consumption

- 100-pin PQFP package

- –40°C to +85°C operation

- 700 mW power consumption at 784 kbps (max using 3.3 V option)

#### **Applications**

- · E1 and T1 HDSL transport

- · Voice/data pairgain systems

- Internet connectivity

- ISDN basic-rate interface concentrators

- Extended range fractional T1/E1

- · Cellular/microcellular base stations

- Personal Communications Systems (PCS) radio ports and cell switches

### **Ordering Information**

| Order Number | Package                               | Ambient Temperature |

|--------------|---------------------------------------|---------------------|

| Bt8970EHF    | 100-Pin Plastic Quad Flat Pack (PQFP) | –40°C to +85°C      |

Copyright © 1997 Rockwell Semiconductor Systems, Inc. All rights reserved.

Print date: December 1997

Rockwell Semiconductor Systems, Inc. reserves the right to make changes to its products or specifications to improve performance, reliability, or manufacturability. Information furnished is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by its implication or otherwise under any patent or intellectual property rights of Rockwell Semiconductor Systems, Inc.

Rockwell Semiconductor Systems, Inc. products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a Rockwell Semiconductor Systems, Inc. product can reasonably be expected to result in personal injury or death. Rockwell Semiconductor Systems, Inc. customers using or selling Rockwell Semiconductor Systems, Inc. products for use in such applications do so at their own risk and agree to fully indemnify Rockwell Semiconductor Systems, Inc. for any damages resulting from such improper use or sale.

Bt is a registered trademark of Rockwell Semiconductor Systems, Inc. SLC® is a registered trademark of AT&T Technologies, Inc. Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective companies. All other marks mentioned herein are the property of their respective holders.

Specifications are subject to change without notice.

PRINTED IN THE UNITED STATES OF AMERICA

# **Table of Contents**

| List of Figures                                 | Vİ |

|-------------------------------------------------|----|

| List of Tables                                  | ix |

| 1.0 System Overview                             | 1  |

| 1.1 Functional Summary                          | 1  |

| 1.1.1 Transmit Section                          | 3  |

| 1.1.2 Receive Section                           |    |

| 1.1.3 Timing Recovery and Clock Interface       | 3  |

| 1.1.4 Microcomputer Interface                   |    |

| 1.1.5 Test and Diagnostic Interface (JTAG)      | 4  |

| 1.2 Pin Descriptions                            | 5  |

| 2.0 Functional Description                      | 11 |

| 2.1 Transmit Section                            | 11 |

| 2.1.1 Symbol Source Selector/Scrambler          | 12 |

| 2.1.2 Variable Gain Digital-to-Analog Converter | 14 |

| 2.1.3 Pulse-Shaping Filter                      |    |

| 2.1.4 Line Driver                               | 14 |

| 2.2 Receive Section                             | 15 |

| 2.2.1 Variable Gain Amplifier                   | 15 |

| 2.2.2 Analog-to-Digital Converter               | 16 |

| 2.2.3 Digital Signal Processor                  |    |

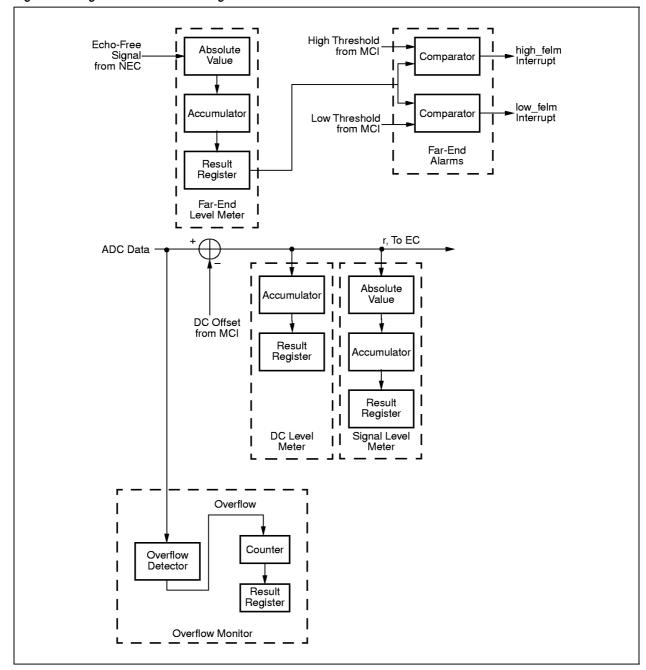

| 2.2.3.1 Digital Front-End                       | 17 |

| 2.2.3.2 Offset Adjustment                       | 18 |

| 2.2.3.3 DC Level Meter                          | 18 |

| 2.2.3.4 Signal Level Meter                      | 18 |

| 2.2.3.5 Overflow Detection                      |    |

| and Monitoring                                  |    |

| 2.2.3.6 Far-End Level Meter                     |    |

| 2.2.3.7 Far-End Level Alarm                     |    |

| 2.2.4 Echo Canceller                            |    |

| 2.2.4.1 Linear Echo Canceller (LEC)             | 19 |

| . 20<br>. 20                                                 |

|--------------------------------------------------------------|

| 20                                                           |

|                                                              |

| . 20                                                         |

| . 20                                                         |

| . 20                                                         |

| . 20                                                         |

| . 21                                                         |

| . 21                                                         |

| . 21                                                         |

| . 21                                                         |

| . 21                                                         |

| . 22                                                         |

| . 23                                                         |

| . 24                                                         |

| . 25                                                         |

| . 25                                                         |

| . 26                                                         |

| . 28                                                         |

| . 28                                                         |

| . 28                                                         |

| . 29                                                         |

| . 29                                                         |

| . 29                                                         |

| . 29                                                         |

| . 30                                                         |

| . 30                                                         |

| . 30                                                         |

| . 32                                                         |

|                                                              |

| . 33                                                         |

|                                                              |

| . 33                                                         |

| . 33<br>. 34                                                 |

| . 33<br>. 34<br>. 39                                         |

| . 33<br>. 34<br>. 39                                         |

| . 33<br>. 34<br>. 39<br>. 39                                 |

| . 33<br>. 34<br>. 39<br>. 39<br>. 40                         |

| . 33<br>. 34<br>. 39<br>. 39<br>. 40<br>. 41                 |

| . 33<br>. 34<br>. 39<br>. 40<br>. 41<br>. 41                 |

| . 33<br>. 34<br>. 39<br>. 40<br>. 41<br>. 41<br>. 42         |

| . 33<br>. 34<br>. 39<br>. 40<br>. 41<br>. 41<br>. 42<br>. 42 |

| . 33<br>. 34<br>. 39<br>. 40<br>. 41<br>. 41<br>. 42<br>. 42 |

| . 33<br>. 34<br>. 39<br>. 40<br>. 41<br>. 41<br>. 42<br>. 42 |

|                                                              |

| 3.2.12 0x0B—Transmitter Modes Register (transmitter_modes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 3.2.13 0x0C—Timer Restart Register (timer_restart)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47                                                       |

| 3.2.14 0x0D—Timer Enable Register (timer_enable)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 48                                                       |

| 3.2.15 0x0E—Timer Continuous Mode Register (timer_continuous)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48                                                       |

| 3.2.16 0x0F—Test Register (reserved2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 48                                                       |

| 3.2.17 0x10, 0x11—Startup Timer 1 Interval Register (sut1_low, sut1_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48                                                       |

| 3.2.18 0x12, 0x13—Startup Timer 2 Interval Register (sut2_low, sut2_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49                                                       |

| 3.2.19 0x14, 0x15—Startup Timer 3 Interval Register (sut3_low, sut3_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49                                                       |

| 3.2.20 0x16, 0x17—Startup Timer 4 Interval Register (sut4_low, sut4_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49                                                       |

| 3.2.21 0x18, 0x19—Meter Timer Interval Register (meter_low, meter_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 49                                                       |

| 3.2.22 0x1A, 0x1B—SNR Alarm Timer Interval Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          |

| (snr_timer_low, snr_timer_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 49                                                       |

| $3.2.23\ 0x1C, 0x1D — General\ Purpose\ Timer\ 3\ Interval\ Register\ (t3\_low,\ t3\_high) \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49                                                       |

| 3.2.24 0x1E, 0x1F—General Purpose Timer 4 Interval Register (t4_low, t4_high) $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49                                                       |

| 3.2.25 0x20—Test Register (reserved9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                                                       |

| 3.2.26 0x21—ADC Control Register (adc_control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50                                                       |

| 3.2.27 0x22—PLL Modes Register (pll_modes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51                                                       |

| 3.2.28 0x23—Test Register (reserved10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 52                                                       |

| 3.2.29 0x24, 0x25—Timing Recovery PLL Phase Offset Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |

| (pll_phase_offset_low, pll_phase_offset_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |

| 3.2.30 0x26, 0x27—Receiver DC Offset Register (dc_offset_low, dc_offset_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |

| 3.2.31 0x28—Transmitter Calibration Register (tx_calibrate)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |

| 3.2.32 0x29—Transmitter Gain Register (tx_gain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

| 3.2.33 0x2A, 0x2B—Noise-Level Histogram Threshold Register (noise_histogram_th_lo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |

| noise_histogram_th_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54                                                       |

| 3.2.34 0x2C, 0x2D—Error Predictor Pause Threshold Register (ep_pause_th_low, ep_pause_th_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 54                                                       |

| 3.2.35 0x2E—Scrambler Synchronization Threshold Register (scr_sync_th)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54                                                       |

| 3.2.36 0x30, 0x31—Far-End High Alarm Threshold Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | J-                                                       |

| (far_end_high_alarm_th_low, far_end_high_alarm_th_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54                                                       |

| (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |

| 3.2.37 0x32, 0x33—Far-End Low Alarm Threshold Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                        |

| 3.2.37 0x32, 0x33—Far-End Low Alarm Threshold Register  (far_end_low_alarm_th_low, far_end_low_alarm_th_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54                                                       |

| (far_end_low_alarm_th_low, far_end_low_alarm_th_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54                                                       |

| (far_end_low_alarm_th_low, far_end_low_alarm_th_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54<br>55                                                 |

| (far_end_low_alarm_th_low, far_end_low_alarm_th_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54<br>55<br>55                                           |

| (far_end_low_alarm_th_low, far_end_low_alarm_th_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54<br>55<br>55<br>55                                     |

| (far_end_low_alarm_th_low, far_end_low_alarm_th_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54<br>55<br>55<br>55                                     |

| (far_end_low_alarm_th_low, far_end_low_alarm_th_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54<br>55<br>55<br>55<br>57                               |

| (far_end_low_alarm_th_low, far_end_low_alarm_th_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 555<br>555<br>557<br>577<br>578                          |

| (far_end_low_alarm_th_low, far_end_low_alarm_th_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54<br>55<br>55<br>57<br>57<br>58                         |

| (far_end_low_alarm_th_low, far_end_low_alarm_th_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 555<br>555<br>557<br>557<br>558<br>558                   |

| (far_end_low_alarm_th_low, far_end_low_alarm_th_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5½<br>55<br>55<br>57<br>57<br>58<br>58<br>58             |

| (far_end_low_alarm_th_low, far_end_low_alarm_th_high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54<br>55<br>55<br>57<br>57<br>58<br>58<br>58<br>59<br>59 |

| (far_end_low_alarm_th_low, far_end_low_alarm_th_high)  3.2.38 0x34, 0x35—SNR Alarm Threshold Register (snr_alarm_th_low, snr_alarm_th_high)  3.2.39 0x36, 0x37—Cursor Level Register (cursor_level_low, cursor_level_high)  3.2.40 0x38, 0x39—DAGC Target Register (dagc_target_low, dagc_target_high)  3.2.41 0x3A—Symbol Detector Modes Register (detector_modes)  3.2.42 0x3B—Peak Detector Delay Register (peak_detector_delay)  3.2.43 0x3C—Digital AGC Modes Register (dagc_modes)  3.2.44 0x3D—Feed Forward Equalizer Modes Register (ffe_modes)  3.2.45 0x3E—Error Predictor Modes Register (ep_modes)  3.2.46 0x40, 0x41—Phase Detector Meter Register (pdm_low, pdm_high)  3.2.47 0x42—Overflow Meter Register (overflow_meter) | 54<br>55<br>55<br>57<br>57<br>58<br>59<br>59<br>59<br>60 |

|                             | 4B—Noise Level Histogram Meter Register (noise_histogram_low, histogram_high) | 60 |

|-----------------------------|-------------------------------------------------------------------------------|----|

|                             | 4D—Bit Error Rate Meter Register                                              | 00 |

|                             | neter_low, ber_meter_high)                                                    | 61 |

| , —                         | ymbol Histogram Meter Register (symbol_histogram)                             |    |

|                             | 51—Noise Level Meter Register (nlm_low, nlm_high)                             |    |

|                             | 5F— PLL Frequency Register                                                    |    |

| **                          | equency_low, pll_frequency_high)                                              |    |

|                             | EC Read Tap Select Register (linear_ec_tap_select_read)                       |    |

|                             | EC Write Tap Select Register (linear_ec_tap_select_write)                     |    |

|                             | EC Read Tap Select Register (nonlinear_ec_tap_select_read)                    |    |

|                             | EC Write Tap Select Register (nonlinear_ec_tap_select_write)                  |    |

|                             | FE Read Tap Select Register (dfe_tap_select_read)                             |    |

|                             | FE Write Tap Select Register (dfe_tap_select_write)                           |    |

|                             | cratch Pad Read Tap Select (sp_tap_select_read)                               |    |

|                             | cratch Pad Write Tap Select (sp_tap_select_write)                             |    |

|                             | qualizer Read Select Register (eq_add_read)                                   |    |

|                             | qualizer Write Select Register (eq_add_write)                                 | OC |

|                             | qualizer iviictocode nead Select negister<br>icrocode_add_read)               | 66 |

|                             | qualizer Microcode Write Select Register                                      | 00 |

|                             | icrocode_add_write)                                                           | 66 |

| 3.2.68 0x7C-0x              | 7F—Access Data Register (access_data_byte3:0)                                 | 66 |

| 4.0 Electrical & Mechanical | Specifications                                                                | 67 |

| 4.1 Absolute Maximum F      | ·<br>Ratings                                                                  | 67 |

|                             | _                                                                             |    |

| •                           | ating Conditions                                                              |    |

| 4.3 Electrical Characteris  | stics                                                                         | 69 |

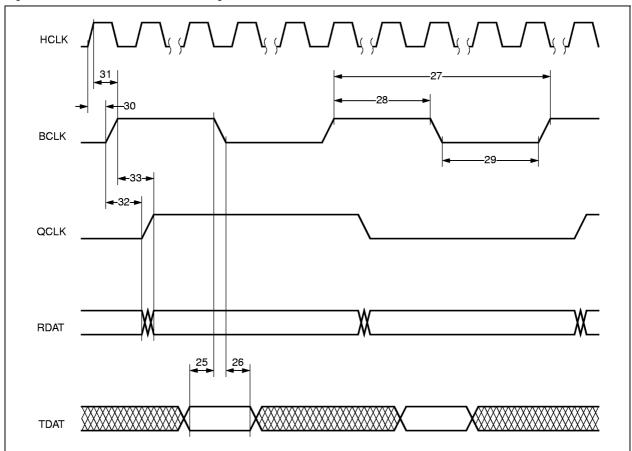

| 4.4 Clock Timing            |                                                                               | 70 |

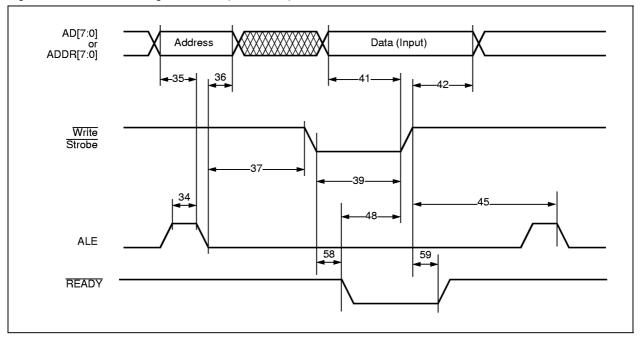

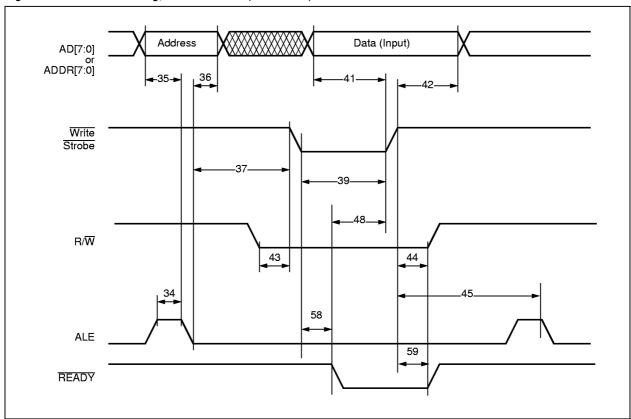

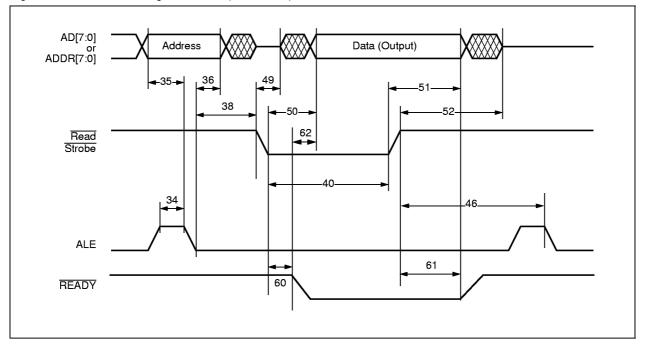

| 4.5 Channel Unit Interfac   | ce Timing                                                                     | 72 |

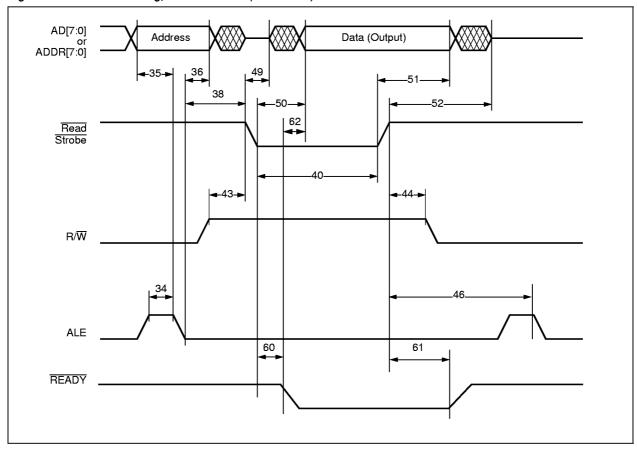

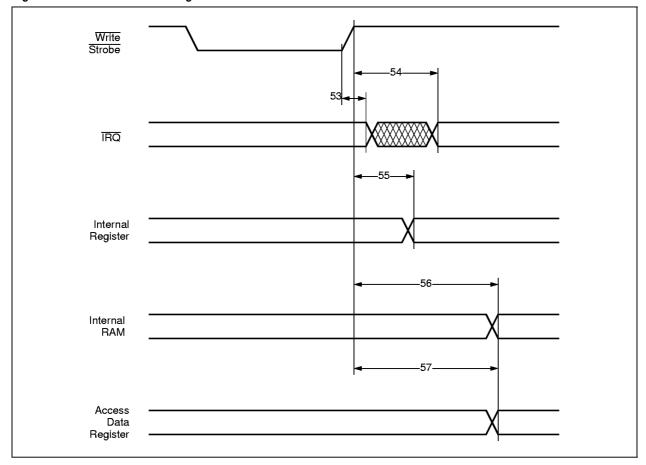

| 4.6 Microcomputer Inter     | face Timing                                                                   | 76 |

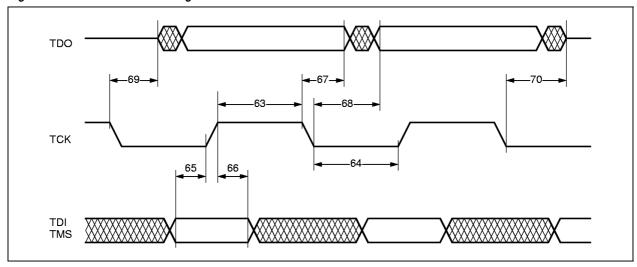

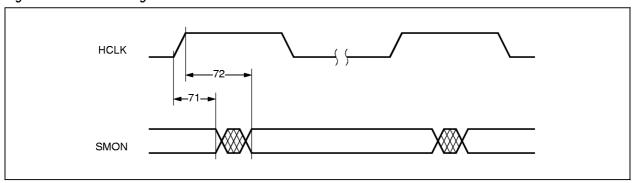

| 4.6.1 Test and D            | Diagnostic Interface Timing                                                   | 81 |

|                             | ecifications                                                                  |    |

|                             | itions                                                                        |    |

| 4.7 Timing Measuremen       | ts                                                                            | 88 |

| 4.8 Mechanical Specifica    | ations                                                                        | 90 |

# **List of Figures**

| Figure 1-1.  | HDSL T1/E1 Terminal                                             | 1  |

|--------------|-----------------------------------------------------------------|----|

| Figure 1-2.  | Bt8970 Detailed Block Diagram                                   | 2  |

| Figure 1-3.  | Pin Diagram                                                     | 5  |

| Figure 2-1.  | Transmit Section Block Diagram                                  | 11 |

| Figure 2-2.  | First-Order Echo Cancellation Using the Variable Gain Amplifier | 15 |

| Figure 2-3.  | Receiver Digital Signal Processing                              | 16 |

| Figure 2-4.  | Digital Front-End Block Diagram                                 | 17 |

| Figure 2-5.  | Timing Recovery and Clock Interface Block Diagram               | 24 |

| Figure 2-6.  | Serial Sign-Bit First Mode                                      | 26 |

| Figure 2-7.  | Parallel Master Mode                                            | 26 |

| Figure 2-8.  | Parallel Slave Mode                                             | 27 |

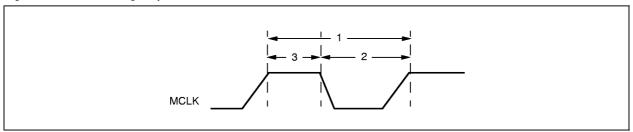

| Figure 4-1.  | MCLK Timing Requirements                                        | 70 |

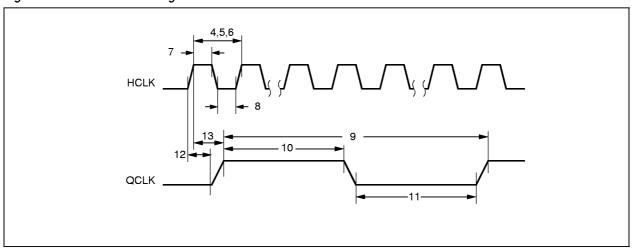

| Figure 4-2.  | Clock Control Timing                                            | 71 |

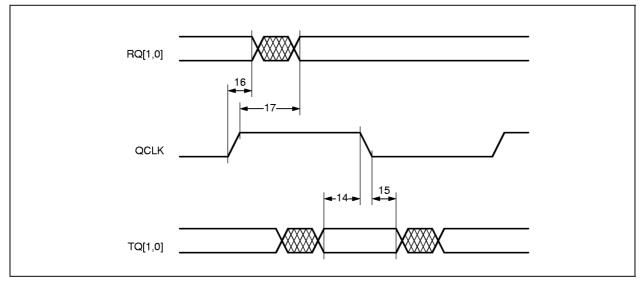

| Figure 4-3.  | Channel Unit Interface Timing, Parallel Master Mode             | 72 |

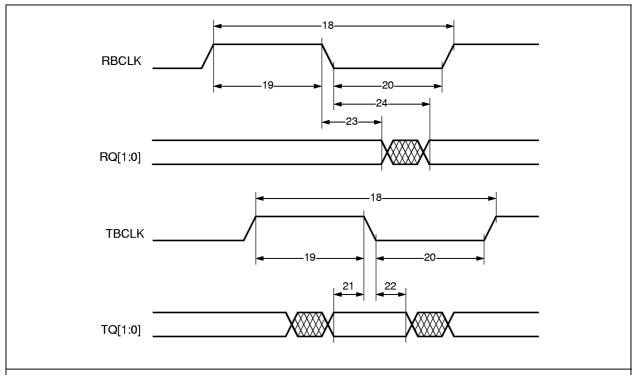

| Figure 4-4.  | Channel Unit Interface Timing, Parallel Slave Mode              | 74 |

| Figure 4-5.  | Channel Unit Interface Timing, Serial Mode                      | 75 |

| Figure 4-6.  | MCI Write Timing, Intel Mode (MOTEL = 0)                        | 78 |

| Figure 4-7.  | MCI Write Timing, Motorola Mode (MOTEL = 1)                     | 78 |

| Figure 4-8.  | MCI Read Timing, Intel Mode (MOTEL = 0)                         | 79 |

| Figure 4-9.  | MCI Read Timing, Motorola Mode (MOTEL = 1)                      | 79 |

| Figure 4-10. | Internal Write Timing                                           | 80 |

| Figure 4-11. | JTAG Interface Timing                                           | 82 |

| Figure 4-12. | SMON Timing                                                     | 82 |

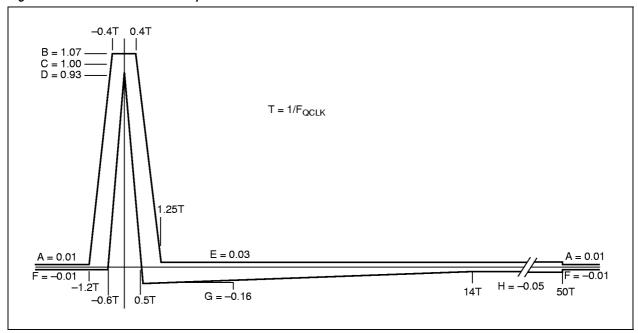

| Figure 4-13. | Transmitted Pulse Template                                      | 85 |

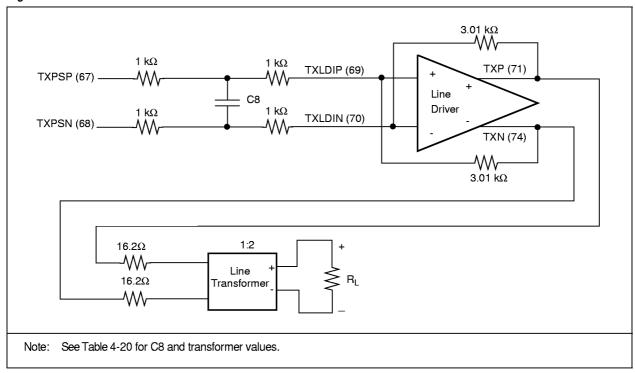

| Figure 4-14. | Transmitter Test Circuit                                        | 86 |

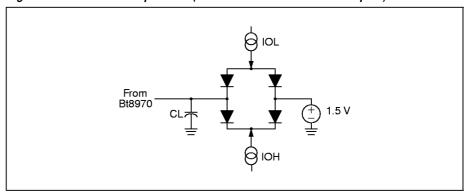

| Figure 4-15. | Standard Output Load (Totem Pole and Three-State Outputs)       | 87 |

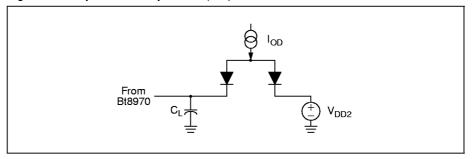

| Figure 4-16. | Open-Drain Output Load (IRQ)                                    | 87 |

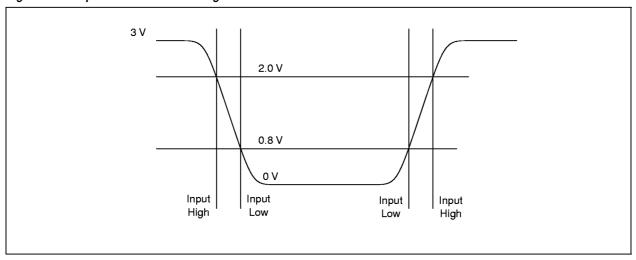

| Figure 4-17. | Input Waveforms for Timing Tests                                | 88 |

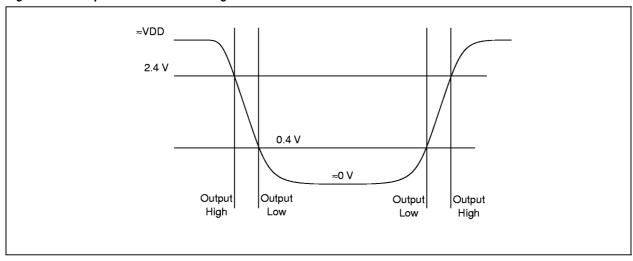

| Figure 4-18. | Output Waveforms for Timing Tests                               | 88 |

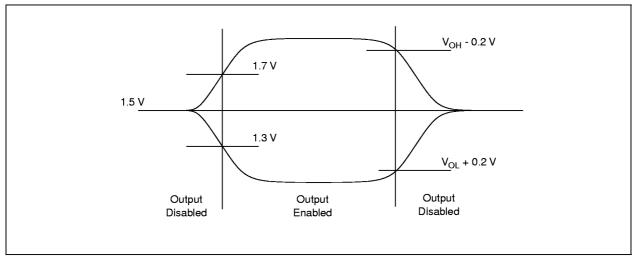

| Figure 4-19. | Output Waveforms for Three-state Enable and Disable Tests       | 89 |

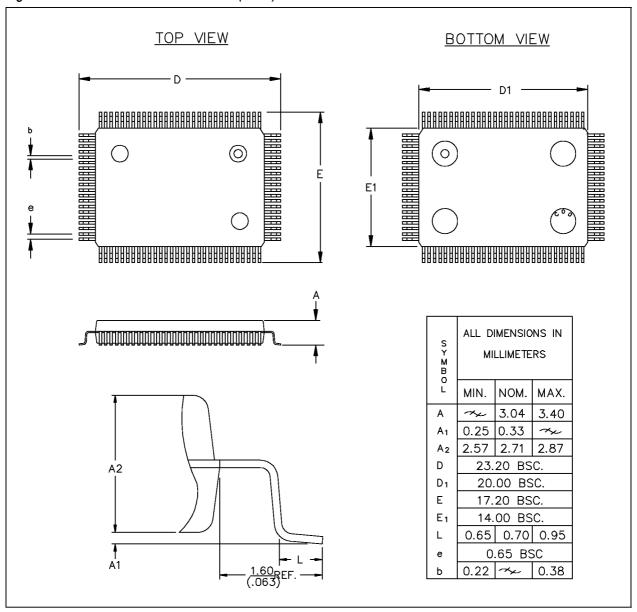

| Figure 4-20. | 100-Pin Plastic Quad Flat Pack (PQFP)                           | 90 |

List of Figures Bt8970

## **List of Tables**

| Table 1-1.  | Pin Descriptions                                                       | . 6 |

|-------------|------------------------------------------------------------------------|-----|

| Table 1-2.  | Hardware Signal Definitions                                            | . 7 |

| Table 2-1.  | Symbol Source Selector/Scrambler Modes                                 | 12  |

| Table 2-2.  | Four-Level Bit-to-Symbol Conversions                                   | 13  |

| Table 2-3.  | Two-Level Bit-to-Symbol Conversions                                    | 13  |

| Table 2-4.  | Two-Level Symbol-to-Bit Conversion                                     | 21  |

| Table 2-5.  | Four-Level Symbol-to-Bit Conversion                                    | 22  |

| Table 2-6.  | Crystal Oscillator Circuit Component Values                            | 25  |

| Table 2-7.  | Timers                                                                 | 31  |

| Table 2-8.  | JTAG Device Identification Register                                    | 32  |

| Table 3-1.  | Register Table                                                         | 34  |

| Table 4-1.  | Absolute Maximum Ratings                                               | 67  |

| Table 4-2.  | Recommended Operating Conditions                                       | 68  |

| Table 4-3.  | Electrical Characteristics                                             | 69  |

| Table 4-4.  | External Clock Timing Requirements (MCLK)                              | 70  |

| Table 4-5.  | HCLK Switching Characteristics                                         | 70  |

| Table 4-6.  | Symbol Clock (QCLK) Switching Characteristics                          | 71  |

| Table 4-7.  | Channel Unit Interface Timing Requirements, Parallel Master Mode       | 72  |

| Table 4-8.  | Channel Unit Interface Switching Characteristics, Parallel Master Mode | 72  |

| Table 4-9.  | Channel-Unit Interface Timing Requirements, Parallel Slave Mode        | 73  |

| Table 4-10. | Channel Unit Interface Switching Characteristics, Parallel Slave Mode  | 73  |

| Table 4-11. | Channel Unit Interface Timing Requirements, Serial Mode                | 74  |

| Table 4-12. | Channel Unit Interface Switching Characteristics, Serial Mode          | 74  |

| Table 4-13. | Microcomputer Interface Timing Requirements                            | 76  |

| Table 4-14. | Microcomputer Interface Switching Characteristics                      | 77  |

| Table 4-15. | Test and Diagnostic Interface Timing Requirements                      | 81  |

| Table 4-16. | Test and Diagnostic Interface Switching Characteristics                | 81  |

| Table 4-17. | Receiver Analog Requirements and Specifications                        | 83  |

| Table 4-18. | Transmitter Analog Requirements and Specifications                     | 84  |

| Table 4-19. | Transmitted Pulse Template                                             | 85  |

| Table 4-20. | Transmitter Test Circuit Component Values                              | 87  |

List of Tables Bt8970

## 1.0 System Overview

## 1.1 Functional Summary

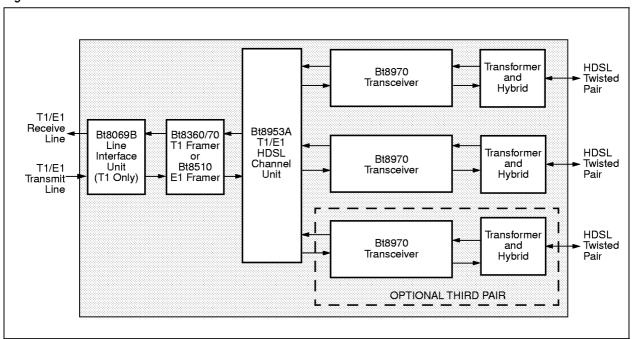

The Bt8970 HDSL transceiver is an integral component of Rockwell's HDSL chipset. System performance of the chipset allows 2-pair T1, 2-pair E1, and 3-pair E1 transmission. The major building blocks of a typical HDSL T1/E1 terminal are shown in Figure 1-1.

Figure 1-1. HDSL T1/E1 Terminal

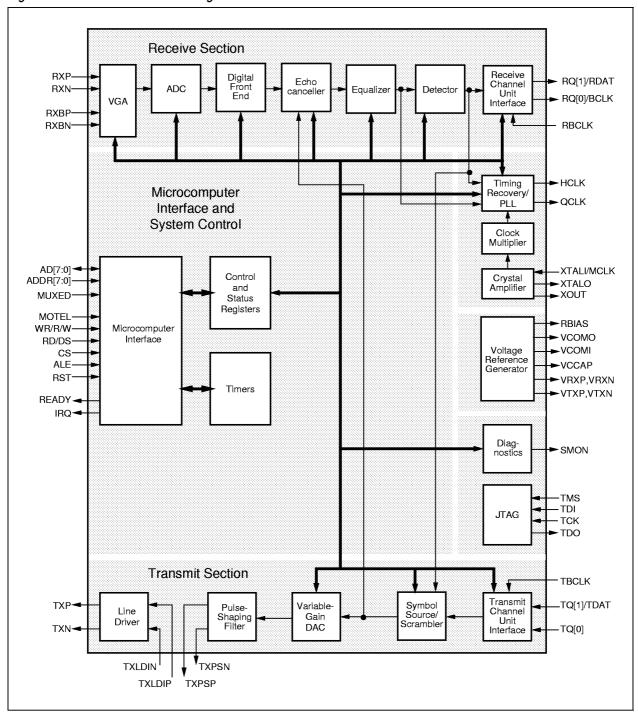

The Bt8970 comprises five major functions: a transmit section, a receive section, a timing recovery and clock interface, a microcomputer interface, and a test and diagnostic interface. Figure 1-2 details the connections within and between each of these functional blocks.

Figure 1-2. Bt8970 Detailed Block Diagram

1.1 Functional Summary

#### 1.1.1 Transmit Section

The source of transmitted symbols is programmable through the microcomputer interface. The primary choices include external 2B1Q-encoded data presented to the TQ[1,0]/TDAT pins of the channel unit interface, internally looped-back receive symbols from the detector, or a constant "all ones" source. The symbols are then optionally scrambled. Isolated pulses can also be generated to support the testing of pulse templates.

The digital symbols are transformed to an analog signal via the DAC, which is highly linear in order to maximize the echo cancellation and detection properties of the signal. In addition, the transmit power level of the DAC may be adjusted via the Transmitter Gain Register [tx\_gain; 0x29] to optimize performance. The Transmitter Calibration Register [tx\_calibrate; 0x28] contains the nominal setting for the transmitter gain which is calibrated and hard-coded at the factory. The pulse-shaping filter then conditions the signal to prevent crosstalk to adjacent subscriber lines. Finally, the differential line driver provides the current driving capabilities and low-distortion characteristics needed to drive a large range of subscriber lines at low-bit error rates.

#### 1.1.2 Receive Section

The differential Variable Gain Amplifier (VGA) receives the data from the subscriber line. Balancing inputs (RXBP, RXBN) are provided to accommodate first-order transmit echo cancellation via an external hybrid. The gain is programmable so that the dynamic range of the Analog-to-Digital Converter (ADC) can be maximized according to the attenuation of the subscriber line.

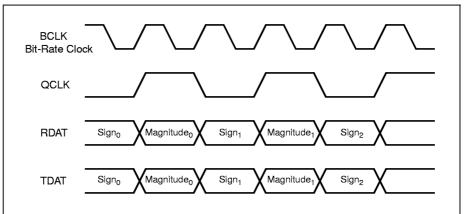

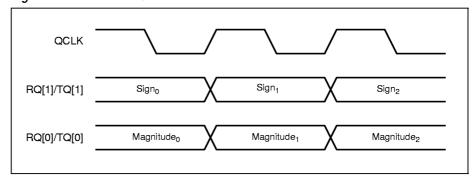

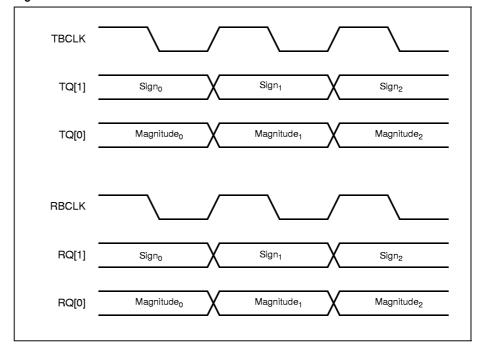

Digitized receive data is passed to the Digital Signal Processor (DSP) portion of the Bt8970. After DC offset cancellation, a replica of the transmit signal is subtracted from the total receive signal by a digital echo canceller. The resultant farend signal is then conditioned by an equalization stage consisting of Automatic Gain Control (AGC), a feed-forward equalizer, a decision-feedback equalizer, and an error predictor. A mode-dependent detector is then used to recover the 2B1Q-encoded data from the equalized signal. The channel unit interface then provides an optional descrambling function followed by parallel or serial output of the sign and magnitude bits on pins RQ[1,0]/RDAT. A number of meters are implemented within the receiver to provide average level indications at various points in the receive signal path. The receive section also performs remote unit clock recovery through an on-chip Phase Lock Loop (PLL) circuit.

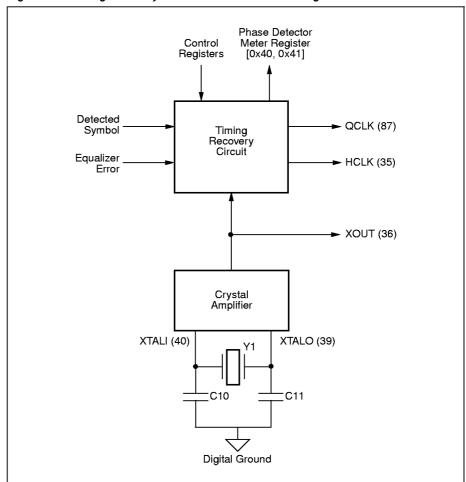

## 1.1.3 Timing Recovery and Clock Interface

The clock interface includes a crystal amplifier module to reduce the external components needed for clock generation. The crystal frequency must be 16 times the desired symbol rate. When configured as a remote unit, the PLL module recovers the incoming data clock and outputs it on the QCLK pin (and also the BCLK pin for serial mode operation). The HCLK output, which is synchronized to the QCLK signal, can be configured to cycle at 16, 32, or 64 times the symbol rate.

1.0 System Overview Bt8970

1.1 Functional Summary

Single-Chip HDSL Transceiver

### 1.1.4 Microcomputer Interface

The Microcomputer Interface (MCI) provides access to a 256-byte address space within the transceiver. A combination of direct and indirect addressing methods are used to access all internal locations. The MCI is designed to interface with both Intel- and Motorola-style processors with no additional glue logic. A MOTEL control pin is provided to configure the bus interface control/handshake lines to conform to common Motorola/Intel conventions. A MUXED control pin is provided to configure the bus interface address and data lines for multiplexed or independent data/address bus operation. Little-endian data formatting (least significant byte of a multibyte word stored at the lowest byte-address location) is used in all cases, regardless of MOTEL pin selection. A READY control pin is provided to support wait-state insertion. An Interrupt Request (IRQ) output pin supports low-latency responses to time-critical events within the transceiver.

Eight 16-bit timers and ten measurement meters are integrated into the transceiver. The timers support various metering functions within the receiver section and off-load the external microcomputer from complex timing operations associated with startup procedures. Control and monitoring access to the timers and meters is provided through the microcomputer interface.

### 1.1.5 Test and Diagnostic Interface (JTAG)

The Test and Diagnostic Interface comprises a test access port and a Serial Monitor Output (SMON). The test access port conforms to IEEE Std 1149.1-1990, (IEEE Standard Test Access Port and Boundary Scan Architecture). Also referred to as Joint Test Action Group (JTAG), this interface provides direct serial access to each of the transceiver's I/O pins. This capability can be used during an in-circuit board test to increase the testability and reduce the cost of the in-circuit test process.

The serial monitor output can be viewed as a real-time virtual probe for looking at the transceiver's internal signals. The programmable signal source is shifted out serially at 16 times the symbol rate. The majority of the receive signal path is accessible through this output.

5

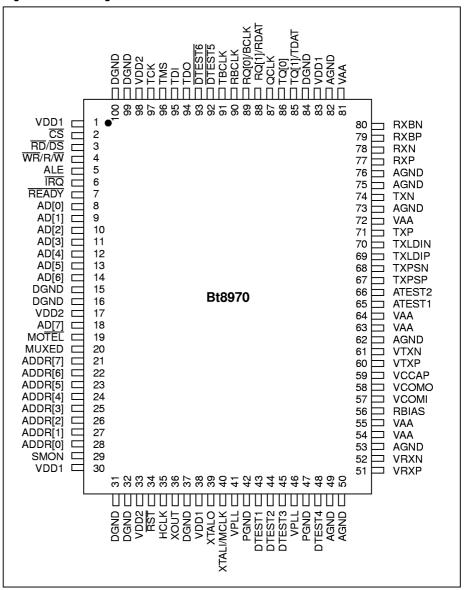

## 1.2 Pin Descriptions

The Bt8970 is packaged in a 100-Pin Plastic Quad Flat Pack (PQFP). The pin assignments are shown in Figure 1-3. A listing of pin labels, numbers, and I/O assignments is given in Table 1-1. Signal definitions are provided in Table 1-2. The coding used in the I/O column is: O = digital output, OA = analog output, OD = open-drain output, I = digital input, IA = analog input, and I/O = bidirectional.

Figure 1-3. Pin Diagram

1.0 System Overview Bt8970

### 1.2 Pin Descriptions

Table 1-1. Pin Descriptions

| Pin | Pin<br>Label | I/O | Pin | Pin Label I/O |                        | Pin | Pin<br>Label | 1/0   | Pin   | Pin Label  | l/<br>O |

|-----|--------------|-----|-----|---------------|------------------------|-----|--------------|-------|-------|------------|---------|

| 1   | VDD1         | _   | 26  | ADDR[2] I     |                        | 51  | VRXP         | OA    | 76    | AGND       | -       |

| 2   | cs           | I   | 27  | ADDR[1]       | I                      | 52  | VRXN         | OA    | 77    | RXP        | ΙA      |

| 3   | RD/DS        | I   | 28  | ADDR[0]       | I                      | 53  | AGND         | -     | 78    | RXN        | IA      |

| 4   | WR/R/W       | I   | 29  | SMON          | SMON O 54 VAA          |     | -            | 79    | RXBP  | IA         |         |

| 5   | ALE          | I   | 30  | VDD1          | _                      | 55  | VAA          | _     | 80    | RXBN       | ΙA      |

| 6   | IRQ          | OD  | 31  | DGND          | _                      | 56  | RBIAS        | OA    | 81    | VAA        | _       |

| 7   | READY        | OD  | 32  | DGND          | _                      | 57  | VCOMI        | OA    | 82    | AGND       | _       |

| 8   | AD[0]        | 1/0 | 33  | VDD2          | -                      | 58  | VCOMO        | OA    | 83    | VDD1       | _       |

| 9   | AD[1]        | 1/0 | 34  | RST           | I                      | 59  | VCCAP        | OA    | 84    | DGND       | _       |

| 10  | AD[2]        | 1/0 | 35  | HCLK          | 0                      | 60  | VTXP         | OA    | 85    | TQ[1]/TDAT | 1       |

| 11  | AD[3]        | 1/0 | 36  | XOUT          | XOUT O 61 VTXN OA      |     | OA           | 86    | TQ[0] | ı          |         |

| 12  | AD[4]        | 1/0 | 37  | DGND          | DGND -                 |     | AGND         | _     | 87    | QCLK       | 0       |

| 13  | AD[5]        | 1/0 | 38  | VDD1          | VDD1 –                 |     | VAA          | _     | 88    | RQ[1]/RDAT | 0       |

| 14  | AD[6]        | 1/0 | 39  | XTALO         | XTALO O 64 VAA         |     | VAA          | _     | 89    | RQ[0]/BCLK | 0       |

| 15  | DGND         | _   | 40  | XTALI/MCLK    | CTALI/MCLK I 65 ATEST1 |     | ATEST1       | IA    | 90    | RBCLK      | I       |

| 16  | DGND         | -   | 41  | VPLL          | VPLL - 66 ATEST2 IA    |     | 91           | TBCLK | 1     |            |         |

| 17  | VDD2         | _   | 42  | PGND          | _                      | 67  | TXPSP        | OA    | 92    | DTEST5     | I       |

| 18  | AD[7]        | 1/0 | 43  | DTEST1        | I                      | 68  | TXPSN        | OA    | 93    | DTEST6     | I       |

| 19  | MOTEL        | I   | 44  | DTEST2        | I                      | 69  | TXLDIP       | IA    | 94    | TDO        | 0       |

| 20  | MUXED        | I   | 45  | DTEST3        | I                      | 70  | TXLDIN       | IA    | 95    | TDI        | ı       |

| 21  | ADDR[7]      | I   | 46  | VPLL          | -                      | 71  | TXP          | OA    | 96    | TMS        | 1       |

| 22  | ADDR[6]      | I   | 47  | PGND          | _                      | 72  | VAA          | _     | 97    | TCK        |         |

| 23  | ADDR[5]      | I   | 48  | DTEST4        | ı                      | 73  | AGND         | _     | 98    | VDD2       | _       |

| 24  | ADDR[4]      | I   | 49  | AGND          | _                      | 74  | TXN          | OA    | 99    | DGND       | _       |

| 25  | ADDR[3]      | I   | 50  | AGND          | _                      | 75  | AGND         | _     | 100   | DGND       | _       |

1.2 Pin Descriptions

Table 1-2. Hardware Signal Definitions (1 of 4)

| Pin Label | Signal Name                        | I/O | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                                    |     | Microcomputer Interface (MCI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MOTEL     | Motorola/Intel                     | I   | Selects between Motorola and Intel handshake conventions for the RD/DS and WR/R/W signals.  MOTEL = 1 for Motorola protocol: DS, R/W MOTEL = 0 for Intel protocol: RD, WR                                                                                                                                                                                                                                                                                                                                            |

| ALE       | Address Latch<br>Enable            | I   | Falling-edge-sensitive input. The value of AD[7:0] when MUXED = 1, or ADDR[7:0] when MUXED = 0, is internally latched on the falling edge of ALE.                                                                                                                                                                                                                                                                                                                                                                    |

| CS        | Chip Select                        | I   | Active-low input used to enable read/write operations on the Microcomputer Interface (MCI).                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RD/DS     | Read/Data Strobe                   | I   | Bimodal input for controlling read/write access on the MCI.  When MOTEL = 1 and CS = 0, RD/DS behaves as an active-low data strobe  DS. Internal data is output on AD[7:0] when DS = 0 and R/W = 1. External data is internally latched from AD[7:0] on the rising edge of DS when R/W = 0.  When MOTEL = 0 and CS = 0, RD/DS behaves as an active-low read strobe  RD. Internal data is output on AD[7:0] when RD = 0. Write operations are not controlled by RD in this mode.                                      |

| WR / R/W  | Write/<br>Read/Write               | I   | Bimodal input for controlling read/write access on the MCI.  When MOTEL = 1 and CS = 0, WR/R/W behaves as a read/write select line R/W. Internal data is output on AD[7:0] when DS = 0 and R/W = 1. External data is internally latched from AD[7:0] on the rising edge of DS when R/W = 0.  When MOTEL = 0 and CS = 0, WR/R/W behaves as an active-low write strobe WR. External data is internally latched from AD[7:0] on the rising edge of WR Read operations are not controlled by WR in this mode.            |

| AD[7:0]   | Address-<br>Data[7:0]              | 1/0 | 8-bit bidirectional multiplexed address-data bus. AD[7] = MSB, AD[0] = LSB. Usage is controlled using the MUXED.                                                                                                                                                                                                                                                                                                                                                                                                     |

| ADDR[7:0] | Address Bus (not multiplexed)[7:0] | I   | Provides a glueless interface to microcomputers with separate address and data buses. ADDR[7] = MSB, ADDR[0] = LSB. Usage is controlled using the MUXED.                                                                                                                                                                                                                                                                                                                                                             |

| MUXED     | Addressing<br>Mode Select          | I   | Controls the MCI addressing mode.  When MUXED = 1, the MCI uses AD[7:0] as a multiplexed signal for address and data (typical of Intel processors).  When MUXED = 0, the MCI uses ADDR[7:0] as the address input, and AD[7:0] for data only (typical of Motorola processors).                                                                                                                                                                                                                                        |

| READY     | Ready                              | OD  | Active-low, open-drain output that indicates that the MCl is ready to transfer data. Can be used to signal the microcomputer to insert wait states.                                                                                                                                                                                                                                                                                                                                                                  |

| IRQ       | Interrupt Request                  | OD  | Active-low, open-drain output that indicates requests for interrupt. Asserted whenever at least one unmasked interrupt flag is set. Remains inactive whenever no unmasked interrupt flags are present.                                                                                                                                                                                                                                                                                                               |

| RST       | Reset                              | ı   | Asynchronous, active-low, level-sensitive input that places the transceiver in an inactive state by setting the power-down mode bit of the Global Modes and Status Register [global_modes; 0x00], and zeroing the clk_freq[1,0] bits of the PLL Modes Register [pll_modes; 0x22] and the hclk_freq[1,0] bits of the Serial Monitor Source Select Register [serial_monitor_source; 0x01]. All RAM contents are lost. Does not affect the state of the test access port which is reset automatically at power-up only. |

### 1.2 Pin Descriptions

Table 1-2. Hardware Signal Definitions (2 of 4)

| Pin Label                     | Signal Name                                                     | Signal Name I/O Definition |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-------------------------------|-----------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                               |                                                                 |                            | Channel Unit Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RQ[1]/<br>RDAT<br>RQ[0]/ BCLK | Receive Quat 1/<br>Receive Data<br>Receive Quat 0/<br>Bit Clock | 0 0                        | RQ[1]/RDAT and RQ[0]/BCLK are bimodal outputs that represent the sign and magnitude bits of the received quaternary output symbol in parallel channel unit modes (RQ[1], RQ[0]), and the serial-data and bit-clock outputs in serial channel unit modes (RDAT, BCLK). Behavior of these outputs is configurable through the Channel Unit Interface Modes Register [CU_interface_modes; 0x06] for parallel master, parallel slave, serial magnitude-bit-first and serial sign-bit-first operations.  For parallel mode operation: |  |  |

|                               |                                                                 |                            | RQ[1] = Sign bit output<br>RQ[0] = Magnitude bit output                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                               |                                                                 |                            | Both outputs are updated at the symbol rate on the rising edge of QCLK (master mode) or the rising/falling edge (programmable) of RBCLK (slave mode).  For serial mode operation:                                                                                                                                                                                                                                                                                                                                                |  |  |