# Microcontroller for battery chargers BU3451

The BU3451 is a 4-bit single-chip microcontroller developed for charging circuits. It is equipped with analog and comparator inputs, and can be used for charging control of various types of batteries with very few attachments.

## Applications

Controllers using A/D, such as battery chargers

## Specifications

| Series                        | BU3451              |

|-------------------------------|---------------------|

| Program memory (ROM) (bytes)  | 2048                |

| Data memory (RAM) (bits)      | 96×4                |

| Subroutine nesting levels     | 3                   |

| Instruction sets              | 38                  |

| I/O ports *1                  | 4                   |

| Input ports *2                | 4                   |

| Large current outputs         | 4                   |

| Analog inputs                 | 4                   |

| Analog reference inputs       | 1                   |

| Instruction cycle ( µs)       | 1.68 (fosc=3.58MHz) |

| Power supply voltage (V) typ. | 5                   |

<sup>\*1</sup> The format of the I/O circuit can be selected using the mask option. (See I/O Circuit Formats.)

#### Features

| 1)         | Equipped with 38 types of instruction sets.     |

|------------|-------------------------------------------------|

| 2)         | High-speed instruction execution time (machine  |

|            | cycle) of 1.68 $\mu$ s (3.58MHz, 5V).           |

| 3)         | ROM 2048 $\times$ 8 bits                        |

| 4)         | RAM (general-purpose) 96 $\times$ 4 bits        |

| <b>5</b> ) | Subroutine nesting 3 levels                     |

| 6)         | Inputs (PIX) 4                                  |

| 7)         | Inputs/outputs (PIO)                            |

| 8)         | Large current outputs (POX: LED direct drive) 4 |

| a)         | Analog inputs (ADI)  4 ch                       |

- 10) Comparator input (CMP) ..... 1 ch

- 11) Internal Power an reset

- 12) Internal chopping wave generator for A/D conversion (constant current source)

Adding an external capacitor to the Cout pin enables chopping wave voltage to be generated with a high level of precision. Software processing enables A/D conversion of analog input voltage.

- 13) Watchdog timer can be built in (mask option)

- 14) Ceramic oscillation possible

- 15) Operating frequency . . . . . . . . 0.3 ∼ 4.2MHz

7858999 0051511 761 🖩

ROHM

<sup>\*2</sup> Standby function provided (See Description of HALT function.)

# ●Absolute maximum ratings (Ta=25℃)

| Parameter           | Symbol | Limits          | Unit |

|---------------------|--------|-----------------|------|

| Applied voltage     | VDD    | −0.3~7.0        | V    |

| Power dissipation   | Pd     | 450*            | mW   |

| Storage temperature | Тѕтс   | <b>−55</b> ~125 | င    |

| Input voltage       | Vin    | -0.3~VDD+0.3    | V    |

| Output voltage      | Vоит   | -0.3~VDD+0.3    | V    |

Reduced by 4.5mW for each increase in Ta of 1℃ over 25℃.

## ■Recommended operating conditions (Ta=25℃).

| Parameter                 | Symbol   | Limits                   | Unit |

|---------------------------|----------|--------------------------|------|

| Power supply voltage      | VDD      | 4.0~6.0                  | ٧    |

| Input voltage (HIGH)*     | ViH      | 0.7Vpp∼Vpp               | ٧    |

| Input voltage (LOW)*      | VIL      | 0.0~0.3Vpp               | ٧    |

| INIT input voltage (HIGH) | VIH INIT | 0.75Vpp~Vpp              | ٧    |

| INIT input voltage (LOW)  | VIL INIT | 0.0∼0.25Vɒɒ              | ٧    |

| AIN input voltage         | Viain    | 0.6∼V <sub>DD</sub> −1.2 | V    |

| CMP input voltage         | VICMP    | 0.6∼V <sub>DD</sub> −1.2 | ٧    |

| Operating temperature     | TOPR     | -25~85                   | င    |

<sup>\*</sup> OSC1 pin and INIT pin not included.

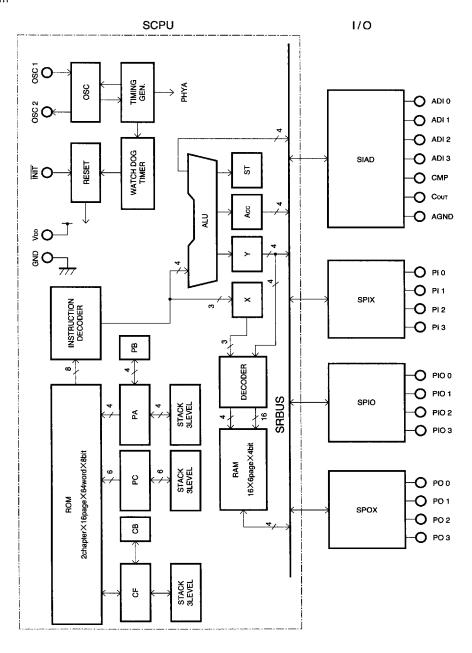

Block diagram

**18** 7828999 0021213 534

ROHM

# Block diagram

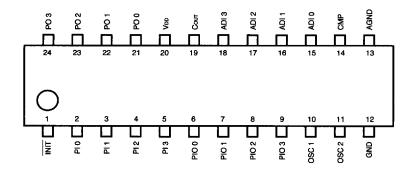

# Pin description

| Pin Name  | 1/0          | Function                                                                                                                                                                                                               | Status at reset     | Status in HALT mode |

|-----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|

| VDD       | _            | Used to connect 4.0 V ~ 6.0 V power supply.                                                                                                                                                                            | -                   | _                   |

| GND       | -            | Reference voltage for digital input/output (0 V).                                                                                                                                                                      | _                   | -                   |

| AGND      | _            | Reference voltage for analog input (0 V).                                                                                                                                                                              | _                   | _                   |

| INIT      | Input        | INIT Manual reset input. Internal PUR*. Setting this pin to LOW sets the ROM address to 0 page, 0 address.                                                                                                             | _                   |                     |

| PI0~PI3   | Input        | 4-bit input ports. Internal PUR *.                                                                                                                                                                                     | _                   | _                   |

| PIO0~PIO3 | Input/output | 4-bit input/output ports. Output is Pch open drain output. Input is enabled when the various outputs are LOW or Hi-Z. The mask option can be used to select whether or not PDR* is to be used for each individual bit. | Hi-Z or LOW output  | _                   |

| P00~P03   | Output       | 4-bit large-current Nch open drain outputs. The mask option can be used to select whether or not PUR* is to be used for each individual bit.                                                                           | Hi-Z or HIGH output | _                   |

| ADI0~ADI3 | Input        | Analog inputs. Switching the four inputs is done via the program.                                                                                                                                                      | ADI0 selected       | -                   |

| СМР       | Input        | Analog reference voltage input; used with comparator operation.                                                                                                                                                        | Not selected        | _                   |

| COUT      | Output       | A capacitor is connected between this and GND (to produce chopping waves).                                                                                                                                             | LOW output          | _                   |

| OSC1      | Input        | Clock generator input pin.                                                                                                                                                                                             | _                   | Н                   |

| OSC2      | Output       | Clock generator output pin.                                                                                                                                                                                            | _                   | Н                   |

| _ | : No change in status | (status | maintained | ١ |

|---|-----------------------|---------|------------|---|

|---|-----------------------|---------|------------|---|

PUR\* : Puli-up resistance PDR \* : Pull-down resistance

| 7828999 | 0021214 | 470 |  |   |

|---------|---------|-----|--|---|

|         | ROHM    |     |  | _ |

# ●Input/output circuits

| Pin Name  | 1/0          | I/O Circuit             | Notes                                                         |

|-----------|--------------|-------------------------|---------------------------------------------------------------|

| ĪNĪT      | Input        | VDD VDD VDD WTH GND GND | Hysteresis input Internal pull - up resistor About.400kΩ      |

| PI0~PI3   | Input        | Won Von Won GND         | For pull-up<br>Internal MOS Tr<br>About.100kΩ                 |

| PIO0~PIO3 | Input/output | Voo Voo Voo GND GND     | For pull-down<br>Internal MOS Tr<br>About.100kΩ               |

| PO0~PO3   | Output       | GND WOOD VOOD GND       | Large-current output For pull-up Internal MOS Tr About.100k Ω |

| ADI0~ADI3 | Input        |                         | Analog input                                                  |

| СМР       | Input        |                         | Analog input                                                  |

O Items are mask options.

**■ 7828999 0021215 307 ■**

ROHM

## Input/output circuits

| Pin Name | I/O    | I/O Circuit  | Notes                                          |

|----------|--------|--------------|------------------------------------------------|

| Соит     | Output | V00          |                                                |

| OSC1     | Input  | OSC1 Rd OSC2 | Internal MOS Tr for feedback<br>Rf:About. 1 MΩ |

| OSC2     | Output | Rt W         | Internal damping resistance Rd:About. 1 kΩ     |

Oltems are mask options.

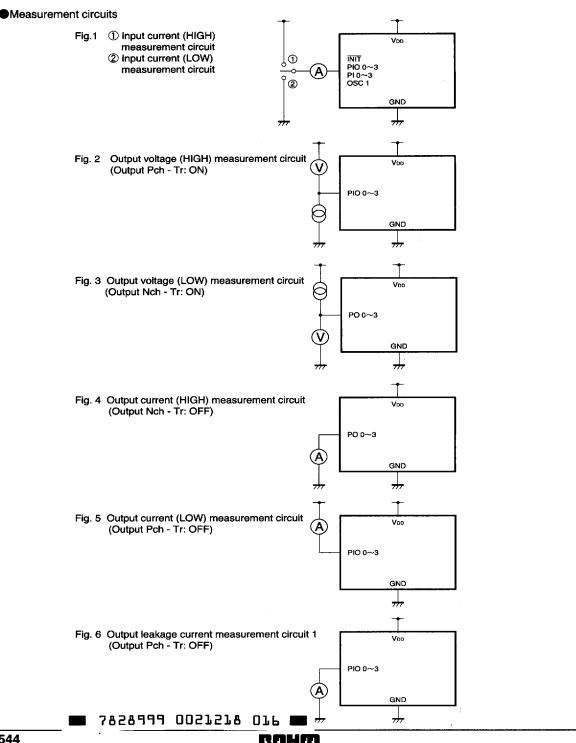

# ●Electrical characteristics (Unless otherwise noted, Ta=25°C, VDD=5.0V)

| Parameter                               | Symbol      | Min. | Тур.       | Max. | Unit | Conditions                                                            | Measurement Circuit |

|-----------------------------------------|-------------|------|------------|------|------|-----------------------------------------------------------------------|---------------------|

| INIT "H" input current                  | <b>i</b> mm | -1.0 | _          | +1.0 | μA   | V <sub>I</sub> =V <sub>DD</sub>                                       | Fig.1               |

| INIT "L" input current                  | Ішт         | -6   | -11        | -20  | μΑ   | Vi=GND                                                                | Fig.1               |

| OSC1 "H" input current                  | Іноѕс       | -1.0 | _          | +1.0 | μΑ   | V <sub>I</sub> =V <sub>DD</sub> With ceramic oscillation              | Fig.1               |

| OSC1 "L" input current                  | liLosc      | -2   | <b>—</b> 5 | -10  | μA   | V <sub>I</sub> =GND<br>With ceramic oscillation                       | Fig.1               |

| OSC1 input current                      | liosc       | -1.0 | _          | +1.0 | μА   | With CR oscillation                                                   | Fig.1               |

| "H" input current                       | lін         | -1.0 | _          | +1.0 | μΑ   | V <sub>I</sub> =V <sub>DD</sub> PIX                                   | Fig.1               |

| "L" input current                       | Iι∟         | -35  | -65        | -120 | μA   | Vi=GND PIX                                                            | Fig.1               |

| "L" output voltage                      | Vol         | _    | 0.25       | 0.4  | ٧    | loL=10mA<br>POX                                                       | Fig.3               |

| "H" output voltage                      | Vон         | 4.4  | 4.6        | _    | ٧    | loн=-1.0mA<br>PIO                                                     | Fig.2               |

| "H" output current                      | Юн          | -35  | 65         | -120 | μA   | With pull-up resistance POX<br>Output Tr: OFF                         | Fig.4               |

| "L" output current                      | lor         | 35   | 65         | 120  | μΑ   | With pull-down resistance PIO Output Tr: OFF                          | Fig.5               |

| Open drain output<br>leakage current    | lL          | -1.0 | _          | +1.0 | μΑ   | With no pull-up or pull-down resistance POX, PIO                      | Fig.6<br>Fig.7      |

| ADI input current                       | ladi        | -1.0 | _          | +1.0 | μA   |                                                                       | Fig.8               |

| CMP input current                       | Ісме        | -1.0 | _          | +1.0 | μA   |                                                                       | Fig.8               |

| Comparator offset voltage               | VFOFF       | -10  | 0          | +10  | mV   | V <sub>in</sub> =0.6~3.8 (V)                                          | _                   |

| Triangular wave peak value voltage      | VPEAK       | 3.8  | 3.9        | _    | ٧    |                                                                       | _                   |

| *1<br>A/D conversion differential error | VDERR       | +1.5 | 0          | -1.5 | mV   | External C=0.1 µF<br>f=3.58MHz<br>When using 11-bit precision program | _                   |

| Operating circuit current               | Іорор       | 0.3  | 0.8        | 2.0  | mA   | fosc=3.58MHz<br>Comparator stopped, ceramic oscillation               | Fig.10              |

| Static circuit current                  | IDDST       | _    | -          | +1.0 | μА   | In HALT mode (oscillation stopped)                                    | Fig.9               |

| Operating frequency                     | fcĸ         | 0.3  | _          | 4.2  | MHz  | External clock                                                        | _                   |

ONot designed for radiation resistance

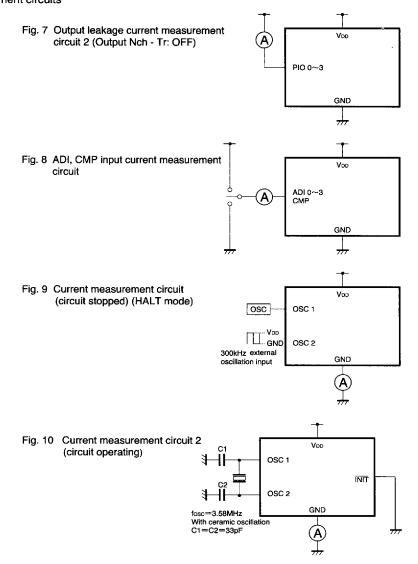

## Measurement circuits

7828999 0021219 T52 ■

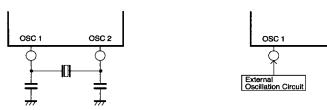

## Clock generator

The clock generator can produce oscillation either through a ceramic resonator or external input. If ceramic oscillation is used, clock signals are obtained through an internal feedback resistance and damping resistance, and an external ceramic resonator and oscillation capacitor. (When selecting the ceramic resonator, please refer to the recommended values of the pertinent manufacturer.)

If clock signals are being input from an external source, they are input through the OSC1 pin, and the OSC2 pin is left open.

Ceramic oscillator external circuit

External clock input circuit

OSC 2

N.C

≪Oscillation circuit configuration example≫

#### Reset function

Two reset functions are available to initialize the CPU. When the CPU is initialized, the program counter executes instructions from 0 page, 0 address.

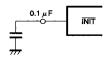

## (1) Reset through an external pin

A reset can be executed by setting the INIT pin to LOW, which is done by specifying an interval of four or more machine cycles. (One machine cycle =  $1/f_{OSC} \times 6$ )

If a reset is executed by turning on the power supply, a capacitor can be connected between the INIT pin and the GND and an integrated circuit configured with the internal pull-up resistance (approximately  $400k\Omega$ ). This generates a reset pulse when the power supply is turned on. However, this method is effective only when a valid reset pulse is input while the power supply voltage is within the operating voltage range and the clock oscillation has stabilized.

≪ Initial reset Circuit configuration example

≫

\* Capacitor value must be changed according to the rising time of power supply.

(The power supply rising time shown in the circuit example is at 10 ms or less.)

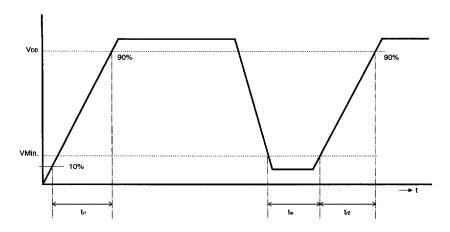

#### (2) Reset using the power on reset circuit

the power on reset circuit is valid when the following conditions are satisfied. In this case, the external capacitor on the INIT pin may be omitted.

Power on reset standard (Ta=25°C, Voo=5 V, fck=3.58 MHz)

| Parameter                   | Symbol          | Min. | Тур. | Max. | Unit | Conditions |

|-----------------------------|-----------------|------|------|------|------|------------|

| Power supply rise time      | trı             | _    | _    | 5    | ms   | VMin.=2.5V |

| Rise time when interrupted  | t <sub>r2</sub> | _    | _    | 5    | ms   | VMin.=2.5V |

| Power supply interrupt time | tw              | 5    | _    | _    | ms   | VMin.=2.5V |

**T828999 0021220 774**

546

ROHN

≪Power ON reset operation≫

### HALT function

By executing the HALT command, the microcontroller goes to HALT state.

- · In HALT state:

- 1. Oscillation comes to a halt and current consumption is reduced to an extremely low level.

- 2. The watchdog timer (WDT) is reset.

- 3. Each output pin keeps the value it was at prior to HALT state.

When executing the HALT OFF function, the mask option can be used to reset any or all of the bits in PIX input. When any of the PIX input settings is set to "L", the HALT state is canceled.

- · When the HALT state is canceled:

- 1. Segments with unstable oscillation (during ceramic oscillation) are disabled, for which reason regular operation does not resume until the wait timer has gone into operation and the effective clock is set to 1024 × 6.

- When the microcontroller returns to regular operation, the WDT resumes counting from 0.

However, the conditions for cancellation of HALT already exist when the HALT command is executed, the microcontroller treats the HALT command as an NOP command, and does not enter HALT state.

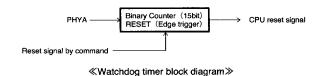

## Watchdog timer

Using the mask option, a watchdog timer can be used for runaway monitoring. The watchdog timer is configured of a 15-bit binary counter, and a clock signal of fosc/6 is input as the initial stage input. When this counter overflows, a CPU reset signal is issued, and the system is initialized. The overflow detection time is set to  $2^{14}$ /PHYA (23ms at 4.2MHz; PHYA = fosc/6). Normally, prior to the overflow of the binary counter, the Watch Dog Timer Reset (WDTR) instruction must be executed in order to reset this counter.

**■** 7858999 0057557 **₽**00 **■**

ROHM

## Analog input

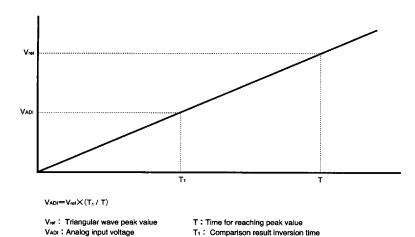

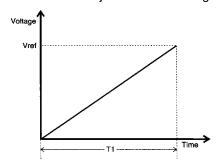

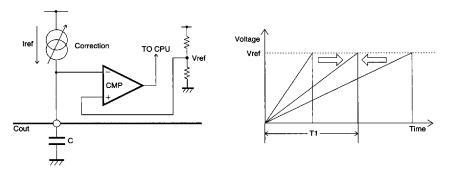

Analog input is used in A/D conversion and comparison of the voltage input through the analog input pins (ADI0  $\sim$  3). A/D conversion is carried out by a chopping wave voltage being created when the external capacitor on the  $C_{OUT}$  pin is charged with constant current, and the voltage of the chopping wave is compared with that of the analog input pins. The time from the beginning of charging to the point where the comparison results are inverted serves in relative terms as the input voltage and A/D conversion is carried out. The inclination of the chopping wave can be determined by the external capacitor.

≪Relationship between triangular wave and analog input voltage≫

7828999 0021222 547 |

ROHM

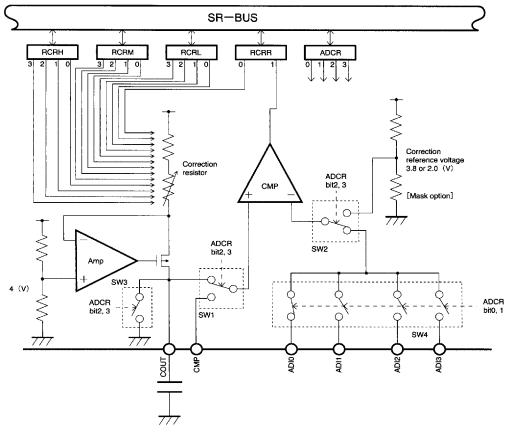

≪A/D convertor configuration diagram≫

[A/D conversion control register (ADCR)]

Operating mode setting (Bits 2 and 3 of ADCR)

Analog input pin selection (Bits 0 and 1 of ADCR)

When reset, the AINO pin is selected at operation stop.

## A/D conversion control register (ADCR)

|   | bit3         | bit2          | bit1                          | bit0 |  |  |

|---|--------------|---------------|-------------------------------|------|--|--|

| 0 | Operating m  | odo sottinas  | Selection of analog input pin |      |  |  |

| 1 | Operating in | loue settings | Selection of analog input pin |      |  |  |

# Operating mode settings (ADCR bit 2 and bit 3)

| bit3 | bit2 | Operating mode                         | Reference voltage |

|------|------|----------------------------------------|-------------------|

| 0    | 0    | Operation stopped                      |                   |

| 0    | 1    | A/D converter mode                     | Cout voltage      |

| 1    | 0    | Comparator operating mode              | CMP voltage       |

| 1    | 1    | Set-up mode for compensated resistance | Cout voltage      |

7828999 0021223 483

Selecting analog input pin (ADCR bit 0, bit 1)

| bit1 | bit0 | ADI pin selection |

|------|------|-------------------|

| 0    | 0    | ADI 0             |

| 0    | 1    | ADI 1             |

| 1    | 0    | ADI 2             |

| 1    | 1    | ADI 3             |

[Correction resistance control registers (RCRH, RCRM, RCRL, RCRR)]

In order to compensate for inclination of the chopping wave, an internal resistance is provided which can be set via the software (Bit 13). The resistance value can be selected within a range from around  $60k\Omega$  to  $260k\Omega$  in units of  $25\Omega$ , centering around  $160k\Omega$ . To set the correction resistance, the chopping wave is compared with the internal comparison voltage. The comparison voltage used when setting the correction resistance can be specified as one of two voltages, using the mask option.

Comparison voltages for correction resistance setting (VDD=5.0V)

| Symbol | Min. | Тур. | Max. | Unit | Conditions            |  |

|--------|------|------|------|------|-----------------------|--|

| Α      |      | 2.00 | _    | ٧    | Set using mask option |  |

| В      | _    | 3.8  | _    | ٧    | Set using mask option |  |

Correction resistance control register H (RCRH).

Bits 0, 1, 2, and 3 are used to set the resistance value, based on the correction resistance.

Correction resistance control register H (RCRH).

|   | bit3                             | bit2 | bit1 | bit0 |  |  |  |

|---|----------------------------------|------|------|------|--|--|--|

| 0 | Continue of companies registered |      |      |      |  |  |  |

| 1 | Setting of correction resistance |      |      |      |  |  |  |

Correction resistance control register M (RCRM).

Bits 0, 1, 2, and 3 are used to set the resistance value, based on the correction resistance.

Correction resistance control register M (RCRM).

|   | bit3 | bit2             | bit1             | bitO |

|---|------|------------------|------------------|------|

| 0 |      | Setting of corre | ction resistance |      |

Correction resistance control register L (RCRL).

Bits 0, 1, 2, and 3 are used to set the resistance value, based on the correction resistance.

Correction resistance control register L (RCRL).

|   | bit3                             | bit2              | bit1             | bit0 |  |  |  |

|---|----------------------------------|-------------------|------------------|------|--|--|--|

| 0 | Setting of correction resistance |                   |                  |      |  |  |  |

| 1 |                                  | Setting of Correc | Clion resistance |      |  |  |  |

| <b>× 1059444 NN575</b> | 24 | 31 T |

|------------------------|----|------|

|------------------------|----|------|

550

ROHM

Correction resistance control register R (RCRR)

Bit 0 is used to set the resistance value, based on the correction resistance.

Bit 1 is used to store the comparison results data (read only).

|   | 1                                                                                                   | 0                                |

|---|-----------------------------------------------------------------------------------------------------|----------------------------------|

| 0 | V <sub>ADI</sub> >Reference voltage                                                                 | Setting of correction resistance |

| 1 | V <sub>ADI</sub> <reference td="" voltage<=""><td>Setting of correction resistance</td></reference> | Setting of correction resistance |

## Setting the correction resistance (set values)

|   | RCRH   |       |       |       | RCRM |      |      |      |

|---|--------|-------|-------|-------|------|------|------|------|

|   | bit3   | bit2  | bit1  | bit0  | bit3 | bit2 | bit1 | bit0 |

| 0 | 0      | 0     | 0     | 0     | 0    | 0    | 0    | 0    |

| 1 | 101215 | 50657 | 25337 | 12647 | 6324 | 3150 | 1569 | 792  |

|   |      | RCRR  |      |      |      |

|---|------|-------|------|------|------|

|   | bit3 | bit2  | bit1 | bit0 | bit0 |

| 0 | 0    | 0     | 0    | 0    | 0    |

| 1 | 410  | 204.5 | 102  | 68   | 34   |

Because an internal fixed resistance of  $58275.06\Omega$  is provided, the correction resistance will be the selected value added to  $58275.06\Omega$ . When a reset is carried out, each bit is reset to 0, and the correction resistance value is set to  $58275.06\Omega$ . The various resistance values are used as the reference values.

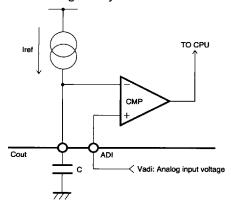

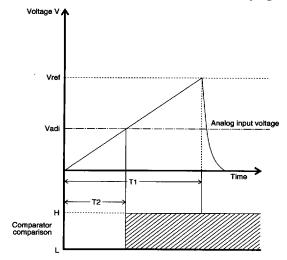

## Principle of A/D conversion

The A/D conversion circuit in the BU3451 is generally like that shown below.

Fig. 11 A/D conversion circuit

The triangular wave is created by this constant current circuit and an external capacitor.

The time required to arrive at the internal reference voltage (Vref) is assumed to be T1, and the time required to arrive at the analog input voltage (ADI) is read as T2.

Based on this, the value of the analog input voltage in relation to Vref can be judged.

Fig. 12 A/D conversion waveform

552

ROHIT

# Constant current adjustment

In A/D conversion, the T1 time is determined by the program, based on the A/D resolution. Thus, before A/D conversion is carried out, the triangular wave must be adjusted to the following inclination.

The constant current section has a 13-bit weighting, and the inclination of the triangular wave is adjusted by the program, by carrying out conversion 13 times.

### A/D conversion principle and constant current adjustment time

#### (1) Constant current adjustment time

In the constant current section, the resistance with the 13-bit weighting is set to the optimum resistance value. Specifically, conversion is being continually carried out to judge whether or not each of the 13 individual resistances is valid. For this reason, a time period which is 13 times the A/D conversion time is required.

| A/D resolution (bits)                   | 8    | 9     | 10    | 11    |

|-----------------------------------------|------|-------|-------|-------|

| Constant current adjustment time (msec) | 54.9 | 139.8 | 279.6 | 559.1 |

## (2) A/D conversion time

The program periodically checks the results of the comparison between the external A/D input and the internal triangular wave, and reads the A/D count as the number of counts when the results are inverted (the A/D input exceeds the chopping wave). For this reason, the time required for A/D conversion is as follows.

| A/D resolution (bits)                   | 8   | 9    | 10   | 11   |

|-----------------------------------------|-----|------|------|------|

| Constant current adjustment time (msec) | 4.2 | 10.8 | 21.5 | 43.0 |

7828999 0021227 029 |

## External capacitor

The capacitance of the external capacitor is based on the A/D resolution, as shown below.

A film capacitor should be used.

| A/D resolution (bits) | 8   | 9  | 10 | 11 |

|-----------------------|-----|----|----|----|

| Capacitance (nF)      | 8.2 | 18 | 33 | 68 |

#### ●A/D error

The method by which A/D error for the BU3451 is calculated is shown below.

(1) The error for 1LSB is determined.

The error for 1LSB is determined using the following equation.

1LSB error =  $\frac{\text{(Vref $\pm$ corrected error)} \times \text{(Vref error)} \times \text{(power supply error)}}{2 \text{ (A/D resolution)}}$

Vref : Reference voltage built into the microcontroller (3.8V or 2)

Correction err : Error produced when correcting the internal correction resistance in the microcontroller.

+0.06%, -0% in relation to Vref (if REF = 3.8V, +2.28mV, -0V)

Vref error : Error for Vref (±1.3%)

Power supply error: Power supply error applied to the microcoroller (±?% (Ex.: ±4%))

A/D resolution : A/D resolution expressed as a number of bits (normally a value between 8 and 12 bits)

(2) Determine the A/D reading error in relation to the threshold value that has to be read. Determine the maximum and minimalues for the A/D reading.

Max. = (threshold value)  $\times$  (maximum value for 1 LSB) + (comparator offset) + (quantum error) Min. = (threshold value)  $\times$  (maximum value for 1 LSB) - (comparator offset) - (quantum error)

Threshold value : Threshold value specified by the microcontroller program (LSB value)

Max./Min./ values for 1LSB: Maximum and minimum values for the error of 1LSB determined in step (1).

Comparator offset: Offset voltage of the comparator built into the microcontroller (±10mV)

Quantum error : Error wh A/D conversion is carried out

The quantum error is as follows, depending on how the threshold value is

determined.

How threshold value is determined

Rounded off to upper value

Rounded off to lower value

+1. -0 LSB

+0. -1 LSB

Rounded off to whichever value is closer

±0.5 LSB

The results determined from steps (1) and (2) above serve as the A/D error for the microcontroller.

Please note the precautions on the following page concerning this procedure.

🖿 7828999 0021228 T65 륿

554

ROHM

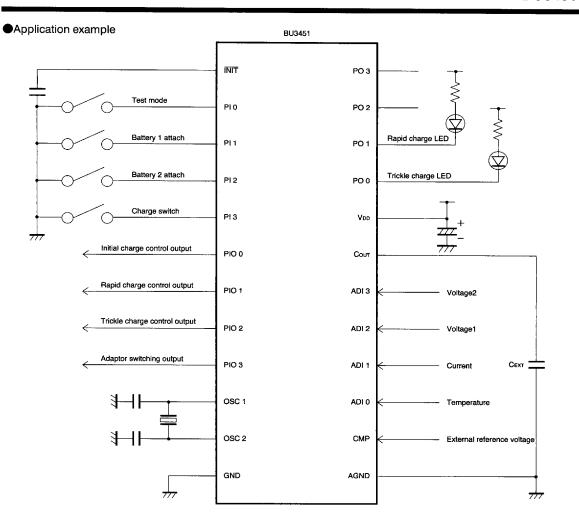

Fig.13 Application example showing use in battery charger

#### Precautions

- (1) In actual use, the tolerance range for the threshold value should be determined based on this result and the error up to the point of microcontroller input.

- (2) The power supply error in step (1) is produced because the microcontroller Vref is configured of the resistance divisions of the power supply. If the power supply error is such as the A/D input is the same as Vref, the power supply error should be ignored. For instance, this applies in cases where the battery thermistor is used and the divided resistance value is used for the A/D input.

- (3) The error is the absolute value from the equations on the previous page. When determining an absolute value (such as  $-\Delta V$ ), the following should be ignored: the power supply error in step (1), and the comparator offset in step (2). Also, the quantum error at this point will be +0/-1 LSB.

- (4) This error calculation does not include error based on leakage current from the capacitor. In order to minimize influence from leakage current, a film capacitor should be used.

7828999 0021229 9T1 **\*\*\*** \_\_\_\_\_\_

#### Electrical characteristic curves

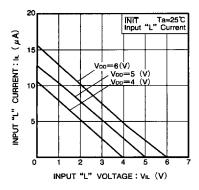

Fig. 14 INIT input "L" current characteristic

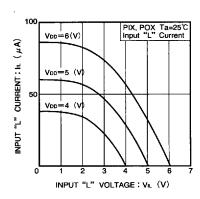

Fig.15 PIX and POX input "L" current characteristic

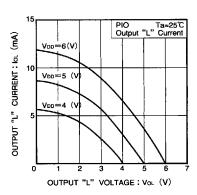

Fig.16 PIO output "L" current characteristic

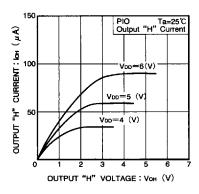

Fig.17 PIO output "H" current characteristic

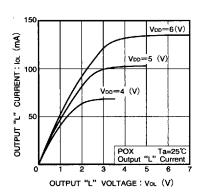

Fig. 18 POX output "L" current characteristic

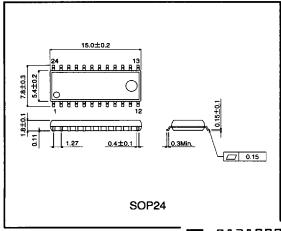

## External dimensions (Units: mm)

7828999 0021230 613 📟

556

MHO71