92D 00703 D

ZX54AHCT 193

# Zyfrex

February 1985 OBJECTIVE SPECIFICATIONS

### Features

- Look-ahead circuitry enhances cascaded counters

- Fully synchronous in count modes

- Parallel asynchronous load for modulo-N count lengths

- Asynchronous clear

- Function, pin-out, speed and drive compatibility with 54/74ALS logic family

- Low power consumption characteristic of CMOS

- High-Drive-Current outputs: I<sub>OL</sub> = 8 mA @ V<sub>OL</sub> = 0.5V

- Inputs and outputs interface directly with TTL, NMOS and CMOS devices

- Wide operating voltage range: 4.5V to 5.5V

- Characterized for operation over industrial and military temperature ranges:

74AHCT: -40°C to +85°C 54AHCT: -55°C to +125°C

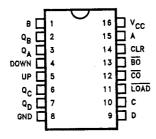

## Pin Configuration

0035-1

## Synchronous 4-Bit Up/Down Binary Counters with Dual Clock

Description

T-45-23-09

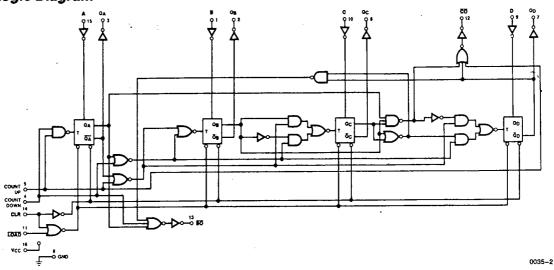

These are high-speed synchronous reversible 4-bit binary counters. Synchronous operation is provided by having all flip-flops clocked simultaneously so that the outputs change coincidently with each other when so instructed by the steering logic. This mode of operation eliminates the output counting spikes normally associated with asynchronous (ripple clock) counters.

The outputs of the four flip-flops are triggered by a lowto-high-level transition of either count (clock) input (Up or Down). The direction of counting is determined by which count input is pulsed while the other count input is high.

All four counters are fully programmable; that is, each output may be preset to either level by placing a low on the load input and entering the desired data at the data inputs. The output will change to agree with the data inputs independently of the count pulses. This feature allows the counters to be used as modulo-N dividers by simply modifying the count length with the preset inputs.

A clear input has been provided that forces all outputs to the low level when a high level is applied. The clear function is independent of the count and the load inputs. The clock, count, and load inputs are buffered to lower the drive requirements. This significantly reduces the loading on clock drivers, etc., for long parallel words.

These counters were designed to be cascaded without the need for external circuitry. The borrow output (BO) produces a low-level pulse while the count is zero (all outputs low) and the count-down input is low. Similarly, the carry output (CO) produces a low-level pulse while the count is maximum (9 or 15) and the count-up input is low. The counters can then be easily cascaded by feeding the borrow and carry outputs to the count-down and count-up inputs, respectively, of the succeeding counter.

Fabricated using Zytrex's proprietary ICE-MOS process, these devices provide speeds and drive capability equivalent to their ALSTTL counterparts and yet maintain CMOS power levels. The Input and output voltage levels allow direct interface with TTL, NMOS and CMOS devices without any external components.

All inputs and outputs are protected from damage due to static discharge by internal diode clamps to  $V_{CC}$  and ground.

92D 00704

0035-3

Logic Diagram

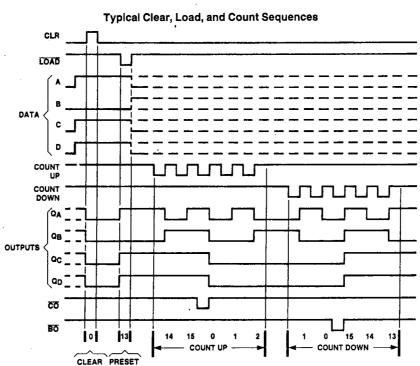

CLEAR PRESET

Sequence:

(1) Clear outputs to zero.

(2) Load (preset) to binary thirteen.

(3) Count up to fourteen, fifteen, carry, zero, one, and two.

(4) Count down to one, zero, borrow, fifteen, fourteen, and thirteen.

Note A: Clear overrides load data, and count inputs.

Note B: When counting up, count-down input must be high; when counting down, count-up input must be high.

## Zytrex

Absolute Maximum Ratings\*

\*Absolute Maximum Ratings are those values beyond which permanent damage to the device may occur. These are stress ratings only and functional operation of the device at or beyond them is not implied. Long exposure to these conditions may affect device reliability.

† Power Dissipation temperature derating: Plastic Package (N): -12 mW/°C from 65°C to 85°C Ceramic Package (J): -12 mW/°C from 100°C to 125°C

## Recommended Operating Conditions

\*Unused inputs must always be tied to an appropriate logic voltage level (either V<sub>CC</sub> or GND)

## DC Electrical Characteristics (V<sub>CC</sub> = 5V ± 10% Unless Otherwise Specified)

| Symbol          | Parameter                            | Test Conditions                                                                                 | T <sub>A</sub> = 25°C  |                             | 74AHCT<br>T <sub>A</sub> = -40°C to +85°C | 54AHCT<br>T <sub>A</sub> = -55°C to + 125°C | Unit |

|-----------------|--------------------------------------|-------------------------------------------------------------------------------------------------|------------------------|-----------------------------|-------------------------------------------|---------------------------------------------|------|

|                 |                                      |                                                                                                 | Тур                    |                             | Guaranteed Li                             | mits                                        |      |

| VIH             | Minimum High-Level<br>Input Voltage  |                                                                                                 |                        | 2.0                         | 2.0                                       | 2.0                                         | V    |

| V <sub>IL</sub> | Maximum Low-Level<br>Input Voltage   |                                                                                                 |                        | 0.8                         | 0.8                                       | 0.8                                         | V    |

| V <sub>OH</sub> | Minimum High-Level<br>Output Voltage | $V_{IN} = V_{IH} \text{ or } V_{IL}$ $I_{O} = -20 \mu A$ $I_{O} = -4 \text{ mA}$                | V <sub>CC</sub><br>4.2 | V <sub>CC</sub> 0.1<br>3.98 | V <sub>CC</sub> - 0.1<br>3.84             | V <sub>CC</sub> = 0.1<br>3.7                | V    |

| VoL             | Maximum Low-Level<br>Output Voltage  | $V_{IN} = V_{IH} \text{ or } V_{IL}$ $I_O = 20 \mu A$ $I_O = 4 \text{ mA}$ $I_O = 8 \text{ mA}$ | 0                      | 0.1<br>0.26<br>0.39         | 0.1<br>0.33<br>0.5                        | 0.1<br>0.4                                  | V    |

| liN             | Maximum Input<br>Current             | V <sub>IN</sub> = V <sub>CC</sub> or GND                                                        |                        | ±0.1                        | ± 1.0                                     | ± 1.0                                       | μΑ   |

| lcc             | Maximum Quiescent<br>Supply Current  | $V_{IN} = V_{CC} \text{ or GND}$<br>$I_{OUT} = 0 \mu A$                                         |                        | 8.0                         | 80.0                                      | 160.0                                       | μΑ   |

## 7519076 RADIATION SEMICONDUCTOR

92D 00706

$\textbf{\textit{AC Electrical Characteristics}} \text{ (Input } t_r, \, t_f \leq 2 \text{ ns), AHCT193}$

T-45 -23-09

| Symbol           | Parameter                                         |                                      | Conditions <sup>†</sup> | T <sub>A</sub> = 25°C<br>V <sub>CC</sub> = 5.0V | 74AHCT<br>T <sub>A</sub> = -40°C to +85°C<br>V <sub>CC</sub> = 5.0V ± 10% | 54AHCT<br>T <sub>A</sub> = -55°C to +125°C<br>V <sub>CC</sub> = 5.0V ±10% | Unit    |  |

|------------------|---------------------------------------------------|--------------------------------------|-------------------------|-------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|---------|--|

|                  |                                                   |                                      |                         | Тур                                             | Guaranteed Limits                                                         |                                                                           | <u></u> |  |

| f <sub>max</sub> | Maximum Clock Frequency                           |                                      |                         | 50 ´                                            | 30                                                                        | 25                                                                        | MHz     |  |

| tPLH             | Maximum Propagation Delay,<br>JP to CO            |                                      |                         | 12                                              | 19                                                                        | 23                                                                        | ns      |  |

| tPHL             |                                                   |                                      |                         | 12                                              | 19                                                                        | 23                                                                        |         |  |

| t <sub>PLH</sub> | Maximum Propa                                     | Maximum Propagation Delay,           |                         | 11                                              | 18                                                                        | 22                                                                        | ns      |  |

| tPHL             | DOWN to BO                                        |                                      | C <sub>L</sub> = 50 pF  | 11                                              | 18                                                                        | 22                                                                        |         |  |

| tpLH             | Maximum Propagation Delay,<br>UP or DOWN to any Q |                                      |                         | 18                                              | 30                                                                        | 36                                                                        | ns      |  |

| t <sub>PHL</sub> |                                                   |                                      |                         | 18                                              | 30                                                                        | 36                                                                        |         |  |

| <sup>1</sup> PLH | Maximum Propagation Delay,                        |                                      |                         | 16                                              | 26                                                                        | 31                                                                        | ns      |  |

| t <sub>PHL</sub> | OAD to any Q                                      |                                      |                         | 16                                              | 26                                                                        | 31                                                                        |         |  |

| tou              | Maximum Propagation Delay,<br>CLR to any Q        |                                      |                         | 13                                              | 22                                                                        | 26                                                                        | ns      |  |

| t <sub>w</sub>   | Minimum Pulse                                     | CLR High                             |                         | 6                                               | 10                                                                        | 15                                                                        | ns      |  |

|                  | Width                                             | LOAD Low                             |                         | 6                                               | 10                                                                        | 15                                                                        |         |  |

|                  |                                                   | UP or DOWN High or Low               | ,                       | 6                                               | 10                                                                        | 15                                                                        |         |  |

| t <sub>su</sub>  | Minimum Setup<br>Width                            | Data before <del>LOAD</del> ↑        |                         | 6                                               | 10                                                                        | 15                                                                        | ns      |  |

|                  |                                                   | CLR Inactive before UP↑ or DOWN↑     |                         | 6                                               | 10                                                                        | 15                                                                        |         |  |

|                  |                                                   | LOAD Inactive before<br>UP↑ or DOWN↑ |                         | 6                                               | 10                                                                        | 15                                                                        |         |  |

| t <sub>h</sub>   | Minimum Hold<br>Time                              | Data after LOAD ↑                    |                         | 0                                               | 0 -                                                                       | 0                                                                         | ns      |  |

|                  |                                                   | UP High after DOWN↑                  |                         | 0                                               | 0                                                                         | 0                                                                         |         |  |

|                  |                                                   | DOWN High after UP 1                 |                         | 0                                               | 0                                                                         | 0                                                                         |         |  |

| CIN              | Maximum Input Capacitance                         |                                      |                         | 5                                               |                                                                           |                                                                           | pF      |  |

| C <sub>PD</sub>  | Power Dissipati                                   | on Capacitance*                      |                         | 80                                              |                                                                           |                                                                           | ρF      |  |

<sup>\*</sup>Cpp determines the no-load dynamic power dissipation:  $P_D = C_{PD} \, V_{CC}^2 \, f + I_{CC} \, V_{CC}$ . For AC switching test circuits and timing waveforms see section 2.