JULY 1987

- Generates User-Programmable Control Signals (Horizontal Sync, Vertical Sync, and Blanking) Which Support a Broad Range of Raster-Scan Display Systems with Varying Resolutions and Scan Rates

- Provides Memory Refresh at User Programmable Rates

- When Combined with the SMJ4161 VRAM, Memory Availability to the Host is Virtually Unlimited, Since Display Access and Dynamic RAM Refresh Require Less than Six Percent of the Memory Bandwidth

- Directly Drives up to 64 SMJ4161 VRAMs or Conventional DRAM Memories with No External Buffering

- Synchronizes to an External Video Source, Which Allows Superimposing of an Image upon an Externally Generated Source

- Independent Video and System Clocks Allow the Video System and the Host Processor to Run Asynchronously

- Supports Both Interlaced and Noninterlaced Displays

- Interfaces Easily to a Wide Variety of Microprocessors (8, 16, 20, and 32-Bit Data Bus Widths)

- Can Be Configured to Support Dot Rates from 5 MHz up to 130 MHz, When Used in Conjunction with the SMJ4161

- X-Y Mode Supports Processors with Limited Addressing Range and More Efficient Drawing Algorithms

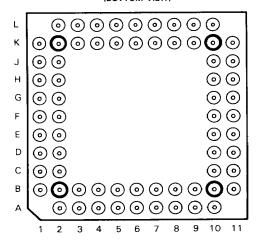

#### SMJ34061GB . . . 68-PIN PGA CERAMIC PACKAGE<sup>†</sup> (BOTTOM VIEW)

<sup>†</sup>See Pin Assignments Table (Page 2) and Pin Descriptions for location and description of all pins.

- 21 Address Bits Directly Access a 2 Megaword Address Space with Arbitrary Word Width

- Standard and Class B Processing

- SM Prefix . . . Standard Processing

- SMJ Prefix . . . Class B Processing

- Package Type Available:

- 68 Pin Grid Array (GB)

### description

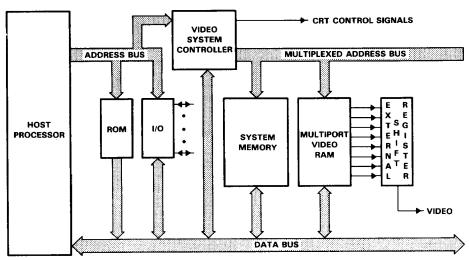

The high-performance Video System Controller (VSC) has been developed to control the video display and main memory subsystems of a bit-mapped graphics system. A monolithic NMOS device, the VSC controls the SMJ4161 Multiport Video RAM (VRAM) and 256K Multiport Video RAM, as well as the conventional 64K and 256K dynamic RAMs.

Most delays caused by conflicts with display update functions are eliminated by the VSC. The host is relieved of system memory control, the video memory refresh, and VRAM internal shift register reload for bit-mapped displays.

Highly programmable, the VSC supports a broad range of raster-scan display systems with various resolutions and scan rates.

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1987, Texas Instruments Incorporated

### PIN ASSIGNMENTS (GB PACKAGE)

| PIN | FUNCTION | PIN | FUNCTION | PIN | FUNCTION |

|-----|----------|-----|----------|-----|----------|

| A2  | RAO      | C11 | W        | J10 | CA6      |

| A3  | RA2      | D1  | RAS3     | J11 | CA7      |

| A4  | MA1      | D2  | RAS2     | K1  | RDY/HOLD |

| A5  | MA3      | D10 | TR/QE    | K2  | CEL      |

| A6  | $v_{SS}$ | D11 | RESET    | кз  | SYSCLK   |

| A7  | MA6      | E1  | RAS1     | K4  | FS0      |

| A8  | MA8      | E2  | RASO.    | K5  | FS2      |

| A9  | RA4      | E10 | R/W      | K6  | DO DO    |

| A10 | RA6      | E11 | CA0      | K7  | D2       |

| B1  | VCC      | F1  | ٧ss      | К8  | D4       |

| B2  | RS1      | F2  | CASHI    | K9  | D6       |

| В3  | RA1      | F10 | CA1      | K10 | CA8      |

| B4  | MAO      | F11 | $v_{SS}$ | K11 | Vcc      |

| B5  | MA2      | G1  | CASLO    | L2  | HOLDACK  |

| В6  | MA4      | G2  | BLANK    | L3  | CEH      |

| B7  | MA5      | G10 | CA2      | L4  | ALE      |

| B8  | MA7      | G11 | CA3      | L5  | FS1      |

| В9  | RA3      | H1  | VSYNC    | L6  | VSS      |

| B10 | RA5      | H2  | HSYNC    | L7  | D1       |

| B11 | RA7      | H10 | CA4      | L8  | D3       |

| C1  | RS0      | H11 | CA5      | L9  | D5       |

| C2  | ĊŚ       | J1  | VIDCLK   | L10 | D7       |

| C10 | RA8      | J2  | INT      |     |          |

The VSC performs four major functions:

- 1) Allows the host virtually unimpeded access to VRAMs, directly (host direct) or indirectly (X-Y).

- Automatically generates the DRAM-refresh cycles needed to maintain data stored within the DRAMs.

- Performs display-update cycles needed to periodically load new video data into the VRAM shift registers.

- 4) Generates sync and blanking signals necessary for monitor control.

All VSC inputs and outputs are TTL compatible. The VSC is guaranteed for operation from -55°C to 110°C.

### typical system block diagram

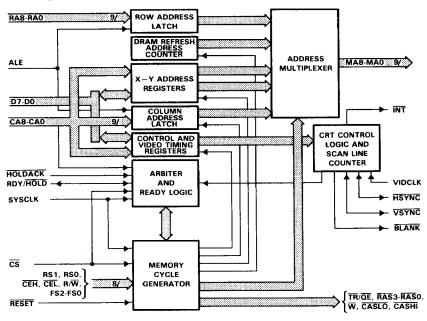

### functional block diagram

# SM/SMJ34061 VIDEO SYSTEM CONTROLLER

## pin descriptions

| NAME           | I/O   | DESCRIPTION                                                                                                             |

|----------------|-------|-------------------------------------------------------------------------------------------------------------------------|

| MA8-MA0        | 0     | Memory Address. These memory address outputs are multiplexed address lines designed to interface directly to            |

|                |       | SMJ4161 VRAMs, as well as conventional DRAMs. MA0 is the LSB.                                                           |

| RA8-RAO        | ı     | Row Address. These address inputs are multiplexed to memory address pins MA8-MA0 during row address time                |

|                |       | when a host-initiated memory access cycle is executed. For host-initiated shift register-transfer cycles, these inputs  |

|                |       | are multiplexed to MA8-MAO during column address time. RAO is the LSB.                                                  |

| CA8-CA0        | 1     | Column Address. These address inputs are multiplexed to memory address pins MA8-MA0 during column address               |

|                |       | time when a host-initiated memory access cycle is executed. For a host-initiated shift register-transfer cycle, these   |

|                |       | inputs are multiplexed to MA8-MA0 during row address time. CA0 is the LSB.                                              |

| RS1,RS0        | - 1   | Row Address Strobe Selects. During host-direct cycles and shift register-transfer cycles, these signals determine       |

|                |       | which of the four row address strobes, RAS3-RAS0, is driven active low. If extended RAS mode is enabled,                |

|                |       | these inputs are ignored.                                                                                               |

| CEH            | _ ' _ | Column Address Enable High. An active low from this signal enables CASHI during a host-initiated memory cycle.          |

| CEL            | - 1   | Column Address Enable Low. An active low from this signal enables CASLO during a host-initiated memory access           |

|                |       | cycle. CEL also strobes data into the internal registers during register write cycles and enables register data onto    |

|                |       | D7-D0 during register read cycles.                                                                                      |

| ALE            | 1     | Address Latch Enable. The high-to-low transition of ALE latches the CS, RA8-RA0, CA8-CA0, RS1-RS0, and                  |

|                |       | FS2-FS0 inputs and is interpreted by the VSC as a command from the host to initiate the cycle specified by the          |

|                |       | values latched at these inputs.                                                                                         |

| R/W            | 1     | Read/Write. During a host initiated memory cycle or internal register access, R/W determines the direction of data      |

|                |       | transfer (high for read, low for write). By appropriately controlling the state of the R/W input, the system is allowed |

|                |       | to execute the following cycles: read, write, early write, or read-modify-write.                                        |

| ĪNĪ            | 0     | Interrupt Request. The interrupt-request output indicates that an interrupt condition previously enabled by the host    |

|                | ĺ     | processor has occurred. INT will remain active until the host processor initiates a read of the Status Register.        |

| D7-D0          | 1/0   | Data Bus. The host accesses the internal registers of the VSC through this 8-bit bidirectional data bus. Each host-     |

|                |       | accessible register within the VSC must be accessed one byte at a time via D7-D0. D0 is the LSB.                        |

| RDY/HOLD       | 0     | Ready or Hold. The operation and timing of RDY/HOLD is defined by two control bits contained in Control                 |

|                |       | Register 2. RDY/HOLD can be configured to operate in "ready," "wait," or "hold" modes to accommodate various            |

|                |       | host processor interfaces.                                                                                              |

| HOLDACK        | ī     | Hold Acknowledge. When the VSC is configured in hold/hold acknowledge mode, the host issues a handshaking               |

| l              | - 1   | signal by driving HOLDACK low. The VSC can perform an internally requested cycle (display update or DRAM                |

|                |       | refresh) in this mode only when a handshaking acknowledgment has been received. HOLDACK is also used to                 |

|                |       | configure the active level of RDY/HOLD at system power up.                                                              |

| <del>C</del> S | 1     | Chip Select. This input operates as a master chip select. Before any host-initiated access involving the VSC can        |

|                |       | begin, CS must be active low.                                                                                           |

| FS2-FS0        | ī     | Function Select. The three-bit function select code input on FS2-FS0 indicates the type of cycle requested by the       |

|                |       | host processor.                                                                                                         |

## pin descriptions (continued)

| NAME          | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                   |  |  |  |

|---------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SYSCLK        | ı   | System Clock. This input is used to generate the timing of signals output to the memory, and the timing of the INT and the RDY/HOLD signals output to the host. All host interface signals input to the VSC must be synchronous To SYSCLK.                                                                    |  |  |  |

| RESET         | 1   | Reset. An active-low RESET places the VSC in a known initial state. While RESET is low, the internal registers are forced to their default values, and all VRAM control outputs are forced to their inactive levels. RESET should be driven low when power is first applied and remain low for at least 1 ms. |  |  |  |

| RAS3-<br>RAS0 | 0   | Row Address Strobes. These active-low outputs are designed to drive the RAS inputs on both the SMJ4161 VRAM and conventional DRAMs. During display update and refresh cycles, all four RAS outputs are driven active low in the default mode of operation.                                                    |  |  |  |

| CASHI         | 0   | Column Address Stobe High. This active-low output is designed to directly drive the CAS inputs on both the SMJ4161 VRAM and conventional DRAMs. During memory cycles initiated by the host, CASHI becomes active only after the CEH input is driven active low.                                               |  |  |  |

| CASLO         | 0   | Column Address Strobe Low. The operation of CASLO is similar to that of CASHI, as described above, except that CASLO is enabled by an active low on CEL rather than CEH.                                                                                                                                      |  |  |  |

| ₩             | 0   | Write Control. This signal is used to drive the $\overline{W}$ inputs on both the SMJ4161 VRAM and conventional DRAMs. $\overline{W}$ is driven active low during write cycles requested by the host.                                                                                                         |  |  |  |

| TR/QE         | 0   | Shift Register Transfer and Output Enable. The TR/OE output directly drives the TR/OE inputs on the SMJ4161 VRAM. Signals used to enable shift register-transfer cycles and VRAM output buffers during read cycles are multiplexed over this single pin.                                                      |  |  |  |

| BLANK         | 0   | Video Blanking. The BLANK output is used to disable video data to the CRT monitor. BLANK is driven active low during both horizontal and vertical blanking intervals.                                                                                                                                         |  |  |  |

| HSYNC         | 1/0 | Horizontal Sync. HSYNC generates the horizontal sync pulses used to control a CRT monitor. It operates as an output, except when the external sync mode is enabled.                                                                                                                                           |  |  |  |

| VSYNC         | 1/0 | Vertical Sync. VSYNC generates the vertical sync pulses used to control a CRT monitor and operates as an output except when the external sync mode is enabled.                                                                                                                                                |  |  |  |

| VIDCLK        | ı   | Video Clock. The video input clock drives the logic within the VSC chip that is responsible for generating the timing for the sync and blanking signals. VIDCLK also drives the logic responsible for generating internal requests for display update and VRAM refresh cycles.                                |  |  |  |

| Vcc           |     | 5-volt supply input.                                                                                                                                                                                                                                                                                          |  |  |  |

| Vss           |     | Ground.                                                                                                                                                                                                                                                                                                       |  |  |  |

### programmable registers

The programmable registers in the SM/SMJ34061 allow configuration of the CRT timings, system CPU interface, and X-Y address parameters. Most of these registers contain bits that are not currently implemented; these bits are designated in the following tables by an "X." To maintain compatibility with future device upgrades, a logical zero should be written to these bits.

| TARIF 1 | VIDEO | TIMING | REGISTERS |

|---------|-------|--------|-----------|

|         |       |        |           |

| REGISTER NAME | UPPER BYTE | LOWER BYTE | ADDRESS |                                                                           |

|---------------|------------|------------|---------|---------------------------------------------------------------------------|

| REGISTER NAME | CA1 = 1    | CA1 = 0    | CA6-CA2 | DESCRIPTION                                                               |

| Horizontal    | XXXXAAAA   | AAAAAAA    | 00000   | Identifies the end of horizontal sync interval. Contents = horizontal     |

| End Sync      |            |            |         | sync width - 1 VIDCLK unit                                                |

| Horizontal    | XXXXAAAA   | AAAAAAA    | 00001   | Identifies the end of horizontal blank interval. Contents = horizontal    |

| End Blank     |            |            |         | sync width + horizontal back porch - 1 VIDCLK unit                        |

| Horizontal    | XXXXAAAA   | AAAAAAA    | 00010   | Identifies the start of horizontal blank interval. Contents = horizontal  |

| Start Blank   |            |            |         | sync width + horizontal back porch + horizontal active screen -           |

|               |            |            |         | 1 VIDCLK unit                                                             |

| Horizontal    | XXXXAAAA   | AAAAAAA    | 00011   | Identifies the start of horizontal sync interval. Contents = total line   |

| Total         |            |            |         | time - 1 VIDCLK unit                                                      |

| Vertical      | XXXXAAAA   | ΑΑΑΑΑΑΑ    | 00100   | Identifies the end of vertical sync interval. Contents = vertical sync    |

| End Sync      |            |            |         | width - 1 horizontal total units                                          |

| Vertical      | XXXXAAAA   | AAAAAAA    | 00101   | Identifies the end of vertical blanking interval. Contents = vertical     |

| End Blank     |            |            |         | sync width + vertical back porch - 1                                      |

| Vertical      | XXXXAAAA   | AAAAAAA    | 00110   | Identifies the start of vertical blank interval. Contents = vertical sync |

| Start Blank   |            |            |         | + vertical back porch + vertical active - 1 horizontal total units        |

| Vertical      | XXXXAAAA   | AAAAAAA    | 00111   | Identifies the start of vertical sync interval. Contents = number of      |

| Total         |            |            |         | horizontal lines - 1 horizontal total units                               |

NOTE: "A" = active register bit, "X" = bit not implemented.

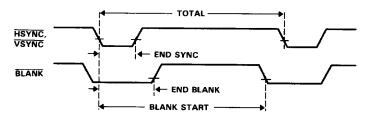

FIGURE 1. SYNC AND BLANK RELATIONSHIP

The following equations show the derivation of the various parameters required to initialize the VSC to interface to any CRT monitor:

```

Horizontal End Sync = Horizontal Sync Width - 1

Horizontal End Blank = Horizontal Sync Width + Horizontal Back Porch - 1

Horizontal Start Blank = Horizontal Sync Width + Horizontal Back Porch + Horizontal

Active Screen - 1

Horizontal Total = Total Line Time - 1

Vertical End Sync = Vertical Sync Width - 1

Vertical End Blank = Vertical Sync Width + Vertical Back Porch - 1

Vertical Start Blank = Vertical Sync Width + Vertical Back Porch + Vertical Active Screen - 1

Vertical Total = Number of Horizontal Lines - 1

```

All horizontal timing parameters are in VIDCLK units, and all vertical timing parameters are in horizontal line time units.

## **TABLE 2. CPU INTERFACE REGISTERS**

| REGISTER NAME | UPPER BYTE  CA1 = 1 | LOWER BYTE<br>CA1 = 0 | ADDRESS<br>CA6-CA2 | DESCRIPTION                                                             |

|---------------|---------------------|-----------------------|--------------------|-------------------------------------------------------------------------|

| Control       | XAAAAAA             | AAAXAAA               | 01011              | Controls the behavior of host interface signals, the timing of display- |

| Register 1    |                     |                       |                    | update cycles, the enabling of interrupt requests, the frequency of     |

| Control       | XAAAAAA             | AAAAAAA               | 01100              | DRAM-refresh cycles, and the configuration of video timing signals.     |

| Register 2    |                     |                       |                    |                                                                         |

TABLE 3. CONTROL REGISTER 1 BIT DEFINITIONS

| BITS       | NAME                      |  |  |

|------------|---------------------------|--|--|

| B3-B0      | Line Count Limit          |  |  |

| B4         | Reserved                  |  |  |

| B5         | Display-Update Inhibit    |  |  |

| В6         | Display-Update Direction  |  |  |

| <b>B</b> 7 | Display-Update RAS Mode   |  |  |

| B8         | External Sync Enable      |  |  |

| B9         | Interlace Enable          |  |  |

| B10        | Vertical Interrupt Enable |  |  |

| B11        | Error Interrupt Enable    |  |  |

| B12-B14    | Refresh Burst Length      |  |  |

| B15        | Reserved                  |  |  |

**TABLE 4. CONTROL REGISTER 2 BIT DEFINITIONS**

| BITS    | NAME                          |  |  |

|---------|-------------------------------|--|--|

| B1-B0   | Extended RAS-Mode Select Bits |  |  |

| B5-B2   | RAS Overrides                 |  |  |

| В6      | Extended RAS Mode             |  |  |

| B7      | X-Y Address Pointer RAS Mode  |  |  |

| B10-B8  | Wait State Limit              |  |  |

| B12-B11 | RDY/HOLD Mode Select          |  |  |

| B13     | Blank Entire Display          |  |  |

| B14     | Early RDY Enable              |  |  |

| B15     | Reserved                      |  |  |

**TABLE 5. STATUS REGISTER**

| REGISTER NAME | UPPER BYTE<br>CA1 = 1 | LOWER BYTE<br>CA1 = 0 | ADDRESS<br>CA6-CA2 | DESCRIPTION                                           |

|---------------|-----------------------|-----------------------|--------------------|-------------------------------------------------------|

| Status        | XXXXXXX               | XXXXXAAA              | 01101              | An error condition or vertical interrupt has occurred |

#### **TABLE 6. STATUS REGISTER BIT DEFINITIONS**

| BITS | NAME               |

|------|--------------------|

| BO   | Vertical Interrupt |

| B1   | Display Error      |

| B2   | Refresh Error      |

#### **TABLE 7. VERTICAL INTERRUPT REGISTER**

| REGISTER NAME | UPPER BYTE<br>CA1 = 1 | LOWER BYTE<br>CA1 = 0 | ADDRESS<br>CA6-CA2 | DESCRIPTION                                                        |

|---------------|-----------------------|-----------------------|--------------------|--------------------------------------------------------------------|

| Vertical      | XXXXAAAA              | AAAAAAA               | 01010              | Generates a vertical interrupt when contents are equal to Vertical |

| Interrupt     |                       |                       |                    | Counter                                                            |

#### **TABLE 8. CRT CONTROL REGISTERS**

| REGISTER NAME      | UPPER BYTE<br>CA1 = 1 | LOWER BYTE<br>CA1 = 0 | ADDRESS<br>CA6-CA2 | DESCRIPTION                                                                          |

|--------------------|-----------------------|-----------------------|--------------------|--------------------------------------------------------------------------------------|

| Display<br>Address | XXXXAAAA              | AAAAAAA               | 10000              | Contains the address to be output during the next automatic display-<br>update cycle |

| Display<br>Update  | xxxxxxx               | XXXXAAAA              | 01000              | Contains the value by which the display address is incremented                       |

| Display<br>Start   | XXXXAAAA              | AAAAAAA               | 01001              | Specifies the memory location to be displayed at the upper left of the screen        |

#### **TABLE 9. X-Y REGISTERS**

| REGISTER NAME    | UPPER BYTE | LOWER BYTE | ADDRESS | DESCRIPTION                                                      |  |  |  |

|------------------|------------|------------|---------|------------------------------------------------------------------|--|--|--|

| TIEGIO TER MAINE | CA1 = 1    | CA1 = 0    | CA6-CA2 |                                                                  |  |  |  |

| X-Y Address      | AAAAAAA    | AAAAAAA    | 01111   | Contains address for host-indirect memory accesses               |  |  |  |

| X-Y Offset       | XXXXAAAA   | ААААААА    | 01110   | Defines the boundary between the X-Y portions of the X-Y Address |  |  |  |

|                  |            |            |         | Register and contains the initial value of the two RAS-select l  |  |  |  |

|                  |            |            |         | and the two independent multiplexed address bits                 |  |  |  |

### address multiplexer

The address multiplexer provides the Multiport VRAM array with row, column, and internal addresses at the proper times. Its inputs are from the host system, the display address register, the X-Y indirect address register, and the DRAM refresh address counter. The specific source of the address is controlled by the arbiter, and the RA or CA portion of the address is controlled by the memory cycle generator. Eighteen multiplexed address signals are provided by the 9-bit MA address outputs. The address multiplexer directly drives inputs for up to 64 SMJ4161 Multiport VRAM devices or conventional dynamic RAM devices of up to 256K bits.

#### **DRAM** refresh counters

Programmable DRAM refresh cycles allow the VSC to relieve the host of refresh burden. The refresh burst length is determined by bits 14-12 in Control Register 1. These three bits output a binary number from 000 to 111 which indicates the number of DRAM refresh cycles, from 0 to 7 per horizontal line. This binary number is then counted by the Refresh Burst Counter (host inaccessible). The Refresh Burst Counter outputs a 9-bit row address to the Address Multiplexers during DRAM refresh cycles, while the Memory Cycle Generator increments the DRAM Refresh Register (host inaccessible) to the next 9-bit row address to be output.

### X-Y address capability

X-Y addressing is particularly useful when the linear addressing range of the host is insufficient to provide proper access of all pixels on the screen. The contents of the X-Y registers replace the RA and CA outputs as source of the memory address. A 4-bit code on inputs CA4-CA1 determines address adjustment (increment, decrement, clear, no change). X-Y capability relieves the host from calculating the address of the next pixel to be modified.

#### arbiter

The arbiter determines whether the host processor, the video shift-register reload logic, or the dynamic-RAM refresh logic can access the memory or start a reload or refresh cycle. Since the display and refresh functions of the VSC normally use less than six percent of the available memory cycles, the arbiter usually grants immediate memory access to the host. When a conflict arises, the arbiter grants priority as follows:

- 1) Any cycle in progress

- 2) A display update cycle (internally granted request)

- 3) A DRAM-refresh cycle that has been delayed for more than ½ horizontal line

- 4) Any host-requested cycle

- 5) DRAM-refresh cycle

### memory cycle generator

Various memory cycles requested by the arbiter are performed by the Memory Cycle Generator, which also provides the DRAM array with the RAS, CAS, TR/QE, and W signals. It controls the multiplexer during all cycles in order to meet the address and control line-setup and hold requirements. Cycles generated:

- Host-requested cycles

- Read

- -- Write

- Early Write

- Read-modify-write

- Memory-to-shift register

- Shift register-to-memory

- Delayed host-requested cycles

- Internally requested shift register transfer

- Internally requested refresh cycle

### **CRT** control

The VSC generates the HSYNC, VSYNC, and BLANK signals used to drive a CRT monitor in a bit-mapped graphics system. These signals are synchronous to the Video Input Clock (VIDCLK). HSYNC, VSYNC, and BLANK are programmed through eight host-accessible video timing registers, which are easily configured to accommodate a variety of display resolutions and CRT monitors in either intertlaced or non-interlaced modes. Two additional registers, clocked by VIDCLK, maintain the current horizontal and vertical counts.

The values in these two counters are compared with the values in the eight video timing registers to determine the limits of the sync and blanking intervals. Programmed synchronization of external sync signals allows the VSC to superimpose an image upon an externally generated video source.

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage, VCC (see Note 1)       | 7 V           |

|----------------------------------------|---------------|

| Input voltage range                    | -0.3 V to 7 V |

| Off-state output voltage range         | 2 V to 7 V    |

| Maximum operating case temperature     | 110°C         |

| Minimum operating free-air temperature | – 55°C        |

| Storage temperature range              | 5°C to 150°C  |

<sup>†</sup>Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values in this data sheet are with respect to VSS.

#### recommended operating conditions

|          |                            |                                              | MIN  | NOM | MAX   | UNIT |

|----------|----------------------------|----------------------------------------------|------|-----|-------|------|

| Vcc      | Supply voltage             |                                              | 4.5  |     | 5.5   | V    |

| $v_{SS}$ | Supply voltage             |                                              |      | 0   |       | V    |

| $v_{IH}$ | High-level input voltage   |                                              | 2.2  |     | i     | V    |

| $V_{IL}$ | Low-level input voltage    |                                              |      |     | 0.8   | V    |

| lон      | High-level output current  | VSYNC, HSYNC, BLANK,<br>INT, RDY/HOLD, D7-D0 |      |     | - 370 | μΑ   |

| loL      | Low-level output current   | VSYNC, HSYNC, BLANK,<br>INT, RDY/HOLD, D7-D0 |      |     | 3.2   | mA   |

| TC       | Operating case temperatur  | e                                            |      |     | 110   | °C   |

| TA       | Operating free-air tempera | ture                                         | ~ 55 |     |       | °C   |

## electrical characteristics over recommended temperature range

|      | PARAMETER                 | TEST CONDITIONS                            |                        | SMJ34   | UNIT         |    |

|------|---------------------------|--------------------------------------------|------------------------|---------|--------------|----|

|      | TAGOWETEN                 |                                            |                        | MIN TYP | MIN TYP† MAX |    |

| ۷он  | High-level output voltage | V <sub>CC</sub> = MIN,                     | I <sub>OH</sub> = MAX  | 2.4     |              | V  |

| VOL  | Low-level output voltage  | V <sub>CC</sub> = MAX,                     | I <sub>OL</sub> = MAX  |         | 0.6          | V  |

| 1cc  | Supply current            | V <sub>CC</sub> = MAX                      |                        | 225     | 315          | A  |

|      | Supply cultent            | $V_{CC} = MAX$                             | T <sub>C</sub> = 110°C | 185     | 225          | mA |

| ю    | High-impedance            | V <sub>CC</sub> = MAX                      | $V_0 = 2.4 \text{ V}$  |         | 20           |    |

| ٠٥   | output current            |                                            | V <sub>O</sub> = 0.6 V |         | - 20         | μΑ |

| lį – | Input current             | V <sub>I</sub> = V <sub>SS</sub> to V      | vcc                    |         | ± 25         | μΑ |

|      |                           | RAS3-RASO, CASLO,<br>CASHI, MAO-MA8, TR/QE |                        |         |              |    |

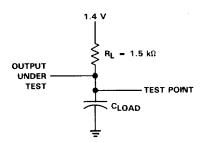

|      | Output loading            |                                            |                        | 350     |              | pF |

|      | (see Figure 2)            | W                                          |                        |         | 670          |    |

<sup>&</sup>lt;sup>†</sup>All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25 ^{\circ}\text{C}$ .

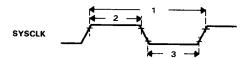

# system clock timing parameters (see Notes 2 and 3)

|               |                                          | SMJ     | SMJ34061 |    |

|---------------|------------------------------------------|---------|----------|----|

| NO. PARAMETER |                                          | MIN MAX | UNIT     |    |

| 1             | t <sub>cSC</sub> SYSCLK clock period     | 100     | 500      | ns |

| 2             | tw(SCH) SYSCLK clock high pulse duration | 48      | 246      | ns |

| 3             | tw(SCL) SYSCLK clock low pulse duration  | 48      | 246      | ns |

NOTES: 2. SYSCLK frequency must be greater than one-half the VIDCLK frequency.

3. All switching characteristics are measured between the maximum low level and the minimum high level using the 10 percent and 90 percent points.

# memory and host interface timing parameters

|     | DAGAMETER                |                                                                                                                 | SI  | MJ34061 | UNIT |  |

|-----|--------------------------|-----------------------------------------------------------------------------------------------------------------|-----|---------|------|--|

| NO. |                          | PARAMETER                                                                                                       |     |         |      |  |

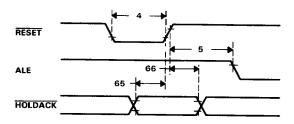

| 4   | tw(RSTL)                 | Reset active (low) pulse duration                                                                               | . 1 |         | ms   |  |

| 5   | th(RSTH-ALEH)            | Reset wait period after a reset low-to-high transition pulse and prior to the first host-requested memory cycle | 1   |         | ms   |  |

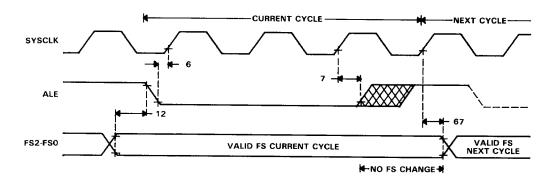

| 6   | t <sub>su(ALE-SCH)</sub> | Setup time of ALE low or high to SYSCLK no longer low (see Note 4)                                              | 20  |         | ns   |  |

| 7   | th(SCH-ALE)              | Hold time of ALE low or high after SYSCLK high (see Note 4)                                                     | 10  |         | ns   |  |

| 8   | tw(ALEH)                 | Pulse duration of ALE high                                                                                      | 40  |         | ns   |  |

| 9   | t <sub>su</sub> (CE-SCH) | Setup time of CEL or CEH low or high to SYSCLK no longer low (see Note 4)                                       | 20  |         | ns   |  |

| 10  | th(SCH-CE)               | Hold time of CEL or CEH low or high after SYSCLK high (see Note 4)                                              | 10  |         | ns   |  |

| 11  | tsu(ADDR-ALEL)           | Setup time of RA, CA, RS, or CS input valid before ALE not longer high                                          | 35  |         | ns   |  |

| 12  | t <sub>su(FS-ALEL)</sub> | Setup time of FS input valid before ALE no longer high                                                          | 55  |         | ns   |  |

| 13  | th(ALEL-ADDR)            | Hold time of RA, CA, FS, RS, or CS input valid after ALE low                                                    | 10  |         | ns   |  |

| 14  | <sup>t</sup> d(SCH-RMA)H | Delay from SYSCLK high to row memory address valid, host initiated memory cycle (see Note 5)                    |     | 80      | ns   |  |

| 15  | th(SCH-RMA)              | Hold time of row address valid after SYSCLK no longer low <sup>†</sup>                                          | 10  | 60      | ns   |  |

| 16  | td(SCH-CMA)              | Delay from SYSCLK high to column memory address valid (see Note 5)                                              | 20  | 80      | ns   |  |

| 17  | th(ALEH-CMA)             | Hold time of column memory address valid after ALE                                                              | 0   |         | ns   |  |

| 18  | td(SCL-RASL)             | Delay from SYSCLK low to RAS low (See note 5)                                                                   | 15  | 70      | ns   |  |

| 19  | td(ALEH-RASH)            | Delay from ALE high to RAS high (see Note 5)                                                                    | 20  | 75      | ns   |  |

| 20  | <sup>t</sup> d(SCH-RASH) | Delay from SYSCLK high to $\overline{\text{RAS}}$ high in display update and DRAM refresh (see Note 5)          | 20  | 75      | ns   |  |

| 21  | td(ALEL-RDYL)            | Delay from ALE low to RDY/HOLD at "not ready" level                                                             |     | 40      | ns   |  |

| 22  | td(SCL-RDYH)             | Delay from SYSCLK low to RDY/HOLD at "ready" level (see Note 6)                                                 |     | 70      | ns   |  |

| 23  | td(SCH-RDYH)             | Delay from SYSCLK high to RDY/HOLD at "ready" level (see Note 6)                                                |     | 75      | ns   |  |

†Row address hold time guaranteed by th(RMA) parameter.

NOTES: 4. ALE, CEH, and CEL inputs are synchronous to SYSCLK and must meet the required setup and hold times specified with respect to each SYSCLK low-to-high transition in order to guarantee correct operation.

5. This timing is based on a load circuit equivalent to 64 SMJ4161 VRAMs being driven by the VSC. Each of the following outputs drives a 350-pF capacitance to VSS: MA8-MA0, CASLO, CASLO, CASLO, TR/QE. The W output drives a 670-pF capacitance to ground. All other outputs drive a 560-ohm resistor tied to a 2.2-volt source with a 100 pF capacitance load tied to VSS.

6. All references made to the RDY/HOLD signal in the timing spec assume an active high level.

# SM/SMJ34061 VIDEO SYSTEM CONTROLLER

# memory and host interface timing parameters (continued)

| NO. | PARAMETER                  |                                                                                                                            | SM | UNIT    |      |

|-----|----------------------------|----------------------------------------------------------------------------------------------------------------------------|----|---------|------|

|     |                            |                                                                                                                            |    | TYP MAX | UNIT |

| 24  | td(ALEH-RDYZ)              | Delay from ALE no longer low to RDY/HOLD high-impedance level starting from RDY/HOLD (see Note 6)                          |    | 40      | ns   |

| 25  | td(SCL-CASL)               | Delay from SYSCLK low to CAS low to CASLO or CASHI (see Note 5)                                                            | 15 | 75      | ns   |

| 26  | td(ALEH-CASH)              | Delay from ALE, CEH, or CEL high to CASLO or CASHI high (see Note 5)                                                       | 20 | 60      | ns   |

| 27  | td(SCL-TRL)                | Delay from SYSCLK low to TR/QE low (see Note 5)                                                                            | 15 | 70      | ns   |

| 28  | td(ALEH-TRH)               | Delay from ALE, CEH, or CEL high to TR/QE high (see Note 5)                                                                | 20 | 60      | ns   |

| 29  | td(SCH-WL)HX               | Delay from SYSCLK high to $\overline{W}$ low (see Note 5), host direct or X-Y indirect cycle                               | 20 | 90      | ns   |

| 30  | td(ALEH-WH)                | Delay from ALE high to W high (see Note 5)                                                                                 | 20 | 90      | ns   |

| 31  | t <sub>d</sub> (RWL-WL)    | Delay from R/W low to W low (see Note 5)                                                                                   | 20 | 90      | ns   |

| 32  | td(RWH-WH)                 | Delay from R/W high to W high (see Note 5)                                                                                 | 20 | 90      | ns   |

| 33  | <sup>t</sup> d(SCH-WL)SR   | Delay from SYSCLK high to $\overline{W}$ or $\overline{TR}/\overline{QE}$ low, shift-register-transfer cycles (see Note 5) | 20 | 90      | ns   |

| 34  | th(ALEL-CELH)              | Hold time of CEL high after ALE no longer high, register cycle                                                             | 0  |         | ns   |

| 35  | th(CELH-ALEL)              | Hold time of ALE low after CEL no longer low, register cycle                                                               | 0  |         | ns   |

| 36  | t <sub>su(RW-CELL)</sub>   | Setup time of R/W valid to CEL no longer high, register cycle                                                              | 30 |         | ns   |

| 37  | th(CELH-RW)                | Hold time of R/W valid after CEL high, register cycle                                                                      | 10 |         | ns   |

| 38  | td(CELL-D)                 | Delay time from CEL low to D7-D0 valid all but status, register cycle                                                      | 20 | 130     | ns   |

| 39  | <sup>‡</sup> d(SCH-D)      | Data valid after next SYSCLK rising edge following CEL low for status read cycle only                                      |    | 130     | ns   |

| 40  | ¹d(CELH-DZ)                | Delay from CEL high to D7-D0 high impedance, register cycle                                                                |    | 105     | ns   |

| 41  | <sup>t</sup> d(CL-RDYH)HX  | Delay from CEL or CEH low to RDY/HOLD at the "ready" level, host access cycle (see Note 6)                                 |    | 90      | ns   |

| 42  | t <sub>su(D-CELH)</sub>    | Setup time of D7-D0 valid to CEL no longer low, register write                                                             | 60 |         | ns   |

| 43  | th(CELH-D)                 | Hold time of D7-D0 valid after CEL high, register write                                                                    | 10 |         | ns   |

| 44  | t <sub>su</sub> (RWL-CELH) | Setup time of R/W low to CEL no longer low, register write                                                                 | 80 |         | ns   |

| 45  | <sup>t</sup> d(RWL-DZ)     | Delay from R/W low to D7-D0 high impedance, register read-modify-write                                                     |    | 115     | ns   |

| 46  | td(ALEL-CL)                | Delay from ALE low to CEL low or CEH low                                                                                   | 0  |         | ns   |

| 47  | td(CE-CASL)                | Delay from late CEL or CEH to CASLO or CASHI for late CAS cycles                                                           |    | 60      | ns   |

| 48  | <sup>t</sup> d(SCH-RMA)D   | Delay from SYSCLK high to row memory address valid,<br>display update cycle (see Note 5)                                   |    | 70      | ns   |

| 49  | <sup>t</sup> h(SCH-CMA)    | Hold time of column address valid after SYSCLK no longer low, display update cycle (see Note 5)                            | 0  |         | ns   |

| 50  | td(SCH-CASH)               | Delay from SYSCLK high to CAS high (see Note 5)                                                                            | 20 | 75      | ns   |

| 51  | td(SCH-TRL)                | Delay from SYSCLK high to TR/QE low, display-update cycle (see Note 5)                                                     | 20 | 65      | ns   |

| 52  | td(SCL-TRH)                | Delay from SYSCLK low to TR/QE high, display-update cycle (see Note 5)                                                     | 20 | 80      | ns   |

$^{\dagger}$ Row address hold time guaranteed by  $t_{h}(RMA)$  parameter.

NOTES: 4. ALE, CEH, and CEL inputs are synchronous to SYSCLK and must meet the required setup and hold times specified with respect to each SYSCLK low-to-high transition in order to guarantee correct operation.

- 5. This timing is based on a load circuit equivalent to 64 SMJ4161 VRAMs being driven by the VSC. Each of the following outputs drives a 350-pF capacitance to VSS: MA8-MA0, CASLO, CASHI, RAS3-RAS0, TR/QE. The W output drives a 670-pF capacitance to ground. All other outputs drive a 560-ohm resistor tied to a 2.2-volt source with a 100 pF capacitance load tied to VSS.

- 6. All references made to the RDY/HOLD signal in the timing spec assume an active high level.

14-294

POST OFFICE BOX 1443 . HOUSTON, TEXAS 77001

## memory and host interface timing parameters (concluded)

|     |                            |                                                                                            | SI  | VIJ3406 | 31  | UNIT      |

|-----|----------------------------|--------------------------------------------------------------------------------------------|-----|---------|-----|-----------|

| NO. |                            | PARAMETER                                                                                  | MIN | TYP N   | XAN | AX   Citi |

| 53  | td(SCH-WL)                 | Delay from SYSCLK high to W low, display-update cycle (see Note 5)                         | 20  |         | 90  | ns        |

| 54  | td(SCH-WH)                 | Delay from SYSCLK high to W high, display-update cycle (see Note 5)                        | 20  |         | 90  | ns        |

| 55  | th(CASL-TRL)               | Hold time of TR/QE low after CAS no longer high                                            | 55  |         |     | ns        |

| 56  | t <sub>su</sub> (TRH-RASH) | Setup time of TR/QE high before RAS no longer low                                          | 15  |         |     | ns        |

| 57  | td(SCH-RDY)                | Delay from SYSCLK high to RDY/HOLD valid (hold mode)                                       |     |         | 80  | пѕ        |

| 58  | <sup>†</sup> h(SCH-HA)     | Hold time of valid HOLDACK after SYSCLK high, hold mode only (see Note 4)                  | 10  |         |     | ns        |

| 59  | t <sub>su(HA-SCH)</sub>    | Setup time of HOLDACK low or high before SYSCLK no longer low, hold mode only (see Note 4) | 20  |         |     | ns        |

| 60  | td(SCH-INT)                | Delay from SYSCLK high to INT low or high                                                  |     |         | 60  | ns        |

| 61  | t <sub>su(RMA)</sub>       | Row memory address setup before RAS no longer high                                         |     | 0       |     | ns        |

| 62  | t <sub>su(CMA)</sub>       | Column memory address setup before CAS no longer high                                      | 0   |         |     | ns        |

| 63  | t <sub>su(TR)</sub>        | TR/QE setup time before RAS no longer high, shift register transfer, display update        | 0   |         |     | ns        |

| 64  | th(RMA)                    | Row memory address hold time from RAS low                                                  | 20  |         |     | пѕ        |

| 65  | t <sub>su(HA-RSTH)</sub>   | Setup of HOLDACK prior to RESET going high, ready and wait modes only                      | 50  |         |     | ns        |

| 66  | th(RSTH-HA)                | Hold time of HOLDACK after RESET high, ready and wait modes only                           | 50  |         |     | ns        |

| 67  | th(SCH-FS)                 | Hold time of FS2-FS0 to SYSCLK high                                                        | 10  |         |     | ns        |

†Row address hold time guaranteed by th(RMA) parameter.

NOTES: 4. ALE, CEH, and CEL inputs are synchronous to SYSCLK and must meet the required setup and hold times specified with respect to each SYSCLK low-to-high transition in order to guarantee correct operation.

- 5. This timing is based on a load circuit equivalent to 64 SMJ4161 VRAMs being driven by the VSC. Each of the following outputs drives a 350-pF capacitance to VSS: MA8-MAO, CASLO, CASLO, CASLO, TR/QE. The W output drives a 670-pF capacitance to ground. All other outputs drive a 560-ohm resistor tied to a 2.2-volt source with a 100 pF capacitance load tied to VSS.

- 6. All references made to the RDY/HOLD signal in the timing spec assume an active high level.

FIGURE 2. STANDARD TEST LOAD CIRCUIT

# SM/SMJ34061 VIDEO SYSTEM CONTROLLER

## system clock timing

### reset timing

# function select (FS) timing

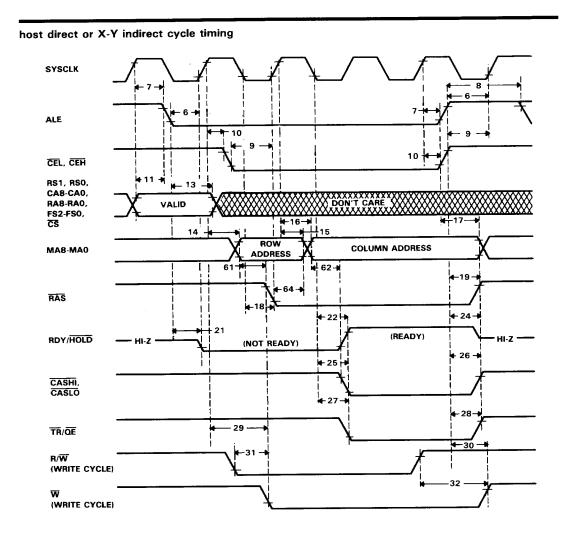

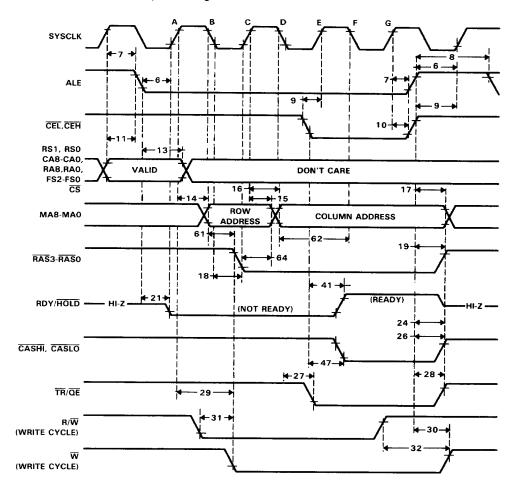

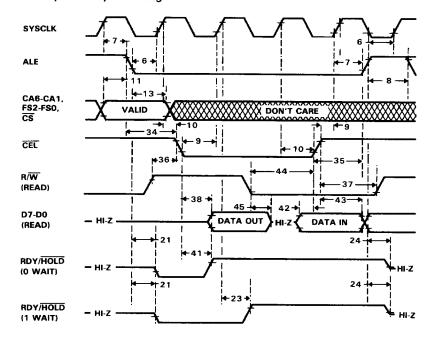

# host direct or X-Y indirect cycle timing with late CAS

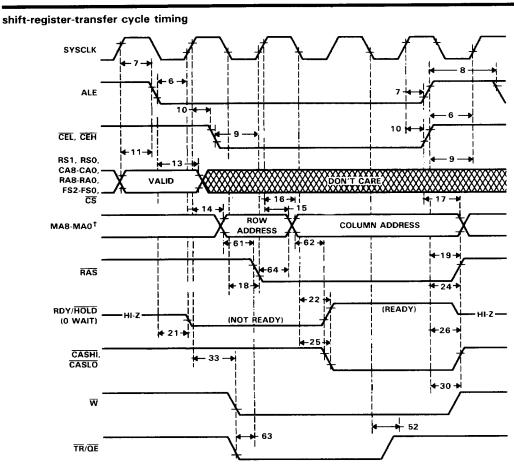

<sup>†</sup>During a shift-register cycle the nine bits of address input on CA8-CA0 are output on MA8-MA0 at row address time, and the nine bits of address input on RA8-RA0 are output on MA8-MA0 at column address time. This multiplexing of the row and column addresses is intended to reduce memory address map requirement.

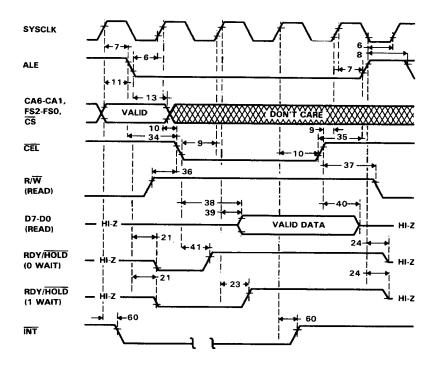

## register read cycle timing

### register write cycle timing SYSCLK ALE CA6-CA1, FS3-FS0, VALID cs CEL R/W 44 (WRITE) 43 42 -D7-D0 DON'T CARE VALID DATA (WRITE) RDY/HOLD – нь-г -HI-Z (O WAIT) 121 RDY/HOLD (READY) HI-Z -- HI-Z (NOT READY) (1 WAIT)

## register read-modify-write cycle timing

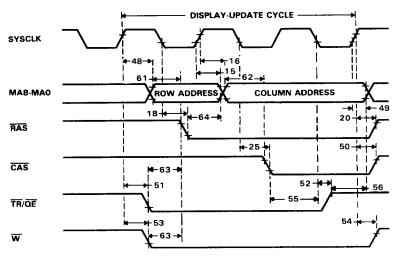

### display-update cycle timing

NOTE: The state of  $\overline{W}$  during update cycles is determined by B6 of control register 1.

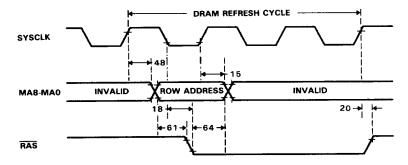

### DRAM-refresh cycle timing

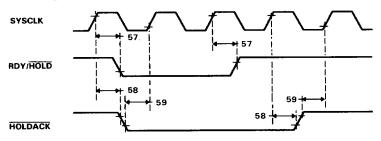

## hold/hold acknowledge timing

### video interface timing parameters

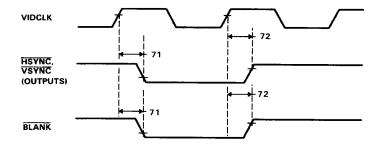

The timing parameters for VSC video interface signals are presented below. This interface includes the following VSC pins: VIDCLK (video input clock), BLANK (blanking), HSYNC (horizontal sync, bidirectional) and VSYNC (vertical sync, bidirectional). HSYNC and VSYNC are inputs only if external sync mode is enabled; if not, they are outputs.

## video interface signals timing parameters

| NO. |                         | PARAMETER                                                                    |     | SMJ34061 |    |

|-----|-------------------------|------------------------------------------------------------------------------|-----|----------|----|

|     | - CAUCHTE LEIT          | MIN                                                                          | MAX | UNIT     |    |

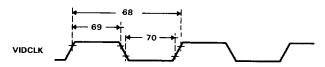

| 68  | tcVC                    | Period of input clock VIDCLK (see Note 7)                                    | 155 | 500      | ns |

| 69  | tw(VCH)                 | Pulse duration of VIDCLK high                                                | 73  | 246      | ns |

| 70  | tw(VCL)                 | Pulse duration of VIDCLK low                                                 | 73  | 246      | ns |

| 71  | td(VCH-VL)              | Delay from VIDCLK high to sync low or blanking output low                    | 15  | 80       | ns |

| 72  | td(VCH-VH)              | Delay from VIDCLK high to sync or blanking output high                       | 15  | 80       | ns |

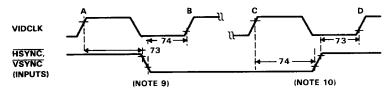

| 73  | t <sub>su(XS-VCH)</sub> | Setup time of external sync low or high to VIDCLK no longer low (see Note 8) | 20  |          | ns |

| 74  | th(VCH-XS)              | Hold time of external sync low or high after VIDCLK high (see Note 8)        | 20  |          | ns |

NOTES: 7. If HTOTAL - HSBLANK is equal to 1, then the VIDCLK frequency must be less than 4 MHz. If HTOTAL - HSBLANK is equal to or greater than 2, then the VIDCLK frequency can operate up to a maximum of 6.5 MHz.

8. Specified setup and hold times on asynchronous inputs are required only to guarantee recognition at indicated clock edge.

### video clock input timing

### output signal timing

### external sync input timing

NOTES: 9. If the falling edge of the sync signal occurs more than 10 ns past VIDCLK edge A, and at least 20 ns before edge B, the transition will be detected at edge B rather than at edge A.

10. If the rising edge of the sync signal occurs more than 10 ns past VIDCLK edge C, and at least 20 ns before edge D, the transition will be detected at edge D rather than at edge C.