# TMS370Cx10 8-BIT MICROCONTROLLERS

T-49-19-01

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

# CMOS/EEPROM/EPROM Technologies on a Single Device

- Form Factor Emulator (FFE) Devices for Prototyping Purposes

- One-Time Programmable (OTP) Devices for Low Volume Production

- Mask ROM Devices for High Volume Production

### Flexible Operating Features

- --- Power Reduction STANDBY and HALT Modes

- -- Commercial and Industrial Temperature Range

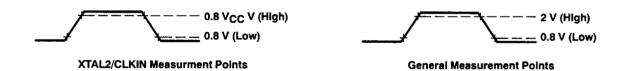

- Input Clock Frequency 2 MHz to 20 MHz

- Voltage ( $V_{CC}$ ) 5 V ± 10%

### Internal System Memory Configurations

- 4K-Byte On-Chip Program Memory

- Mask ROM (TMS370C010 and TMS370C310) or

- EPROM (TMS370C710 and TMS370C610)

- Data EEPROM, 256 Bytes (TMS370C010 and TMS370C710)

- Static RAM, 128 Bytes Usable as Registers

### 16-Bit General Purpose Timer

- Software Configurable for a 16-Bit Event Counter, or a 16-Bit Pulse Accumulator, or a 16-Bit Input Capture Function, or Two Compare Registers, or a Self-Contained PWM Output Function

- Software Programmable Input Polarity

- 8-Bit Prescaler, Providing a 24-Bit Realtime Timer

- On-Chip 24-Bit Watchdog Timer

- Serial Peripheral Interface (SPI)

- Variable-Length High-Speed Shift Register

- Synchronous Master/Slave Operation

### Flexible Interrupt Handling

- Two S/W Programmable Interrupt Levels

- Global and Individual Interrupt Masking

- --- Programmable Rising or Falling Edge

Detect

### 22 CMOS/TTL Compatible I/O Pins

- All Peripheral Function Pins Software Configurable for Digital I/O

- 21 Bidirectional Pins, 1 Input Pin

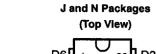

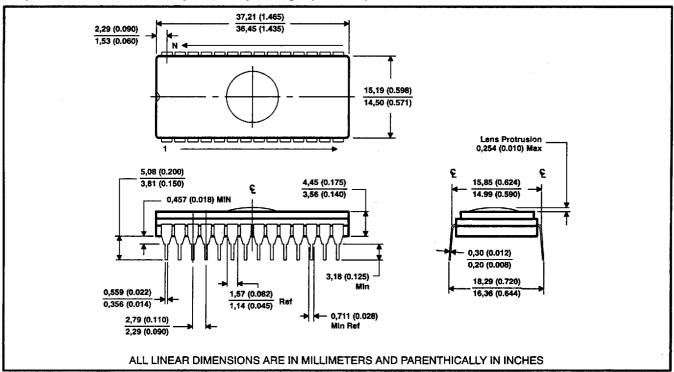

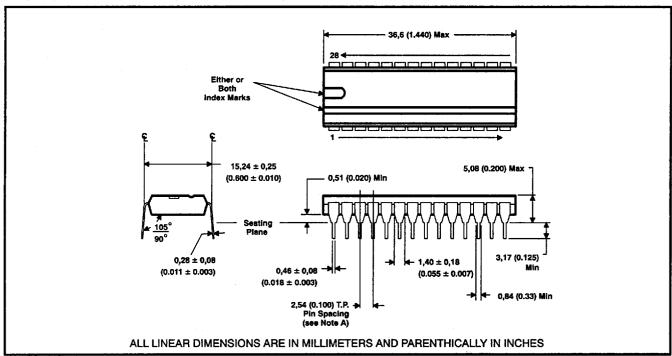

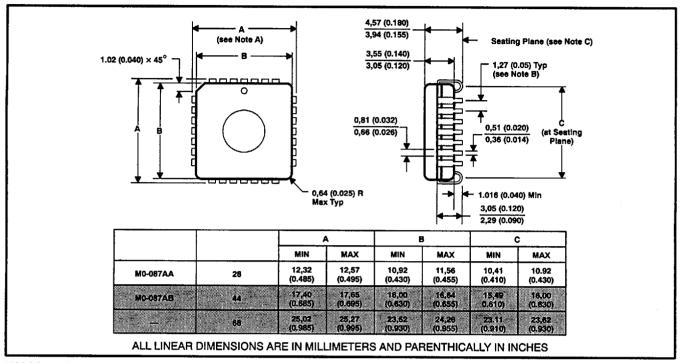

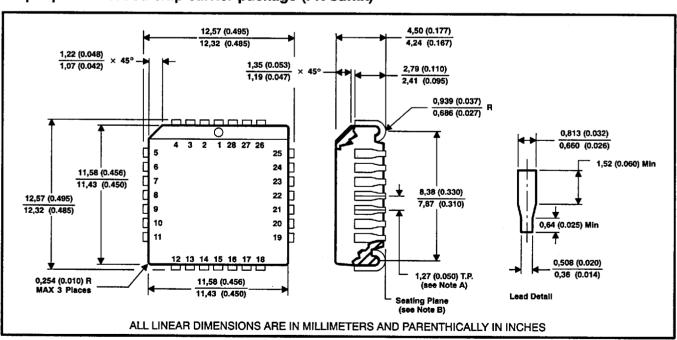

### FZ and FN Packages (Top View)

### 28-Pin Packages

- --- Plastic DIP ROM or OTP (N Suffix)

- Ceramic DIP FFE (J Suffix)

- Plastic PLCC ROM or OTP (FN Suffix)

- --- Ceramic CLCC FFE (FZ Suffix)

# TMS370 Series Compatibility

- Register-to-Register Architecture

- 128 General-Purpose Registers

- 14 Powerful Addressing Modes

# PC-Based Workstation Development Support Emphasizes Productivity, Featuring:

- Realtime In-Circuit Emulation

- Symbolic Debug

- Extensive Breakpoint/Trace Capability

- C-Compiler Support

- Multi-Window User Interface

- EEPROM/EPROM Programming

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Texas instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1990, Texas Instruments Incorporated

1

SPNS012B -- MAY 1987 -- REVISED DECEMBER 1990

### description

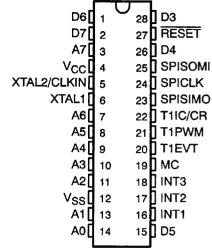

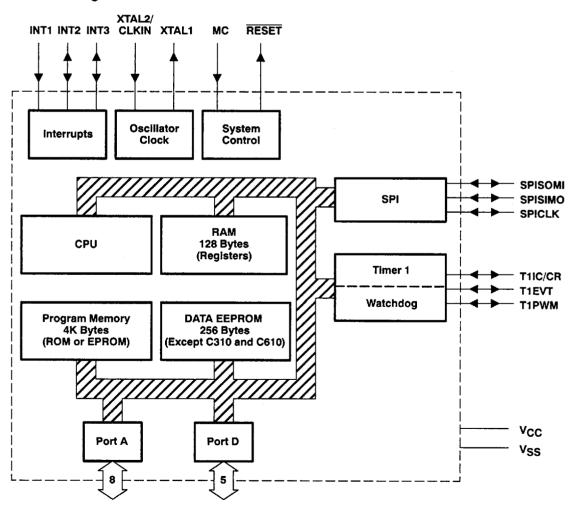

The TMS370C010, TMS370C310, TMS370C610, and TMS370C710 devices are members of the TMS370 family of single-chip 8-bit microcontrollers. The TMS370 family provides cost-effective realtime system control through VLSI integration of advanced on-chip memory and peripheral function modules.

The TMS370 family is implemented using high-performance silicon-gate CMOS technology. The low operating power, wide operating temperature range, and high noise immunity of CMOS technology coupled with the high performance and extensive on-chip peripheral functions make the TMS370Cx10 devices attractive in system designs for automotive electronics, industrial control, computer peripheral control, and telecommunications.

Unless otherwise noted, the term TMS370Cx10 refers to the TMS370C010, TMS370C310, TMS370C10, and the TMS370C710 for all peripheral function modules available on those devices. All TMS370Cx10 devices contain the following modules:

- 4 K bytes Program memory.

- 128 bytes Ram (usable as registers).

- Serial Peripheral Interface (SPI).

- Timer1-16-bit general-purpose timer with Watchdog

The following table provides a memory configuration overview of the TMS370Cx10 devices.

| DEVICE                 | PROGRAM MEMORY | DATA EEPROM | PACKAGE   |

|------------------------|----------------|-------------|-----------|

| TMS370C010             | AK Pideo BOM   | OSC Duton   | N – DIP   |

| TMIS370C010            | 4K Bytes ROM   | 256 Bytes   | FN - PLCC |

| TMS370C310             | AV Bridge BOM  | None        | N – DIP   |

| TM5370C310             | 4K Bytes ROM   | None        | FN - PLCC |

| TMS370C610             | AV Pidos EDDOM | None        | N – DIP   |

| IM5370C610             | 4K Bytes EPROM | None        | FN - PLCC |

| TMS370C710             | 4K Bytes EPROM | 256 Putos   | N – DIP   |

| 11VISS/UC/10           | 4K Byles EPROM | 256 Bytes   | FN - PLCC |

| SE370C710 <sup>†</sup> | AV Pitos EDDOM | OFE Putos   | J – CDIP  |

| 3E3/00/101             | 4K Bytes EPROM | 256 Bytes   | FZ - CLCC |

<sup>†</sup> System evaluators and development tools are for use only in a prototype environment and their reliability has not been characterized.

The 4K bytes of mask-programmable ROM in the TMS370C010 and TMS370C310 are replaced in the TMS370C710 and TMS370C610 with 4K bytes of EPROM while all other available memory and on-chip peripherals are identical, with the exception of no Data EEPROM on the TMS370C310 and TMS370C610 devices. The TMS370C610 and TMS370C710 OTP devices allow customers to change code without reordering a MASK ROM device. The OTP devices reduce manufacturing design times for new code and are excellent low volume production alternatives.

The windowed ceramic FFE devices, SE370C710 FZ, J, offer reprogramming capabilities for prototyping requirements.

The TMS370Cx10 provides two power reduction modes (STANDBY and HALT) for applications where low power consumption is critical. Both modes stop all CPU activity (i.e., no instructions are executed). In the STANDBY mode the internal oscillator and the general purpose timer remain active. In the HALT mode, all device activity is stopped. The device retains all RAM data and peripheral configuration bits throughout both powerdown modes.

The TMS370Cx10 features advanced register-to-register architecture that allows direct arithmetic and logical operations without requiring an accumulator (e.g., ADD R24, R47; add the contents of register 24 to the contents of register 47 and store the result in register 47). The TMS370Cx10 instruction set is fully compatible with other TMS370 family members, allowing easy transition between members.

# TMS370Cx10 8-BIT MICROCONTROLLERS

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

The SPI gives a convenient method of serial interaction for high speed communications between simpler shift register type devices, such as display drivers, A/D converters, PLL, I/O expansion, or other microcontrollers in the system.  $T_{-449-19-01}$

The TMS370 family provides the system designer with an economical, efficient solution to realtime control applications. The TMS370 family eXtended Development System (XDS) solves the challenge of efficiently developing the software and hardware required to design the TMS370 into an ever-increasing number of complex applications. The application source code modules can be written in Assembly and/or C language and the output code can be generated by the linker. The TMS370 family XDS communicates via a standard RS-232-C interface with an existing personal computer to form a PC-DOS hosted workstation, using the PC's editors and software utilities already familiar to the designer. The TMS370 family XDS emphasizes ease-of-use through extensive use of menus and screen windowing so that a system designer can begin developing software with minimum training. Precise realtime in-circuit emulation and extensive symbolic debug and analysis tools ensure efficient software and hardware implementation as well as reduced time-to-market.

The TMS370Cx10 mask ROM devices, the TMS370x10 OTP devices, together with the TMS370 family XDS for applications development, the SE370C710 EPROM devices, and comprehensive product documentation and customer support provide a complete solution to the low end needs of the systems designer. Other TMS370 family members are available with additional memory, I/O and peripheral functions such as SCI and A/D to meet more complex system requirements.

# functional block diagram

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

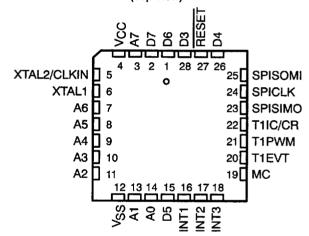

# pin descriptions

| PIN                                          |                                          |                                        |                                                                                                                                                                                                                                                |

|----------------------------------------------|------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                         | NO.                                      | 1/0                                    | DESCRIPTION                                                                                                                                                                                                                                    |

| A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7 | 14<br>13<br>11<br>10<br>9<br>8<br>7<br>3 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Port A is a general purpose bidirectional port.                                                                                                                                                                                                |

| D3<br>D4<br>D5<br>D6<br>D7                   | 28<br>26<br>15<br>1<br>2                 | I/O<br>I/O<br>I/O<br>I/O               | General purpose bidirectional pin. Also configurable as CLKOUT. General purpose bidirectional pin. |

| INT1<br>INT2<br>INT3                         | 16<br>17<br>18                           | 1<br>1/0<br>1/0                        | External interrupt non-maskable or maskable interrupt / general purpose input pin. External maskable interrupt input/general purpose bidirectional pin. External maskable interrupt input/general purpose bidirectional pin.                   |

| T1IC/CR<br>T1PWM<br>T1EVT                    | 22<br>21<br>20                           | 1/O<br>1/O<br>1/O                      | Timer 1 Input Capture/Counter Reset input pin/general purpose bidirectional pin. Timer 1 PWM output pin/general purpose bidirectional pin. Timer 1 External Event input pin/general purpose bidirectional pin.                                 |

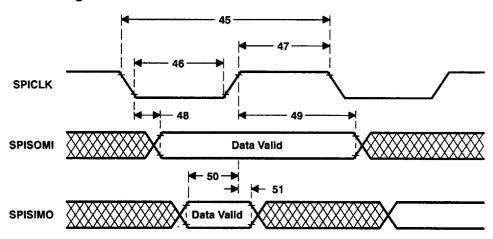

| SPISOMI<br>SPISIMO<br>SPICLK                 | 25<br>23<br>24                           | 1/0<br>1/0<br>1/0                      | SPI Slave Output pin, Master Input pin/general purpose bidirectional pin. SPI Slave Input pin, Master Output pin/general purpose bidirectional pin. SPI bidirectional Serial Clock pin/general purpose bidirectional pin.                      |

| RESET                                        | 27                                       | 1/0                                    | System reset bidirectional pin. As an input, it initializes microcontroller. As open-drain output it indicates an internal failure was detected by the Watchdog or Oscillator Fault circuit.                                                   |

| мс                                           | 19                                       | ı                                      | Mode control input pin; enables EEPROM Write Protection Override (WPO) mode.  Normal operation = 0 V, WPO = 12 V. Vpp supply for EPROM programming.                                                                                            |

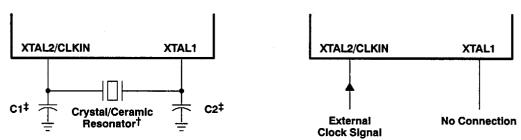

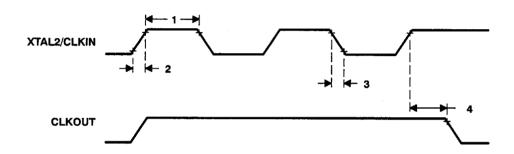

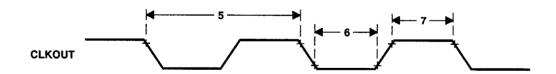

| XTAL2/ CLKIN                                 | 5                                        | ı                                      | Internal oscillator crystal input/external clock source input.                                                                                                                                                                                 |

| XTAL1                                        | 6                                        | 0                                      | Internal oscillator output for crystal.                                                                                                                                                                                                        |

| Vcc                                          | 4                                        |                                        | Positive supply voltage.                                                                                                                                                                                                                       |

| VSS                                          | 12                                       |                                        | Ground reference.                                                                                                                                                                                                                              |

NOTE 1: Each pin associated with Interrupt 2, Interrupt 3, Timer 1, and SPI functional blocks may be individually programmed as a general purpose bidirectional pin if it is not used for its primary block function.

SPNS012B - MAY 1987 - REVISED DECEMBER 1990

### memory map

T=49-19-01

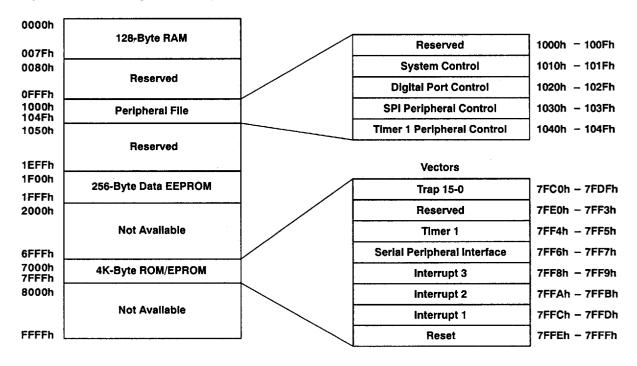

The TMS370 family architecture is based on the Von Neumann architecture, where the program memory and data memory share a common address space. All peripheral input/output is memory mapped in this same common address space. As shown in Figure 1, the TMS370 provides memory-mapped RAM, ROM, EEPROM, EPROM, input/output pins, and peripheral functions.

The peripheral file contains all input/output port control, peripheral status and control, EEPROM memory programming, and system-wide control functions. The peripheral file is located from 1010h to 104Fh and is logically divided into 5 Peripheral File Frames of 16 bytes each. Each on-chip peripheral is assigned to a separate frame through which peripheral control and data information is passed. The TMS370Cx10 has its peripherals and system control assigned to Peripheral File Frames 1 through 4, addresses 1010h through 104Fh.

Figure 1. TMS370Cx10 Memory Map

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

#### memories

### RAM/register file

The TMS370Cx10 has 128 bytes of static RAM, which serve as both the CPU register file and general-purpose memory. The RAM is treated as registers by the instruction set and is referenced as R0 through R127. The first two registers, R0 and R1, are also called the A and B registers, respectively. The stack is located in the RAM, and operates as a last-in first-out read/write memory. It is used to store the return address on subroutine calls and the status register during interrupts. Accessing this memory as registers is performed in one system clock cycle (t<sub>C</sub>), while general-purpose memory access is performed in two system clock cycles.

#### data EEPROM

The TMS370C010 and TMS370C710 have 256 bytes of on-chip Electrically Erasable Programmable ROM (EEPROM), addressed as 256 consecutive bytes mapped from locations 1F00h to 1FFFh. The Data EEPROM provides nonvolatile programmable storage for items such as calibration constants and configuration information for personalization of a generic algorithm for use in specific end applications. The Data EEPROM supports bit, byte, and block write/erase modes. Instructions may be executed from Data EEPROM, providing additional program space and the ability to patch algorithms by placing a branch table for volatile routines in Data EEPROM.

The Data EEPROM uses the 5-V  $V_{CC}$  supply voltage and provides the programming voltage via an internal dedicated generator, eliminating the need for an external high-voltage programming source. The dedicated voltage generator optimizes the programming voltage characteristics, increasing the reliability as well as extending the write/erase endurance of the array.

Programming control and status monitoring are performed through the Data EEPROM control register (DEECTL) in the peripheral file. An EEPROM write/erase operation is performed in the following sequence:

- 1. Perform normal memory write to the target EEPROM location.

- 2. Write to DEECTL control register to select WRITE1/WRITE0 and set the EXECUTE (EXE) bit to 1.

- 3. Wait for program time to elapse  $[t_{w(PGM)B} \text{ or } t_{w(PGM)AR}]$ .

- 4. Write to DEECTL control register to set the EXECUTE (EXE) bit to 0.

The WRITE1/WRITE0 control bit selects whether the zeros or the ones in the data byte are to be programmed into the selected EEPROM location. For example, a WRITE1 operation will program ones into all bit positions within the EEPROM byte that have ones in the data byte, while bits that are zero in the data byte will not affect the EEPROM contents. The WRITE1 operation effectively performs a logical OR of the information previously stored on the EEPROM byte with the data byte. The WRITE0 operation effectively performs a logical AND between these two bytes. Single bit programming within an EEPROM byte is performed by writing only the zeros or ones of the data byte. The EEPROM programming algorithm may use this bit-programming capability to optimize the life of the EEPROM.

When a data value cannot be achieved by writing only zeros or only ones into the EEPROM byte, a WRITE1 followed by a WRITE0 will program any data value into the EEPROM byte, regardless of the previous data stored at that location.

All unprotected bytes within the Data EEPROM array may be programmed during a single EEPROM programming cycle by setting the ARRAY PROG bit of DEECTL to 1 at the start of the programming cycle.

Data EEPROM read accesses are performed as normal memory read operations in two system clock cycles. A memory read cycle to any EEPROM location while EXE = 1 returns the value currently being written to the EEPROM. Following an EEPROM write operation, the EEPROM voltages must stabilize prior to performing an EEPROM read operation. The BUSY FLAG indicates the status of the EEPROM voltage. When set, the EEPROM is not ready for a read operation. The BUSY flag is reset to 0 by the EEPROM control logic when 128

SPNS012B -- MAY 1987 -- REVISED DECEMBER

system clock cycles have elapsed following the EXE bit being set to 0. If an EEPROM read operation is performed while BUSY = 1, automatic WAIT states will be generated until BUSY = 0, and then the read operation will be performed.

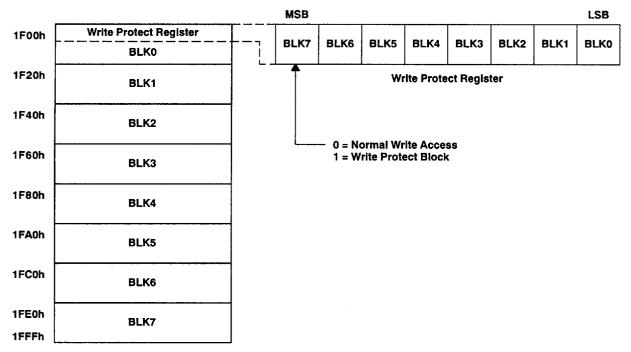

Bytes within the Data EEPROM may be protected from inadvertent overwriting of critical information. As shown in Figure 2, the 8-bit Write Protect Register (WPR), located at 1F00h within the data EEPROM, provides write protection for the 256-byte Data EEPROM, segmenting the array into eight blocks of 32 bytes each. Each of these 32-byte blocks may be individually write- and erase-protected by setting the corresponding bit to 1 in the WPR. Since the WPR resides in the array in BLK0, the WPR may also be write-protected, thereby increasing the system reliability by preventing bytes from being reprogrammed. Bytes left unprotected may be written to by the normal EEPROM programming sequence. The Write Protection Override (WPO) mode overrides the write protection of all blocks in the Data EEPROM, and enables data to be written to any location in the Data EEPROM, regardless of the WPR contents. Enter the WPO mode by placing 12-V on the MC pin. The WPO mode is typically used in a service environment to update the protected EEPROM contents. The 12-V input level on the MC pin to enter the WPO mode is not normally present in an application except in a service environment; therefore, the data integrity of the program is ensured during normal operation.

Figure 2. Write Protect Register

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

### program ROM

The Program ROM consists of 4K bytes of mask programmable read-only memory. The Program ROM is used for permanent storage of data and instructions, with read operations performed in two system clock cycles. Memory addresses 7FF4h through 7FFFh are reserved for interrupt and reset vectors. Trap vectors, used with TRAP0 through TRAP15 instructions, are located between addresses 7FC0h and 7FDFh. Programming of the mask ROM is performed at the time of device fabrication.

### program EPROM

The Program EPROM of the TMS370C610 and TMS370C710 is a 4K ultraviolet-light-erasable, electrically programmable read-only memory, addressed as 4K consecutive bytes mapped form location 7000h to 7FFFh. It provides application performance identical to the TMS370Cx10 mask ROM devices with up to 4K bytes. Program instructions are read from the Program EPROM in two system clock cycles, providing the prototyping capability of the Mask Program ROM.

An external supply  $(V_{PP})$  is needed at the MC pin to provide the necessary voltage  $(V_{PP})$  for programming. Programming is controlled through the EPCTL register (P01C) in the peripheral file.

Before programming, the SE370C710's EPROM must be erased by exposing the device through the transparent window to high-intensity ultraviolet light (wavelength 2537Å). The recommended minimum exposure dose (UV intensity × exposure time) is 15- W•s/cm². A typical 12-mW/cm², filterless UV lamp will erase the device in 21 minutes. The lamp should be located about 2.5 cm above the chip during erasure. After erasure, the entire array is in a logic high state. A programmed low can be erased only by exposure to ultraviolet light. It should be noted that normal ambient light contains the correct wavelength for erasure. Therefore, when using the SE370C710, the window should be covered with an opaque label. All devices are erased to logical high when delivered from the factory.

### **CAUTION**

Exposing the EPROM module to ultraviolet light may also cause erasure in any EEPROM module. Any useful data stored in the EEPROM must be reprogrammed after exposure to UV light.

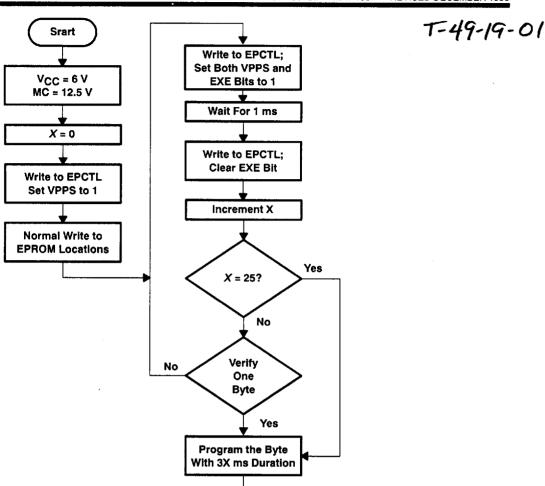

Programming lows into the EPROM is controlled by the EPCTL register via the EXE bit and the VPPS bit. The EXE bit initiates EPROM programming when set and disables programming when cleared. The VPPS bit connects the programming voltage VPP at the MC pin to the EPROM module. VPPS (EPCTL.6) and EXE (EPCTL.0) should be set separately, and the VPPS bit should be set at least two microseconds before the EXE bit is set. After programming, the application programming should wait for four microseconds before any read attempt is made. The programming operation (see Figure 3) is performed in the following recommended sequence:

- 1. Supply the programming voltage to the MC pin.

- 2. Write to EPCTL register to set the VPPS bit to 1 (high).

- 3. Perform normal memory write register to the target EPROM location.

- 4. Write to EPCTL register to set the EXE bit register to 1 (high). (Wait at least two microseconds after step 2.

- 5. Wait for program time to elapse (one millisecond).

- 6. Write to EPCTL register to clear the EXE bit (leave VPPS bit set to 1 ( high)).

- 7. Read the byte being programmed; if correct data is not read, repeat steps 4 through 6 up to a maximum X of 25.

- 8. Write to EPCTL register to set the EXE bit to 1 (high) for Final programming.

- 9. Wait for program time to elapse (3X milliseconds duration).

- 10. Write to EPCTL register to clear the EXE and VPPS bits.

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

Clear Both EXE and VPPS

Figure 3. EPROM Programming Operation

An external power supply at V<sub>PP</sub>, I<sub>PP</sub> (30 mA), is required for programming operation. Programming voltage V<sub>PP</sub> is supplied via the MC pin. This also automatically puts the microcontroller in the Write Protection Override (WPO) mode. Programming voltage may be applied via the MC pin anytime after reset and remain at V<sub>PP</sub> after programming (after the EXE bit is cleared). Applying programming voltage while RESET is active will put the microcontroller in a reserved mode, where programming operation is inhibited.

#### write protect of program EPROM

To override the EPROM write protection, the  $V_{PP}$  voltage must be applied to the MC pin and the VPPS bit (EPCTL.6) must be set. This dual requirement ensures that the program EPROM will not accidentally be overwritten during the Data EEPROM operations when  $V_{PP}$  is applied to the MC pin. The Data EEPROM may be programmed when the VPPS bit is set.

1MS370CX10 8-BIT MICROCONTROLLERS

T-49-19-01

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

# central processing unit

The central processing unit (CPU) of the TMS370 series is an enhanced version of the TMS7000 Family CPU. The enhancements include additional user instructions such as integer divide, conditional jump instructions based on the overflow status bit, and addressing modes such as stack-pointer-relative addressing for subroutine parameter passing. The efficient register-to-register architecture of the TMS7000 family has been carried over to the TMS370 family, which avoids the conventional accumulator bottleneck. The complete TMS370 family instruction set is summarized in the TI TMS370 INSTRUCTION SET SUMMARY beginning on page 28.

In addition to the interpretation and execution of the user program, the CPU performs the functions of bus protocol generation and interrupt priority arbitration. While the CPU is implemented independent of the memory, input/output, and peripheral modules, it performs the central system control function through communications with these on-chip modules.

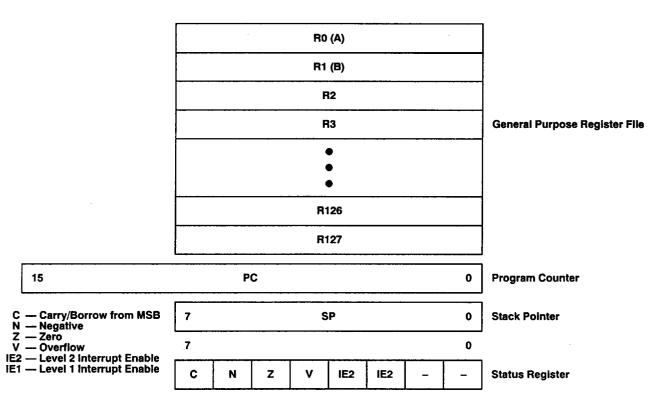

The TMS370 family CPU registers accessible to the programmer are shown in Figure 4. The register file consists of 128 general purpose registers, R0 through R127 implemented in on-chip RAM, and is used by the CPU for general purpose 8- and 16-bit source and destination operands, index registers, and indirect addressing. The first two registers, R0 and R1, are also called registers A and B and are used by the CPU as general purpose registers or for implied operands. The program counter (PC) contains the address of the next instruction to be executed. The stack pointer (SP) contains the address of the last or top entry on the stack, which is located in the on-chip RAM. The status register (ST) contains four bits that reflect the outcome of the instruction just executed, and two bits that control the masking of the interrupt priority chains.

Figure 4. CPU Registers

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

### system resets

T-49-19-01

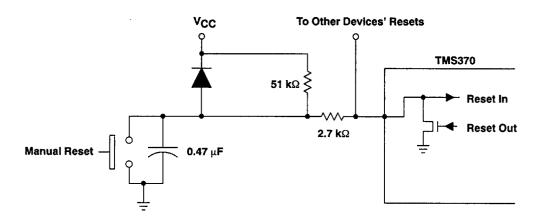

The TMS370Cx10 has three possible reset sources: a low input to the  $\overline{RESET}$  pin, a programmable watchdog timer timeout, or a programmable oscillator fault failure. The  $\overline{RESET}$  pin, an input/output pin, initiates TMS370Cx10 hardware initialization and ensures an orderly software startup. A minimum 50-ns low level input initiates the reset sequence. The microcontroller is held in reset until the  $\overline{RESET}$  pin goes inactive (high). If the  $\overline{RESET}$  input signal is low for less than eight system clock cycles, the TMS370Cx10 will hold the external  $\overline{RESET}$  pin low for eight system clock cycles to reset external system components. The  $\overline{RESET}$  should be released only after stable oscillation and valid  $V_{CC}$ . The  $\overline{RESET}$  pin must be activated by the application at power-up, which can be accomplished by an external input or an RC power-up reset circuit. In addition, the application must activate  $\overline{RESET}$  when  $V_{CC}$  goes out of spec to prevent corruption of data and erroneous operation. The  $\overline{RESET}$  pin can be asserted at any time during operation, resulting in an immediate initiation of the reset sequence.

Figure 5. Typical Reset Circuit

The watchdog timer provides system integrity by detecting a program that has become lost or is not executing as expected. A system reset is generated if the watchdog timer is not properly re-initialized by a specific software sequence, or if the re-initialization does not occur before the watchdog timer times out. The watchdog timer timeout initiates the TMS370Cx10 reset sequence and drives the external RESET pin low for eight system clock cycles to reset external system components. The Watchdog reset function is enabled by setting WD OVRFL RST ENA bit of T1CTL2 to 1. Once the software enables the watchdog reset function, subsequent writes to the WD OVRFL RST ENA bit are ignored. Watchdog control bits can be initialized only following a power-up reset. The timer section discusses additional information on the watchdog timer and its configurations.

The oscillator fault circuit provides the means to monitor failures of the oscillator input signal (XTAL2/CLKIN). If the oscillator input signal frequency remains above the 90% point of the minimum operating frequency (CLKIN), the oscillator input will not to be activated. However, if the oscillator input is lost or its frequency falls below 20 kHz and the oscillator fault reset has not been disabled, the TMS370Cx10 is reset and the external RESET pin is driven low.

When an oscillator input failure occurs, the internal clocks are stopped and RESET is held active until the oscillator input frequency is greater than 100 kHz typical. The reset action can be disabled by clearing the OSC FLT RST ENA bit (P012.5). Oscillator fault detection can be disabled by setting the OSC FLT DISABLE bit (P012.2). Since operation is unpredictable with slow or intermittent clocks, neither of these actions is recommended. During the HALT mode the oscillator fault circuitry is disabled.

Reset puts the address at 7FFEh and 7FFFh (Isb) into the PC and then clears Registers A and B and the status register. The Stack Pointer is set to 01h during reset. A reset when the device is already running will not affect the other RAM registers.

SPNS012B -- MAY 1987 -- REVISED DECEMBER 1990

# **Control Bit States Following Reset**

| REGISTER | CONTROL BIT   | POWER-UP | WARM RESET |

|----------|---------------|----------|------------|

| SCCR0    | μΡ/μC MODE    | 0        | 0          |

| SCCR0    | MC PIN DATA   | 0        | 0          |

| SCCR0    | COLD START    | 1        | t          |

| SCCR0    | OSC FLT FLAG  | 0        | į.         |

| T1CTL2   | WD OVRFL FLAG | Ö        | i i        |

<sup>†</sup> Status bit corresponding to active reset source is set to 1.

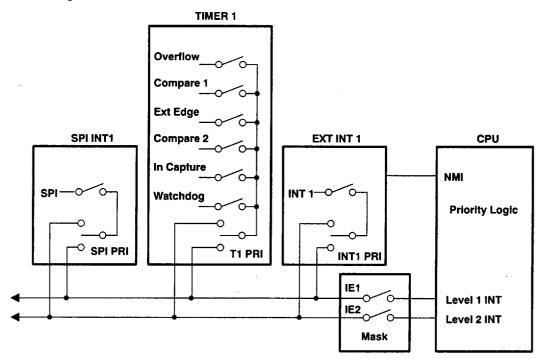

### interrupts

The TMS370 family software-programmable interrupt structure supports flexible on-chip and external interrupt configurations to meet realtime interrupt-driven application requirements. The hardware interrupt structure incorporates two priority levels as shown in Figure 5. Interrupt level 1 has a higher priority than interrupt level 2. The two priority levels can be independently enabled by the global interrupt enable bits (IE1 and IE2) of the Status Register.

Figure 6. Interrupt Control

Each system interrupt is independently configured on either the high or low priority chain by the application program during system initialization. Within each interrupt chain, the interrupt priority is fixed by the position of the system interrupt. However, since each system interrupt is selectively configured on either the high or low priority interrupt chain, the application program can elevate any system interrupt to the highest priority. Arbitration between the two priority levels is performed within the CPU. Arbitration within each of the priority chains is performed within the peripheral modules. Pending interrupts are serviced upon completion of current instruction execution, depending on their interrupt mask and priority conditions.

The TMS370Cx10 has six hardware system interrupts as shown in the following table. Each system interrupt has a dedicated interrupt vector located in program memory through which control is passed to the interrupt service routines. A system interrupt may have multiple interrupt sources. All of the interrupt sources are

TMS370Cx10 8-BIT MICROCONTROLLERS

T-49-19-01

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

individually maskable by local interrupt enable control bits in the associated peripheral file. Each interrupt source FLAG bit is individually readable for software polling or to determine which interrupt source generated the associated system interrupt.

Two of the system interrupts are generated by on-chip peripheral functions, and three external interrupts are supported. Software configuration of the external interrupts is performed through the INT1, INT2, and INT3 control registers in peripheral file frame 1. Each external interrupt is individually software configurable for input polarity (rising or falling) for ease of system interface. External interrupt INT1 is software configurable as either a maskable or non-maskable interrupt. When INT1 is configured as non-maskable, it cannot be masked by the individual or global mask bits. Recall that the INT1 NMI bit is protected during nonprivileged operation and therefore should be configured during the initialization sequence following reset. To maximize pin flexibility, external interrupts INT2 and INT3 can be software configured as general purpose input/output pins if the interrupt function is not required (INT1 can be similarly configured as an input pin).

### **Hardware System Interrupts**

| INTERRUPT SOURCE                                                                                                   | INTERRUPT FLAG                                                                                | SYSTEM<br>INTERRUPT | VECTOR<br>INTERRUPT | PRIORITYS |  |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------|---------------------|-----------|--|

| External Reset<br>Watchdog Overflow<br>Oscillator Fault Detect                                                     | COLD START<br>WD OVRFL INT FLAG<br>OSC FLT FLAG                                               | RESET†              | 7FFEh, 7FFFh        | 1         |  |

| External INT1                                                                                                      | INT1 FLAG                                                                                     | INT1 <sup>†</sup>   | 7FFCh, 7FFDh        | 2         |  |

| External INT2                                                                                                      | INT2 FLAG                                                                                     | INT2†               | 7FFAh, 7FFBh        | 3         |  |

| External INT3                                                                                                      | INT3 FLAG                                                                                     | INT3†               | 7FF8h, 7FF9h        | 4         |  |

| SPI RX/TX Complete                                                                                                 | SPI INT FLAG                                                                                  | SPIINT              | 7FF6h, 7FF7h        | 5         |  |

| Timer 1 Overlfow Timer 1 Compare 1 Timer 1 Compare 2 Timer 1 External Edge Timer 1 Input Capture Watchdog Overflow | T1 OVRFL INT FLAG T1C1 INT FLAG T1C2 INT FLAG T1EDGE INT FLAG T1IC INT FLAG WD OVRFL INT FLAG | T1INT <sup>‡</sup>  | 7FF4h, 7FF5h        | 6         |  |

<sup>†</sup> Releases microcontroller from STANDBY and HALT low power modes.

<sup>‡</sup> Releases microcontroller from STANDBY low power mode.

<sup>§</sup> Relative priority within an interrupt level.

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

8-BIT MICROCONTROLLERS

# privileged operation and EEPROM write protection override

The TMS370Cx10 family is designed with significant flexibility to enable the designer to software-configure the system and peripherals to meet the requirements of a broad variety of applications. The non-privileged mode of operation ensures the integrity of the system configuration once defined for an end application. Following a hardware reset, the TMS370Cx10 operates in the privileged mode, where all peripheral file registers have unrestricted read/write access and the application program will configure the system during the initialization sequence following reset. As the last step of system initialization, the PRIVILEGED MODE bit of SCCR3 will be set to 1, entering the non-privileged mode and disabling write operations to specific configuration control bits within the peripheral file. The following system configuration bits are write-protected during the non-privileged mode and must be configured by software prior to exiting the privileged mode:

| REGI                                                        | STER <sup>†</sup>                                                  | CONTROL BIT                                                                                 |

|-------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| NAME                                                        | LOCATION                                                           | CONTROLBIT                                                                                  |

| SCCR0<br>SCCR2<br>SCCR2<br>SCCR2<br>SCCR2<br>SCCR2<br>SCCR2 | P010.6<br>P012.0<br>P012.6<br>P012.7<br>P012.1<br>P012.2<br>P012.5 | OSC POWER PRIVILEGED MODE PWRDWN/IDLE HALT/STANDBY INT1 NMI OSC FLT DISABLE OSC FLT RST ENA |

| SPIPRI<br>T1PRI                                             | P03F.6<br>P04F.6                                                   | SPI PRIORITY<br>T1 PRIORITY                                                                 |

<sup>†</sup> Identified by name and bit location within the register

The privileged bits are shown in a **bold typeface** in the following Peripheral File Frame sections.

The EPROM can only be written to when  $V_{PP}$  is applied to the MC pin and the VPPS (EPCTL.6) bit is set. When  $V_{PP}$  is applied to the MC pin all on-chip EEPROM is in the Write Protect Override (WPO) mode regardless of the state of the VPPS bit. This allows the EPROM to be protected while the EEPROM is in WPO.

#### low-power operating modes

The STANDBY and HALT low-power modes significantly reduce power consumption by reducing or stopping the activity of the various on-chip peripherals when processing is not required. Each of the low-power modes is entered by executing the IDLE instruction when the POWERDOWN/IDLE bit in SCCR2 has been set to 1. The HALT/STANDBY bit in SCCR2 controls which low-power mode is entered.

In the STANDBY mode (HALT/STANDBY=0), all CPU activity and most peripheral module activity is stopped; however, the oscillator, internal clocks, and Timer 1 remain active. System processing is suspended until a qualified interrupt (hardware RESET, external interrupt on INT1, INT2, or INT3, or a Timer 1 interrupt) is detected.

In the HALT mode (HALT/STANDBY=1), the TMS370x10 is placed in its lowest power consumption mode. The oscillator and internal clocks are stopped, causing all internal activity to be halted. System activity is suspended until a qualified interrupt (hardware RESET or external interrupt on INT1, INT2, or INT3) is detected. The powerdown mode selection bits are summarized in the following table:

| POWERDOWN                | CONTROL BITS              |               |

|--------------------------|---------------------------|---------------|

| PWRDWN/IDLE<br>(SCCR2.6) | HALT/STANDBY<br>(SCCR2.7) | MODE SELECTED |

| 1                        | 0                         | Standby       |

| 1                        | 1                         | Halt          |

The following information is preserved throughout both the STANDBY and HALT modes: RAM (register file), CPU registers (stack pointer, program counter, and status register), I/O pin direction and output data, and status registers of all on-chip peripheral functions. All CPU instruction processing is stopped during the STANDBY and HALT modes, and clocking of the watchdog timer is inhibited.

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

# peripheral file frame 1

T-49-19-01

Peripheral File Frame 1 contains system configuration and control functions and registers for controlling EPROM and EEPROM programming. The privileged bits are shown in a **bold typeface** in the Peripheral File Frames.

# Peripheral File Frame 1: System Configuration and Control Registers

| ADDR                 | PF                 | BIT 7            | BIT 6            | BIT 5              | BIT 4               | BIT 3            | BIT 2              | BIT 1            | BIT 0                |       |

|----------------------|--------------------|------------------|------------------|--------------------|---------------------|------------------|--------------------|------------------|----------------------|-------|

| 1010h                | P010               | COLD<br>START    | OSC<br>POWER     | PF AUTO<br>WAIT    | OSC FLT<br>FLAG     | MC PIN<br>WPO    | MC PIN<br>DATA     | _                | μΡ/μC<br>MODE        | SCCR  |

| 1011h                | P011               | _                |                  | _                  | AUTOWAIT<br>DISABLE | _                | MEMORY<br>DISABLE  | _                | _                    | SCCR  |

| 1012h                | P012               | HALT/<br>STANDBY | PWRDWN/<br>IDLE  | OSC FLT<br>RST ENA | BUS<br>STEST        | CPU<br>STEST     | OSC FLT<br>DISABLE | INT1<br>NMI      | PRIVILEGE<br>DISABLE | SCCR  |

| 1013h<br>to<br>1016h | P013<br>to<br>P016 |                  | RESERVED         |                    |                     |                  |                    |                  |                      |       |

| 1017h                | P017               | INT1<br>FLAG     | INT1<br>PIN DATA | _                  | _                   |                  | INT1<br>POLARITY   | INT1<br>PRIORITY | INT1<br>ENABLE       | INT1  |

| 1018h                | P018               | INT2<br>FLAG     | INT2<br>PIN DATA | _                  | INT2<br>DATA DIR    | INT2<br>DATA OUT | INT2<br>POLARITY   | INT2<br>PRIORITY | INT2<br>ENABLE       | INT2  |

| 1019h                | P019               | INT3<br>FLAG     | INT3<br>PIN DATA | _                  | INT3<br>DATA DIR    | INT3<br>DATA OUT | INT3<br>POLARITY   | INT3<br>PRIORITY | INT3<br>ENABLE       | INT3  |

| 101Ah                | P01A               | BUSY             |                  |                    | _                   |                  | AP                 | W1W0             | EXE                  | DEECT |

| 101Bh                | P01B               |                  | RESERVED         |                    |                     |                  |                    |                  |                      |       |

| 101Ch                | P01C               | BUSY             | VPPS             |                    | _                   |                  | _                  | W0               | EXE                  | EPCTL |

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

### peripheral file frame 2

Peripheral File Frame 2 contains the digital I/O pin configuration and control registers. The following figure details the specific addresses, registers, and control bits within this Peripheral File Frame.

### Peripheral File Frame 2: Digital Port Control Registers

| ADDR                 | PF                 | BIT 7           | BIT 6                                  | BIT 5            | BIT 4       | BIT 3     | BIT 2 | BIT 1 | BIT 0 |  |

|----------------------|--------------------|-----------------|----------------------------------------|------------------|-------------|-----------|-------|-------|-------|--|

| 1020h                | P020               |                 |                                        |                  | RES         | ERVED     |       | -     |       |  |

| 1021h                | P021               | ·               | Port A Control Register 2 (must be 0)  |                  |             |           |       |       |       |  |

| 1022h                | P022               |                 | Port A Data                            |                  |             |           |       |       |       |  |

| 1023h                | P023               |                 |                                        |                  | Port A      | Direction |       |       |       |  |

| 1024h<br>to<br>102Bh | P024<br>to<br>P02B |                 | RESERVED                               |                  |             |           |       |       |       |  |

| 102Ch                | P02C               |                 | Port D Con                             | rol Register 1   | (must be 0) |           | х     | Х     | х     |  |

| 102Dh                | P02D               |                 | Port D Control Register 2 (must be 0)† |                  |             |           |       | Х     | Х     |  |

| 102Eh                | P02E               | Port D Data X X |                                        |                  |             |           | Х     |       |       |  |

| 102Fh                | P02F               |                 |                                        | Port D Direction | on          |           | Х     | Х     | Х     |  |

<sup>†</sup> To configure pin D3 as CLKOUT, set Port D Control Register 2 equal to 08h.

### **Port Configuration Registers Set-up**

| PORT | PIN | abcd<br>00x0 | abcd<br>00q1 |

|------|-----|--------------|--------------|

| Α    | 0-7 | Data In      | Out q        |

| D    | 3-7 | Data In      | Out q        |

| -    |     |              |              |

NOTES: 2. Each bit controls the corresponding pin; for example, bit 6 controls Port pin 6. Each pin is individually configurable.

3. Only register combination 00xx is defined for TMS370Cx10.

SPNS012B - MAY 1987 - REVISED DECEMBER 1990

### programmable timers

T-49-19-01

The programmable timer module of the TMS370Cx10 provides the designer with the enhanced timer resources required to perform realtime system control. The Timer 1 module contains the general-purpose T1 and the watchdog timer WD. The two independent 16-bit timers, T1 and WD, allow program selection of input clock sources (realtime, external event, or pulse accumulate) with multiple 16-bit registers (input capture and compare) for special timer function control. These timers provide the capabilities for:

### **System Requirements**

Realtime System Control

Input Pulse Width Measurement

External Event Synchronization

Timer Output Control

Pulse-Width Modulated Output Control

System Integrity

#### **Timer Resource**

Interval Timers with Interrupts

Pulse Accumulate or Input Capture Functions

Event Counter Function

Compare Function

PWM Output Function

Watchdog Function

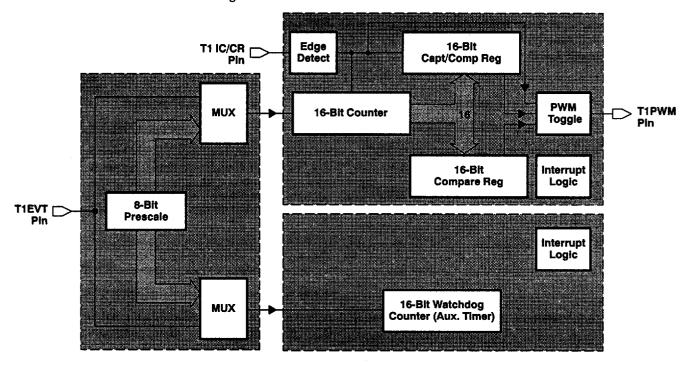

#### timer 1 module

The timer 1 module consists of three major blocks:

- 1. Prescaler/Clock Source, which determines the independent clock sources for the general purpose timer and the watchdog timer.

- 2. 16-bit General Purpose Timer, T1, which provides the event count, input capture, and compare functions.

- 3. 16-bit Watchdog Timer, which may be software programmed as an event counter, pulse accumulator, or interval timer if the watchdog function is not desired.

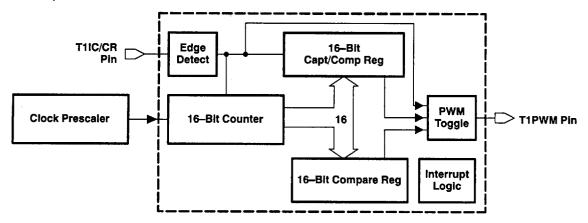

Figure 7. Timer 1 Module Block Diagram

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

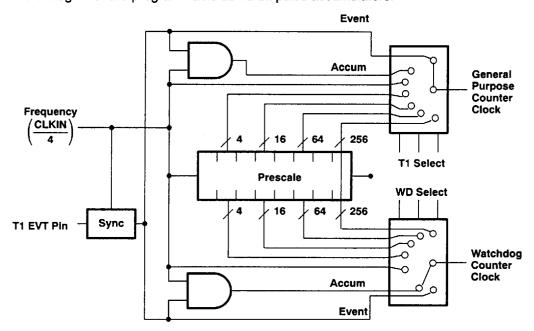

# timer 1 module prescaler/clock source

The clock source inputs for the general purpose timer and the watchdog timer are independently configured by the T1 and WD INPUT SELECT control bits of the T1CTL1 cotnrol register. The WD INPUT SELECT control bits cannot be changed after entering the watchdog mode (WD RST ENA = 1). Eight possible clock sources are programmable for each counter.

| T1 INPUT |          |          |                  |          | WD INPUT |          |  |

|----------|----------|----------|------------------|----------|----------|----------|--|

| SELECT 2 | SELECT 1 | SELECT 0 |                  | SELECT 2 | SELECT 1 | SELECT 0 |  |

| 0        | 0        | 0        | System Clock     | 0        | 0 .      | 0        |  |

| 0        | 0        | 1 1      | Pulse Accumulate | 0        | 0        | 1        |  |

| 0        | 1        | 0        | Event Input      | 0        | 1        | 0        |  |

| 0        | 1        | 1        | No Clock Input   | 0        | 1        | 1        |  |

| 1        | 0        | 0        | System Clock/4   | 1        | 0        | 0        |  |

| 1        | 0        | 1 1      | System Clock/16  | 1 1      | 0        | 1        |  |

| 1        | 1        | 0        | System Clock/64  | 1        | 1        | 0        |  |

| 1        | 1        | 1 1      | System Clock/256 | 1        | 1        | 1        |  |

For realtime control applications, both the general-purpose timer and the watchdog timer are independently programmable from 15 to 24 bits in length. The 24-bit prescaler/timer generates overflow rates ranging from 13.1 ms with 200 ns timer resolution to 3.35 seconds with 51.2 µs timer resolution (external clock = 20 MHz).

In the **Event Counter mode**, an external high-to-low transition on the T1EVT pin is used to provide the clock for the internal timers. As shown in Figure 8, the T1EVT input provides the timer clock and is not routed through the prescaler. The T1EVT external clock frequency may not exceed the system clock frequency divided by 2. The general-purpose timer and the watchdog timer are programmable as 16-bit event counters.

In the **Pulse Accumulate mode**, an external input on the T1EVT pin is used to gate the internal system clock to the internal timers. While T1EVT input is logic one (high), the timers will be clocked at the system clock rate and will accumulate system clock pulses until the T1EVT pin returns to logic zero. Both the general purpose timer and the watchdog timer are programmable as 16-bit pulse accumulators.

Figure 8. Timer 1 Counter Prescaler

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

# timer 1 general purpose timer

T-49-19-01

The 16-bit general purpose timer, T1, is composed of a 16-bit resettable counter, a 16-bit compare register and associated compare logic, and a 16-bit register that functions as a capture register in one mode and a compare register in the other mode. The T1 MODE bit selects whether T1 operates in the Capture/Compare mode or the Dual Compare mode.

Figure 9. Timer 1 — General Purpose Timer

The counter is a free-running, 16-bit up-counter, clocked by the output of the Prescaler/Clock source. During initialization the counter is loaded with 0000h and begins its up-count. If the counter is not reset before reaching FFFFh, the counter will roll over to 0000h and continue counting. Upon counter roll-over, the T1 OVRFL INT FLAG is set to 1, and a timer interrupt is generated if the T1 OVRFL INT ENA bit is set to 1.

The counter may be reset to 0000h during counting by either; 1) writing a 1 to the T1 SW RESET bit; 2) a compare equal condition from the dedicated T1 compare function; or 3) an external pulse on the T1 IC/CR pin (Dual Compare mode). The designer may select via software (T1 EDGE POLARITY bit) which external transition, low-to-high or high-to-low, on the T1IC/CR pin will cause the counter to be reset.

Special circuitry prevents the 16-bit registers, including the Counter, Compare, or Capture registers, from changing in the middle of a 16-bit read or write operation. When reading a 16-bit register, read the LSB first and then read the MSB. When writing to a 16-bit register, write the MSB first and then write the LSB. The register value will not change between reading or writing the bytes when done in this order.

The timer 1 module has three I/O pins used for the functions shown in the following table. Any of these three pins not used in a timer application may be individually configured as general purpose digital I/O pins by the timer 1 module port control registers (T1PC1 and T1PC2).

Timer 1 Module I/O Pin Functions

| PIN     | DUAL COMPARE MODE                              | CAPTURE/COMPARE MODE                           |

|---------|------------------------------------------------|------------------------------------------------|

| T1IC/CR | Counter Reset input                            | Input Capture input                            |

| T1PWM   | PWM output                                     | Compare output                                 |

| T1EVT   | External Event input or Pulse Accumulate input | External Event input or Pulse Accumulate input |

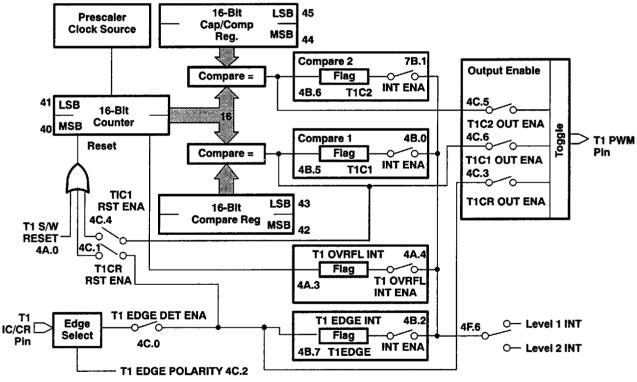

The **Dual Compare mode** (T1 MODE = 0) provides two compare registers, an external resettable counter, and a timer output pin. These allow the timer to act as an interval timer, a PWM output, simple output toggle, or many other timer functions. The Dual Compare mode as shown in Figure 10 continuously compares the contents of the two compare registers to the current value of the 16-bit counter. If a timer compare register equals the counter, the circuit sets the associated interrupt flag to 1 and toggles the T1PWM output pin if enabled, and/or

SPNS012B -- MAY 1987 -- REVISED DECEMBER 1990

generates a Timer 1 interrupt. An output compare equal condition from the dedicated compare register can also initiate a counter reset. A programmable interval timer function, selected by using the compare equal condition to generate a system interrupt and the counter reset function, generates a periodic interrupt.

Either compare function may be used to toggle the T1PWM output pin when a timer compare equal occurs, while the other compare function may be used for another system timing function. Using both compare functions to control the T1PWM pin allows direct PWM generation with minimal CPU software overhead. In typical PWM applications, the compare register is written with the periodic interval and is configured to allow counter reset on compare equal, and the Capture/Compare register is written with the pulse width to be generated within that interval. The program pulse width may be changed by the application program during the timer operation to alter the PWM output. For high-speed control applications, a minimum pulse width of 200 ns and a period as low as 400 ns can be maintained when using a clock of 20 MHz.

In addition, a PWM output that is initiated by a transition on an external pin is provided by the timer hardware to support time-critical control applications. Typically, in these applications an external input (T1IC/CR) is used to reset the counter, generate a timer interrupt, and toggle the T1PWM pin to start the PWM output. The compare function will then toggle the output after the programmed pulse width has elapsed. The input edge detect function is enabled under program control by the T1CR DET ENA bit, and upon the next occurrence of the selected edge transition, the T1EDGE INT FLAG bit is set to 1, a timer interrupt is generated (if T1EDGE INT ENA = 1), and the T1PWM output pin is toggled (if T1CR OUT ENA = 1). Selection of the active input transition is under control of T1EDGE POLARITY. In the Dual Compare mode, the edge detect function must be re-enabled after each valid edge detect.

NOTE 4: The numbers on the diagram, such as 4C.0, identify the register and the bit in the peripheral frame. For example, the actual address of 4C.0 is 104Ch, bit 0, in the T1CTL4 register.

Figure 10. Timer 1 — Dual Compare Mode

TEXAS INSTR (UC/UP)

T-49-19-01 SPNS012B - MAY 1987 - REVISED DECEMBER 1990

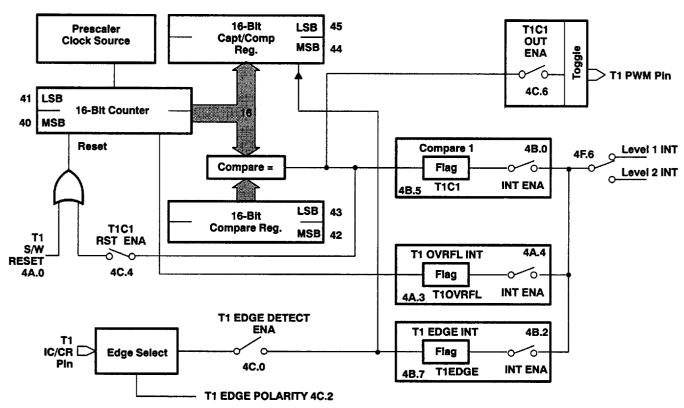

In the Capture/Compare mode (T1 MODE = 1), T1 is configured to provide one input capture register for external timing and pulse width measurement, and one compare register for use as a programmable interval timer. The compare register in this mode functions the same as in the Dual Compare mode described above, including the ability to toggle the PWM pin. The capture/compare register functions in this mode as a 16-bit input capture register, as shown in Figure 11. On the occurrence of a valid input on the T1IC/CR pin, the current counter value is loaded into the 16-bit input capture register, the T1 EDGE INT FLAG is set to 1, and a timer interrupt is generated (if TI EDGE INT ENA = 1). The input detect function is enabled by the T1 EDGE DET ENA bit, with T1 EDGE POLARITY selecting the active input transition. In the Capture/Compare mode, the edge detect function, once enabled, remains enabled following a valid edge detect.

NOTE 4: The numbers on the diagram, such as 4C.0, identify the register and the bit in the peripheral frame. For example, the actual address of 4C.0 is 104Ch, bit0, in the T1CTL4 register.

Figure 11. Timer 1 — Capture/Compare Mode

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

# timer 1 module watchdog timer

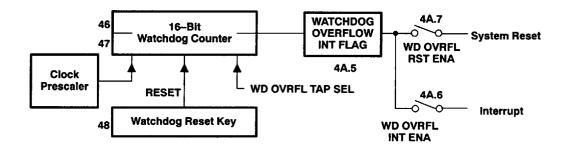

The watchdog timer, contained in the timer 1 module, is a free-running 16-bit resettable up-counter clocked by the output of the Prescaler/Clock Source. The timer is software configured as either a watchdog timer to protect against system software failures and corruption, or as a general purpose timer if the watchdog function is not desired. The 16-bit up-counter is programmable (via the WD OVRFLTAP SEL bit) to set the initial count at either 0000h or 8000h. The current value of the watchdog timer may be read at any time during its operation.

In the **Watchdog mode** (WD OVRFL RST ENA = 1), the timer will generate a system reset if the timer is re-initialized by an incorrect value or if the counter overflows. The required re-initialization frequency is determined by the system clock frequency, the prescaler/clock source selected, and whether the WD OVRFL TAP SEL bit is set for 15 or 16 bit counter rollover. With a clock = 20 MHz, the watchdog timer overflow rates range form 6.55 ms to 3.35 seconds. These values are selected prior to entering the watchdog mode because once the software enables the watchdog reset function (WD OVRFL RST ENA set to 1), subsequent writes to these control bits are ignored. Writes to these watchdog control bits can occur only following a powerup reset, which enhances watchdog timer system integrity.

The watchdog timer is re-initialized by writing a predefined value to the watchdog reset key (WDRST) located in the peripheral file. The proper reset key alternates between 55h and AAh, beginning with 55h following the enable of the watchdog reset function. Writes of the correct value must occur prior to the timer overflow period. A write of any value other than the correct predefined value to the watchdog reset key will be interpreted as a lost program and a system reset will be initiated. A watchdog timer overflow or incorrect reset key will set the WD OVRFL INT FLAG bit to 1 and may be interrogated by the program following system reset to determine the source of the reset.

In the **Non-watchdog mode** (WD OVRFL RST ENA = 0), the watchdog timer may be used as an event counter, pulse accumulator, or as an interval timer. In this mode, the system reset function is disabled. The watchdog counter is re-initialized by writing any value to the watchdog reset key (WDRST). In real-time control applications, the timer overflow rates are determined by the system clock frequency, the prescaler/clock source value selected, and the value of the WD OVRFL TAP SEL bit. If the WD counter is not reset before overflowing, the counter will roll over to either 0000h or 8000h, as determined by the WD OVRFL TAP SEL bit, and continue counting. Upon counter overflow, the WD OVRFL INT FLAG is set to 1 and a timer interrupt is generated if the WD OVRFL INT ENA bit set to 1. Alternately, an external input on the T1EVT pin may be used with the watchdog timer to provide an additional 16-bit event counter or pulse accumulator.

Figure 12. Watchdog/General Purpose Timer

TEXAS INSTR (UC/UP)

SPNS012B -- MAY 1987 -- REVISED DECEMBER 1990

# Peripheral File Frame 4: Timer 1 Module Control Registers

T-49-19-01

| ADDR          | PF     | BIT 7                            | BIT 6                             | BIT 5                             | BIT 4                             | BIT 3                | BIT 2                | BIT 1                | BIT 0                |        |  |

|---------------|--------|----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|----------------------|----------------------|----------------------|----------------------|--------|--|

| 1040h         | P040   | Bit 15                           |                                   |                                   | Counte                            | er MSB               |                      |                      | Bit 8                | T1CNTR |  |

| <b>104</b> 1h | P041   | Bit 7                            |                                   |                                   | Count                             | er LSB               |                      |                      | Bit 0                | HONIA  |  |

| 1042h         | P042   | Bit 15                           |                                   |                                   | Compare Re                        | egister MSB          |                      |                      | Bit 8                | T1C    |  |

| 1043h         | P043   | Bit 7                            | it 7 Compare Register LSB Bit 0   |                                   |                                   |                      |                      |                      |                      |        |  |

| 1044h         | P044   | Bit 15                           |                                   | С                                 | apture/Compa                      | re Register MS       | В                    |                      | Bit 8                | T1CC   |  |

| 1045h         | P045   | Bit 7                            |                                   | C                                 | apture/Compa                      | re Register LS       | В                    |                      | Bit 0                |        |  |

| 1046h         | P046   | Bit 15                           |                                   |                                   | Watchdog C                        | ounter MSB           |                      |                      | Bit 8                | WDCNTR |  |

| 1047h         | P047   | Bit 7                            |                                   |                                   | Watchdog C                        | Counter LSB          |                      |                      | Bit 0                | 7      |  |

| 1048h         | P048   |                                  |                                   |                                   | Watchdog                          | Reset Key            |                      |                      |                      | WDRST  |  |

| 1049h         | P049   | WD OVRFL<br>TAP SEL <sup>†</sup> | WD INPUT<br>SELECT 2 <sup>†</sup> | WD INPUT<br>SELECT 1 <sup>†</sup> | WD INPUT<br>SELECT 0 <sup>†</sup> |                      | TI INPUT<br>SELECT 2 | TI INPUT<br>SELECT 1 | TI INPUT<br>SELECT 0 | T1CTL1 |  |

| 104Ah         | P04A   | WD OVRFL<br>RST ENA <sup>†</sup> | WD OVRFL<br>INT ENA               | WD OVRFL<br>INT FLAG              | TI OVRFL<br>INT ENA               | T1 OVRFL<br>INT FLAG | _                    | _                    | T1<br>SW RESET       | T1CTL2 |  |

| Mode:         | Dual C | ompare                           |                                   |                                   |                                   |                      |                      |                      |                      |        |  |

| 104Bh         | P04B   | T1 EDGE<br>INT FLAG              | T1C2<br>INT FLAG                  | T1C1<br>INT FLAG                  | _                                 | _                    | T1 EDGE<br>INT ENA   | T1C2<br>INT ENA      | T1C1<br>INT ENA      | T1CTL3 |  |

| 104Ch         | P04C   | T1 MODE<br>= 0                   | T1C1<br>OUT ENA                   | T1C2<br>OUT ENA                   | T1C1<br>RST ENA                   | T1CR<br>OUT ENA      | T1EDGE<br>POLARITY   | T1CR<br>RST ENA      | T1EDGE<br>DET ENA    | T1CTL4 |  |

| Mode:         | Captur | e/Compare                        |                                   |                                   |                                   |                      |                      |                      |                      | •      |  |

| 104Bh         | P04B   | T1EDGE<br>INT FLAG               | <u> </u>                          | T1C1<br>INT FLAG                  | _                                 |                      | T1 EDGE<br>INT ENA   | <u>-</u>             | T1C1<br>INT ENA      | T1CTL3 |  |

| 104Ch         | P04C   | T1 MODE<br>= 1                   | T1C1<br>OUT ENA                   |                                   | T1C1<br>RST ENA                   |                      | T1EDGE<br>POLARITY   | _                    | T1EDGE<br>DET ENA    | T1CTL4 |  |

|               |        |                                  |                                   |                                   |                                   |                      |                      |                      |                      | •      |  |

| 104Dh         | P04D   | _                                |                                   | _                                 | -                                 | T1EVT<br>DATA IN     | T1EVT<br>DATA OUT    | T1EVT<br>FUNCTION    | T1EVT<br>DATA DIR    | T1PC1  |  |

| 104Eh         | P04E   | T1PWM<br>DATA IN                 | T1PWM<br>DATA OUT                 | T1PWM<br>FUNCTION                 | T1PWM<br>DATA DIR                 | T1IC/CR<br>DATA IN   | T1IC/CR<br>DATA OUT  | T1IC/CR<br>FUNCTION  | T1IC/CR<br>DATA DIR  | T1PC2  |  |

| 104Fh         | P04F   | T1<br>STEST                      | T1<br>PRIORITY                    | _                                 | _                                 | _                    | _                    |                      |                      | T1PRI  |  |

<sup>†</sup> Subsequent writes to these control bits are ignored after the WD OVRFL RST ENA bit is set to 1 (see timer1 module watchdog timer) and can be initialized only following a powerup reset.

The formulas in Figure 13 show the calculations for the resulting time, given values in the compare registers T1C and T1CC.

time =

$$\left(\frac{4}{\text{CLKIN}}\right)$$

(prescale) (compare + 1)

or

time =  $t_c$  (prescale) (compare + 1)

Figure 13. Timer 1 Compare Register Formulas

SPNS012B -- MAY 1987 -- REVISED DECEMBER 1990

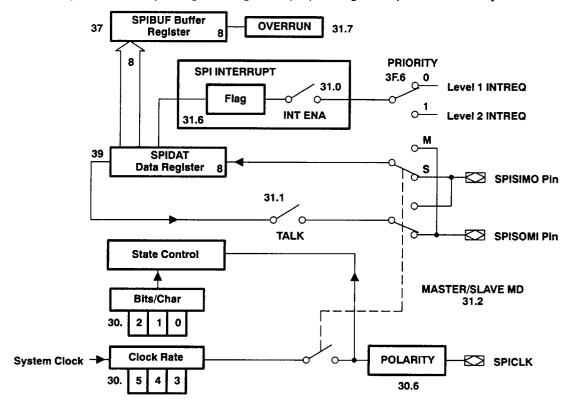

# serial peripheral interface (SPI)

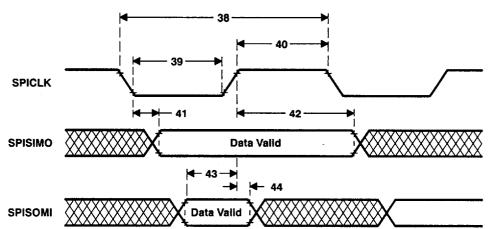

The Serial Peripheral Interface (SPI) is a high-speed synchronous serial I/O port that allows a serial bit stream of programmed length (one to eight data bits) to be shifted into and/or out of the device at a programmed bit transfer rate. The SPI is normally used for communications between the microcontroller and external peripherals or another microcontroller. Typical applications include external I/O or peripheral expansion using devices such as shift registers, display drivers, A/D converters, etc. Multiprocessor communications are also supported by the master/slave operation of the SPI.

Three I/O pins are associated with the SPI. These include the SPI slave-in master-out (SPISIMO), SPI slave-out master-in (SPISOMI), and SPI serial serial clock (SPICLK). These I/O pins can be configured for three-wire full-duplex transmit/receive or two-wire receive or transmit only. Any of these three pins not used in an SPI application may be individually configured as general purpose digital I/O pins controlled by SPIPC1 and SPIPC2.

Figure 14. SPI Block Diagram

A variety of multiprocessor configurations can be supported, ranging from single master with multiple slaves to multi-master systems. General purpose I/O pins can be used to implement the slave enables and multi-master hardware handshakes between microcontrollers in the network.

The MASTER/SLAVE bit of the SPICTL control register determines if the SPI operates in the master or slave mode. Master or slave data transmission can be disabled by writing a zero to the TALK bit of the SPICTL control register, forming a two-wire receive-only network (SPICLK and data in).

In the **Master mode** (MASTER/SLAVE = 1), the SPI provides the serial clock on the SPICLK pin for the entire serial communications network. The SPICCR register (SPI BIT RATE2, RATE1, RATE0) determines the bit transfer rate for the network, both transmit and receive. For any specific system clock frequency, there are eight data transfer rates that can be selected by these control bits. The data transfer rate is defined by selecting a one-of-eight divide-by of the system clock frequency (divide-by-2, -4, -8, -16, -32, -64, -128, and -256).

SPNS012B -- MAY 1987 -- REVISED DECEMBER 1990

SPI Baud Rate =

$$\frac{\text{CLKIN}}{8 \times 2^{\text{b}}}$$

T-49-19-01

where b = bit rate in SPICCR bit 3, 4, 5 (range 0-7).

Data written to the SPIDAT register initiates data transmission on the SPISIMO pin, MSB of data transmitted first. Simultaneously, received data is shifted in the SPISOMI pin into the SPIDAT register, and upon completion of transmitting the selected number of bits, the data is transferred to the SPIBUF (double buffered receiver) for reading by the CPU to permit new transactions to take place. Data is shifted into the SPI the most significant bit first, there it is stored right-justified in the SPIBUF. To receive a character when operating as a master, data must be written to the SPIDAT to initiate the transaction. When the specified number of data bits have been shifted into or out of the SPIDAT register, the SPI INT FLAG bit is set and if the SPI INT ENA bit is set to one, an Interrupt is asserted.

In the **Slave mode** (MASTER/SLAVE = 0), data shifts out on the SPISOMI pin and in on the SPISIMO pin. The SPICLK pin is used as the input for the serial shift clock, which is supplied from the external network master. The transfer rate is defined by the input clock on the SPICLK pin, which is supplied from the network master. The SPICLK input frequency should be no greater than system clock frequency divided by eight.

Data written to the SPIDAT register will be transmitted to the network when the SPICLK is received from the network master. To receive data, the SPI waits for the network master to send SPICLK and then shifts the data on the SPISIMO pin into the SPIDAT register. If data is to be transferred by the slave simultaneously, then it must be written to the SPIDAT register prior to the beginning of SPICLK.

Compatibility with the broadest range of existing peripheral devices is provided by the SPI through its software programmable transmit/receive character length, bit transfer rate, and clock polarity. A character length from one to eight data bits is selected by writing to the SPICCR control register (SPI CHAR2, CHAR1, and CHAR0) to specifically match the peripheral's data length requirements, thereby not requiring the overhead of data bit padding during communications. Applications requiring more than eight bits of serial data use multiple back-to-back SPI operations.

External peripherals enable output data on either the rising or the falling edge of the serial clock, while latching incoming data on the opposite edge. The SPI supports data transfer using either of these approaches. The CLOCK POLARITY bit controls the steady-state or at-rest condition of the SPICLK signal. This bit affects both master and slave modes of operation. When CLOCK POLARITY is set to 1, the at-rest level of SPICLK is a logic one (high). Data is enabled at the output on the falling edge of SPICLK, and data is latched by the network master and slaves on the rising edge of SPICLK. When CLOCK POLARITY is set to zero, the at-rest level of SPICLK is a logic zero (low). Data is enabled for output on the rising edge of SPICLK, and data is latched by the network master on the falling edge of SPICLK.

# TMS370Cx10 8-BIT MICROCONTROLLERS

SPNS012B — MAY 1987 — REVISED DECEMBER 1990

T-49-19-01

# Peripheral File Frame 3: Serial Peripheral Interface (SPI) Control Registers

| ADDR                 | PF                 | BIT 7               | BIT 6                                                  | BIT 5               | BIT 4               | BIT 3              | BIT 2               | BIT 1               | BIT 0               |        |  |  |  |  |  |

|----------------------|--------------------|---------------------|--------------------------------------------------------|---------------------|---------------------|--------------------|---------------------|---------------------|---------------------|--------|--|--|--|--|--|

| 1030h                | P030               | SPI<br>SW RESET     | CLOCK<br>POLARITY                                      | SPI BIT<br>RATE2    | SPI BIT<br>RATE1    | SPI BIT<br>RATE 0  | SPI<br>CHAR2        | SPI<br>CHAR1        | SPI<br>CHAR0        | SPICCR |  |  |  |  |  |

| 1031h                | P031               | RECEIVER<br>OVERRUN | SPI<br>INT FLAG                                        | _                   | _                   | _                  | MASTER/<br>SLAVE    | TALK                | SPI<br>INT ENA      | SPICTL |  |  |  |  |  |

| 1032h<br>to<br>1036h | P032<br>to<br>P036 |                     | Reserved                                               |                     |                     |                    |                     |                     |                     |        |  |  |  |  |  |

| 1037h                | P037               |                     | SPI Receive Data Buffer Register                       |                     |                     |                    |                     |                     |                     |        |  |  |  |  |  |

| 1038h                | P038               |                     | Reserved                                               |                     |                     |                    |                     |                     |                     |        |  |  |  |  |  |

| 1039h                | P039               |                     |                                                        |                     | SPI Serial D        | ata Register       |                     |                     |                     | SPIDAT |  |  |  |  |  |

| 103Ah<br>to<br>103Dh | P03A<br>to<br>P03C |                     |                                                        |                     | Rese                | rved               |                     |                     |                     |        |  |  |  |  |  |

| 103Dh                | P03D               | _                   | SPICLK SPICLK SPICLK SPICLK DATA OUT FUNCTION DATA DIR |                     |                     |                    |                     |                     |                     |        |  |  |  |  |  |

| 103Eh                | P03E               | SPISIMO<br>DATA IN  | SPISIMO<br>DATA OUT                                    | SPISIMO<br>FUNCTION | SPISIMO<br>DATA DIR | SPISOMI<br>DATA IN | SPISOMI<br>DATA OUT | SPISOMI<br>FUNCTION | SPISOMI<br>DATA DIR | SPIPC2 |  |  |  |  |  |

| 103Fh                | P03F               | SPI<br>STEST        | SPI<br>PRIORITY                                        | SPI<br>ESPEN        | _                   | _                  | <u>-</u>            | _                   |                     | SPIPRI |  |  |  |  |  |

SPNS012B -- MAY 1987 -- REVISED DECEMBER 1990

### instruction set

T-49-19-01

The TMS370 family instruction set consists of 73 instructions that control input, output, data manipulations, data comparisons, and program flow. The instruction set is supported with 14 addresssing modes to provide the flexibility to optimize programs to the user's applications. For example, the MOV instruction has 27 operand combinations supported by its addressing modes.

| ADDRESSING MODE                                                                                                                                                                     | E                                                 | KAMPLE                                                                       | OPERATION                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|