## PRELIMINARY DATA SHEET BU-64703 SIMPLE SYSTEM RT Mark3 (SSRT Mark3)

## DESCRIPTION

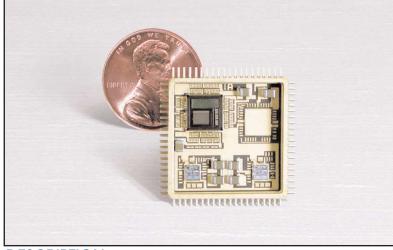

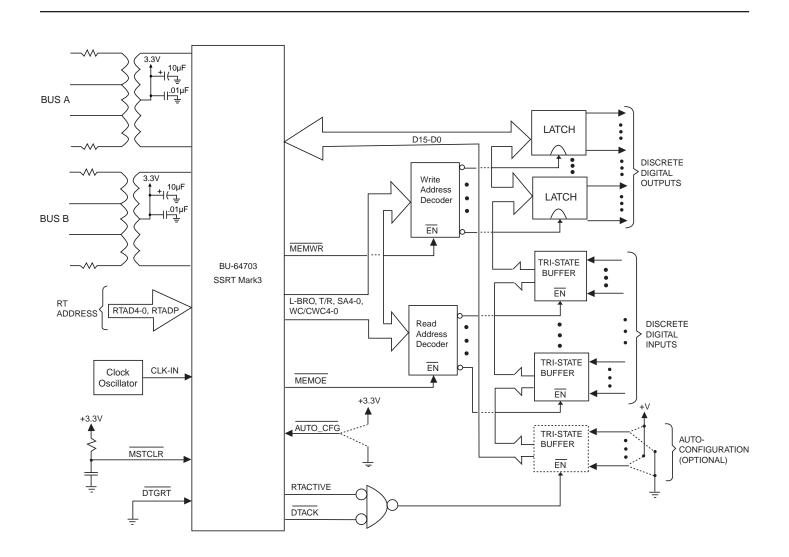

The BU-64703 Simple System RT Mark3 (SSRT Mark3) MIL-STD-1553 terminals provide a complete interface between a simple system and a MIL-STD-1553 bus. The SSRT Mark3 is powered entirely by 3.3 volts, thus eliminating the need for a 5V power supply. This terminal integrates dual transceiver, protocol logic, and a FIFO memory for received messages in a 0.88 inch square ceramic package. The gull wing package with a "toe-to-toe" maximum dimension of 1.13 inches enables its use in applications where PC board space is at a premium. The SSRT Mark3 provides multi-protocol support of MIL-STD-1553A/B, MIL-STD-1760, McAir, and STANAG-3838.

The SSRT Mark3's transceivers are completely monolithic, require only a +3.3V supply, and consume low power. The internal architecture is identical to that of the original BU-61703/61705 Simple System RT (SSRT). There are versions of the Simple System RT Mark3 available with transceivers trimmed for MIL-STD-1760 compliance, or compatible to McAir standards. The SSRT Mark3 can operate with a choice of clock frequencies of 10, 12, 16, or 20 MHz.

The SSRT Mark3 incorporates a built-in self-test (BIT). This BIT, which is processed following power turn-on or after receipt of an Initiate Self-Test Mode command, provides a comprehensive test of the SSRT Mark3's encoders, decoders, protocol, transmitter watch-dog timer, and protocol section. The SSRT Mark3 also includes an auto-configuration feature.

The SSRT Mark3 is ideal for stores and other simple systems that do not require a microprocessor. To streamline the interface to simple systems, the SSRT Mark3 includes an internal 32-word FIFO for received data words. This serves to ensure that only complete, consistent blocks of validated data words are transferred to a system.

## • FEATURES

- Complete Integrated Remote Terminal Including:

- All 3.3Volt Terminal (No Other Power Supplies Are Required)

- Dual Low-Power 3.3V Only Transceivers

- Complete RT Protocol Logic

- Supports MIL-STD-1553A/B Notice 2, STANAG-3838 RT, and MIL-STD-1760 Stores Management

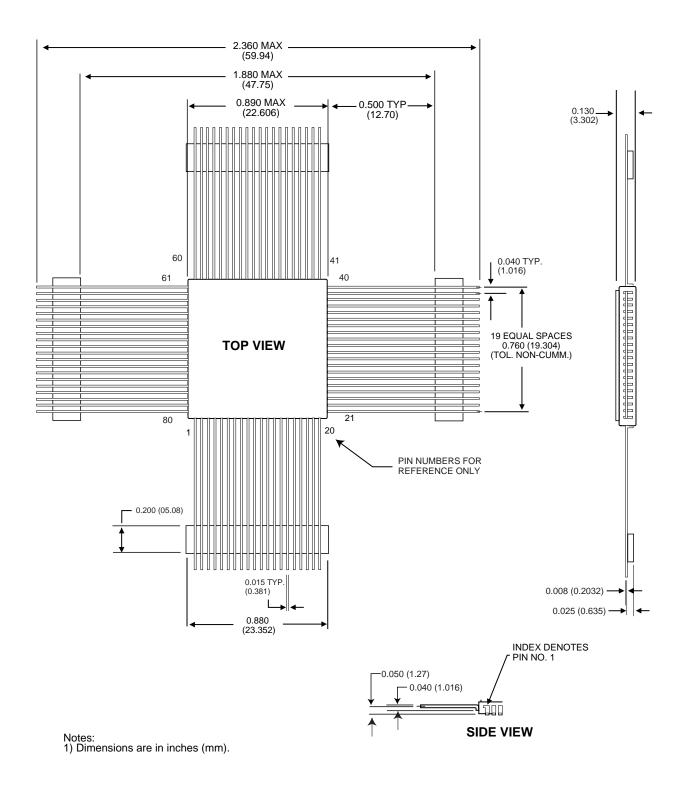

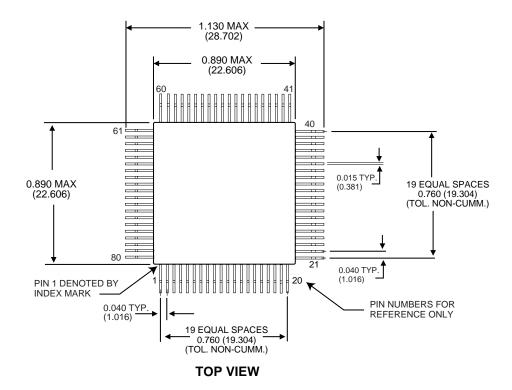

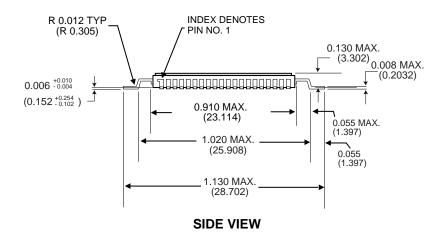

- 0.88" X 0.88", 0.130", Max Height CQFP

- 80-Pin Ceramic Flatpack or Gullwing

Package

- 3.3V Logic Power

- Meets 1553A/McAir Response Time Requirements

- Internal FIFO for Burst Mode Capability on Receive Data

- 16-bit DMA Interface

- Auto Configuration Capability

- Comprehensive Built-In Self-Test

- Direct Interface to Simple (Processorless) Systems

- Available with Full Military Temperature Range and Screening

- Selectable Input Clock: 10, 12, 16, or 20 MHz

This Preliminary data sheet provides detailed functional capabilities for product currently in prototype production. These specifications are being provided to allow for electrical design, layout and operation.

FOR MORE INFORMATION CONTACT:

Technical Support: 1-800-DDC-5757 ext. 7234

Data Device Corporation 105 Wilbur Place Bohemia, New York 11716 631-567-5600 Fax: 631-567-7358 www.ddc-web.com

© 2003 Data Device Corporation

BU-64703 Pre-01-03/03

Ν

| TABLE 1. SSRT Mark3 SPECIFICATIONS                                                                                                                                                                   |                     |            |                  |                       |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|------------------|-----------------------|--|--|--|

| PARAMETER                                                                                                                                                                                            | MIN                 | TYP        | MAX              | UNITS                 |  |  |  |

| ABSOLUTE MAXIMUM RATING<br>Supply Voltage (Note 10)<br>• Logic (Voltage Input Range)<br>• Transceivers                                                                                               | -0.3<br>-0.3        |            | 6.0<br>6.0       | V<br>V                |  |  |  |

| (not during transmit)<br>• Transceiver (during transmit)                                                                                                                                             | -0.3                |            | 4.5              | V                     |  |  |  |

| RECEIVER<br>Differential Input Resistance<br>(Notes 1-6)                                                                                                                                             | 2.5                 |            |                  | kΩ                    |  |  |  |

| Differential Input Capacitance<br>(Notes 1-6)                                                                                                                                                        |                     |            | 5                | pF                    |  |  |  |

| Threshold Voltage, Transformer<br>Coupled, Measured on Stub                                                                                                                                          | 0.200               |            | 0.860            | Vp-р                  |  |  |  |

| Common Mode Voltage (Note 7)                                                                                                                                                                         |                     |            | 10               | Vpeak                 |  |  |  |

| <ul> <li>TRANSMITTER</li> <li>Differential Output Voltage (Note 8)</li> <li>Direct Coupled Across 35 Ω,<br/>Measured on Bus</li> <li>Transformer Coupled Across<br/>70 Ω, Measured on Bus</li> </ul> | 6                   | 7          | 9                | Vp-р                  |  |  |  |

| BU-64703XX-XX0<br>BU-64703X8-XX2 (Note 9)<br>Output Noise, Differential (Direct<br>Coupled)                                                                                                          | 18<br>20            | 20<br>22   | 27<br>27<br>10   | Vp-p<br>Vp-p<br>mVp-p |  |  |  |

| Output Offset Voltage, Transformer<br>Coupled Across 70 ohms<br>Rise/Fall Time                                                                                                                       | -250                |            | 250              | mVpeak                |  |  |  |

| BU-64703X8<br>BU-64703X9                                                                                                                                                                             | 100<br>200          | 150<br>250 | 300<br>300       | nsec<br>nsec          |  |  |  |

| LOGIC                                                                                                                                                                                                |                     |            |                  |                       |  |  |  |

| V⊪<br>All signals except CLOCK_IN<br>CLOCK_IN<br>Vı∟                                                                                                                                                 | 2.1<br>0.8•Vcc      |            |                  | V<br>V                |  |  |  |

| All signals except CLOCK_IN<br>CLOCK_IN<br>Schmidt Hysteresis                                                                                                                                        |                     |            | 0.7<br>0.2•Vcc   | V<br>V                |  |  |  |

| All signals except CLOCK_IN<br>CLOCK_IN<br>Iıн, Iı∟                                                                                                                                                  | 0.4<br>1.0          |            |                  | V<br>V                |  |  |  |

| All signals except CLOCK_IN<br>IIH (Vcc=3.6V, VIN=Vcc)<br>IIH (Vcc=3.6V, VIH=2.7V)<br>IIL (Vcc=3.6V, VIH=0.4V)<br>CLOCK_IN                                                                           | -10<br>-350<br>-350 |            | 10<br>-33<br>-33 | μΑ<br>μΑ<br>μΑ        |  |  |  |

| Ін<br>Іц                                                                                                                                                                                             | -10<br>-10          |            | 10<br>10         | μΑ<br>μΑ              |  |  |  |

| Voн (Vcc=3.0V, Viн=2.7V,<br>Vil=0.2V, Ioн=max)<br>Vol (Vcc=3.0V, Viн=2.7V,                                                                                                                           | 2.4                 |            |                  | V                     |  |  |  |

| VIL=0.2V, IoL=max)<br>IoL<br>Ioн                                                                                                                                                                     | 3.4                 |            | 0.4<br>-3.4      | V<br>mA<br>mA         |  |  |  |

| Cı (Input Capacitance)<br>Cıo (Bi-directional signal input<br>capacitance)                                                                                                                           |                     | 50<br>50   |                  | pF<br>pF              |  |  |  |

## TABLE 1. SSRT Mark3 SPECIFICATIONS (Cont'd)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |                              |                                                                                                                      | <u> </u>                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------|

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MIN             | TYP                          | MAX                                                                                                                  | UNITS                         |

| POWER SUPPLY REQUIREMENTS<br>Voltages/Tolerances (Note 10)<br>• +3.3V Logic<br>• +3.3V Transceivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.14<br>3.14    | 3.3<br>3.3                   | 3.46<br>3.46                                                                                                         | V<br>V                        |

| Current Drain(Total Hybrid)(Notes 8,14)<br>• BU-64703X8/9-XX0,(1553 & McAir)<br>• Idle<br>• 25% Transmitter Duty Cycle<br>• 50% Transmitter Duty Cycle<br>• 100% Transmitter Duty Cycle<br>• BU-64703X8-XX2, (1760)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                              | 95<br>310<br>525<br>955                                                                                              | mA<br>mA<br>mA<br>mA          |

| <ul> <li>Idle</li> <li>25% Transmitter Duty Cycle</li> <li>50% Transmitter Duty Cycle</li> <li>100% Transmitter Duty Cycle</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |                              | 95<br>332<br>583<br>1.041                                                                                            | mA<br>mA<br>MA<br>A           |

| POWER DISSIPATION<br>Total Hybrid (Notes 8, 11 and 14)<br>• BU-64703X8/9-XX0, (1553 & McAir)<br>• Idle<br>• 25% Transmitter Duty Cycle<br>• 50% Transmitter Duty Cycle<br>• 100% Transmitter Duty Cycle<br>• BU-64703X8-XX2, (1760)<br>• Idle<br>• 25% Transmitter Duty Cycle<br>• 100% Transmitter Duty Cycle<br>• 100% Transmitter Duty Cycle<br>• BU-64703X8/9-XX0 (1553 &McAir)<br>• Idle<br>• 25% Transmitter Duty Cycle<br>• 50% Transmitter Duty Cycle<br>• 50% Transmitter Duty Cycle<br>• 100% Transmitter Duty Cycle<br>• 50% Transmitter Duty Cycle |                 |                              | 0.31<br>0.67<br>1.02<br>1.72<br>0.31<br>0.74<br>1.16<br>2.01<br>0.09<br>0.45<br>0.80<br>1.51<br>0.09<br>0.54<br>0.54 | ***<br>****<br>****           |

| 100% Transmitter Duty Cycle  CLOCK INPUT  Frequency     Nominal Value     Default     Option     Option     Option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 | 16.0<br>12.0<br>10.0<br>20.0 | 1.80                                                                                                                 | W<br>MHz<br>MHz<br>MHz<br>MHz |

| Long Term Tolerance     1553A Compliance     1553B Compliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.01<br>0.10    |                              | -0.01<br>-0.10                                                                                                       | %<br>%                        |

| <ul> <li>Short Term Tolerance, 1 second</li> <li>1553A Compliance</li> <li>1553B Compliance</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -0.001<br>-0.01 |                              | 0.001<br>0.01                                                                                                        | %<br>%                        |

| Duty Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40              |                              | 60                                                                                                                   | %                             |

| TABLE 1. SSRT Mark3 SPECIFICATIONS (Cont'd)                        |          |          |            |        |  |  |

|--------------------------------------------------------------------|----------|----------|------------|--------|--|--|

| PARAMETER                                                          | MIN      | TYP      | MAX        | UNITS  |  |  |

| 1553 MESSAGE TIMING                                                |          |          |            |        |  |  |

| RT-to-RT Response Timeout<br>(Note 12)                             | 17.5     | 18.5     | 19.5       | μS     |  |  |

| RT Response Time                                                   |          |          |            | 1      |  |  |

| (mid-parity to mid-sync) (Note 12)<br>Transmitter Watchdog Timeout | 4        | 660.5    | 7          | μS     |  |  |

|                                                                    |          | 000.5    |            | μS     |  |  |

| Thermal Resistance (Notes 8, 13)                                   |          |          |            |        |  |  |

| Ceramic Flatpack / Gull Lead                                       |          |          |            |        |  |  |

| Junction-to-Case, Hottest Die (0JC)                                |          | 9        | 11         | °C/W   |  |  |

| Operating Case Temperature                                         |          |          |            |        |  |  |

| -1XX, -4XX                                                         | -55      |          | +125       | °C     |  |  |

| -2XX, -5XX                                                         | -40<br>0 |          | +85<br>+70 | ℃<br>℃ |  |  |

| -3XX, -8XX                                                         | 0        |          | +70        |        |  |  |

| Operating Junction Temperature                                     | -55      |          | 155        | °C     |  |  |

| Storage Temperature                                                | -65      |          | 155        | ℃<br>℃ |  |  |

| Lead Temperature (soldering, 10 sec.)                              |          |          | +300       | Ĵ      |  |  |

| PHYSICAL CHARACTERISTICS<br>Size                                   |          |          |            |        |  |  |

| 80-pin Ceramic Flatpack / Gull Lead                                | 0.88 >   | ( 0.88 ) | K 0.13     | in.    |  |  |

|                                                                    | (22.3    | x 22.3   | x 3.3)     | (mm)   |  |  |

| Lead Toe-Toe Distance<br>80-pin Gull Wing                          |          | 1.13     |            | in.    |  |  |

|                                                                    |          | (28.7)   |            | (mm)   |  |  |

|                                                                    |          | ()       |            | ()     |  |  |

| Weight<br>80-pin Ceramic Flatpack/Gull Wing                        |          | 0.353    |            | oz     |  |  |

| Package                                                            |          | (10)     |            | (g)    |  |  |

|                                                                    |          | · · /    |            | (0)    |  |  |

## TABLE 1. SSRT Mark3 SPECIFICATIONS (Cont'd

#### NOTES:

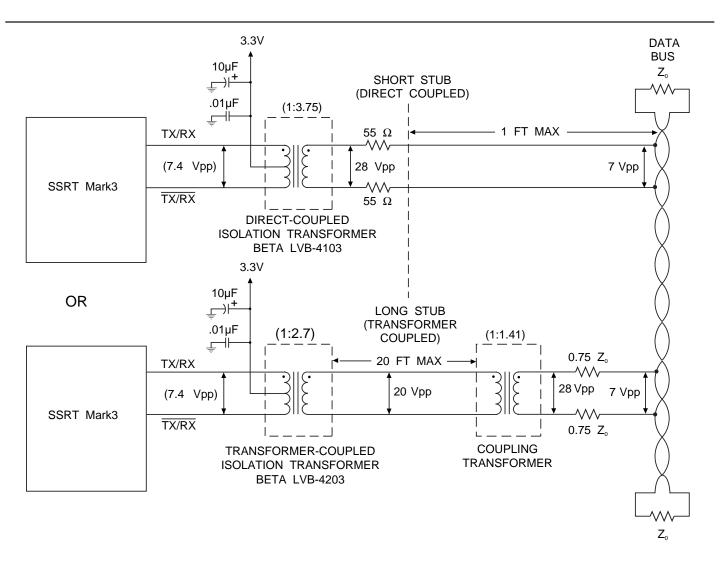

- Notes 1 through 6 are applicable to the Receiver Differential Resistance and Differential Capacitance Specifications:

- (1) Specifications include both transmitter and receiver (tied together internally).

- (2) Impedance parameters are specified directly between pins TX/RX A(B) and TX/RX A(B) of the SSRT Mark3 hybrid.

- (3) It is assumed that all power and ground inputs to the hybrid are connected.

- (4) The specifications are applicable for both unpowered and powered conditions.

- (5) The specifications assume a 2 volt rms balanced, differential, sinusoidal input. The applicable frequency range is 75 kHz to 1 MHz.

- (6) Minimum resistance and maximum capacitance parameters are guaranteed over the operating range, but are not tested.

- (7) Assumes a common mode voltage within the frequency range of dc to 2 MHz, applied to the pins of the isolation transformer on the stub side (either direct or transformer coupled), and referenced to hybrid

Data Device Corporation www.ddc-web.com

ground. Transformer must be a DDC recommended transformer or other transformer that provides an equivalent minimum CMRR.

- (8) An "X" in one or more of the product type fields indicates that the reference is applicable to all available product options.

- (9) MIL-STD-1760 requires a 20 Vp-p minimum output on the stub connection.

- (10) External 10  $\mu$ F tantalum and 0.1  $\mu$ F capacitors to ground should be located as close as possible to +3.3 Vdc input pins.

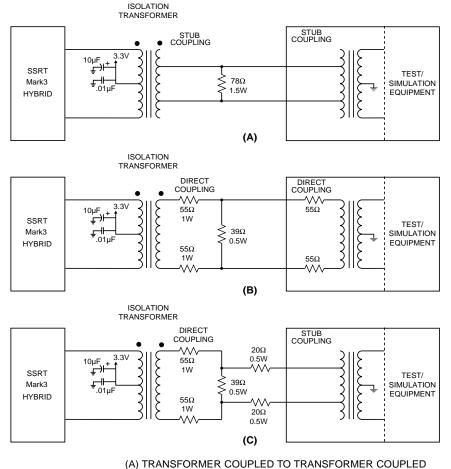

- (11) Power dissipation specifications assume a transformer coupled configuration, with external dissipation (while transmitting) of 0.14 watts for the active isolation transformer, 0.08 watts for the active bus coupling transformer, 0.45 watts for each of the two bus isolation resistors, and 0.15 watts for each of the two bus termination resistors.

- (12) Measured from mid-parity crossing of command word to mid-sync crossing of RT's status word.

- (13) Out is measured to bottom of ceramic case.

- (14) Current drain and power dissipation specs are preliminary and subject to change.

## INTRODUCTION

#### GENERAL

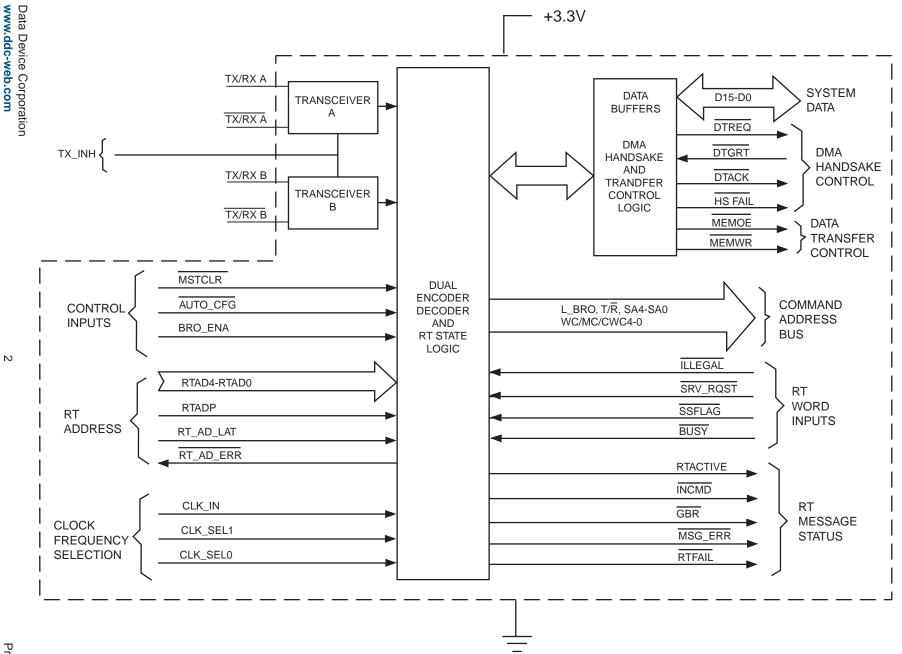

The BU-64703 Simple System RT Mark3 (SSRT Mark3) is a complete MIL-STD-1553 Remote Terminal (RT) bus interface unit. Contained in this hybrid are a dual transceiver and Manchester II encoder/decoder, and MIL-STD-1553 Remote Terminal (RT) protocol logic. Also included are built-in self-test capability and a parallel subsystem interface. The subsystem interface includes a 12-bit address bus and a 16-bit data bus that operates in a 16-bit DMA handshake transfer configuration. The local bus and associated control signals are optimized for +3.3 volt logic but are +5 volt tolerant.

The transceiver front end of the SSRT Mark3 is implemented by means of low-power monolithic technology. The transceiver requires only a single +3.3 V voltage source. The voltage source transmitters provide superior line driving capability for long cables and heavy amounts of bus loading. In addition, the monolithic transceivers can provide a minimum stub voltage level of 20 volts peak-to-peak transformer coupled, making the SSRT Mark3 suitable for MIL-STD-1760 applications. To provide compatability to McAir specs, the SSRT Mark3 is available with an option for transmitters with increased rise and fall times.

Besides eliminating the demand for an additional power supply, the use of a +3.3V only transceiver requires the use of a step-up, rather than a step-down, isolation transformer. This provides the advantage of a higher terminal input impedance than is possible for a 15V, 12V or 5V transmitter. As a result, there is a greater margin for the input impedance test, mandated for the 1553 validation test. This allows for longer cable lengths between a system connector and the isolation transformers of an embedded 1553 terminal.

The receiver sections of the SSRT Mark3 are fully compliant with MIL-STD-1553B in terms of front-end overvoltage protection, threshold, and bit-error rate.

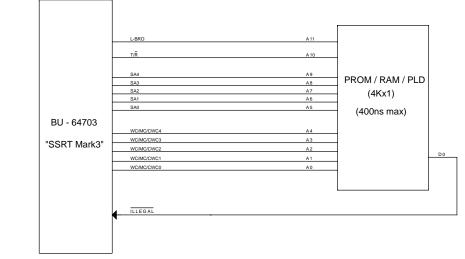

The SSRT Mark3 implements all MIL-STD-1553 message formats, including all 13 MIL-STD 1553 dual redundant mode codes. Any subset of the possible 1553 commands (broadcast, T/R bit, subaddress, word count/mode code) may be optionally illegalized by means of an external PROM, PLD, or RAM. An extensive amount of message validation is performed for each message received. Each word received is validated for correct sync type and sync encoding, Manchester II encoding, parity, and bit count. All messages are verified to contain a legal, defined command word and correct word count. If the SSRT Mark3 is the receiving RT in an RT-to-RT transfer, it verifies that the T/R bit of the transmit command word is logic "1" and that the transmitting RT responds in time and contains the correct RT address in its Status Word.

The SSRT Mark3 may be operated from a 10, 12, 16, or 20 MHz clock input. For any clock frequency, the decoder samples incoming data on **both** edges of the clock input. This oversampling, in effect, provides for a sampling rate of twice the input clocks' frequency. Benefits of the higher sampling rate include a wider tolerance for zero-crossing distortion and improved bit error rate performance.

The SSRT Mark3 includes a hardwired RT address input. This includes 5 address lines, an address parity input, and an address parity error output. The RT address can also be latched by means of a latching input signal.

The SSRT Mark3 supports command illegalization. Commands may be illegalized by asserting the input signal ILLEGAL active low within approximately 2  $\mu$ s after the mid-parity bit zero-crossing of the received command word. Command words may be illegalized as a function of broadcast, T/R bit, subaddress, word count, and/or mode code.

An internal Built-in-Test (BIT) Word register is updated at the end of each message. The contents of the BIT Word Register are transmitted in response to a Transmit BIT Word Mode Command. The SSRT Mark3 provides a number of real-time output signals. These various signals provide indications of message in progress, valid received message, message error, handshake fail, loop-test fail or transmitter timeout.

The SSRT Mark3 includes standard DMA handshake signals (Request, Grant, and Acknowledge) as well as transfer control outputs (MEMOE and MEMWR). The DMA interface operates in a 16-bit mode, supporting word-wide transfers.

The SSRT Mark3's system interface allows the SSRT Mark3 to be interfaced directly to a simple system that doesn't include a microprocessor. This provides a low-cost 1553 interface for A/D and D/A converters, switch closures, actuators, and other discrete I/O signals.

The SSRT Mark3 has an internal FIFO for received data words. This 32-word deep FIFO may be used to allow the SSRT Mark3 to transfer its data words to the local system in burst mode. Burst mode utilizes the FIFO by transferring data to the local bus at a rate of one data word every three clock cycles. Burst mode negotiates only once for use of the subsystem bus. Negotiation is performed only after all 1553 data words have been received and validated. In non-burst mode, the SSRT Mark3 will negotiate for the local bus after every received data word. The data word transfer period is three clock cycles for each received 1553 data word.

The SSRT Mark3 may also be used in a shared RAM interface configuration. By means of tri-state buffers and a small amount of "glue" logic, the SSRT Mark3 will store Command Words and access Data Words to/from dedicated "mailbox" areas in a shared RAM for each broadcast / T/R bit / subaddress / mode code.

#### ADDRESS MAPPING

A typical addressing scheme for the SSRT Mark3 12-bit address bus could be as follows:

- A11: BROADCAST/OWNADDRESS

- A10: TRANSMIT/RECEIVE

- A9-A5: SUBADDRESS 4-0

- A4-A0: WORD COUNT/MODE CODE 4-0

This method of address mapping provides for a "mailbox" allocation scheme for the storage of data words. The 12 address outputs may be used to map into 4K words of processor address space. The SSRT Mark3's addressing scheme maps messages in terms of broadcast/ownaddress, transmit/receive, subaddress, and word/count mode code. A 32-word message block is allocated for each T/R-subaddress.

For non-mode code messages, the Data Words to be transmitted or received are accessed from (to) relative locations 0 through 31 within the respective message block. For the MIL-STD-1553B Synchronize with data, Selected transmitter shutdown, Override selected transmitter shutdown, and Transmit vector word mode commands which involve a single data word transfer, the address for the data word is offset from location 0 of the message block for subaddresses 0 and 31 by the value of the mode code field of the received command word.

The data words transmitted in response to the Transmit last command or Transmit BIT word mode commands are accessed from a pair of internal registers.

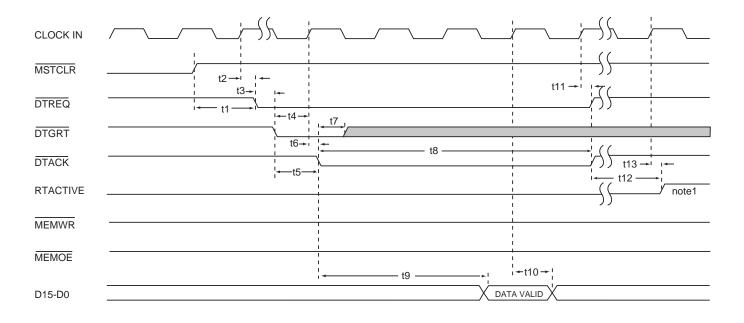

#### DMA INTERFACE

A 16-bit data bus, a 12-bit address bus, and six control signals are provided to facilitate communication with the parallel subsystem. The data bus D15-D0 consists of bi-directional tri-state signals. The address bus L\_BRO, T/ $\overline{R}$ , SA4-SA0, and WC/MC/CWC4-0; along with the data transfer control signals  $\overline{MEMOE}$  and  $\overline{MEMWR}$  are two-state output signals.

The control signals include the standard DMA handshake signals DTREQ, DTGRT, DTACK, as well as the transfer control outputs MEMOE and MEMWR. HS\_FAIL provides an indication to the subsystem of a handshake failure condition.

Data transfers between the subsystem and the SSRT Mark3 are performed by means of a DMA handshake, initiated by the SSRT Mark3. A data read operation is defined to be the transfer of data from the subsystem to the SSRT Mark3. Conversely, a data write operation transfers data from the SSRT Mark3 to the subsystem. Data is transferred as a single 16-bit word.

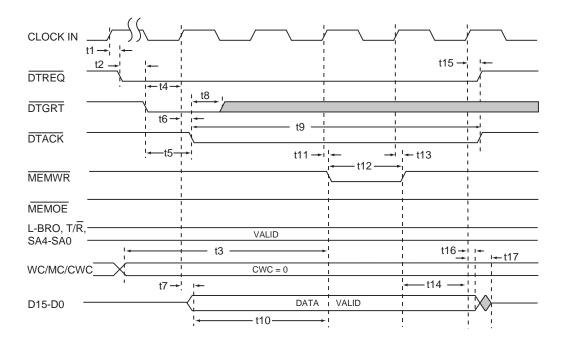

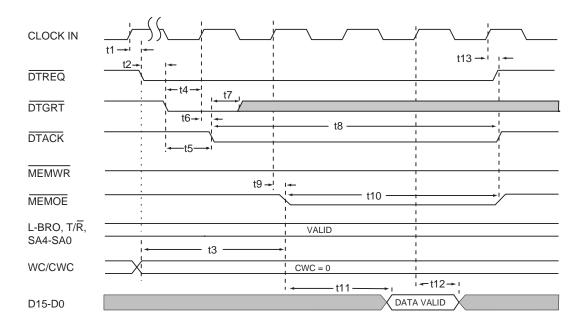

## DMA READ OPERATION

In response to a transmit command, the SSRT Mark3 needs to read data words from the external subsystem. To initiate a data word read transfer, the SSRT Mark3 asserts the signal  $\overline{\text{DTREQ}}$  low. Assuming that the subsystem asserts  $\overline{\text{DTGRT}}$  in time, the SSRT Mark3 will then assert the appropriate values of L\_BRO (logic "0"),  $T/\overline{\text{R}}$  (high), SA4-0, and MC/CWC4-0; MEMWR high, along with  $\overline{\text{DTACK}}$  low and  $\overline{\text{MEMOE}}$  low to enable data to be read from the subsystem.

After the transfer of each Data Word has been completed, the value of the address bus outputs CWC4 through CWC0 is incremented.

## DMA WRITE OPERATION

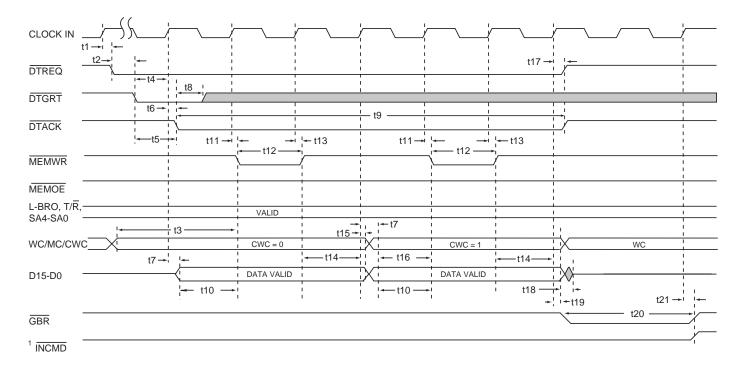

In response to a receive command, the SSRT Mark3 will need to transfer data to the subsystem. There are two options for doing

this, the burst mode and the non-burst mode. In burst mode, all received data words are transferred from the SSRT Mark3 to the subsystem in a contiguous burst, only following the reception of the correct number of valid data words. In the non-burst mode, single data words are written to the external subsystem immediately following the reception of each individual data word.

To initiate a DMA write cycle, the SSRT Mark3 asserts  $\overline{\text{DTREQ}}$  low. The subsystem must then respond with  $\overline{\text{DTGRT}}$  low. Assuming that  $\overline{\text{DTGRT}}$  was asserted in time, the SSRT Mark3 will then assert  $\overline{\text{DTACK}}$  low. The SSRT Mark3 will then assert the appropriate value of L\_BRO, T/R, SA4-0, and MC/CWC4-0, MEMOE high, and MEMWR low. MEMWR will be asserted low for one clock cycle. The subsystem may then use either the falling or rising edge of MEMWR to latch the data. Similar to the DMA read operation, the address outputs CWC4 through CWC0 are incremented after the completion of a DMA write operation.

#### HANDSHAKE FAIL

Following the assertion of  $\overline{\text{DTREQ}}$  low by the SSRT Mark3, the external subsystem has 10  $\mu s$  to respond by asserting  $\overline{\text{DTACK}}$  to logic "0".

If the SSRT Mark3 (SSRT Mark3) asserts DTREQ and the subsystem does not respond with DTGRT in time for the SSRT Mark3 to complete a data word transfer, the HSFAIL output will be asserted low to inform the subsystem of the handshake failure, and bit 12 in the internal Built-In-Test (BIT) word will be set to logic "1". If the handshake failure occurs on a data word read transfer (for a transmit command), the SSRT Mark3 will abort the current message transmission. In the case of a handshake failure on a write transfer (received command) the SSRT Mark3 will set the handshake failure output and BIT word bit, and abort processing the current message.

#### MESSAGE PROCESSING OPERATION

Following the receipt and transfer of a valid Command Word, the SSRT Mark3 will attempt to perform one of the following operations: (1) transfer received 1553 data to the subsystem, (2) read data from the subsystem for transmission on the 1553 bus, (3) transmit status (and possibly the last command word or RT BIT word) on the 1553 bus, and/or (4) set status word conditions.

The SSRT Mark3 responds to all non-broadcast messages to its RT address with a 1553 Status Word.

#### **RT ADDRESS**

RT Address 4-0 (RT\_AD\_4 = MSB) and RT Address Parity (RT\_AD\_P) should be programmed for a unique RT address and reflect an odd parity sum. The SSRT Mark3 will not respond to any MIL-STD-1553 commands or transfer received data from any non-broadcast messages if an odd parity sum is not presented by RT\_AD\_4-0 and RT\_AD\_P. An address parity error will be indicated by a low output on the RT\_AD\_ERR pin. The input signal RT\_AD\_LAT operates a transparent latch for RTAD4-RTAD0 and RTADP. If RT\_AD\_LAT is low, the output of the latch tracks the value presented on the input pins. If RT\_AD\_LAT is high, the output of the internal latch becomes latched to the values presented at the time of a low-to-high transition of RT\_AD\_LAT.

RT address and RT Address Parity must be presented valid before the mid-parity crossing of the 1553 command and held, at least, until following the first received data word.

#### COMMAND ILLEGALIZATION

The SSRT Mark3 includes a provision for command illegalization. If a command is illegalized, the SSRT Mark3 will set the Message error bit and transmit its status word to the Bus Controller. No data words will be transmitted in response to an illegalized transmit command. However, data words associated with an illegalized receive command **will** be written to the external subsystem (although these transfers may be blocked using external logic).

ILLEGAL is sampled approximately 2  $\mu$ s following the mid-parity bit zero crossing of the received command word. A low on ILLE-GAL will illegalize a particular command word and cause the SSRT Mark3 to respond with its Message error bit set in its status word. Command illegalization based on broadcast, T/R bit, subaddress, and/or word count/mode code may be implemented by means of an external PROM, PLD, or RAM device, as shown in Figure 2.

The external device may be used to define the legality of specific commands. Any subset of the possible 1553 commands may be illegalized as a function of broadcast,  $T/\overline{R}$  bit, subaddress, word count, and/or mode code. The output of the illegalization device should be tied directly to the SSRT Mark3's ILLEGAL signal input. The maximum access time of the external illegalizing device is 400 ns.

If illegalization is not used, ILLEGAL should be hardwired to logic "1".

#### BUSY

The external subsystem may control the SSRT Mark3's Busy RT status word bit by means of the BUSY input signal. The SSRT

Mark3 samples  $\overline{\text{BUSY}}$  approximately 2 µs following the mid-parity bit zero crossing of the received Command Word. If  $\overline{\text{BUSY}}$  is sampled low for a particular message, the value of the busy bit transmitted in the SSRT Mark3's status word will be logic "1". If  $\overline{\text{BUSY}}$  is sampled high for a particular message, the value of the busy bit transmitted in the SSRT Mark3's status word will be logic "0".

If the RT responds to a transmit command with a busy bit of logic "1", the status word will be transmitted, but no data words will be transmitted by the SSRT Mark3. If the SSRT Mark3 responds to a receive command with a busy bit of logic "1", data words **will be** transferred to the external subsystem (although these may be blocked by means of external logic).

Similar to ILLEGAL, it is possible to cause the SSRT Mark3 to respond with Busy for specific command words (only), by means of an external PROM, RAM, or PLD device.

## TRANSMIT COMMAND (RT-TO-BC TRANSFER)

If the SSRT Mark3 receives a valid Transmit command word that the subsystem determines is legal (input signal ILLEGAL is high) and the subsystem is not BUSY (input signal BUSY is high), the SSRT Mark3 will initiate a transmit data response following transmission of its status word. This entails a handshake/read cycle for each data word transmitted, with the number of data words to be transmitted specified by the word count field of the transmit command word.

If ILLEGAL is sampled low, the Message Error bit will be set in the SSRT Mark3's status word. No data words will be transmitted following transmission of the status word to an illegalized transmit command. A low on the BUSY input will set the busy bit in the Status Word; in this instance, only the status word will be transmitted, with no data words.

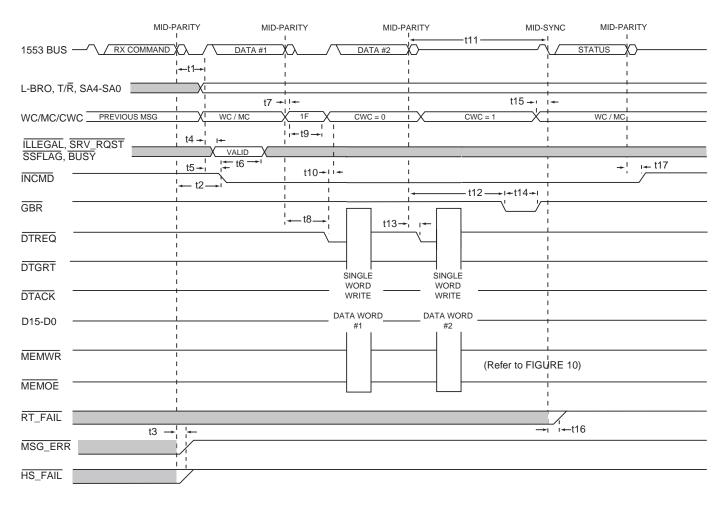

## RECEIVE COMMAND (BC-TO-RT TRANSFER)

In non-burst mode, a DMA handshake will be initiated for each data word received from the 1553 data bus. If successful, the

## FIGURE 2. SSRT Mark3 ILLEGALIZATION

respective handshake will be followed by a corresponding write cycle. A handshake timeout will not terminate transfer attempts for the remaining data words, error flagging or Status Word transmission. After the reception of a valid non-mode code receive Command Word followed by the correct number of valid Data Words and assuming that all words are successfully transferred to the subsystem, a negative pulse will be asserted on the Good Block Received (GBR) output. The width of this pulse is two clock cycles.

In burst mode, a DMA handshake will not be initiated until after **all** data words have been received over the 1553 data bus and stored into the SSRT Mark3's internal FIFO. After the handshake has been negotiated, the SSRT Mark3 will burst the contents of the FIFO to the local bus (D0-D15). After the reception of a valid non-mode code receive command word followed by the correct number of valid data words and assuming that all words are successfully transferred to the subsystem, a negative pulse will be asserted on the output Good Block Received (GBR). The width of this pulse is two clock cycles.

#### **RT-TO-RT TRANSFER ERRORS**

For the case where the SSRT Mark3 is the receiving RT of an RT-to-RT transfer, if the transmitting RT does not respond within the specified time period, the SSRT Mark3 will determine that a timeout condition has occurred. The value of the SSRT Mark3's RT-to-RT timeout timer is in the range from 17.5 to 18.5 µs, and is specified from the mid-parity bit crossing of the transmit command word to the mid-sync crossing of the transmitting RT's status word. In the case of an RT-to-RT timeout, the SSRT Mark3 will not respond and the RT-to-RT NO TRANSFER TIMEOUT bit (bit 2) of the SSRT Mark3's BIT Word will be set to logic "1".

Also, if the SSRT Mark3 is the receiving RT for an RT-to-RT transfer, and the  $T/\overline{R}$  bit of the second command word is logic "0", **or** the RT address field for the transmit command is the same as for the receive command, or the subaddress for the transmit command is 00000 or 11111, the SSRT Mark3 will not respond, and will set the RT-to-RT SECOND COMMAND ERROR bit (bit 1) of the RT BIT word to logic "1".

# RT STATUS, ERROR HANDLING, AND MESSAGE TIMING SIGNALS

Message transfers and transfer errors are indicated by means of the INCMD, HS\_FAIL, MSG\_ERR, and RTFAIL error indication outputs. Additional error detection and indication mechanisms include updating of the internal command, RT status and BIT word registers.

The SSRT Mark3 provides a number of timing signals during the processing of 1553 messages. INCMD is asserted low when a new command is received. At the end of a message (either valid or invalid), INCMD transitions from low to high.

As discussed above,  $\overline{\text{HS}_{FAIL}}$  will be asserted low if the subsystem fails to respond to  $\overline{\text{DTREQ}}$  within the maximum amount of time (10 µs).

Following the last data word transfer for a valid non-mode code receive message (for either non-burst mode or burst mode), GBR will be asserted low for two clock cycles.

MSG\_ERR is asserted as a low output level following any detected error in a received message, except for an error in the command word. If an error is detected in a received command word, the rest of the message will be ignored.

If MSG\_ERR and/or HS\_FAIL have been asserted (low), they will be cleared to logic "1" following receipt of a subsequent valid command word.

## LOOPBACK TEST

The SSRT Mark3 performs a loopback self-test at the end of each non-broadcast message processed. The loopback test consists of the following verifications: (1) The received version of every transmitted word is verified for validity (encoding, bit count, parity) and correct sync type; and (2) The received version of the last transmitted word is verified by means of a bit-by-bit comparison to the transmitted version of this word. If there is a transmitter timeout (660.5  $\mu$ s) and/or if the loopback test fails for one or more transmitted words, the Terminal flag status word bit will be set in response to the next non-broadcast message.

Note that the setting of the Terminal flag status bit following a loop test failure may be disabled by means of the Auto-Config feature; i.e., by setting Auto-Config bit 4 to logic "0".

## STATUS WORD

The Broadcast Command Received bit is formulated internally by the SSRT Mark3. The Message Error Status bit will be set if the current command is a Transmit Status Word or Transmit Last Command mode command if there was an error in the data portion of the previous receive message. Message Error will also be set if ILLEGAL has been sampled low by the SSRT Mark3 for the current message. ILLEGAL, SRV\_RQST, BUSY, and SSFLAG (Subsystem Flag) will be sampled from their respective Status input pins approximately 2  $\mu$ s following the mid-parity bit zero crossing of the received Command Word. This time is 400 ns maximum following after the L\_BRO, T/R, SA4-0, and WC/MC/CWC4-0 outputs have been presented valid.

## PROTOCOL SELF-TEST

The SSRT Mark3 includes a comprehensive, autonomous offline self-test of its internal protocol logic. The test includes a comprehensive test of all registers, Manchester encoder and decoders, transmitter failsafe timer, protocol logic, and the internal FIFO.

This test is completed in approximately 32,000 clock cycles. That is, about 1.6 ms with a 20 MHz clock, 2.0 ms at 16 MHz, 2.7 ms at 12 MHz, and 3.2 ms at 10 MHz. While the SSRT Mark3 is performing its off-line self-test, it will ignore (and therefore not respond to) all messages received from the 1553 bus.

Unless disabled by means of the SSRT Mark3's Auto-Config feature, the protocol self-test will be performed following the SSRT Mark3's power turn-on (i.e., when MSTCLR is released high). If the Auto-Config feature is used and Auto-Config bit 5 is set to logic "0", then a failure of the protocol self-test following power turn-on will result in the SSRT Mark3 not going online. If bit 5 is set to logic "0" and the protocol self-test passes following power turn-on, the SSRT Mark3 will go online.

The protocol self-test will also be performed following receipt of an Initiate self-test mode command from the 1553 bus. If an Initiate self-test mode command is received by the SSRT Mark3, and Auto-Config bit 5 is set to logic "0", then a failure of the protocol self-test following will result in the SSRT Mark3 going offline.

If the protocol self-test fails: (1) the Terminal Flag bit will be set to logic "1" in the SSRT Mark3 status word; (2) bit 8 in the SSRT Mark3's BIT word, BIT Test Fail, will be set to logic "1"; (3) the SSRT Mark3's RTFAIL output will be asserted to logic "0".

## AUTO-CONFIGURATION

The SSRT Mark3 includes an auto-configuration feature, which allows various optional features to be enabled or disabled. Auto-configuration may be enabled or disabled by means of the input signal AUTO\_CFG. If AUTO\_CFG is connected to logic "1", then the auto-configure option is disabled, and the six configuration parameters revert to their default values.

Note that the default condition for each configuration parameter is <u>enabled</u> (for the MIL-STD-1553A/B protocol selection, -1553B is the default).

If AUTO\_CFG is connected to logic "0", then the configuration parameters are transferred over D5-D0 by means of a DMA read data transfer. The transfer occurs during the time that the RTACTIVE **and** DTACK outputs are logic "0", following MSTCLR transitioning from logic "0" to logic "1" and a successful DT\_REQ-to-DTGRT handshake.

Note that if DTGRT is hardwired to logic "0", the handshake process is not necessary (i.e., DTACK and RTACTIVE will both be asserted to logic "0" one clock cycle following DT\_REQ).

Each of the configuration parameters is **enabled** if the SSRT Mark3 reads a value of logic "1" for the respective data bit.

The auto-configuration parameters are defined by TABLE 2.

The timing signals pertaining to Auto-Configuration mode are illustrated in Figure 12.

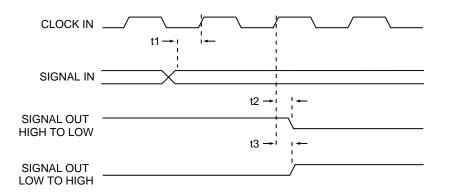

#### **CLOCK INPUT**

The SSRT Mark3 may be operated from one of four clock frequencies: 10, 12, 16, or 20 MHz. The selected clock frequency must be designated by means of the input signals CLK\_SEL\_1 and CLK\_SEL\_0, as shown in TABLE 3.

| T/  | ABLE 2. AUTO-CO                                          | NFIGURATION PARAMETERS                                                                                                                                                                                                                                                                                                                                         |

|-----|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT | FUNCTION                                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                    |

| 5   | RT GOES ONLINE IF<br>SELF-TEST FAILS                     | If logic "0", the RT will become enabled<br>only if the self-test passes. If auto-config<br>is not used, or if this bit is logic "1", or if<br>the power-up self-test passes, then the<br>RT will go online following self-test.                                                                                                                               |

| 4   | RTFAIL-to-TERMINAL<br>FLAG AUTO-WRAP                     | If the loop test fails for a particular mes-<br>sage, the Terminal flag bit will be set in<br>the SSRT Mark3's status response for<br>the subsequent non-broadcast message.                                                                                                                                                                                    |

| 3   | MIL-STD-1553A/B<br>(-B is logic "1", or the<br>default). | In MIL-STD-1553B mode, subaddress<br>31 is a mode code subaddress, and<br>mode codes are implemented in full<br>accordance with MIL-STD-1553B. In<br>MIL-STD-1553A mode, subaddress 31<br>is a non-mode code subaddress, and no<br>data words are transmitted or anticipat-<br>ed to be received for mode code mes-<br>sages.                                  |

| 2   | SUBADDRESS 30<br>WRAPAROUND                              | Subaddress 30 wraparound is enabled.<br>That is, the data words for a receive<br>message to subaddress 30 are stored in<br>the internal FIFO, and not transferred to<br>the external system. For a subsequent<br>transmit message to subaddress 30, the<br>transmitted data words are read from<br>the internal FIFO, rather than from the<br>external system. |

| 1   | BURST MODE                                               | Enables burst mode (using the internal<br>FIFO) for received data words. In burst<br>mode, for a receive message, all data<br>words are transferred to the external<br>system in a contiguous burst following<br>reception of the last data word.                                                                                                              |

| 0   | POWER-UP SELF-<br>TEST ENABLE                            | If enabled, the SSRT Mark3 will perform self-test following the rising edge of MSTCLR.                                                                                                                                                                                                                                                                         |

| TABLE 3. CLOCK FREQUENCY SELECTION |                                     |        |  |  |  |  |

|------------------------------------|-------------------------------------|--------|--|--|--|--|

| CLK_SEL_1                          | CLK_SEL_1 CLK_SEL_0 CLOCK FREQUENCY |        |  |  |  |  |

| 0                                  | 0                                   | 10 MHz |  |  |  |  |

| 0                                  | 1                                   | 20 MHz |  |  |  |  |

| 1                                  | 0                                   | 12 MHz |  |  |  |  |

| 1                                  | 1                                   | 16 MHz |  |  |  |  |

| MID-P                             | PARITY MID-PARITY MID-PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | D-PARITY            |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1553 BUS — ( <u>RX COMMAND</u> )  | A A DATA #1 X A DATA #2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |