SDNS001B - SEPTEMBER 1992 - REVISED DECEMBER 1994

- Recovers a 155.52-MHz Clock Signal From a 155.52-Mbit/s STS-3/STM-1 NRZ Data Stream

- Accepts Pseudo-ECL (PECL) Input Voltage Levels on the Input Data Stream

- Provides a Separate Pseudo-ECL-to-True-ECL Converter for an Additional Data Signal Requiring Conversion

- Requires a Single 5-V Supply

# description

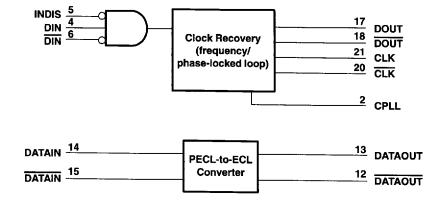

The TNETA1555 device recovers an embedded clock signal from a 155.52-Mbit/s STS-3/STM-1 nonreturn-to-zero (NRZ) data stream using a frequency/phase-locked loop. The device accepts

**DW PACKAGE** (TOP VIEW) 24 TEST1 Vcc[ **CPLL**[ 23 TEST2 GNDF 22 VCC DIN 21 T CLK 20 CLK INDISE DIN 19 GND 18 DOUT Vcc[ GND[ 17 DOUT TESTOUT 16 V<sub>CC</sub> GND[] 10 15 DATAIN 14 DATAIN V<sub>CC</sub>[] 11 DATAOUT 13 DATAOUT

PECL (ECL signals referenced to 5 V instead of GND) input-voltage levels. The recovered clock and dat outputs are PECL compatible. The serial data input and recovered clock and data outputs are differential to provide maximum noise immunity.

The input disable (INDIS) disconnects the incoming serial data stream from the clock-recovery circuitry. When the INDIS input is high, the data output is forced low and the clock-recovery circuitry maintains the output frequency present at the time the input was disabled for a specific amount of time. This time is dependent upon the value of the capacitor in the loop filter.

A PECL-to-ECL converter is included in the device for those applications where an interface between the two different voltage levels is required. An example of such an application is an optical transmitter that requires ECL input voltage levels and a parallel-to-serial converter with pseudo-ECL-level outputs.

The TNETA1555 requires only a positive 5-V supply (5 V  $\pm$  5 %) for operation. The device is characterized for operation over a temperature range of  $-40^{\circ}$ C to 85°C.

#### functional block diagram

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1994, Texas Instruments Incorporated

SDNS001B - SEPTEMBER 1992 - REVISED DECEMBER 1994

## **Terminal Functions**

| TERMIN           | AL               | ΙO | DESCRIPTION                                                                                                                        |

|------------------|------------------|----|------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | NO.              | "  | DESCRIPTION                                                                                                                        |

| CLK, CLK         | 20, 21           | 0  | Recovered clock output. PECL compatible.                                                                                           |

| CPLL             | 2                | ı  | Capacitor connection for phase-locked-loop filter (CpLL = 0.1 µF recommended)                                                      |

| DATAIN, DATAIN,  | 14, 15           | ı  | PECL-compatible input for PECL-to-ECL converter                                                                                    |

| DATAOUT, DATAOUT | 12, 13           | 0  | ECL-compatible output for PECL converter                                                                                           |

| DIN, DIN         | 4, 6             | ı  | Serial data input. PECL compatible.                                                                                                |

| DOUT, DOUT       | 18, 17           | 0  | Serial data output. PECL compatible.                                                                                               |

| GND              | 3, 8, 10, 19     |    | Ground (0-V reference)                                                                                                             |

| INDIS            | 5                | ı  | Input disable terminal (TTL compatible). The device ignores the input data when INDIS is active and forces DOUT low and DOUT high. |

| TESTOUT          | 9                | 0  | Manufacturing test output. Leave open.                                                                                             |

| TEST2            | 23               | I  | Manufacturing test input. Tied to GND.                                                                                             |

| TEST1            | 24               | ı  | Manufacturing test input. Tied to GND.                                                                                             |

| Vcc              | 1, 7, 11, 16, 22 |    | Supply voltage                                                                                                                     |

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)   | 0.5 V to 7 V    |

|------------------------------------------------------|-----------------|

| Input voltage range, TTL                             | $-1.2$ V to 7 V |

| Input voltage range, ECL                             | $-5.5$ V to 0 V |

| Input voltage range, pseudo-ECL                      |                 |

| Operating free-air temperature range, T <sub>A</sub> | 40 C to 85°C    |

| Storage temperature range, T <sub>stq</sub>          | 65 C to 150°C   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## recommended operating conditions

|          |                                             | MIN                  | NOM | MAX                  | UNIT |

|----------|---------------------------------------------|----------------------|-----|----------------------|------|

| Vcc      | Supply voltage                              | 4.75                 | 5   | 5.25                 | ٧    |

| VIH      | High-level input voltage, TTL               | 2                    |     |                      | ٧    |

| $V_{IL}$ | Low-level input voltage, TTL                |                      |     | 0.8                  | ٧    |

| lικ      | Input clamp current, TTL                    |                      |     | -18                  | mA   |

| ViH      | High-level input voltage, PECL (see Note 2) | V <sub>CC</sub> -1.1 |     | V <sub>CC</sub> -0.8 | >    |

| VIL      | Low-level input voltage, PECL (see Note 2)  | V <sub>CC</sub> -1.9 |     | V <sub>CC</sub> -1.5 | ٧    |

| TA       | Operating free-air temperature              | -40                  |     | 85                   | °C   |

NOTE 2: The algebraic convention, in which the least positive (most negative) value is designated minimum, is used in this data sheet for logic-level voltages only.

NOTE 1: All voltage values are with respect to the GND terminals.

SDNS001B - SEPTEMBER 1992 - REVISED DECEMBER 1994

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted) (see Figure 1)

| !   | PARAME                   |                             | TEST CON                                  | DITIONS                                 | MIN                   | TYP | MAX                   | UNIT |

|-----|--------------------------|-----------------------------|-------------------------------------------|-----------------------------------------|-----------------------|-----|-----------------------|------|

| Vон | High-level               | DOUT, DOUT,<br>CLK, CLK     | V <sub>CC</sub> = 4.75 V to 5.25 V,       | See Notes 2 and 3                       | V <sub>CC</sub> -1.03 |     | V <sub>CC</sub> -0.85 |      |

| ₹OH | output voltage           | DATAOUT,<br>DATAOUT         | V <sub>CC</sub> = 4.75 V,                 | See Notes 2 and 4                       | -1.02                 |     | -0.75                 | V    |

| VOL | DOUT, DOUT, CLK, CLK     |                             | V <sub>CC</sub> = 4.75 V to 5.25 V,       | See Notes 2 and 3                       | V <sub>CC</sub> -1.85 |     | V <sub>CC</sub> -1.62 |      |

| VOL | output voltage           | DATAOUT,<br>DATAOUT         | V <sub>CC</sub> = 4.75 V,                 | See Notes 2 and 4                       | -1.81                 |     | -1.58                 | ٧    |

| VIK | Input clamp<br>voltage   | INDIS                       | V <sub>CC</sub> = 4.75 V,                 | I <sub>I</sub> = -18 mA                 |                       |     | -1.2                  | V    |

| lį  | Input current            | INDIS                       | V <sub>CC</sub> = 5.25 V,                 | V <sub>I</sub> = V <sub>CC</sub> or GND |                       |     | ±1                    | μA   |

| ۱н  | High-level input current | DIN, DIN,<br>DATAIN, DATAIN | V <sub>CC</sub> = 5.25 V,                 | V <sub>I</sub> = 4.45 V                 |                       |     | 50                    | μА   |

| կլ  | Low-level input current  | DIN, DIN,<br>DATAIN, DATAIN | V <sub>CC</sub> = 5.25 V,                 | V <sub>I</sub> = 3.35 V                 |                       |     | 50                    | μА   |

| lcc | Supply current           |                             | V <sub>CC</sub> = 5.25 V,<br>Outputs open | f <sub>i</sub> = 155.52 Mbit/s,         |                       | 71  | 100                   | mA   |

|     | - Josephy Junion         |                             | V <sub>CC</sub> = 5.25 V,<br>See Note 5   | $f_i = 155.52 \text{ Mbit/s},$          |                       | 112 | 150                   | mA   |

NOTES: 2. The algebraic convention, in which the least positive (most negative) value is designated minimum, is used in this data sheet for logic-level voltages only.

3. These outputs are terminated through a 50- $\Omega$  resistor to V<sub>CC</sub> –2 V.

4. These outputs are terminated through a 50- $\Omega$  resistor to -2 V.

5. DOUT, DOUT, CLK, and CLK are each terminated with a 50-Ω resistor to V<sub>CC</sub> -2 V. DATAOUT and DATAOUT are each terminated with a 50- $\Omega$  resistor to -2 V.

# operating characteristics over recommended operating free-air temperature range (unless otherwise noted) (see Figure 1)

| TEST         | MIN                                           | TYP                                                             | MAX                                                                                                                            | UNIT                                                                                                                  |                                                                                                                                                                       |

|--------------|-----------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| See Note 6   | C <sub>PLL</sub> = 330 pF                     | 1                                                               |                                                                                                                                |                                                                                                                       |                                                                                                                                                                       |

| See Note 6   | C <sub>PLL</sub> = 0.1 μF                     | 3                                                               | 3                                                                                                                              | _                                                                                                                     | ms                                                                                                                                                                    |

| See Figure 1 |                                               | -800                                                            |                                                                                                                                | 800                                                                                                                   | ps                                                                                                                                                                    |

| See Note 7   |                                               |                                                                 | 1.5°                                                                                                                           | 4°                                                                                                                    | °RMS                                                                                                                                                                  |

|              |                                               |                                                                 | 155.52                                                                                                                         |                                                                                                                       | Mb/s                                                                                                                                                                  |

| See Note 3   |                                               | 45%                                                             |                                                                                                                                | 55%                                                                                                                   |                                                                                                                                                                       |

| See Note 8   |                                               | 100                                                             | 450                                                                                                                            |                                                                                                                       |                                                                                                                                                                       |

|              | See Note 6 See Figure 1 See Note 7 See Note 3 | See Note 6  CPLL = 0.1 µF  See Figure 1  See Note 7  See Note 3 | CPLL = 330 pF         CPLL = 0.1 μF         See Figure 1       -800         See Note 7       -800         See Note 3       45% | See Note 6 $C_{PLL} = 330 \text{ pF}$ 1       Ce Figure 1     -800       See Note 7     1.5°       See Note 3     45% | See Note 6 $\frac{\text{CpLL}}{\text{CpLL}} = 330  \text{pF}$ 1       See Figure 1     -800     800       See Note 7     1.5°     4°       See Note 3     45%     55% |

NOTES: 3. These outputs are terminated through a 50- $\Omega$  resistor to V<sub>CC</sub> -2 V.

6. Acquisition time is the time required to achieve a valid clock output while applying a 2<sup>7</sup> – 1 pseudo-random bit sequence.

7. RMS jitter is measured with a 2<sup>31</sup> – 1 pseudo-random bit sequence.

8. This measurement is made with a 2<sup>13</sup> -1 pseudo-random bit sequence with string substitution.

# switching characteristics over recommended operating free-air temperature range, $V_{CC}$ = 5 V $\pm$ 0.5 V (unless otherwise noted) (see Figure 1)

| PARAMETER        | FROM<br>(INPUT)  | TO<br>(OUTPUT)     | MIN | MAX | UNIT |

|------------------|------------------|--------------------|-----|-----|------|

| t <sub>PLH</sub> | DATAIN or DATAIN | DATAOUT or DATAOUT | 1.5 | 4.5 | ns   |

| <sup>t</sup> PHL | DATAIN or DATAIN | DATAOUT or DATAOUT | 1.5 | 4.5 | ns   |

SDNS001B - SEPTEMBER 1992 - REVISED DECEMBER 1994

**VOLTAGE WAVEFORMS**

**OUTPUT CLOCK AND DATA TIMING**

#### PARAMETER MEASUREMENT INFORMATION - V<sub>CC</sub> -2 V $\lesssim$ 50 $\Omega \lesssim$ 50 $\Omega \lesssim$ 50 $\Omega \lesssim$ 50 $\Omega$ 17 DOUT DIN 18 DOUT 6 DIN 21 CLK 50 Ω ≥ 50 Ω 2 **CPLL TNETA1555** 20 **CLK** 14 13 DATAOUT DATAIN 12 15 CPLL DATAOUT DATAIN 0.1 μF **LOAD CIRCUITS** - 3.215 ns **DATAIN** $V_{IH}$ 50% 50% DATAIN $v_{IL}$ DIN 50% 50% <sup>t</sup>PHL **CLK** 50% DATAOUT VOH 50% 50% tcsp DATAOUT VOL

Figure 1. Load Circuits and Voltage Waveforms

**VOLTAGE WAVEFORMS**

**PROPAGATION DELAY TIMES**

SDNS001B - SEPTEMBER 1992 - REVISED DECEMBER 1994

#### **APPLICATION INFORMATION**

#### introduction

The TNETA1555 provides clock recovery and data retiming on a nonreturn to zero (NRZ) serial-input data stream. The device uses an analog phase-locked loop (APLL) with an integrated voltage controlled oscillator (VCO) to recover the imbedded clock signal from incoming data. A loop-filter capacitor is the only external component required for the proper operation of the device. The TNETA1555 is designed for operation with a 155.52-Mbit/s serial-input data stream. The device has pseudo-ECL compatible inputs and outputs and operates from a single 5-V supply. Pseudo-ECL levels are referenced to 5 V instead of ground.

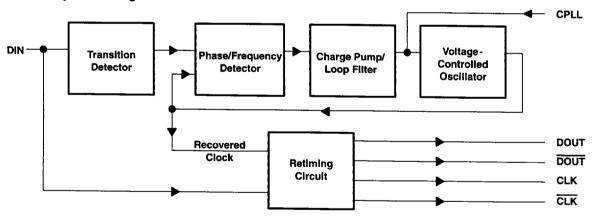

Since the incoming 155.52-Mbit/s serial-input data stream does not contain a 155.52-MHz frequency component, a transition detector, shown on the clock-recovery block diagram, is used as a frequency doubler to generate this frequency. The output of the transition detector is passed to a phase/frequency detector where it is compared to the output of the VCO. The phase/frequency detector is actually comprised of two circuits. One circuit provides a coarse frequency-detection capability and a second provides a finer phase adjustment. The phase/frequency detector compares the signal from the transition detector to the VCO output and generates signals to either increase or decrease the VCO frequency, depending upon whether the VCO frequency is less than or greater than the frequency of the signal from the transition detector. The up/down pulses are sent to the charge pump/loop filter for conversion to a bias voltage that sets the VCO output frequency.

The process of comparing the input signal frequency and the VCO output frequency is continuous and eventually results in the VCO output frequency equaling the frequency of the input signal. The device also allows the VCO output to react to changes in the input signal due to jitter. The recovered clock output is sent from the VCO to the retiming circuit where the input data is retimed to the recovered clock. The retiming circuit centers the output clock in the middle of the output data.

#### clock-recovery block diagram

#### performance measurements

Measuring the performance of a clock-recovery circuit involves determining how well the circuit operates in the presence of jitter. Jitter is defined as the short-term variations of digital signals significant instants from their ideal positions in time. For testing purposes, jitter is usually generated by modulating a digital data sequence with a sinusoidal waveform of a known frequency. This results in a digital data stream where the widths of the individual data pulses vary with time. The amount of pulse-width variation can be changed by altering the frequency and amplitude of the modulating signal, which changes the amount of jitter in the data stream. The following paragraphs describe the test results obtained from the TNETA1555 for various performance measurements.

† Bellcore technical reference TR-TSY-000499 Issue 3, December 1989, page 7-1.

SDNS001B - SEPTEMBER 1992 - REVISED DECEMBER 1994

#### **APPLICATION INFORMATION**

#### **RMS** jitter

This test provides a measure of the internal jitter performance of the clock-recovery circuit. A data stream with very low jitter (all data generators have a small amount of jitter) is input to the clock-recovery device, and the jitter of the recovered clock is measured. A  $2^{31}$ –1 pseudo-random bit sequence (PRBS) is used for the input data stream. For this test, the worst-case jitter performance was measured with  $V_{CC}$  = 4.75 V at an operating free-air temperature of 85°C. Table 1 summarizes these test results.

Table 1. Worst-Case RMS Jitter Measurement,  $V_{CC} = 4.75 \text{ V}$ ,  $T_A = 85^{\circ}\text{C}$

| Device No.        | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   |

|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Jitter<br>(° RMS) | 3.5 | 3.2 | 3.5 | 3.3 | 3.1 | 3.5 | 3.1 | 3.0 | 3.4 |

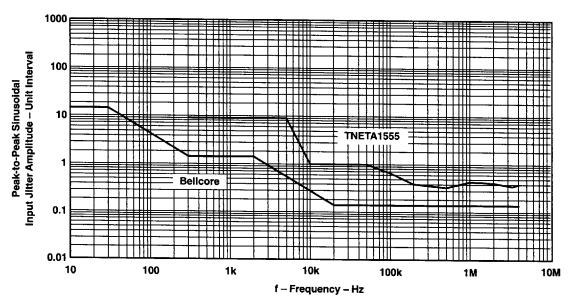

#### jitter tolerance

Jitter tolerance is a measure of the ability of the clock-recovery circuit to tolerate an input signal without experiencing a bit error. For this test, the Bellcore SONET category II jitter-tolerance mask was used (Bellcore specification TR-NWT-000253). The worst-case performance was measured with  $V_{CC} = 5.25 \text{ V}$  at an operating free-air temperature of 85°C. Table 2 and Figure 2 show the results of this test.

Table 2. Jitter Tolerance Values Used in the Graph of Figure 2

| Frequency H <sub>Z</sub> | Bellcore | TNETA1555 |

|--------------------------|----------|-----------|

| 10                       | 15       | N.A.      |

| 30                       | 15       | N.A.      |

| 300                      | 1.5      | 10        |

| 1k                       | 1.5      | 10        |

| 2k                       | 1.5      | 10        |

| 5k                       | 0.81     | 10        |

| 10k                      | 0.3      | 1         |

| 20k                      | 0.15     | 1         |

| 50k                      | 0.15     | 1         |

| 100k                     | 0.15     | 0.658     |

| 200k                     | 0.15     | 0.382     |

| 500k                     | 0.15     | 0.34      |

| 1M                       | 0.15     | 0.536     |

| 2M                       | 0.15     | 0.515     |

| 3.5M                     | 0.15     | 0.486     |

| 4M                       | 0.15     | 0.493     |

#### **APPLICATION INFORMATION**

## jitter tolerance (continued)

Figure 2. Jitter Tolerance (Worst Case)

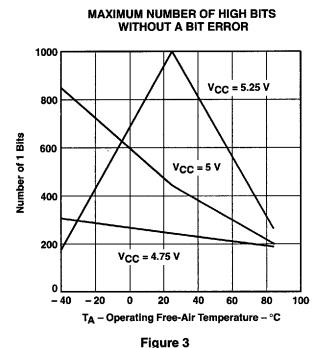

#### transitionless bit periods

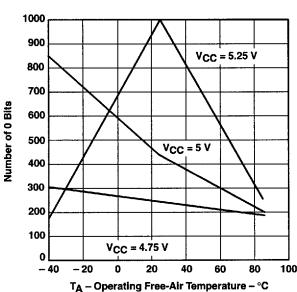

The SONET/SDH specifications do not use a line code that limits the number of transitionless bit periods in a bit stream to a specific number. Instead, a scrambler is used to provide some randomization of the line signal. As long as the output data stream does not match the output of the scrambler, this technique works fairly well. However, it is possible for the scrambled data stream to contain a large number of transitionless bit periods, depending upon the data being transmitted. It is important that the clock-recovery device handle large numbers of transitionless bit periods without causing a bit error. Figures 3 and 4 show the results of tests conducted on the TNETA1555 for transitionless bit periods. The y-axis shows the number of transitionless bit periods that the devices can accept before a bit error is recorded on the bit-error rate tester.

SDNS001B - SEPTEMBER 1992 - REVISED DECEMBER 1994

#### **APPLICATION INFORMATION**

#### transitionless bit periods (continued)

MAXIMUM NUMBER OF LOW BITS WITHOUT A BIT ERROR

Figure 4

## jitter transfer (peaking and bandwidth)

SONET/SDH regenerator interfaces are required to meet jitter-transfer requirements. Jitter transfer is the ratio of measured output jitter to applied input jitter, and it is measured in decibels. Meeting the jitter-transfer requirement in SONET/SDH regenerators requires either a clock-recovery circuit with a voltage-controlled crystal oscillator (VCXO) or a similar technique that provides extremely low jitter. The TNETA1555 provides a typical jitter-transfer bandwidth of approximately 2 MHz. This is where the device begins to attenuate the input jitter so that the output jitter is less than the input jitter. The device exhibits minimal jitter peaking when a capacitor of approximately 0.1 µF is used in the loop filter. The peaking is less than 0.3 dB, which is the resolution of the test equipment used to measure this parameter.

#### external connections

#### loop-filter capacitor

The capacitor for the loop filter is connected from terminal 2 of the TNETA1555 to ground. It is recommended that a 0.1-μF chip capacitor be used. A smaller capacitor reduces the amount of acquisition time required for the device to lock on to the input data stream while it increases the amount of jitter peaking that can occur. A larger capacitor results in a longer acquisition time and does not provide any noticeable increase in jitter performance.

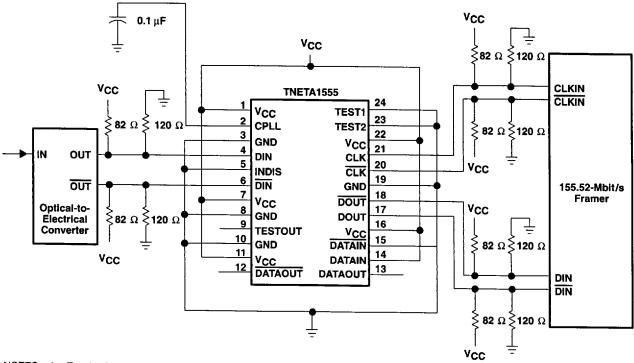

#### signal connections

Figure 5 shows a typical connection between the TNETA1555, an optical-to-electrical converter, and a framer device. The TNETA1555 accepts pseudo-ECL compatible signals at the serial data inputs DIN and  $\overline{\text{DIN}}$ . The retimed pseudo-ECL clock outputs are provided at outputs  $\overline{\text{CLK}}$  and CLK. The pseudo-ECL inputs and outputs require a 50- $\Omega$  termination to V<sub>CC</sub> –2 V (or a Thevenin equivalent). The Thevenin equivalent circuit consists of an 82- $\Omega$  resistor to V<sub>CC</sub> and 120- $\Omega$  resistor to ground.

## **APPLICATION INFORMATION**

# signal connections (continued)

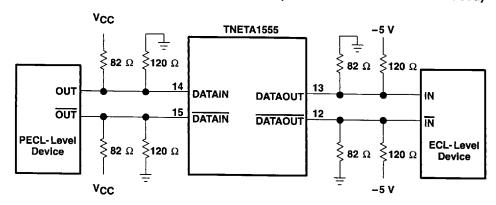

A separate pseudo-ECL to ECL converter is also provided on the TNETA1555. The pseudo-ECL inputs require a 50- $\Omega$  to V<sub>CC</sub>-2 V termination (or a Thevenin equivalent) and the ECL outputs require a 50- $\Omega$  to -2 V termination (or its equivalent). Figure 6 shows the external connections for the pseudo-ECL to ECL converter.

- NOTES: A. Terminating resistors should be placed as close to the input terminal as possible.

- B. The 0.1- $\mu\text{F}$  bypass capacitors should be connected from the VCC terminals to ground.

Figure 5. TNETA1555 External Connections (PECL-to-ECL converter not used)

Figure 6. External Connections for PECL-to-ECL Converter

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1995, Texas Instruments Incorporated