#### 3 Electrical Characteristics

# 3.1 Absolute Maximum Ratings Over Operating Free-Air Temperature Range (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>DD</sub> (see Note 1)                       | 7 V                                     |

|--------------------------------------------------------------------|-----------------------------------------|

| Input voltage range, V <sub>I</sub> –0.5                           | $5 \text{ V to V}_{DD} + 0.5 \text{ V}$ |

| Analog output short-circuit duration to any power supply or common | unlimited                               |

| Operating free-air temperature range, T <sub>A</sub>               | 0°C to 70°C                             |

| Storage temperature range                                          | 65°C to 150°C                           |

| Junction temperature                                               | 175°C                                   |

| Case temperature for 10 seconds: FN package                        | 260°C                                   |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds       | 260°C                                   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to GND.

## 3.2 Recommended Operating Conditions

|                                                      | MIN  | NOM   | MAX                  | UNIT |

|------------------------------------------------------|------|-------|----------------------|------|

| Supply voltages, AV <sub>DD</sub> , DV <sub>DD</sub> | 4.75 | 5     | 5.25                 | ٧    |

| Reference voltage, V <sub>ref</sub>                  | 1.15 | 1.235 | 1.26                 | ٧    |

| High-level input voltage, VIH                        | 2.4  |       | V <sub>DD</sub> +0.5 | ٧    |

| Low-level input voltage, VIL                         |      |       | 0.8                  | ٧    |

| Output load resistance, RL                           |      | 37.5  |                      | Ω    |

| FS ADJUST resistor, R <sub>SET</sub>                 |      | 523   |                      | Ω    |

| Operating free-air temperature, TA                   | 0    |       | 70                   | °C   |

#### 3.3 Electrical Characteristics

|                      | PARAM                                                | ETER                         | TEST<br>CONDITIONS                   | MIN  | TYP  | MAX                  | UNIT   |

|----------------------|------------------------------------------------------|------------------------------|--------------------------------------|------|------|----------------------|--------|

| Vон                  | High-level output volta                              | ige                          | I <sub>OH</sub> = -800 μA            | 2.4  | 2.4  |                      |        |

|                      | Low-level output                                     | D(0-7), VCLK, RCLK,<br>SENSE | I <sub>OL</sub> = 3.2 mA             |      |      | 0.4                  | v      |

| VOL                  | voltage                                              | HSYNCOUT, VSYNCOUT           | 1OL = 15 mA                          |      |      | 0.4                  | ٧      |

|                      |                                                      | SCLK                         | I <sub>OL</sub> = 18 mA              |      |      | 0.4                  |        |

| VID                  | Differential input voltage                           | ECL inputs                   |                                      | 0.6  |      | 6                    | ٧      |

| ۷ <sub>IC</sub>      | Common-mode input voltage                            | ECL inputs                   |                                      | 2.85 | 3.15 | V <sub>DD</sub> -0.5 | ٧      |

|                      | High-level input                                     | TTL inputs                   | V <sub>I</sub> = 2.4 V               |      |      | 1                    | μΑ     |

| ΉΗ                   | current                                              | ECL inputs                   | V <sub>I</sub> = 4 V                 |      |      | 1                    | , part |

|                      | Low-level input                                      | TTL inputs                   | V <sub>I</sub> = 0.8 V               |      |      | -1                   | дA     |

| 11                   | current                                              | ECL inputs                   | V <sub>1</sub> = 0.4 V               |      |      | -1                   | μ.,    |

|                      | Supply current,<br>pseudo-color mode<br>(see Note 2) | TVP3010-85                   |                                      |      | 250  | 280                  |        |

| ١.                   |                                                      | TVP3010-110                  | V <sub>DD</sub> = 5                  |      | 270  | 320                  | mA     |

| IDD                  |                                                      | TVP3010-135                  |                                      |      | 330  | 380                  | 11125  |

|                      | (000 11010 =)                                        | TVP3010-170                  |                                      |      | 390  | 440                  |        |

|                      | ····                                                 | TVP3010-85                   |                                      |      | 270  | 320                  |        |

| ١.                   | Supply current, true-                                | TVP3010-110                  | ],,                                  |      | 320  | 370                  | mA     |

| IDD                  | color mode                                           | TVP3010-135                  | V <sub>DD</sub> = 5                  |      | 370  | 420                  | 111/5  |

|                      |                                                      | TVP3010-170                  |                                      | 420  | 475  |                      |        |

| loz                  | High-impedance-state                                 | output current               |                                      |      |      | 10                   | μA     |

|                      | l                                                    | TTL inputs                   | f = 1 MHz,<br>V <sub>I</sub> = 2.4 V |      | 4    |                      | pF     |

| C <sub>i</sub> Input | Input capacitance                                    | ECL inputs                   | f = 1 MHz,<br>V <sub>i</sub> = 4 V   |      | 4    |                      | Pi     |

† All typical values are at V<sub>DD</sub> = 5 V, T<sub>A</sub> = 25°C.

NOTE 2: IDD is measured with dot clock running at the maximum specified frequency, SCLK frequency = dot clock frequency/8 (in pseudo-color modes), and the palette RAM loaded with repeating full-range toggling patterns (00h/00h/00h/00h/FFh/FFh/FFh). Pseudo-color mode is also known as color indexing mode.

# 3.4 Operating Characteristics

|    | PARAMETER                        | TEST CONDITIONS                                 | MiN                   | TYP      | MAX   | UNIT    |

|----|----------------------------------|-------------------------------------------------|-----------------------|----------|-------|---------|

|    | Decelution (such DAO)            | 8/ <del>6</del> high                            |                       | 8        |       | L.32    |

|    | Resolution (each DAC)            | 8/6 low                                         |                       | 6        |       | bits    |

| F. | End-point linearity error        | 8/6 high                                        |                       |          | 1     | LSB     |

| EL | (each DAC)                       | 8/6 low                                         |                       |          | 1/4   | LOB     |

| F- | Differential linearity error     | 8/6 high                                        |                       |          | 1     | LSB     |

| ED | (each DAC)                       | 8/6 low                                         |                       |          | 1/4   | LOB     |

|    | Gray scale error                 |                                                 |                       | 1        | 5%    |         |

|    |                                  | White level relative to blank                   | 17.69                 | 19.05    | 20.4  | mA      |

|    |                                  | White level relative to black (7.5 IRE only)    | 16.74                 | 17.62    | 18.5  | mA      |

|    |                                  | Black level relative to blank<br>(7.5 IRE only) | 0.95                  | 1.44     | 1.9   | mA      |

|    | Output current (see Note 3)      | Blank level on IOR, IOB                         | 0                     | 5        | 50    | μА      |

|    | , ,                              | Blank level on IOG<br>(with SYNC enabled)       | 6.29                  | 7.6      | 8.96  | mA      |

|    |                                  | Sync level on IOG (with SYNC enabled)           | 0                     | 5        | 50    | μА      |

|    |                                  | One LSB (8/6 high)                              |                       | 69.1     |       | μΑ      |

|    |                                  | One LSB (8/6 low)                               |                       | 276.4    |       | μА      |

|    | DAC-to-DAC matching              |                                                 |                       | 2%       | 5%    |         |

|    | DAC-to-DAC crosstalk             |                                                 |                       | -20      |       | dB      |

|    | Output compliance                |                                                 | -1                    |          | 1.2   | V       |

|    | Voltage reference output voltage |                                                 | 1.15                  | 1.235    | 1.26  | V       |

|    | Output impedance                 |                                                 |                       | 50       |       | kΩ      |

|    | Output capacitance               | f = 1 MHz, I <sub>OUT</sub> = 0                 |                       | 13       |       | pF      |

|    | Sense voltage reference          |                                                 | 300                   | 350      | 400   | mV      |

|    | Clock and data feedthrough       |                                                 |                       | -20      |       | dB      |

|    | Glitch impulse (see Note 4)      |                                                 |                       | 50       |       | pV–s    |

|    | Pinalina dalay VGA sart          | Self-clocked timing                             | 18 dot                |          | k     | periods |

|    | Pipeline delay, VGA port         | Externally-clocked timing                       | 15 dot clock          |          | k     | periods |

|    | Dinalina dalay nivol nort        | Self-clocked timing                             | 2 RCLK + 14 dot clock |          | clock | periods |

|    | Pipeline delay, pixel port       | Externally-clocked timing                       | 1 RCL                 | C+14 dot | clock | periods |

NOTES: 3. Test conditions for RS343-A video signals (unless otherwise specified) can be found in "Recommended Operating Conditions" using external voltage reference  $V_{ref} = 1.235 \text{ V}$ ,  $R_{SET} = 523 \Omega$ . When using the internal voltage reference,  $R_{SET}$  may need to be adjusted in order to meet these limits.

<sup>4.</sup> Glitch impulse does not include clock and data feedthrough. The – 3-dB test bandwidth is twice the clock rate.

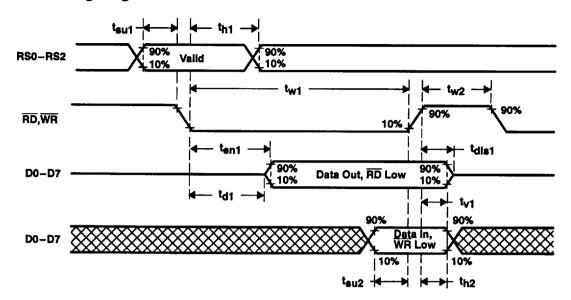

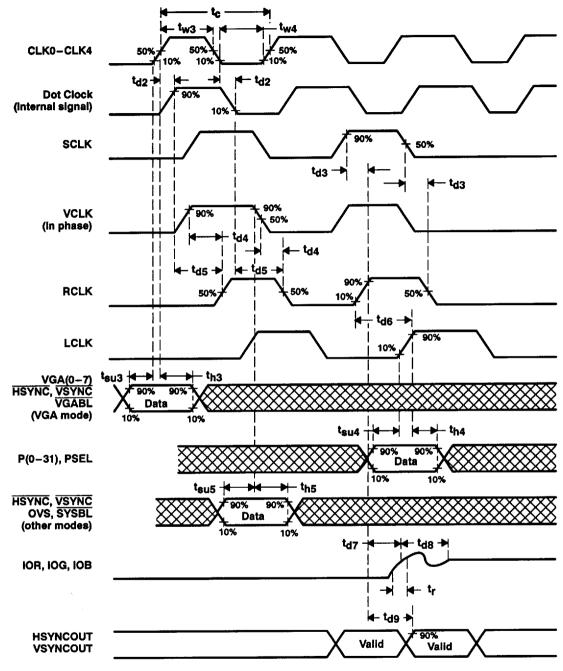

### 3.5 Timing Requirements (see Note 5)

|                  |                                                             | -          |              | 3010<br>35 | TVP:<br>-1 |     |            | 3010<br>35 |            | TVP3010<br>-170 |     |

|------------------|-------------------------------------------------------------|------------|--------------|------------|------------|-----|------------|------------|------------|-----------------|-----|

|                  |                                                             |            | MIN          | MAX        | MIN        | MAX | MIN        | MAX        | MIN        | MAX             |     |

|                  | Dot clock frequency                                         |            | -            | 85         |            | 110 |            | 135        |            | 170             | MHz |

|                  | CLK0 frequency for VGA<br>pass-through mode (see Note 6     | <b>3)</b>  |              | 85         |            | 85  |            | 85         |            | 85              | MHz |

| tc               | Clock cycle time                                            | TTL<br>ECL | 11.8<br>11.8 |            | 9.1<br>9.1 |     | 7.4<br>7.4 |            | 7.1<br>5.8 |                 | ns  |

| t <sub>su1</sub> | Setup time, RS(0−3) valid befo                              | re RD      | 10           |            | 10         |     | 10         |            | 10         |                 | ns  |

| t <sub>h1</sub>  | Hold time, RS(0-3) valid after i                            | RD or      | 10           |            | 10         |     | 10         |            | 10         |                 | ns  |

| t <sub>su2</sub> | Setup time, D(0-7) valid before                             | WR†        | 35           |            | 35         |     | 35         |            | 35         |                 | ns  |

| th2              | Hold time, D(0−7) valid after W                             | R†         | 0            |            | 0          |     | 0          |            | 0          |                 | ns  |

| t <sub>su3</sub> | Setup time, VGA(0-7) and VGA valid before CLK0† (see Note 7 |            | 2            |            | 2          |     | 2          |            | 2          |                 | ns  |

| t <sub>h3</sub>  | Hold time, VGA(0-7) and VGA valid after CLK0↑ (see Note 7)  | BL         | 2            |            | 2          |     | 2          |            | 2          |                 | ns  |

| t <sub>su4</sub> | Setup time, P(0-31) and PSEL before LCLK† (see Note 8)      | . valid    | 2            |            | 2          |     | 2          |            | 2          |                 | ns  |

| t <sub>h4</sub>  | Hold time, P(0-31) and PSEL vafter LCLK† (see Note 8)       | valid      | 5            |            | 5          |     | 5          |            | 5          |                 | ns  |

| t <sub>su5</sub> | Setup time, HSYNC, VSYNC, a SYSBL valid before VCLK.        | ınd        | 5            |            | 5          |     | 5          |            | 5          |                 | ns  |

| t <sub>h5</sub>  | Hold time, HSYNC, VSYNC and SYSBL valid after VCLK.         | d          | 1            |            | 1          |     | 1          |            | 1          |                 | ns  |

| tw1              | Pulse duration, RD or WR low                                |            | 50           |            | 50         |     | 50         |            | 50         |                 | ns  |

| tw2              | Pulse duration, RD or WR high                               |            | 30           |            | 30         |     | 30         |            | 30         |                 | ns  |

|                  | Pulse duration, clock high                                  | ΠL         | 4            |            | 3.5        |     | 3          |            | 3          |                 | ns  |

| tw3              | i dise dutation, stook mgm                                  | ECL        | 4            |            | 3          |     | 3          |            | 2.5        |                 |     |

| t <sub>w4</sub>  | Pulse duration, clock low                                   | TTL        | 4            | -          | 3.5        |     | 3          |            | 3          |                 | ns  |

|                  |                                                             | ECL        | 4            |            | 3          |     | 3          |            | 2.5        |                 |     |

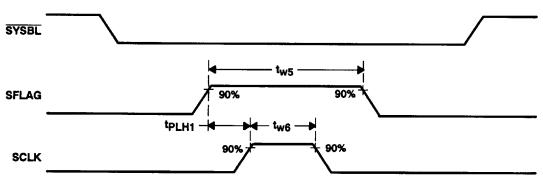

| tw5              | Pulse duration, SFLAG high (see Note 9)                     |            | 30           |            | 30         |     | 30         |            | 30         |                 | ns  |

| tw6              | Pulse duration, SCLK high (see Note 9)                      |            | 15           | 55         | 15         | 55  | 15         | 55         | 15         | 55              | ns  |

NOTES: 5. TTL input signals are 0 to 3 V with less than 3-ns rise/fall time between the 10% and 90% levels unless otherwise specified. ECL input signals are V<sub>DD</sub>-1.8 V to V<sub>DD</sub>-0.8 V with less than 2-ns rise/fall time between the 20% and 80% levels. For input and output signals, timing reference points are at the 10% and 90% signal levels. Analog output loads are less than 10 pF. D(0-7) output loads are less than 50 pF. All other output loads are less than 50 pF unless otherwise specified.

In VGA mode, CLK0 minimum pulse duration for clock low should be greater than 4.8 ns. If VGA switching

is to be performed using self-clocked timing, the maximum pixel rate cannot exceed 50 MHz.

7. Reference to CLK0 input only.

8. RCLK is delayed from SCLK in such a way that when RCLK is connected to LCLK, the timing is essentially the same as the TLC3407x family of parts.

This parameter applies when the split shift-register transfer (SSRT) function is enabled. See Section 2.15 for details.

#### 3.6 Switching Characteristics

|                   | PARAMETER                                                                                 |     | TVP3010-85 |         |     | TVP3010-110 |         |      |  |

|-------------------|-------------------------------------------------------------------------------------------|-----|------------|---------|-----|-------------|---------|------|--|

|                   | PARAMETER                                                                                 | MIN | TYP        | MAX     | MIN | TYP         | MAX     | UNIT |  |

|                   | SCLK frequency (C <sub>L</sub> ≤ 15 pF) (see<br>Note 10)                                  |     |            | 85      |     |             | 85      | MHz  |  |

|                   | SCLK frequency (C <sub>L</sub> ≤ 60 pF) (see Note 10)                                     |     |            | 85      |     |             | 85      | MHz  |  |

|                   | RCLK/VCLK frequency (see Note 10)                                                         |     |            | 85      |     |             | 85      | MHz  |  |

| t <sub>en1</sub>  | Enable time, RD low to D(0-7) valid                                                       |     |            | 40      |     | -           | 40      | ns   |  |

| <sup>t</sup> dis1 | Disable time, $\overline{RD}$ high to D(0-7) disabled                                     |     |            | 17      |     | •           | 17      | ns   |  |

| t <sub>v1</sub>   | Valid time, D(0−7) valid after RD high                                                    | 5   |            |         | 5   |             |         | ns   |  |

| <sup>t</sup> PLH1 | Propagation delay, SFLAG† to SCLK high (see Note 10 and 11)                               | 0   |            | 20      | 0   |             | 20      | ns   |  |

| <sup>t</sup> d1   | Delay time, $\overline{RD}$ low to D(0-7) starting to turn on                             | 5   |            |         | 5   |             |         | ns   |  |

| <sup>t</sup> d2   | Delay time, selected input clock high/low to dot clock (internal signal) high/low         |     | 7          |         | -   | 7           |         | ns   |  |

| t <sub>d3</sub>   | Delay time, SCLK high/low to RCLK high/low (see Note 12)                                  | 1   | 2          | 5       | 1   | 2           | 5       | ns   |  |

| <sup>t</sup> d4   | Delay time, VCLK high/low to RCLK high/low (see Note 12)                                  | 1   | 3          | 6       | 1   | 3           | 6       | ns   |  |

| t <sub>d5</sub>   | Delay time, RCLK high/low from dot clock high/low (internal signal)                       |     | 7          |         |     | 7           |         | ns   |  |

| t <sub>d6</sub>   | Delay time, LCLK from RCLK                                                                |     |            | tRCLK-7 |     |             | tRCLK-7 | ns   |  |

| <sup>t</sup> d7   | Delay time, dot clock high to IOR/IOG/IOB active (analog output delay time) (see Note 13) |     | 4          |         |     | 4           |         | ns   |  |

| t <sub>d8</sub>   | Analog output settling time (see Note 14)                                                 |     | 6          |         |     | 6           |         | ns   |  |

| <sup>t</sup> d9   | Delay time, dot clock high to HSYNCOUT and VSYNCOUT valid                                 |     | 9          |         |     | 9           |         | ns   |  |

| t <sub>r</sub>    | Analog output rise time (see Note 15)                                                     |     | 2          |         |     | 2           |         | ns   |  |

|                   | Analog output skew                                                                        | 0   |            | 2       | 0   |             | 2       | ns   |  |

NOTES: 10. SCLK can drive an output capacitive load up to 60 pF. The worst-case transition time between the 10% and 90% levels is less than 4 ns (typical 3 ns). RCLK and VCLK can drive output capacitive loads up to 15 pF, with worst-case transition times between 10% and 90% levels less than 4 ns (typical 3 ns).

- This parameter applies when the split shift-register transfer (SSRT) function is enabled. See Section 2.15 for details.

- 12. The SCLK and VCLK delay time to RCLK depends on the load that the signals drive. This parameter is measured with an RCLK to VCLK ratio of 1:1, a VCLK = RCLK load of 15 pF, and an SCLK load of 60 pF.

- Measured from the 90% point of the rising edge of the internal dot clock signal to 50% of the full-scale transition

- 14. Measured from the 50% point of the full-scale transition to the point at which the output has settled within ± 1 LSB (settling time does not include clock and data feedthrough)

- 15. Measured between 10% and 90% of the full-scale transition

## 3.6 Switching Characteristics (Continued)

|                   |                                                                                           | Т   | VP3010 | -135    | TVP3010-170 |     | UNIT    |      |

|-------------------|-------------------------------------------------------------------------------------------|-----|--------|---------|-------------|-----|---------|------|

|                   | PARAMETER                                                                                 | MIN | TYP    | MAX     | MIN         | TYP | MAX     | ONII |

|                   | SCLK frequency (C <sub>L</sub> ≤ 15 pF)<br>(see Note 10)                                  |     |        | 85      |             | -   | 87.5    | MHz  |

|                   | SCLK frequency (C <sub>L</sub> ≤ 60 pF) (see Note 10)                                     |     |        | 85      |             |     | 85      | MHz  |

|                   | RCLK, VCLK frequency (see Note 10)                                                        |     |        | 85      | ,           |     | 85      | MHz  |

| t <sub>en1</sub>  | Enable time, RD low to D(0−7) valid                                                       |     |        | 40      |             |     | 40      | ns   |

| <sup>t</sup> dis1 | Disable time, $\overline{RD}$ high to D(0-7) disabled                                     |     |        | 17      |             |     | 17      | ns   |

| t <sub>v1</sub>   | Valid time, D(0−7) valid after RD high                                                    | 5   | ·      |         | 5           |     |         | ns   |

| <sup>t</sup> PLH1 | Propagation delay, SFLAG† to SCLK high (see Note 10 and 11)                               | 0   |        | 20      | 0           |     | 20      | ns   |

| <sup>t</sup> d1   | Delay time, RD low to D(0-7) starting to turn on                                          | 5   |        |         | 5           |     |         | ns   |

| t <sub>d2</sub>   | Delay time, selected input clock high/low to dot clock (internal signal) high/low         |     | 7      |         |             | 7   |         | ns   |

| <sup>t</sup> d3   | Delay time, SCLK high/low to RCLK high/low (see Note 12)                                  | 1   | 2      | 5       | 1           | 2   | 5       | ns   |

| t <sub>d4</sub>   | Delay time, VCLK high/low to RCLK high/low (see Note 12)                                  | 1   | 3      | 6       | 1           | 3   | 6       | ns   |

| <sup>t</sup> d5   | Delay time, RCLK high/low from dot clock high/low (internal signal)                       |     | 7      |         |             | 7   |         | ns   |

| <sup>t</sup> d6   | Delay time, LCLK from RCLK                                                                |     |        | tRCLK-7 |             |     | tRCLK-7 | ns   |

| <sup>t</sup> d7   | Delay time, dot clock high to IOR/IOG/IOB active (analog output delay time) (see Note 13) |     | 4      |         |             | 4   |         | ns   |

| <sup>t</sup> d8   | Analog output settling time (see Note 14)                                                 |     | 6      |         |             | 5   |         | ns   |

| t <sub>d9</sub>   | Delay time, dot clock high to HSYNCOUT and VSYNCOUT valid                                 |     | 9      |         |             | 9   |         | ns   |

| t <sub>r</sub>    | Analog output rise time (see Note 15)                                                     |     | 2      |         |             | 2   |         | ns   |

|                   | Analog output skew                                                                        | 0   |        | 2       | 0           |     | 2       | ns   |

NOTES: 10. SCLK can drive an output capacitive load up to 60 pF. The worst-case transition time between the 10% and 90% levels is less than 4 ns (typical 3 ns). RCLK and VCLK can drive output capacitive loads up to 15 pF, with worst-case transition times between 10% and 90% levels less than 4 ns (typical 3 ns).

- 11. This parameter applies when the split shift-register transfer (SSRT) function is enabled. See Section 2.15 for details.

- 12. The SCLK and VCLK delay time to RCLK depends on the load that the signals drive. This parameter is measured with an RCLK to VCLK ratio of 1:1, a VCLK = RCLK load of 15 pF, and an SCLK load of 60 pF.

- 13. Measured from the 90% point of the rising edge of the internal dot clock signal to 50% of the full-scale transition

- Measured from the 50% point of the full-scale transition to the point at which the output has settled, within ± 1 LSB (settling time does not include clock and data feedthrough)

- 15. Measured between 10% and 90% of the full-scale transition

# 3.7 Timing Diagrams

Figure 3-1. MPU Interface Timing

Figure 3-2. Video Input/Output Timing

Figure 3-3. SFLAG Timing (When SSRT Function is Enabled)