# DART Device Advanced E3/DS3 Receiver/Transmitter TXC-02030

**DATA SHEET**

### **FEATURES**

- Single LIU for E3 and DS3

- Meets 'cross-connect frame' mask requirements

- Adaptive equalization for 0 900 ft of cable for DS3, 0-1300 ft for E3

- Input dynamic range of 30 dB (35 mVp 1.1Vp)

- Meets E3/DS3 jitter requirement standards

- · Optional HDB3 or B3ZS line encoding/decoding

- Line and terminal side E3 or DS3 AIS insertion

- · Full loopback capabilities

- Coding violation and excessive zeros monitors

- Loss of signal detection (per T1/M1 Spec)

- On-device transmit line buffer/filter for DS3; E3 square-wave output

- Receive and transmit power-down modes

- Dejitter PLL/dejitter buffer using external VCXO

- Meets all relevant ANSI and ITU-T standards

- Single +5 volt, ±5% power supply

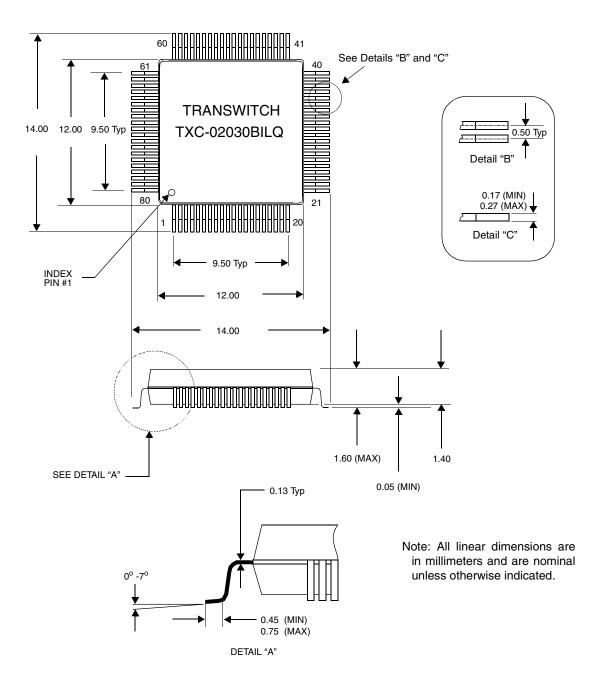

- · 80-pin low profile plastic quad flat package

### **DESCRIPTION I**

The Dual-market Advanced E3/DS3 Receiver/Transmitter (DART) device performs the receive and transmit line interface functions required for transmission of E3 (34.368 Mbit/s) or DS3 (44.736 Mbit/s) signals across a coaxial interface.

The DART operates from a single +5 volt supply with a minimum number of external components. Performance monitoring, loopbacks, E3/DS3 AIS generation, dejitter FIFO, dejitter PLL, PRBS diagnostic circuits and HDB3/B3ZS encoding/decoding functions are included.

A single-device solution for interfacing E3 or DS3 signals to DSX cross-connect frames, the DART meets all applicable ANSI, BellCore and ITU-T interconnection specifications for a wide range of system applications. Specifications include, but are not limited to ANSI T1.102-1993, ANSI T1.404-1994, GR-499-CORE, ITU-T G.703, G.751, G.755, G.823, and ETSI TBR24.

### **APPLICATIONS**

- Multiplexers

- E3/DSX and performance monitoring cross-connects

- Fiber optic and microwave radio terminals

- High speed DSU

- Any E3/DS3 transmission application

U.S. Patents No. 5,119,326; 5,323,423; 5,548,833

Copyright © 2000 TranSwitch Corporation

DART is a trademark of TranSwitch Corporation

TranSwitch and TXC are registered trademarks of TranSwitch Corporation

Document Number: PRELIMINARY TXC-02030-MB Ed. 2A, April 2000 **PRELIMINARY** information documents contain information on products in the sampling, pre-production or early production phases of the product life cycle. Characteristic data and other specifications are subject to change. Contact TranSwitch Applications Engineering for current information on this product.

# **TABLE OF CONTENTS**

| Section                                                | Page |

|--------------------------------------------------------|------|

| Block Diagram                                          | 5    |

| Block Diagram Description                              | 6    |

| Receiver Functions                                     | 9    |

| Adaptive Equalizer/AGC                                 | 9    |

| Clock Recovery                                         | 9    |

| B3ZS/HDB3 Decoder                                      | 9    |

| Rx I/O Control                                         | 9    |

| LOS Detector                                           | 10   |

| Transmitter Functions                                  | 10   |

| Tx I/O Control                                         | 10   |

| Transmit Clock Duty Cycle Control Circuit              |      |

| B3ZS/HDB3 Encoder                                      | 11   |

| Transmitter Output Control Block                       |      |

| Transmitter Calibration PLL                            |      |

| Loopbacks and AIS Insertion                            | 12   |

| Internal Digital Transmit Terminal Side Loopback       |      |

| Internal Analog Receive Line Side Loopback             | 12   |

| Internal Analog Transmit Terminal Side Loopback        |      |

| DS3/E3 AIS Generator                                   |      |

| Testability                                            |      |

| 2 <sup>15</sup> / 2 <sup>23</sup> -1 PRBS Generator    |      |

| 2 <sup>15</sup> / 2 <sup>23</sup> -1 PRBS Analyzer     |      |

| Input Reference Clock                                  |      |

| Dejitter FIFO/Dejitter PLL Operation                   |      |

| Pin Diagram                                            |      |

| Pin Descriptions                                       |      |

| Power Supply and Ground                                | 22   |

| Receive Interface                                      |      |

| Transmit Interface                                     |      |

| Control/Reference Pins                                 |      |

| Miscellaneous Pins                                     |      |

| No Connects                                            |      |

| Absolute Maximum Ratings and Environmental Limitations |      |

| Thermal Characteristics                                |      |

| Power Requirements                                     |      |

| Input and Output Parameters                            |      |

| Input Parameters for TTLp                              |      |

| Output Parameters for CMOS                             |      |

| Timing Characteristics                                 |      |

| E3 Line Side Timing Characteristics                    |      |

| DS3 Line Side Timing Characteristics                   |      |

| Digital Terminal Side Timing Diagrams                  |      |

| Operation                                              |      |

| Receiver Line Side Input Requirements                  |      |

| Interfering Tone Tolerance                             |      |

| Receiver Terminal Side Output Specifications           | 38   |

## **DATA SHEET**

| Transmitter Line Side Output Specifications | 38 |

|---------------------------------------------|----|

| B3ZS Patterns                               | 39 |

| Power-down Mode                             | 41 |

| Jitter Transfer and Generation              | 42 |

| Jitter Transfer                             | 42 |

| Jitter Generation                           | 43 |

| Jitter Tolerance                            | 43 |

| Physical Design                             | 45 |

| General Comments                            | 46 |

| Package Information                         | 52 |

| Ordering Information                        |    |

| Related Products                            |    |

| Standards Documentation Sources             |    |

| List of Data Sheet Changes                  |    |

| Documentation Update Registration Form      |    |

|                                             |    |

## **LIST OF TABLES**

| Tal | ble                                         | Page |

|-----|---------------------------------------------|------|

| 1.  | Dejitter Control Signals                    | 18   |

| 2.  | Dejitter PLL Divide Control                 | 18   |

| 3.  | Receiver and Transmitter Latencies          | 35   |

| 4.  | E3 Interfering Tone Tolerance               | 37   |

| 5.  | DS3 Interfering Tone Tolerance              | 37   |

| 6.  | AIS and Loopback Control Signal Arbitration | 41   |

|     | Deiitter PLL Recommended Components         |      |

<sup>\*</sup>Please note that TranSwitch provides documentation for all of its products. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

# **LIST OF FIGURES**

| Fig | ure                                                                           | Page |

|-----|-------------------------------------------------------------------------------|------|

| 1.  | Simplified DART Block Diagram                                                 | 5    |

| 2.  | Block Diagram of DART Receive Section                                         | 7    |

| 3.  | Block Diagram of DART Transmit Section                                        | 8    |

| 4.  | Receive Side Dejitter FIFO Using PN Data (DJSEL0=0, DJSEL1=0)                 | 14   |

| 5.  | Receive Side Dejitter FIFO Using NRZ Output (DJSEL0=0, DJSEL1=0)              | 15   |

| 6.  | Receive Side Clock Dejitter Only; NRZ Mode (DJSEL0=0, DJSEL1=1)               | 15   |

| 7.  | Receive Side Clock Dejitter Only; PN Mode (DJSEL0=0, DJSEL1=1)                | 16   |

| 8.  | Transmit Side Dejitter FIFO; NRZ Mode (DJSEL0=1, DJSEL1=0)                    | 16   |

| 9.  | Transmit Side Dejitter FIFO; PN Mode (DJSEL0=1, DJSEL1=0)                     | 17   |

| 10. | Normal Operation; PN Mode (DJSEL0=1, DJSEL1=1)                                | 17   |

| 11. | Normal Operation; NRZ Mode (DJSEL0=1, DJSEL1=1)                               | 18   |

| 12. | Dejitter PLL Block Diagram                                                    | 19   |

| 13. | Measured Output Jitter of Dejitter PLL at DS3 (E3 results better or equal to) | 20   |

| 14. | DART TXC-02030 Pin Diagram                                                    | 21   |

| 15. | Pulse Mask at the 34368 kbit/s Interface                                      | 30   |

| 16. | DS3 Interface Isolated Pulse Mask                                             | 31   |

| 17. | DS3 Interface Isolated Pulse Mask Equations                                   | 31   |

| 18. | Receiver CLKO to Data Output Timing                                           | 32   |

| 19. | Receiver CLKO to Data Output Timing                                           | 32   |

| 20. | Transmitter Input Timing                                                      | 33   |

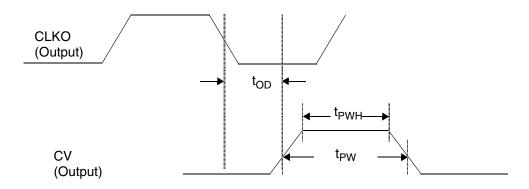

| 21. | Coding Violation Pulse Timing                                                 | 33   |

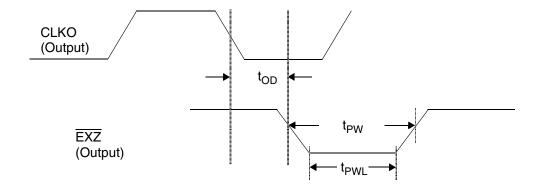

| 22. | Excessive Zeros Pulse Timing                                                  | 34   |

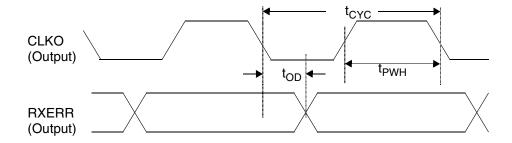

| 23. | Receiver CLKO to RXERR Output Timing                                          | 34   |

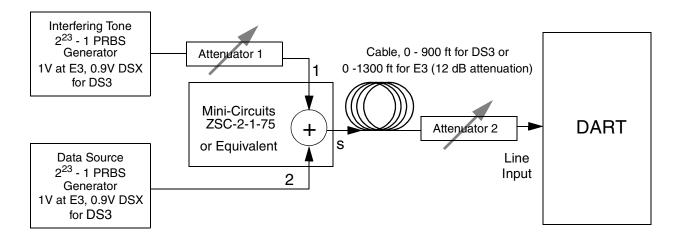

| 24. | Interference Margin Test Configuration                                        | 37   |

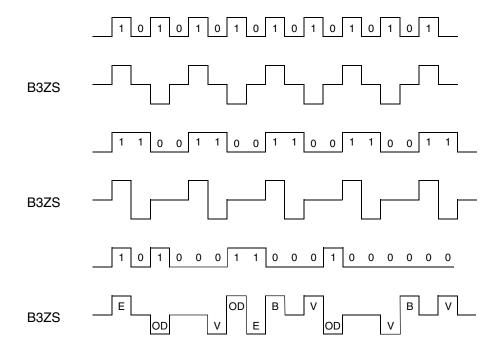

| 25. | Examples of B3ZS Coding (HDB3 Similar)                                        | 39   |

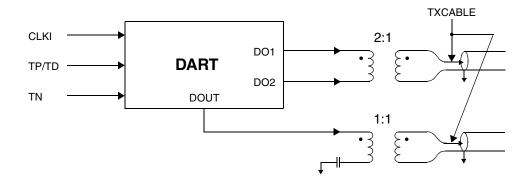

| 26. | Examples of Idealized Transmit Input and Output Data Using B3ZS Coding        | 40   |

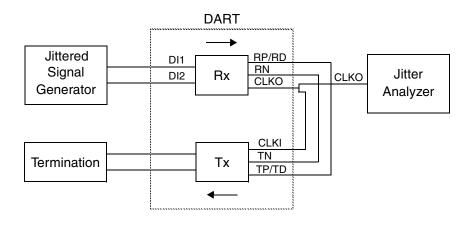

| 27. | Jitter Transfer Test Arrangement                                              | 42   |

| 28. | Jitter Generation Test Arrangement                                            | 43   |

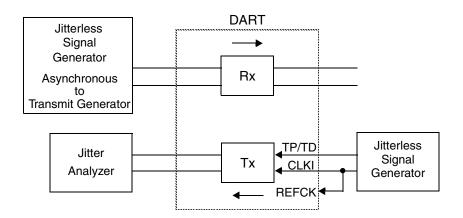

| 29. | Input Jitter Tolerance for E3                                                 | 44   |

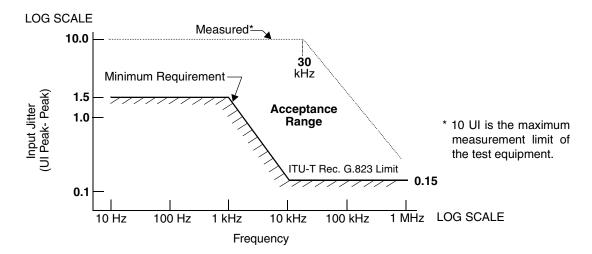

| 30. | Input Jitter Tolerance for DS3                                                | 44   |

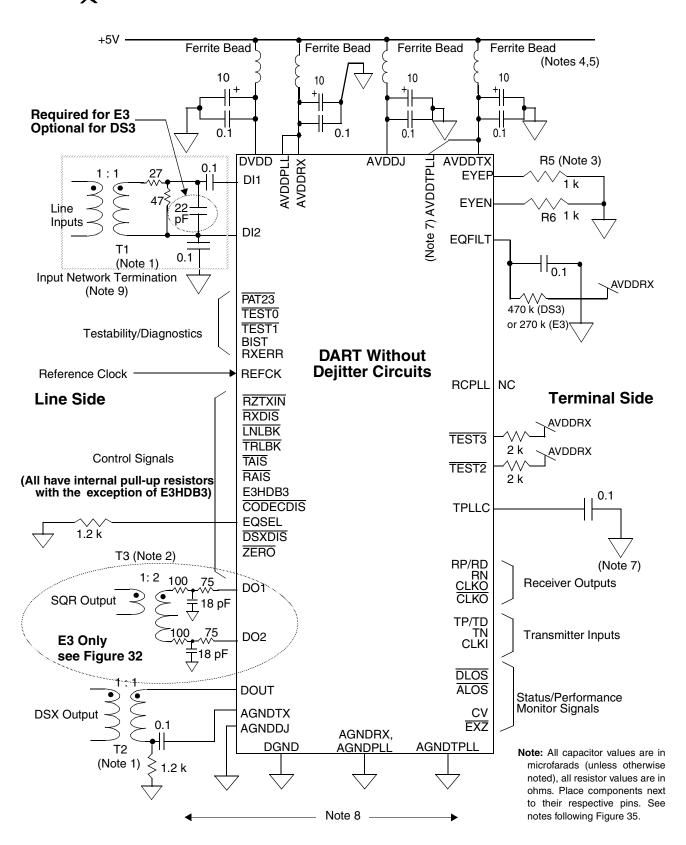

| 31. | External Components, Pin Connections and Power/Grounds                        | 47   |

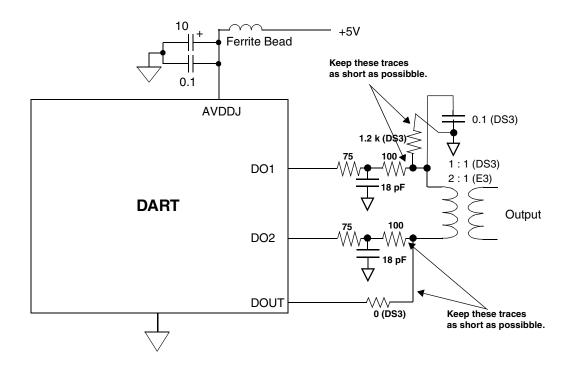

| 32. | DART Layout Guidelines for Combined E3/DS3 Board                              | 48   |

| 33. | DART VCXO Interface When Using the Dejitter Buffer                            | 49   |

| 34. | DART VCXO Interface for Dejittering RCLK Only                                 | 50   |

| 35. | Suggested Single-Ended Termination Circuit for Non-Monitor Functions          | 51   |

| 36. | DART TXC-02030 80-Pin Low Profile Plastic Quad Flat Package                   | 52   |

## **BLOCK DIAGRAM**

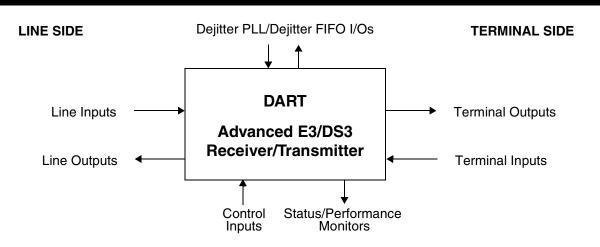

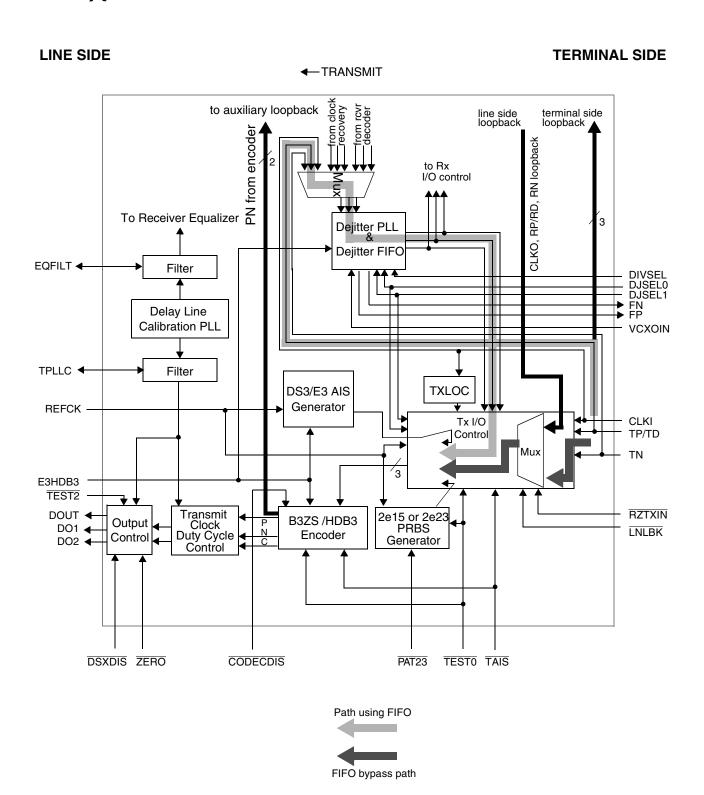

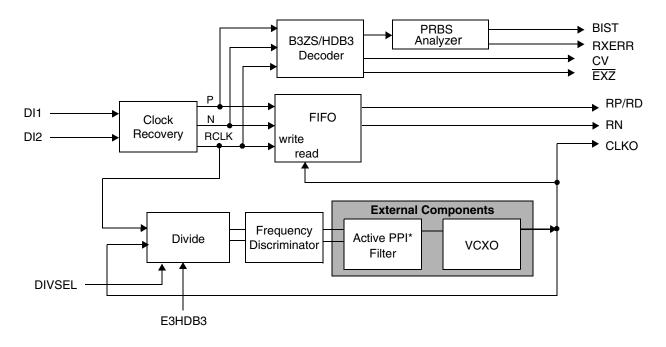

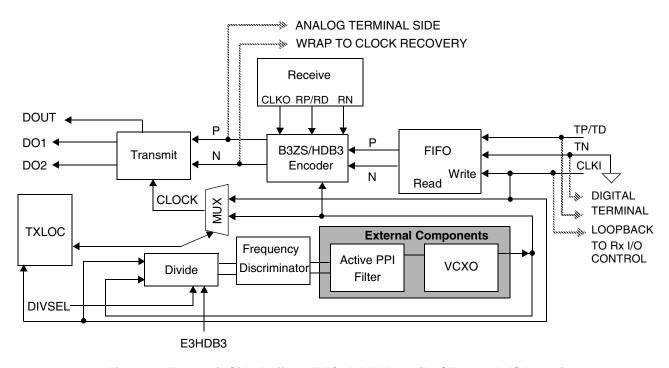

A block diagram of the DART device is provided in Figure 1 below.

Note: Thick and dashed lines show parts of loopback paths.

Figure 1. Simplified DART Block Diagram

### **BLOCK DIAGRAM DESCRIPTION**

The DART is designed to send and receive E3 and DS3 signals across coaxial cables. In addition to the basic receiver, clock recovery and transmitter functions the DART has several additional functions which increase its usefulness in designs. The additional functions are encoder/decoder (optional use), PRBS generator, PRBS analyzer, AIS generator, Loss of Signal detection, three different loopbacks, dejitter PLL (in conjunction with an external VCXO) and a 52-bit dejitter buffer. The latter two optional functions are especially useful for repeaters or when performing loop timing.

Due to the complexity of the DART, Figure 1 shows a simplified block diagram which does not include the dejitter PLL/dejitter buffer paths. The figure shows the device operation when the dejitter circuits are not being used

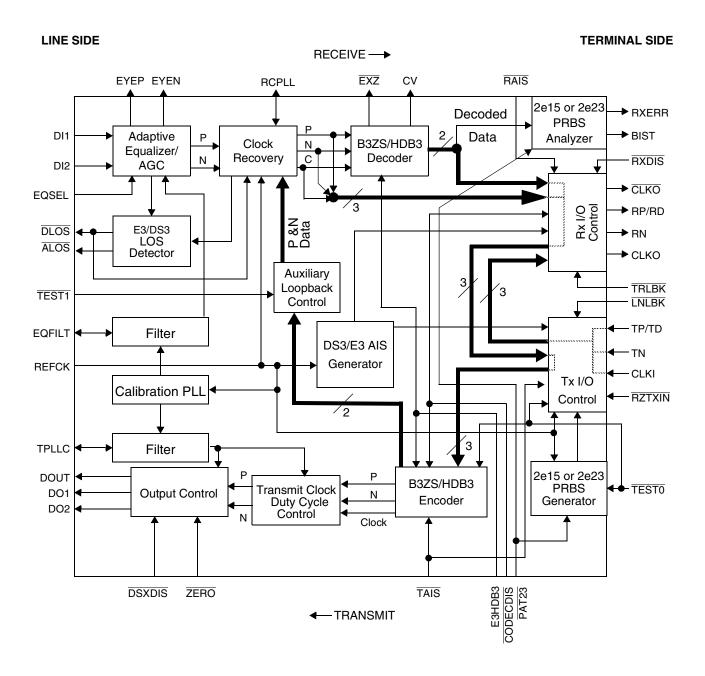

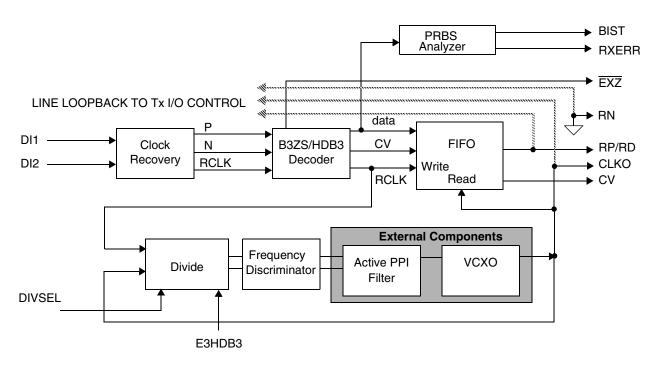

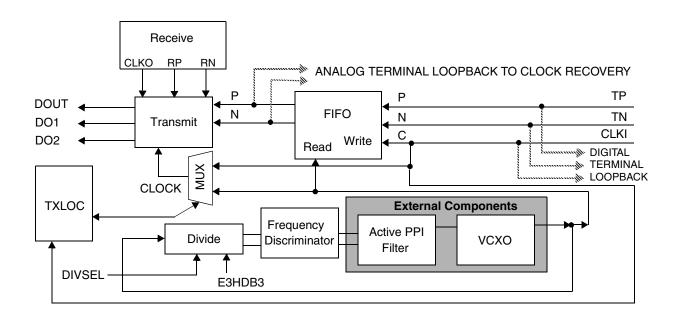

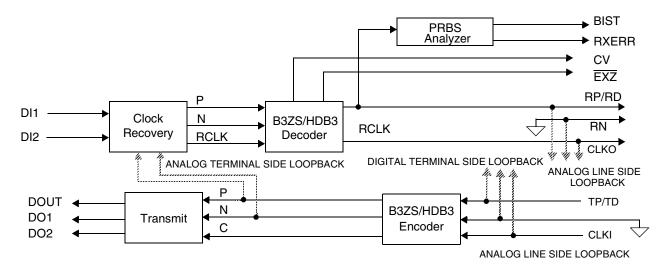

Figure 2 shows the receive section of the DART, which includes the terminal side dejitter circuits. The dejitter PLL can be used independent of the dejitter buffer when in the receive path. Received data can be either encoded NRZ or unencoded PN rail data. The PRBS analyzer output is valid in all modes as are the CV and  $\overline{\text{EXZ}}$  signals.

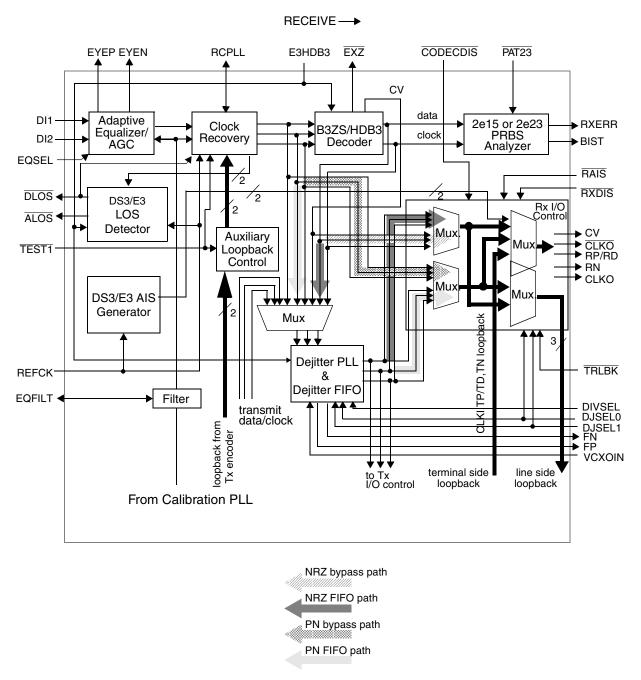

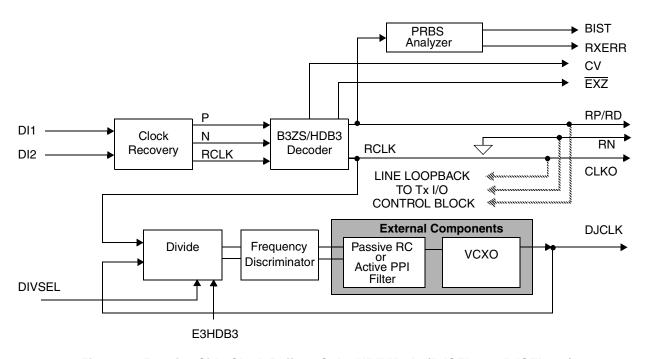

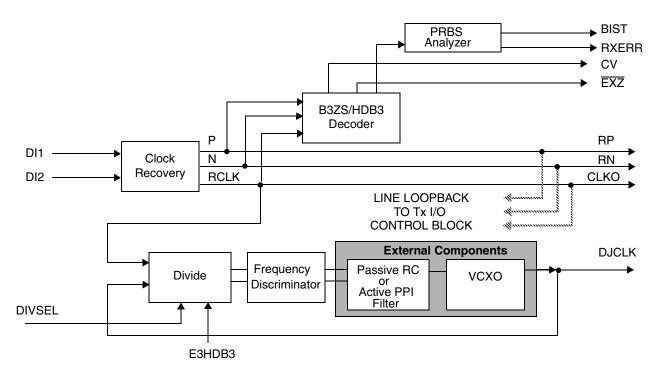

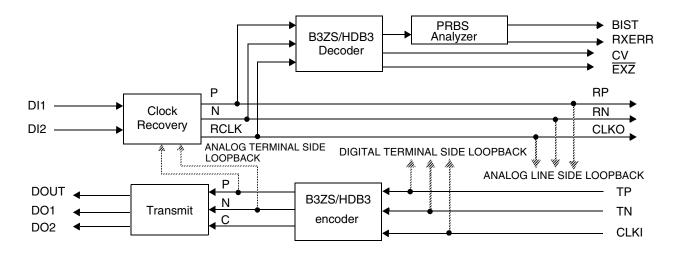

Figure 3 shows the transmit section of the DART, which includes the dejitter circuits. Transmit data can be either unencoded NRZ or encoded PN rail data. The dejitter PLL cannot be used independent of the dejitter buffer when in the transmit path.

Comparing Figures 2 and 3 we see that the dejitter buffer can be used in either the receive or transmit direction with either NRZ or PN data.

In the receive direction the FIFO will contain the decoded-one-bit NRZ data and any code violations (CVs) that occur for CODECDIS high. The CV should be aligned with the data bit that generated the coding violation. When CODECDIS is low the FIFO contains the encoded PN data from the receiver.

The dejitter PLL can be used in the receiver path without using the dejitter FIFO. The FIFO is gated off in this mode. The dejittered clock will be available at the VCXO output. The receive terminal side outputs will be the normal, jittered outputs that are outputs when the dejitter circuits are not used.

In the transmit direction the FIFO will contain both TP and TN data. In the NRZ mode the TN input must be tied low as the FIFO always accepts TP and TN data when the DART is in the transmit dejitter mode.

Figures 4 through 9 illustrate the various data paths for the four different dejitter modes. Tables 1 and 2 show the control pin settings for the various modes of operation.

LINE SIDE TERMINAL SIDE

Figure 2. Block Diagram of DART Receive Section

Figure 3. Block Diagram of DART Transmit Section

#### RECEIVER FUNCTIONS

### Adaptive Equalizer/AGC

The Adaptive Equalizer/AGC block in the DART receiver is used to recover CMOS level PN rail data from the bipolar B3ZS (or HDB3) encoded input pulses. The AGC in the DART has a dynamic range of 30 dB (35 mV to 1.1 V). Adaptive equalization is included to restore the integrity of the signal after it has been attenuated by the frequency-dependent loss of up to 900 feet of coaxial cable (1300 feet for E3). The buffered, equalized and AGC'd differential receiver signals are provided as outputs on the EYEP and EYEN pins. Internally, this signal is sliced at approximately fifty percent of the peak voltage to generate CMOS-level P and N data.

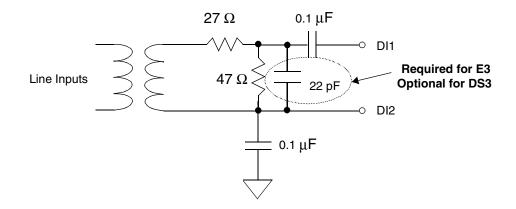

Differential inputs DI1 and DI2 are provided to allow optimum performance of the device in noisy environments. Alternatively, single-ended operation can be used in less critical environments or where the use of a transformer is not desired (the input signal can be AC-coupled via a capacitor). When the differential mode is used, the peak AC voltage measured between DI1 and DI2 is a maximum magnitude of 1.1 volts. For single-ended operation, the voltage measured at DI1 (DI2) relative to the DC bias voltage at DI2 (DI1) is a maximum of  $\pm$ 1.1 peak volts. Since the DART has a sensitive receiver, the 4 dB attenuator shown in Figures 31 and 35 must be used. For input levels larger than 1.1 V peak, a step-down transformer or resistive attenuation should be used (see Figure 35 for suggested attenuator topology - the circuit may be modified to give the desired attenuation). The EQSEL pin should be held low to select an amplitude-controlled equalizer.

### **Clock Recovery**

The PLL-based Clock Recovery block is used to recover a CMOS level clock from the equalized and sliced input pulses. The filters are internal. When DLOS is high and TEST1 is high (data is present), CLKO is the clock recovered from the data. When DLOS is low and TEST1 is high, CLKO is equal to the reference clock (REFCK). When TEST1 is low or TRLBK is low, CLKO is equal to the transmit input clock CLKI.

#### **B3ZS/HDB3** Decoder

The B3ZS/HDB3 Decoder block decodes the B3ZS (or HDB3) encoded line signal and detects coding errors and excessive zeros in the incoming data stream. An active-high pulse is generated on the CV output whenever the input signal violates the B3ZS (or HDB3) encoding sequence for bipolar violations or contains three (four) or more consecutive zeros. An active-low pulse is generated on the  $\overline{\text{EXZ}}$  output when a string of three (four) or more consecutive zeros is detected and it remains low until a one is detected. When in NRZ mode, the CV signal is timed to occur at the terminal-side receiver output at the same time as the bit violating the coding. The CV is approximately 9 cycles after the errored data in the eye pattern monitor. The  $\overline{\text{CODECDIS}}$  control input is used to bypass the decoder  $\overline{\text{NRZ}}$  outputs with PN data at the receiver terminal side outputs; the decoder is always operating so CV and  $\overline{\text{EXZ}}$  are always valid. E3HDB3 high will select HDB3 encoding and decoding.

#### Rx I/O Control

The Rx I/O Control block multiplexes the appropriate signals to the receiver terminal side outputs. The output NRZ data formats include:

- 1. B3ZS (or HDB3) decoded output recovered from the line (RP/RD contains recovered data; RN is held low). This mode is referred to as NRZ mode. CODECDIS high enables the codec.

- 2. Encoded outputs from the Clock Recovery block (RP/RD contains positive data; RN contains negative data). This mode allows an external device to perform the encoding/decoding functions. CODECDIS low enables this mode. This is referred to as PN rail mode.

- 3. Loopback signals from the transmitter terminal side inputs are looped through the digital logic when TRLBK is low. The receiver and clock recovery are bypassed. Data can be either NRZ or PN data.

- 4. AIS DS3-framed format signals when RAIS is low and E3HDB3 is low.

- 5. AIS alternating ones (E3 format) when  $\overline{RAIS}$  is low and E3HDB3 is high.

6. Loopback data from the transmit terminal side inputs are encoded PN data which is looped to the receiver terminal side outputs through the Clock Recovery block, when TEST1 is low. The data input into the transmit terminal side inputs can be unencoded NRZ data or encoded PN data.

See the AIS and Loopback Control Signal Arbitration table (Table 6) for further clarification.

Outputs CLKO and CLKO provide true and inverted clocks for all formats.

The RXDIS signal forces the RP/RD and RN outputs to a low state.

#### **LOS Detector**

The LOS Detector block generates active low outputs which indicate the absence of the line side input signal(s). The  $\overline{\text{DLOS}}$  output goes low when a string of  $175\pm75$  consecutive zeros occurs on the line. This output is reset to high when the detected ones density is in the range of 28 to 33% (or > 33%) for  $175\pm75$  pulses for B3ZS or 20 to 25% (or > 25%) for  $175\pm75$  pulses for HDB3. The  $\overline{\text{ALOS}}$  output goes low when the detected ones density is below 28% for  $175\pm75$  pulses for B3ZS or below 20% for  $175\pm75$  pulses for HDB3.  $\overline{\text{ALOS}}$  is reset to high when the ones density is greater than 33% for B3ZS, or greater than 25% for HDB3, for  $175\pm75$  pulses. Between 28 and 33% for B3ZS, or between 20 and 25% for HDB3, the  $\overline{\text{ALOS}}$  output may toggle between the active and reset states.

The LOS Detector block always uses the receiver outputs which are based upon the receiver inputs DI1 and DI2. When TRBLK is low the Clock Recovery block is still recovering the clock from the receiver inputs. Therefore the DLOS and ALOS signals are still valid. When TEST1 is low the Clock Recovery block will recover the clock from the internally looped transmitter inputs. In this state DLOS and ALOS will be active but may no longer meet the limits given above.

The  $\overline{\text{DLOS}}$  signal meets ITU-T Rec. G.775 for the loss of signal indication. The  $\overline{\text{ALOS}}$  signal is a stricter indication of line degradation and there is no standard related to this function.  $\overline{\text{DLOS}}$  requires a large number of consecutive zeros to give a loss of signal indication. An occasional "1" data bit can prevent the activation of  $\overline{\text{DLOS}}$  even though the data is highly errored. In contrast, the  $\overline{\text{ALOS}}$  signal monitors the data to ensure the data stream has the proper number of ones (ones density), as required by the B3ZS (or HDB3) coding algorithm. For this reason,  $\overline{\text{ALOS}}$  is a stricter indicator of the status of a transmission impairment. The  $\overline{\text{ALOS}}$  and  $\overline{\text{DLOS}}$  outputs may not be reliable if the input cable at the receive interface is left disconnected. This effect is layout dependent. If the data cycles on and off at a slow rate  $\overline{\text{ALOS}}$  and  $\overline{\text{DLOS}}$  may become stuck off (high) and the receiver output clock (CLKO) will also be running at a slow rate.

### TRANSMITTER FUNCTIONS

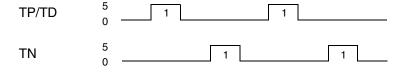

### Tx I/O Control

The Tx I/O Control block multiplexes the appropriate signals for use by the transmitter. The selectable formats include:

- 1. Unencoded Non-Return-to-Zero (NRZ) input data (TP/TD contains unencoded data, TN must be grounded). This is referred to as NRZ mode which is selected when CODECDIS is high.

- 2. B3ZS (or HDB3) encoded PN input data (TP/TD contains positive data, TN contains negative data). CODECDIS pin held low enables this mode (PN rail mode).

- 3. B3ZS (valid for DS3 only) encoded Return-to-Zero (RZ) input data (TP/TD contains positive data, TN contains negative data). The transmit encoder and transmit clock duty cycle control circuits are bypassed. The RZ pulses must contain input pulses that have the correct pulse width. This mode is enabled when RZTXIN is held low. CLKI should be tied low to gate the transmit logic off and CODECDIS should be tied low.

- 4. Looped-back clock and data from the receiver (to the internal transmitter input) when LNLBK is low. Looped data can be either NRZ or PN data. In the NRZ mode the data will first be decoded and then re-encoded. Code violations in the data stream will be lost in the decoding/encoding process. In contrast, the PN mode passes the received data to the transmitter unaltered.

- 5. AIS DS3-framed format signal when TAIS is low and E3HDB3 is low. The encoder is automatically enabled when TAIS is low.

- 6. AIS alternating ones (E3 format) signal when TAIS is low and E3HDB3 is high.

- 7. B3ZS (or HDB3) unencoded, unframed 2<sup>15</sup>/2<sup>23</sup>-1 PRBS generator output when TEST0 is low with the exception of LNLBK and RZ format. The state of the CODECDIS pin does not affect the encoding of the generator output. When TEST0 is set low, the encoder is enabled to ensure that correctly coded data is always transmitted.

The AIS and Loopback Control Arbitration table (Table 6) provides further clarification.

The CLKI pin is the input clock for the formats described in 1, 2 and 7 above. When  $\overline{RZTXIN}$  is low, the CLKI signal is ignored and should be tied low. When  $\overline{LNLBK}$  is active, CLKI is also ignored but does not have to be tied low. For transmitting AIS, the reference clock REFCK is used exclusively. The duty cycle requirement for CLKI and REFCK is  $(50 \pm 10)\%$  with a frequency accuracy of the nominal bit rate  $\pm$  20 ppm. The frequency accuracy of REFCK can be relaxed to the nominal bit rate  $\pm$  100 ppm if the transmit AIS function is not used.

### **Transmit Clock Duty Cycle Control Circuit**

The Transmit Clock Duty Cycle Control circuit relaxes the duty cycle requirement for both REFCK (when using the transmit AIS function) and CLKI. Instead of the usual  $\pm$  5% duty cycle tolerance, the duty cycle tolerance of the DART clocks is  $\pm$  10%. This allows using a less expensive oscillator and eases the board design.

#### B3ZS/HDB3 Encoder

The B3ZS/HDB3 Encoder block encodes the input NRZ mode data so as to be compliant with ANSI Specification T1.102A (ITU-T Rec. G.703 for E3). Figure 25 gives examples of B3ZS encoding (HDB3 is similar). The CODECDIS control pin can be used to disable the encoding function of this block so that the PN rail data is passed through unchanged. CODECDIS must be low when RZTXIN is low.

When TAIS is low and TESTO is high the encoder is disabled and the AIS signal is passed to the output.

When TESTO is low the encoder is enabled and the output of the PRBS data generator is encoded and passed to the output.

The AIS and Loopback Control Signal Arbitration table (Table 6) provides further clarification.

#### **Transmitter Output Control Block**

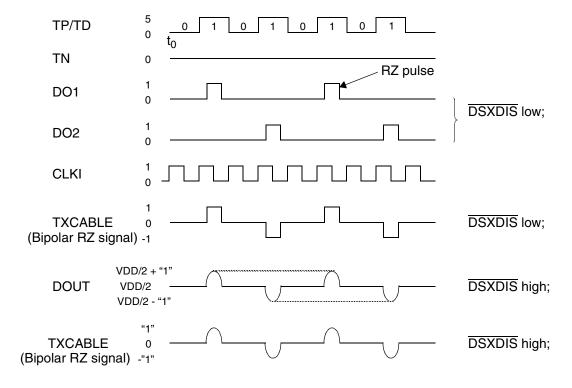

### **DS3 Shaped Output**

The Output Control block contains the pulse shaping circuitry required to transform the B3ZS encoded data into pulses that meet the mask templates and power requirements for DS3 line rates. An internal line driver is included which enables the DART to drive this signal directly from DOUT into the 75 ohm load of the output cable. The  $\overline{\text{ZERO}}$  pin should be held low for all cable lengths.

When the DSXDIS pin is high the DOUT transmitter output is enabled. DOUT is a single-ended output which meets the DS3 mask template. An internal transversal filter is used to create this output.

### E3 Square-Wave Output

Transmit outputs DO1 and DO2 are rectangular CMOS level pulses, generated in conjunction with external passive components, that produce level-translated E3 transmit mask-compliant versions of the input digital signal(s). The AVDDTX pins set the amplitude of these waveforms. The amplitudes will have little variation with V<sub>DD</sub> if the AVDDTX supply voltage used is produced by a three-terminal voltage regulator. The square wave outputs need external load resistors as shown in Figure 31, "External Components, Pin Connections and Power/Ground". An external transformer is required to translate the DO1 and DO2 signals to the appropriate +/- polarity (bipolar) waveform. When using the DO1 and DO2 outputs, power dissipation is minimal in the transmitter when no data is being transmitted.

### Waveform Control Pins

When  $\overline{DSXDIS}$  is high, the DOUT output is enabled. When  $\overline{DSXDIS}$  is low, the DO1/DO2 outputs are enabled. Figure 26 shows idealized transmitter waveforms for both output modes.

#### TRANSMITTER CALIBRATION PLL

The calibration PLL calibrates an internal delay line by locking to the REFCK signal. The resulting control voltages are filtered and used in delay lines in other parts of the device.

An external capacitor connected from TPLLC to the proper analog ground is required for filtering the internal calibration PLL control voltages. The filtered voltages are used to calibrate the transmitter transversal filter circuit (see Figure 31 and Note 7). The transmitted pulse width can be changed by adding an external resistor from TPLLC to either AVDDTX (which narrows the pulse) or AGNDTX (which widens the pulse).

#### LOOPBACKS AND AIS INSERTION

The loopback control signals enable input signals of the DART to be looped back on both the line side and terminal side. The AIS and Loopback Control Signal Arbitration table (Table 6) illustrates the various control signals and related DART outputs.

### **Internal Digital Transmit Terminal Side Loopback**

When TRLBK (terminal loopback) is low, the TP/TD, TN and CLKI inputs are directly looped back to the RP/RD, RN and CLKO pins via the Rx I/O Control Block (all-digital signal path). The normal transmit path is active in this state. The state of CODECDIS does not affect the terminal loopback path.

### **Internal Analog Receive Line Side Loopback**

When LNLBK is low and CODECDIS is high, the DI1/DI2 signals are looped back to the DOUT or DO1/DO2 outputs via the Adaptive Equalizer/AGC, Clock Recovery, B3ZS/HDB3 Decoder, Rx I/O Control, Tx I/O Control, B3ZS/HDB3 Encoder and Output Control blocks. Since the data will be processed through the decoder then re-encoded in this mode, any receiver code violations will not be propagated to the transmitter output.

When LNLBK is low and CODECDIS is low, the DI1/DI2 signals are looped back to the DOUT or DO1/DO2 outputs via the Adaptive Equalizer/AGC, Clock Recovery, Rx I/O Control, Tx I/O Control and Output Control blocks. The decoder and encoder data paths are bypassed in this mode, but the CV and EXZ signals are valid and the normal receiver path is active. Received data will propagate to the transmitter output with no alteration.

The above two loopbacks may be operated independently or simultaneously. It should be noted that when TRLBK is active, the CV, DLOS, EXZ and ALOS output signals will still respond to the line input data signals applied at pins DI1 and DI2 and will be valid signals. As stated previously, the normal receive path is active during LNLBK.

### **Internal Analog Transmit Terminal Side Loopback**

For the DART device, when TEST1 is low and CODECDIS is high, the transmit terminal input data will loop back through the Encoder, Auxiliary Loopback Control, Clock Recovery, Decoder and Rx I/O Control blocks as shown in Figures 4 through 11. When TEST1 is low and CODECDIS is low, the transmit terminal input data will loop back through the auxiliary loopback control, clock recovery and Rx I/O control blocks, as shown in Figures 4 through 11. When TAIS is active low at the same time as TEST1 is active low, AIS will loop through this path and be provided at the output on the receiver terminal side.

#### **DS3/E3 AIS Generator**

The DS3/E3 AIS Generator block generates a DS3 (E3) alarm indication signal (AIS) compliant with Bellcore Specification TR-TSY-000191 (ITU-T Rec. G.775) on the line or terminal sides of the device. The AIS outputs are selected with TAIS or RAIS. This block generates DS3 or E3 format AIS only. AIS will override the loop-

back commands. The reference clock REFCK is used to generate both AIS (framed for DS3) and PRBS transmitted data. The required duty cycle for REFCK is  $(50 \pm 10)\%$  and the frequency accuracy is the nominal bit rate  $\pm$  20 ppm (as required by the standards). The transmit clock duty cycle control circuit will generate a transmit clock from REFCK that has the proper duty cycle.

#### **TESTABILITY**

# 2<sup>15</sup>/2<sup>23</sup>-1 PRBS Generator

The  $2^{15}/2^{23}$ -1 PRBS (Pseudo-Random Binary Sequence) Generator and PRBS Analyzer blocks provide diagnostic capability. When the  $\overline{\text{TEST0}}$  pin is low, the output of the PRBS generator is driven through the Tx I/O Control, B3ZS Encoder and Output Control blocks to either DOUT when  $\overline{\text{DSXDIS}}$  is high, or DO1/DO2 when  $\overline{\text{DSXDIS}}$  is low. The encoder is always enabled when  $\overline{\text{TEST0}}$  is low, regardless of the state of the  $\overline{\text{CODECDIS}}$  pin. The analyzer works in either NRZ mode or PN mode.

## 2<sup>15</sup>/2<sup>23</sup>-1 PRBS Analyzer

The PRBS Analyzer monitors the output of the B3ZS/HDB3 decoder block. If the output signal conforms to the correct  $2^{15}/2^{23}$ -1 pattern the BIST output will go high. The PRBS Analyzer always functions, regardless of the state of the TEST0 pin. Whenever a valid  $2^{15}/2^{23}$ -1 pattern (this pattern can contain a significant number of errors and still be valid) appears at the receiver outputs the BIST pin will go high. The BIST signal operates as a PRBS synchronization indicator for the incoming received data. The RXERR output of the device goes high whenever a received bit is in error for the selected PRBS pattern and the BIST pin is high.

The analyzer runs regardless of the state of the CODECDIS pin, since the PRBS analyzer is supplied with decoded data by the Decoder at all times. The Generator/Analyzer combination can be used in conjunction with both external and internal line-side loopbacks for diagnostic purposes. The combination of both TESTO and TEST1 pins being low sends signals through all of the data path blocks in the device. This is particularly useful for manufacturing test.

Setting the  $\overline{PAT23}$  pin low selects the  $2^{23}$ -1 pattern operation. Setting the  $\overline{PAT23}$  pin high selects the  $2^{15}$ -1 pattern operation.

### INPUT REFERENCE CLOCK

A TTL level input clock at the E3 or DS3 rate must be applied to the REFCK input for the DART device to operate. This will typically be supplied by a local oscillator on the board. The tolerance required is  $\pm$  100 ppm for operation when the DS3 AIS generator is not used. To generate a valid AIS transmit signal a frequency tolerance of  $\pm$  20 ppm is required. The required duty cycle is  $(50 \pm 10)\%$ . REFCK can be the same signal as CLKI, if CLKI is driven from a local card oscillator. If loop timing is being performed REFCK can be the same signal as CLKI, if a provision is made to multiplex between the local card oscillator and the dejittered recovered clock; the logical "or" of  $\overline{\text{ALOS}}$  and  $\overline{\text{DLOS}}$  should be part of the mux control logic. When these signals are active, it may indicate the recovered clock is inaccurate and the local card oscillator should be used.

#### **DEJITTER FIFO/DEJITTER PLL OPERATION**

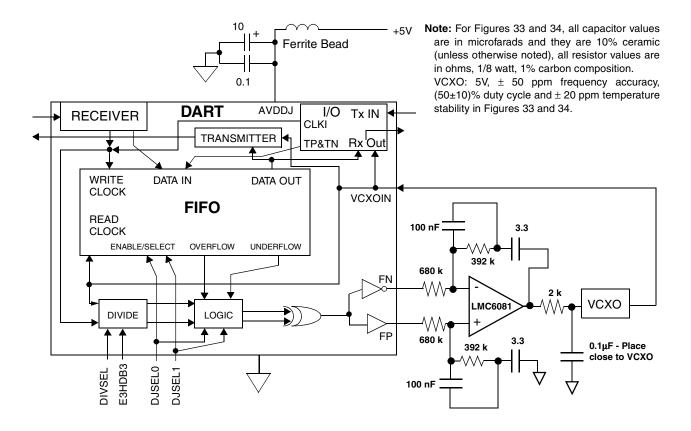

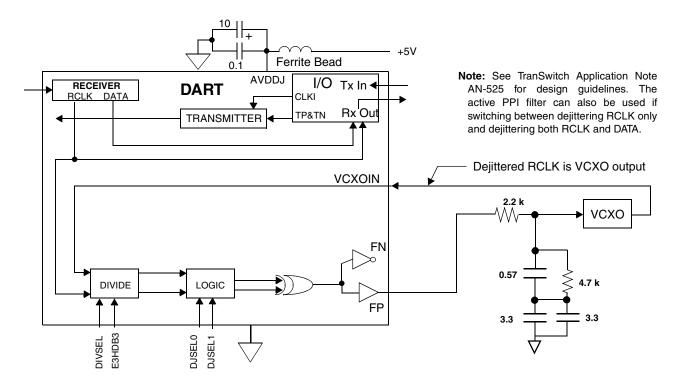

The data paths and operation of the Dejitter PLL and Dejitter FIFO portions of the DART device are shown in Figures 2 through 11. Figures 2 and 3 show the block diagrams of the DART receive and transmit sections, respectively, with dejitter circuits included. Figures 4 through 11 show the simplified Dejitter PLL/FIFO data paths for each operating mode of the DART device. Note that use of the LNLBK pin is invalid when in the dejitter mode and PN mode (see Figure 4). The VCXO interface diagrams in Figures 33 and 34 show the external component connections for the DART dejitter PLL. TranSwitch Application Note AN-525, "Dejitter Circuit for Data Transmission Using the Recovered Clock", Document No. TXC-02050-AN2 can be used as an aid in the design of a recovered clock dejitter only circuit, which is shown in Figures 6 and 7.

There are four distinct modes of operation of the Dejitter PLL/Dejitter Buffer. The first mode involves dejittering both the recovered clock and receive data. In this mode either P and N data is dejittered or NRZ data (i.e. RP/RD) and associated CVs are dejittered. Figures 4 and 5 show these paths. The second mode involves dejittering the recovered clock. In this mode the dejitter FIFO is gated off. The dejitter PLL uses the recovered clock to allow recovered clock dejittering. This is shown in Figures 6 and 7. The third mode involves dejittering both the transmit clock and the transmit data. Both TP/TD and TN are fed into the FIFO regardless of the state of CODECDIS. TN should be tied low when the NRZ mode is being used. Figures 8 and 9 show the data paths for CLKI, TP/TD and TN dejittering. The dejitter FIFO and dejitter PLL are bypassed in transmit dejitter mode if LNLBK is active (low). The looped recovered clock and data signals will not be dejittered. The fourth mode bypasses both dejitter circuits. Figures 10 and 11 show the data paths when the dejitter circuits are not used.

Figures 33 and 34 show a simplified block diagram of the dejitter circuits in the DART and the associated external circuits. It can be seen from these figures that the phase detector is a simple exclusive-or gate. The logic block preceding the exclusive-or gate contains logic that performs frequency acquisition to ensure that the dejitter PLL will lock to the correct clock frequency under all frequency offset conditions.

The active filter is necessary when using the FIFO because any static phase offset in the PLL loop will cause the FIFO fill level to be offset from the nominal half-full level. For this reason the external operational amplifier used should have a low input-offset voltage. The active filter can also be used when dejittering only the recovered clock. However, since static phase offsets are not important in this mode, the passive external RC filter can be used. When operating in transmit dejitter mode, the transmission will stop if the VCXO stops (the VCXO output is being used as the transmit clock in this mode).

Tables 1 and 2 that follow Figure 11 show the functions of the dejitter control pins.

\*Note: PPI is an abbreviation for Proportional Plus Integral

Figure 4. Receive Side Dejitter FIFO Using PN Data (DJSEL0=0, DJSEL1=0)

Figure 5. Receive Side Dejitter FIFO Using NRZ Output (DJSEL0=0, DJSEL1=0)

Figure 6. Receive Side Clock Dejitter Only; NRZ Mode (DJSEL0=0, DJSEL1=1)

Figure 7. Receive Side Clock Dejitter Only; PN Mode (DJSEL0=0, DJSEL1=1)

Figure 8. Transmit Side Dejitter FIFO; NRZ Mode (DJSEL0=1, DJSEL1=0)

Figure 9. Transmit Side Dejitter FIFO; PN Mode (DJSEL0=1, DJSEL1=0)

Figure 10. Normal Operation; PN Mode (DJSEL0=1, DJSEL1=1)

Figure 11. Normal Operation; NRZ Mode (DJSEL0=1, DJSEL1=1)

| CODECDIS       | DJSEL0 | DJSEL1 | Dejitter FIFO<br>Inputs/Outputs | Dejitter PLL<br>Reference<br>Clock Source | Device Outputs                        |

|----------------|--------|--------|---------------------------------|-------------------------------------------|---------------------------------------|

| 1              | 0      | 0      | RP and CV                       | RCLK                                      | Dejittered CLKO, RP and CV            |

| 0              | 0      | 0      | RP and RN                       | RCLK                                      | Dejittered CLKO, RP and RN            |

| X <sup>1</sup> | 0      | 1      | FIFO gated off                  | RCLK                                      | Normal, jittered outputs <sup>2</sup> |

| 1              | 1      | 0      | TP and TN <sup>3</sup>          | CLKI                                      | Dejittered Transmit Data              |

| 0              | 1      | 0      | TP and TN                       | CLKI                                      | Dejittered DOUT or DO1and DO2         |

| X <sup>1</sup> | 1      | 1      | FIFO gated off <sup>4</sup>     | PLL gated off <sup>4</sup>                | Normal, jittered outputs              |

**Table 1. Dejitter Control Signals**

#### Notes:

- 1. X = don't care.

- 2. The normal data paths are enabled. The dejittered recovered clock is the output of the VCXO. CLKO is the normal, jittery recovered clock signal.

- 3. Tie TN low in NRZ mode.

- 4. All dejitter circuits are disabled. All dejitter data paths are bypassed.

Table 2. Dejitter PLL Divide Control

| E3HDB3 | DIVSEL | Dejitter PLL Internal Divide-By |

|--------|--------|---------------------------------|

| 0      | 0      | 1024                            |

| 0      | 1      | 2048                            |

| 1      | 0      | 512                             |

| 1      | 1      | 1024                            |

Note: The dividers are located directly before the frequency discriminator in both the reference clock path and the PLL feedback path.

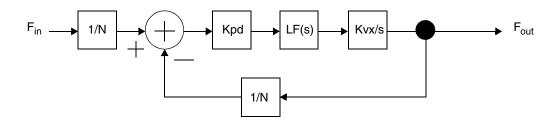

From the table above it is seen that the Divide Factor (N) is controlled by the DIVSEL and E3HDB3 pins. The PLL open gain is inversely proportional to the divide factor; the divide factor is application dependent. The divide factor in combination with the VCXO gain and the external filter frequency response is used to determine the stability, transient response, and bandwidth of the dejitter PLL. The greatest variability of the these three factors is the VCXO gain. Attention should be paid to the VCXO minimum and maximum frequency deviation range which is not often specified by the VXCO manufacturer. A conservative number should be used for the VCXO gain to ensure the design goals are met.

The PLL behavior is described by the following equations:

VCXO gain = Kvx/s = [(Deviation\_range \* Center Frequency \* 2 \* pi) / 4] / s.

Phase Detector gain = Kpd = [5, 10]/(2 \* pi \* N); 10 for differential filter, 5 for single-ended filter.

Active Filter Transfer Function =  $LF(s) = [1 / (s^* R1 * C1) + [R2 / (s * R1 * R2 * C2) + R1];$  single-ended version of the differential filter shown in Figure 33. The block diagram of the Dejitter PLL is shown in the Figure 12.

Figure 12. Dejitter PLL Block Diagram

From the block diagram the following equations can be derived.

The Dejitter PLL open loop transfer function = Loop(s) = Kpd \* LF(s) \* Kvx/s.

The Dejitter PLL closed loop transfer function = PLL(s) = (Loop(s) / (1 + Loop(s))).

For well-behaved operation the open loop frequency response must have less than 135 degrees of phase shift when the loop gain crosses the unity gain line of the Bode response. There are two primary sources of phase shift. The first is the VCXO (1/s) and the second is the external filter (LF(s)). Application note AN-525 goes into greater detail for designing a dejitter PLL using a passive filter. Changes to the design equations of AN-525 when using an active filter are straightforward. There are MATLAB and Mathcad routines to help in designing the Dejitter PLL for a specific application. Contact the TranSwitch applications group for additional information and the analysis tools.

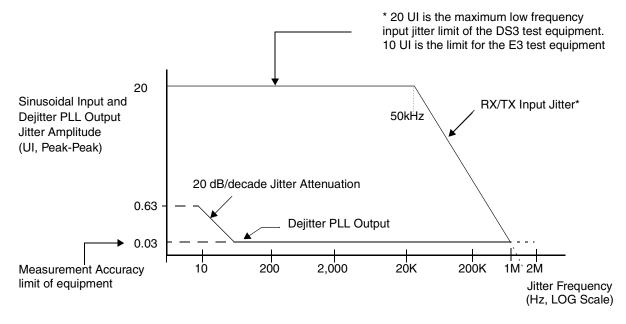

Figure 13 shows the measured results of the DART Dejitter PLL at DS3 using the external filter values shown in Figure 33. The upper curve of the figure shows the jitter on the input signal to the DART; for the receiver the jitter is into DI1/DI2 and for the transmitter the jitter is on TP/TD and CLKI. The upper curve is actually the receiver jitter tolerance curve.

The lower curve shows the measured dejitter PLL output jitter. For the receive side the jitter was measured at the receiver terminal side. For the transmitter the jitter was measured at the transmitter line side.

From the figure we see that at the beginning measurement frequency of 10 Hz (lowest measurement frequency of the equipment) the measured output jitter is 0.63 UI for input jitter of 20 UI. The measured output jitter decreases at 20 dB/decade until it reaches a level of 0.03 UI for the receiver; 0.03 UI is the measurement accuracy of the test equipment. The measured output jitter level for the transmitter is 0.04 UI; 0.04 UI is the generated jitter of the transmitter with a jitterless input clock.

The dejitter PLL output jitter measurements were taken at three different frequency offsets. The frequencies

were 44.736 MHz and 44.736 MHz +/- 40 ppm. The supply voltage was varied from 4.7 to 5.3 volts. The measurement temperatures were -40  $^{\circ}$ C, 25  $^{\circ}$ C, and 85  $^{\circ}$ C. The output jitter curve shown represents the worst case measurement for the test conditions.

No failures to phase lock were experienced for any of the tests performed and there were no cycle slips.

It should be noted that the VCXO is the biggest source of variability of the PLL response and particular attention should be paid to its characteristics.

Notes: Unit Interval (UI) = 1/(DS3 System Clock Frequency).

Test conditions:  $V_{DD}=5V$  +/- 0.5V,  $T_A=-40^{\circ}C$ ,  $0^{\circ}C$ ,  $85^{\circ}C$ , B3ZS coding,  $2^{15}-1$  data pattern.

Dejitter Clock Frequency Offset from DS3 Nominal = -40ppm, 0ppm, 40ppm.

Figure 13. Measured Output Jitter of Dejitter PLL at DS3 (E3 results better or equal to)

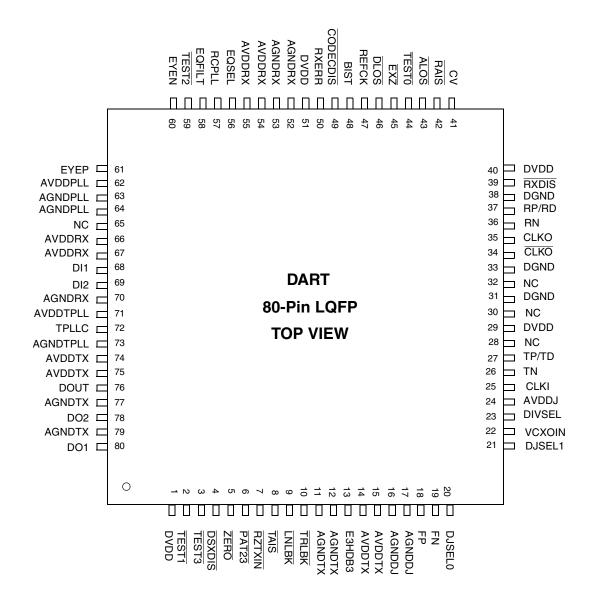

### **PIN DIAGRAM**

Figure 14. DART TXC-02030 Pin Diagram

# **PIN DESCRIPTIONS**

The following tables describe the 80 pins (leads) of the DART device, grouped by functional category.

# **POWER SUPPLY AND GROUND**

| Symbol   | Pin No.              | I/O/P* | Туре | Name/Function                                                                                                                                                                           |

|----------|----------------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AVDDTX   | 14<br>15<br>74<br>75 | Р      |      | Analog VDD Transmit: + 5 volt supply ± 5%.                                                                                                                                              |

| AVDDRX   | 54<br>55<br>66<br>67 | Р      |      | Analog VDD Receive: + 5 volt supply ± 5%.                                                                                                                                               |

| AVDDTPLL | 71                   | Р      |      | Analog VDD Transmit PLL: + 5 volt supply $\pm$ 5%.                                                                                                                                      |

| DVDD     | 1<br>29<br>40<br>51  | Р      |      | Digital VDD: + 5 volt supply ± 5%.                                                                                                                                                      |

| AVDDPLL  | 62                   | Р      |      | <b>Analog VDD Receive PLL:</b> + 5 volt supply $\pm$ 5%.                                                                                                                                |

| AVDDJ    | 24                   | Р      |      | Analog VDD Dejitter: + 5 volt supply $\pm$ 5%. Leave as NC (No Connect) if the dejitter function is not being used. Use a separate power filter as shown in Figures 31, 32, 33, and 34. |

| AGNDTX   | 11<br>12<br>77<br>79 | Р      |      | Analog Ground Transmit: 0 volt reference.                                                                                                                                               |

| AGNDRX   | 52<br>53<br>70       | Р      |      | Analog Ground Receive: 0 volt reference.                                                                                                                                                |

| AGNDTPLL | 73                   | Р      |      | Analog Ground Transmit PLL: 0 volt reference.                                                                                                                                           |

| DGND     | 31<br>33<br>38       | Р      |      | Digital Ground: 0 volt reference.                                                                                                                                                       |

| AGNDPLL  | 63<br>64             | Р      |      | Analog Ground Receive PLL: 0 volt reference.                                                                                                                                            |

| AGNDDJ   | 16<br>17             | Р      |      | Analog Ground Dejitter: 0 volt reference.                                                                                                                                               |

\*Note: I = Input; O = Output; P = Power

# **RECEIVE INTERFACE**

| Symbol | Pin No. | I/O/P | Type * | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|---------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DI1    | 68      | -     | Analog | Data In 1, Data In 2: Line side inputs. For single-ended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DI2    | 69      | I     | Analog | operation DI1 or DI2 must be AC-coupled to ground via a capacitor. For differential operation both inputs can be tied directly to a transformer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| EYEP   | 61      | 0     | Analog | Positive Eye Pattern Monitor: Monitors non-inverted AGC'd and equalized output from Adaptive Equalizer/AGC block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EYEN   | 60      | 0     | Analog | Negative Eye Pattern Monitor: Monitors inverted AGC'd and equalized output from Adaptive Equalizer/AGC block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| EXZ    | 45      | 0     | CMOS   | Excessive Zeros: This pin is low for B3ZS coding when three or more consecutive zeros occur in the input data stream. This pin is low for HDB3 coding for four or more consecutive zeros in the data. Ignore when DLOS is active (low).                                                                                                                                                                                                                                                                                                                                                                                                    |

| CV     | 41      | 0     | CMOS   | Coding Violation: This pin is high when incoming data violates B3ZS (or HDB3) coding for bipolar violations or when three (or four) or more consecutive zeros occur in the input data stream. Valid regardless of the state of CODECDIS. Ignore when DLOS is active (low).                                                                                                                                                                                                                                                                                                                                                                 |

| DLOS   | 46      | 0     | CMOS   | <b>Digital LOS:</b> This pin is low when 175 $\pm$ 75 consecutive zeros appear in the incoming data stream. Cleared for B3ZS when ones pulse density is in the range of 28 to 33% (or > 33%) for 175 $\pm$ 75 pulses. Cleared for HDB3 when ones pulse density is in the range of 20 to 25% (or > 25%) for 175 $\pm$ 75 pulses. Valid regardless of the state of $\overline{\text{TRLBK}}$ **. May be invalid if the input cable at the receive interface is left disconnected (see LOS Detector section).                                                                                                                                 |

| ALOS   | 43      | 0     | CMOS   | <b>Analog LOS:</b> For B3ZS this pin is low when pulse density is < 28% for $175 \pm 75$ pulses. Cleared when pulse density is > 33% for $175 \pm 75$ pulses. ALOS may toggle between active and inactive when pulse density is between 28 and 33%. For HDB3 this pin is low when pulse density is < 20% for $175 \pm 75$ pulses. Cleared when pulse density is > 25% for $175 \pm 75$ pulses. ALOS may toggle between active and inactive when pulse density is between 20 and 25%. Valid regardless of the state of TRLBK**. May be invalid if the input cable at the receive interface is left disconnected (see LOS Detector section). |

| RP/RD  | 37      | 0     | CMOS   | Receiver Positive/Data: Generates B3ZS (or HDB3) decoded NRZ, combined data (CODECDIS high) or positive rail data (CODECDIS low). Held low when RXDIS is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Symbol | Pin No. | I/O/P | Type * | Name/Function                                                                                                                                                                                                                             |

|--------|---------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RN     | 36      | 0     | CMOS   | Receiver Negative: Generates negative rail data when CODECDIS is low. Held low when CODECDIS is high and/or when RXDIS is low.                                                                                                            |

| CLKO   | 35      | 0     | CMOS   | Receiver Clock Out: Receiver output clock.                                                                                                                                                                                                |

| CLKO   | 34      | 0     | CMOS   | Receiver Clock Out Inverted: Receiver inverted output clock.                                                                                                                                                                              |

| BIST   | 48      | 0     | CMOS   | Built-In Self Test Output: This pin is high when a valid unframed 2 <sup>15</sup> -1 PRBS or 2 <sup>23</sup> -1 PRBS pattern is detected. PAT23 pin set low selects 2 <sup>23</sup> -1 PRBS. Valid for both decoded NRZ and PN rail data. |

| RXERR  | 50      | 0     | CMOS   | PRBS Analyzer Error: This pin is high when an invalid PRBS pattern bit is detected.                                                                                                                                                       |

| EQFILT | 58      | I     | Analog | Equalizer Filter: Filter pin for adjusting equalizer control.                                                                                                                                                                             |

| RCPLL  | 57      | I     | Analog | Clock Recovery External Filter: Pin for external clock recovery PLL filter adjustment. See Figure 31.                                                                                                                                     |

| TEST3  | 3       | I     | TTLp   | <b>Test In 3:</b> TranSwitch use only. Tie to AVDDRX through a 2 $k\Omega$ resistor. See Figure 31.                                                                                                                                       |

#### Notes:

## TRANSMIT INTERFACE

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                           |

|--------|---------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TP/TD  | 27      | I     | TTLp   | Transmitter Positive/Data: Input pin for unencoded NRZ, combined data (CODECDIS high) or positive rail data (CODECDIS low).                                                             |

| TN     | 26      | I     | TTLp   | Transmitter Negative: Input pin for negative rail data when CODECDIS is low. Must be tied low when CODECDIS is high.                                                                    |

| CLKI   | 25      | I     | TTLp   | <b>Transmitter Input Clock:</b> Transmitter clock input. The frequency accuracy of this input clock must be the nominal bit rate $\pm$ 20 ppm. The duty cycle must be $(50 \pm 10)\%$ . |

| TPLLC  | 72      | I     | Analog | <b>Transmit Filter Capacitor:</b> Capacitor pin for filtering calibration PLL voltages (see Figure 31 and following notes for proper connection).                                       |

| DO1    | 80      | 0     | Analog | Data Out Positive: The output on this pin is a rectangular positive pulse when DSXDIS is low. This pin is a low impedance to AGNDTX when DSXDIS is high.                                |

<sup>\*</sup> See Input and Output Parameters section for digital Type definitions.

<sup>\*\*</sup>For TRLBK low (active), this output signal responds to the receiver input at the DI1 and DI2 pins.

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                            |

|--------|---------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| DO2    | 78      | 0     | Analog | Data Out Negative: The output on this pin is a rectangular negative pulse when DSXDIS is low. This pin is a low impedance to AGNDTX when DSXDIS is high. |

| DOUT   | 76      | 0     | Analog | Data Out: The output on this pin is DSX filtered single-ended when DSXDIS is high. This pin is a high impedance when DSXDIS is low.                      |

# **CONTROL/REFERENCE PINS**

| Symbol        | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|---------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAIS          | 42      | I     | TTLp | Receive AIS Enable: This pin enables generation of framed DS3 AIS on the receiver outputs when E3HDB3 is low. This pin enables E3 alternating ones AIS when E3HDB3 is high (See Note below). This pin is active low.                                                                                                                                                             |

| RXDIS         | 39      | 1     | TTLp | Receive Output Disable: This pin forces the receiver RP/RD and RN outputs to a low state. This pin is active low.                                                                                                                                                                                                                                                                |

| TRLBK         | 10      | _     | TTLp | <b>Terminal Loopback Enable:</b> This pin enables a digital loopback from the transmitter inputs to the receiver terminal side outputs via the Tx I/O Control block, the Loopback Controls block and the Rx I/O Control block. Transmitter output is in the normal condition. See the Loopback and AIS Insertion section for more thorough descriptions. This pin is active low. |

| <u> ENLBK</u> | 9       |       | TTLp | Line Loopback Enable: This pin enables an internal line loopback from the DI1/DI2 inputs to the DOUT or DO1/DO2 outputs. See the Loopback and AIS Insertion section for more thorough descriptions. This pin is active low.                                                                                                                                                      |

| RZTXIN        | 7       | I     | TTLp | Transmit RZ Input Enable: When this pin is low, the device accepts encoded return-to-zero pulses (properly timed and of correct width) on the transmitter TP/TD and TN inputs. CLKI and CODECDIS must be held low. This pin is active low.                                                                                                                                       |

| CODECDIS      | 49      | I     | TTLp | Codec Disable: When this pin is low, the device bypasses the internal encoder and decoder functions. The decoder remains functional, so that CV and $\overline{EXZ}$ are always valid. This pin is active low.                                                                                                                                                                   |

| ZERO          | 5       | I     | TTLp | <b>Transmit Zero Cable Enable:</b> Hold low for all cable lengths at DS3. This pin is a don't care for E3 operation using DO1 and DO2.                                                                                                                                                                                                                                           |

| TEST2         | 59      | I     | TTLp | <b>Test In 2:</b> TranSwitch use only. Tie to AVDDRX through a 2 $k\Omega$ resistor. See Figure 31.                                                                                                                                                                                                                                                                              |

| TAIS          | 8       | I     | TTLp | <b>Transmit AIS Enable:</b> This pin enables generation of framed DS3 AIS on the transmitter outputs when E3HDB3 is low. This pin enables generation of E3 alternating ones AIS when E3HDB3 is high. (See Note below). This pin is active low.                                                                                                                                   |

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                    |

|--------|---------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DSXDIS | 4       | I     | TTLp | <b>Transmit DSX Output Disable:</b> Disables DOUT output and enables DO1/DO2 differential square wave outputs. This pin is active low.                                                                                                                                                                                           |

| TEST0  | 44      | I     | TTLp | <b>Test In 0:</b> This pin enables an internal PRBS generator (unframed 2 <sup>15</sup> -1 or 2 <sup>23</sup> -1 PRBS generator). Valid for NRZ or PN rail mode. The encoder is used whenever TEST0 is active. See the Block Diagram Description, Testability section. This pin is active low.                                   |

| TEST1  | 2       | I     | TTLp | <b>Test In 1:</b> This pin enables an internal analog terminal side loopback from the TP/TD and TN signals to the receiver outputs. See the Block Diagram Description, Testability section. This pin is active low.                                                                                                              |

| REFCK  | 47      | I     | TTLp | <b>Reference Clock Input:</b> Input reference clock at the system frequency required for device operation, namely 34.368 MHz for E3, 44.736 MHz for DS3. The required tolerance is the nominal frequency $\pm$ 20 ppm when AIS generation is required and $\pm$ 100 ppm otherwise. The duty cycle tolerance is $(50 \pm 10)\%$ . |

| PAT23  | 6       | I     | TTLp | PRBS 2 <sup>23</sup> Select: This pin, set low, selects a 2 <sup>23</sup> -1 pattern for the PRBS analyzer and generator. This pin, set high, selects a 2 <sup>15</sup> -1 pattern for the analyzer and generator. The encoder is enabled regardless of the state of CODECDIS.                                                   |

| E3HDB3 | 13      | I     | TTL  | HDB3 or B3ZS Select: This pin, set high, selects HDB3 encoding/decoding. This pin, set low, selects B3ZS encoding/decoding. This TTL pin has no internal pull-up resistor.                                                                                                                                                       |

| DJSEL0 | 20      | I     | TTLp | <b>Dejitter Block Control:</b> First of two control pins which control the dejitter buffer/dejitter PLL modes. See "Dejitter Control Signals" Table 1.                                                                                                                                                                           |

| DJSEL1 | 21      | I     | TTLp | <b>Dejitter Block Control:</b> Second of two control pins which control dejitter buffer/dejitter PLL modes. See "Dejitter Control Signals" Table 1.                                                                                                                                                                              |

| DIVSEL | 23      | I     | TTLp | <b>Divide Select:</b> Selects the divisor in the divide-by block in the dejitter PLL. See "Dejitter PLL Divide Control" Table 2.                                                                                                                                                                                                 |

| EQSEL  | 56      | I     | TTLp | <b>Equalizer select pin:</b> Set low to select the amplitude-controlled equalizer.                                                                                                                                                                                                                                               |

Note: DS3 AIS is defined as a valid M-frame with proper subframe structure. The data payload is a 1010 ... sequence starting with a 1 after each overhead bit. Overhead bits are as follows: F0=0, F1=1, M0=0, M1=1; C-bits are set to 0; X-bits are set to 1; and P-bits are set for valid parity.

# **MISCELLANEOUS PINS**

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                            |

|--------|---------|-------|------|----------------------------------------------------------------------------------------------------------|

| FP     | 18      | 0     | CMOS | Filter Charge-pump Positive: This pin provides a 2 mA driver output to the external dejitter PLL filter. |

| FN     | 19      | 0     | CMOS | Filter Charge-pump Negative: This pin provides a 2 mA driver output to the external dejitter PLL filter. |

| VCXOIN | 22      | I     | TTLp | <b>External VCXO:</b> This pin is used to input the dejittered clock from the external VCXO output.      |

# **NO CONNECTS**

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                            |

|--------|---------|-------|------|----------------------------------------------------------|

| NC     | 28      |       |      | No Connect: NC pins are not to be connected, not         |

|        | 30      |       |      | even to another NC pin, but must be left floating. Oper- |

|        | 32      |       |      | ation may be impaired or the device may be damaged       |

|        | 65      |       |      | if NC pins are connected.                                |

# **ABSOLUTE MAXIMUM RATINGS AND ENVIRONMENTAL LIMITATIONS**

| Parameter                          | Symbol          | Min      | Max                   | Unit   | Conditions                     |

|------------------------------------|-----------------|----------|-----------------------|--------|--------------------------------|

| Supply voltage                     | $V_{DD}$        | -0.3     | +7.0                  | V      | Note 1                         |

| DC input voltage                   | V <sub>IN</sub> | -0.3     | V <sub>DD</sub> + 0.3 | V      | Note 1                         |

| Ambient operating temperature      | T <sub>A</sub>  | -40      | 85                    | °C     | 0 ft/min linear airflow        |

| Storage temperature range          | T <sub>S</sub>  | -55      | 150                   | °C     | Note 1                         |

| Component Temperature x Time       | TI              |          | 270 x 5               | °C x s | Note 1                         |

| Moisture Exposure Level            | ME              | 5        |                       | Level  | per EIA/JEDEC<br>JESD22-A112-A |

| Relative Humidity, during assembly | RH              | 30       | 60                    | %      | Note 2                         |

| Relative Humidity, in-circuit      | RH              | 0        | 100                   | %      | non-condensing                 |

| ESD Classification                 | ESD             | absolute | value 2000            | V      | Note 3                         |

#### Notes:

- 1. Conditions exceeding the Min or Max values may cause permanent failure. Exposure to conditions near the Min or Max values for extended periods may impair device reliability.

- 2. Pre-assembly storage in non-drypack conditions is not recommended. Please refer to the instructions on the "CAUTION" label on the drypack bag in which devices are supplied.

- 3. Test method for ESD per MIL-STD-883D, Method 3015.7.

# THERMAL CHARACTERISTICS

| Parameter                               | Min | Тур | Max | Unit | Test Conditions         |

|-----------------------------------------|-----|-----|-----|------|-------------------------|

| Thermal resistance: junction to ambient |     | 50  |     | °C/W | 0 ft/min linear airflow |

## **POWER REQUIREMENTS**

| Parameter       | Min  | Тур | Max  | Unit | Test Conditions                                    |

|-----------------|------|-----|------|------|----------------------------------------------------|

| $V_{DD}$        | 4.75 | 5.0 | 5.25 | V    |                                                    |

| I <sub>DD</sub> |      | 150 | 160  | mA   | Outputs terminated                                 |

| P <sub>DD</sub> |      | 750 | 840  | mW   | Inputs switching,<br>V <sub>DD</sub> =5.25 for Max |

# **INPUT AND OUTPUT PARAMETERS**

# **Input Parameters for TTLp**

| Parameter         | Min   | Тур | Max                   | Unit | Test Conditions         |

|-------------------|-------|-----|-----------------------|------|-------------------------|

| V <sub>IH</sub>   | 2.0   |     | V <sub>DD</sub> + 0.3 | V    |                         |

| V <sub>IL</sub>   | - 0.3 |     | 0.8                   | V    |                         |

| I <sub>IH</sub>   |       |     | - 10                  | μΑ   | V <sub>DD</sub> = 5.25V |

| I <sub>IL</sub>   |       |     | 550                   | μΑ   | V <sub>DD</sub> = 5.25V |

| Input Capacitance |       |     | 10                    | pF   |                         |

Note: All TTL input pins with the exception of the E3HDB3 pin have an internal pull-up resistor.

# **Output Parameters for CMOS**

| Parameter         | Min                   | Тур | Max   | Unit | Test Conditions           |

|-------------------|-----------------------|-----|-------|------|---------------------------|

| V <sub>OH</sub>   | V <sub>DD</sub> - 0.5 |     |       | V    | 4 mA source               |

| V <sub>OL</sub>   |                       |     | 0.5   | V    | 4 mA sink                 |

| I <sub>OH</sub>   |                       |     | - 4.0 | mA   | V <sub>DD</sub> = 4.75V   |

| I <sub>OL</sub>   |                       |     | 4.0   | mA   | V <sub>DD</sub> = 4.75V   |

| t <sub>RISE</sub> | 1.7                   | 2.7 | 4.2   | ns   | C <sub>LOAD</sub> = 15 pF |

| t <sub>FALL</sub> | 1.9                   | 2.8 | 4.1   | ns   | C <sub>LOAD</sub> = 15 pF |

Note: For driving traces greater than 2 inches or driving multiple loads, the DART digital outputs should be buffered.

## TIMING CHARACTERISTICS

### **E3 LINE SIDE TIMING CHARACTERISTICS**

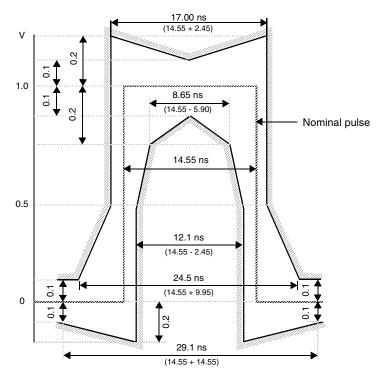

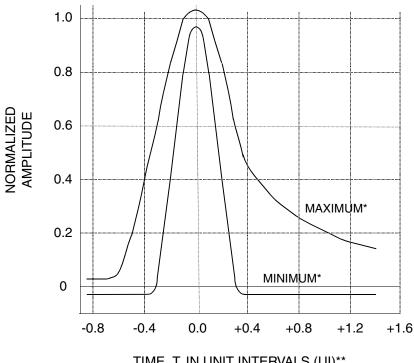

The line side timing characteristics of the DART are designed so that the line output at the transformer output meets the pulse shape specified in ITU-T Rec. G.703 for 34368 kbit/s operation. The pulse mask is shown in Figure 15. Refer to ITU-T Rec. G.703 for further details regarding the pulse mask.

Reference: ITU-T Recommendation G.703

Figure 15. Pulse Mask at the 34368 kbit/s Interface

#### **DS3 LINE SIDE TIMING CHARACTERISTICS**

The line side signal characteristics are designed so that the output meets the requirements of Bellcore GR-499-CORE, Issue 1, December 1995. When terminated into a test load of 75 ohm ± 5% using ATT 734A coaxial cable the DART device will meet the DS3 interface isolated pulse mask defined below in Figures 16 and 17 for a cable distance of 0 to 450 feet. The pulse measurement is made using a Hewlett Packard HP54502A oscilloscope (or equivalent) in the average mode, which is described in the HP instruction manual for this instrument. The input to the DART device is a 2<sup>15</sup>-1 pseudo-random binary sequence (PRBS) signal.

TIME, T, IN UNIT INTERVALS (UI)\*\*

Figure 16. DS3 Interface Isolated Pulse Mask

| CURVE                       | TIME IN<br>UNIT INTERVALS                                                 | NORMALIZED<br>AMPLITUDE                                                                                                 |

|-----------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| MAXIMUM<br>(UPPER)<br>CURVE | $-0.85 \le T \le -0.68$<br>$-0.68 \le T \le 0.36$<br>$0.36 \le T \le 1.4$ | 0.03<br>0.5 $\left[1 + \sin \frac{\pi}{2} \left(1 + \frac{T}{0.34}\right)\right] + 0.03$<br>0.08 + 0.407e -1.84(T-0.36) |

| MINIMUM<br>(LOWER)<br>CURVE | $-0.85 \le T \le -0.36$<br>$-0.36 \le T \le 0.36$<br>$0.36 \le T \le 1.4$ | $0.5 \left[ 1 + \sin \frac{\pi}{2} \left( 1 + \frac{T}{0.18} \right) \right] - 0.03$ $- 0.03$                           |

Figure 17. DS3 Interface Isolated Pulse Mask Equations

<sup>\*</sup> Note: The DS3 curves shown are approximate representations of the equations in Figure 17.

<sup>\*\*</sup>Note: UI = 1 / (System Clock Frequency).

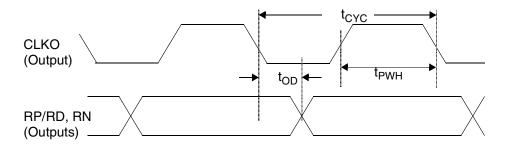

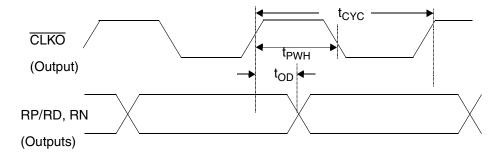

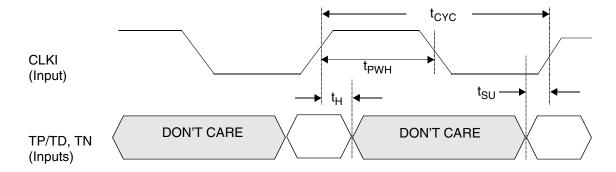

### **DIGITAL TERMINAL SIDE TIMING DIAGRAMS**