# WESTERN DIGITAL

# UC1671 ASTRO

## **FEATURES**

# SYNCHRONOUS AND ASYNCHRONOUS

· Full Duplex Operations

# SYNCHRONOUS MODE

- Selectable 5-8 Bit Characters

- Two Successive SYN Characters Sets Synchronization

- Programmable SYN and DLE Character Stripping

- Programmable SYN and DLE-SYN Fill

# **ASYNCHRONOUS MODE**

- Selectable 5-8 Bit Characters

- · Line Break Detection and Generation

- 1-, 11/2-, or 2-Stop Bit Selection

- False Start Bit Detection Automatic Serial Echo Mode

# SYSTEM COMPATIBILITY

- · Double Buffering of Data

- 8-Bit Bi-Directional Bus For Data, Status, and Control Words

- · All Inputs and Outputs TTL Compatible

- Up to 32 ASTROS Can Be Addressed On Bus

- On-Line Diagnostic Capability

# TRANSMISSION ERROR DETECTION-PARITY

· Overrun and Framing

BAUD RATE - DC TO 1M BIT/SEC

#### 8 SELECTABLE CLOCK RATES

- Accepts 1X Clock and Up to 4 Different 32X Baud Rate Clock Inputs

- Up to 47% Distortion Allowance with 32X Clock

#### DESCRIPTION

The UC1671 (ASTRO) is a MOS/LSI device which performs the functions of interfacing a serial data communication channel to a parallel digital system. The device is capable of full duplex communications (receiving and transmitting) with synchronous or asynchronous systems. The ASTRO is designed to operate on a multiplexed bus with other bus-oriented

PIN DESIGNATION

#### **APPLICATIONS**

SYNCHRONOUS COMMUNICATIONS ASYNCHRONOUS COMMUNICATIONS SERIAL/PARALLEL COMMUNICATIONS

devices. Its operation is programmed by a processor or controller via the bus and all parallel data transfers with these machines are accomplished over the bus lines.

The ASTRO is fabricated in n-channel silicon gate MOS technology and is TTL compatible on all inputs and outputs.

# **PIN DESCRIPTION**

The device is packaged in a 40-pin plastic or ceramic cavity package. The interface signals are defined below with all input/output signals complemented to facilitate bussing and interfacing with TTL. The Data Set controls and Status signals are also com-

plemented to allow for an inversion when converting to EIA RS232C levels. The names and symbols assigned to the Data Set interface signals follows EIA standard nomenclature.

A bar over a signal (SIGNAL), means active low (set = low).

| PIN<br>NUMBER      | MNEMONIC        | SIGNAL NAME                  | FUNCTION                                                                                                                                                                                                                                                |

|--------------------|-----------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | V <sub>BB</sub> | POWER SUPPLIES               | – 5V                                                                                                                                                                                                                                                    |

| 2                  | IACKI           | INTERRUPT<br>ACKNOWLEDGE IN  | This input becomes low when polling takes place on the bus by the Controller to determine the interrupting source. When this signal is received, the ASTRO places its ID code on the DAL if it is requesting interrupt, otherwise it makes IACKO a low. |

| 3                  | <del>C</del> S  | CHIP SELECT                  | The low logic transition of CS identifies a valid address on the DAL bus during Read and Write operations.                                                                                                                                              |

| 4                  | WE              | WRITE ENABLE                 | This signal, when low, gates the contents of the DAL bus into the addressed register of a selected ASTRO.                                                                                                                                               |

| 5                  | IACKO           | INTERRUPT<br>ACKNOWLEDGE OUT | This output is made a logic low in response to a low IACKI if the ASTRO receiving an IACKI input is not the interrupting device.                                                                                                                        |

| 6                  | RPLY            | REPLY                        | This open drain output is made low when the ASTRO is responding to being selected by an address on the DAL during read or write operations or in affirming that it is the interrupting source during interrupt polling.                                 |

| 7                  | INTR            | INTERRUPT                    | This open drain output is made low when one of the communication interrupt conditions occur.                                                                                                                                                            |

| 8-15               | DALO-DAL7       | DATA ACCESS LINES            | Eight-bit bi-directional bus used for transfer of data, control, status, and address information.                                                                                                                                                       |

| 16                 | DTR (CD)        | DATA TERMINAL READY          | This output is generated by a bit in the Control Register and indicates Controller readiness.                                                                                                                                                           |

| 17,22,24,<br>25,26 | ĪD7-ID3         | SELECT CODE                  | Five input pins which when hard-wired assign the device<br>a unique identification code used to select the device<br>when addressing and used as an identification when<br>responding to interrupts.                                                    |

| 18                 | RING (CE)       | RING INDICATOR               | This input from the Data Set generates an interrupt when made low with Data Terminal Ready in the "Off" condition.                                                                                                                                      |

| 19                 | MISC            | MISCELLANEOUS                | This output is controlled by a bit in the Control Register and is used as an extra programmable signal.                                                                                                                                                 |

| 20                 | Vss             |                              | Ground.                                                                                                                                                                                                                                                 |

| 21                 | VCC             |                              | +5V                                                                                                                                                                                                                                                     |

| 23                 | MR              | MASTER RESET                 | The Control and Status Registers and other controls are cleared when this input is low.                                                                                                                                                                 |

| 27                 | RDATA (BB)      | RECEIVED DATA                | This input receives serial data into the ASTRO.                                                                                                                                                                                                         |

| 28                 | DSR (CC)        | DATA SET READY               | This input generates an interrupt when going On or Off while the Data Terminal Ready signal is On. It appears as a bit in the Status Register.                                                                                                          |

| 29                 | CARR (CF)       | CARRIER DETECTOR             | This input from the Data Set generates an interrupt when going On or Off if Data Terminal Ready is On. It appears as a bit in the Status Register.                                                                                                      |

# PIN DESCRIPTION (CONTINUED)

| PIN<br>NUMBER | MNEMONIC        | SIGNAL NAME        | FUNCTION                                                                                                                                                                                                                                                   |

|---------------|-----------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30-33         | R1-R4           | CLOCK RATES        | These four inputs accept four different local 32X data rate Transmit and Receive clocks. The input on R4 may be divided down into a 32X clock from a 32X, 64X, 128X, or 256X clock input. The clock used in the ASTRO is selected by the control Register. |

| 34            | IXRC (DD)       | RECEIVER TIMING    | This input is the Receiver 1X Data Rate Clock. Its use is selected by the Control Register. The Received Data is sampled by the ASTRO on the positive transition of this signal.                                                                           |

| 35            | IXTC (DB)       | TRANSMITTER TIMING | This input is the Transmitter 1X Data Rate Clock. Its use is selected by the Control Register. The transmitted data changes on the negative transition of this signal.                                                                                     |

| 36            | CTS (CB)        | CLEAR TO SEND      | This input, when low, enables the transmitter section of the ASTRO.                                                                                                                                                                                        |

| 37            | TDATA (BA)      | TRANSMITTED DATA   | This output is the transmitted serial data from the ASTRO. This output is held in a Marking condition when the transmitter section is not enabled.                                                                                                         |

| 38            | RTS (CA)        | REQUEST TO SEND    | This output is enabled by the Control Register and remains in a low state during transmitted data from the ASTRO.                                                                                                                                          |

| 39            | RE              | READ ENABLE        | This signal, when low, gates the contents of an addressed register from a selected ASTRO onto the DAL bus.                                                                                                                                                 |

| 40            | V <sub>DD</sub> |                    | + 12V                                                                                                                                                                                                                                                      |

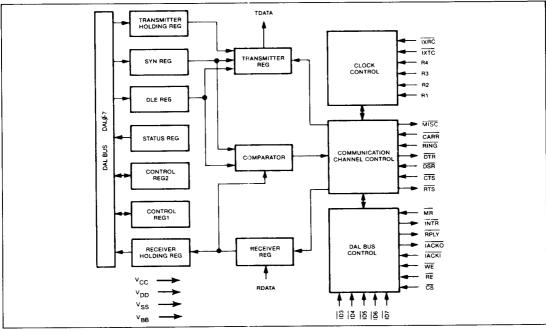

**UC1671 BLOCK DIAGRAM**

**RECEIVER REGISTER** — This 8-bit shift register inputs the received data at a clock rate determined by the Control Register. The incoming data is assembled to the selected character length and then transferred to the Receiver Holding Register with logic zeroes filling out any unused high-order bit positions.

**RECEIVER HOLDING REGISTER** — This 8-bit parallel buffer register presents assembled receiver characters to the DAL bus lines when requested through a Read operation.

COMPARATOR — The 8-bit comparator is used in the Synchronous mode to compare the assembled contents of the Receiver Register and the SYN register or DLE register. A match between the registers sets up stripping of the received character, when programmed, by preventing the data from being loaded into the Receiver Holding Register. A bit in the Status Register is set when stripping is performed. The comparator output also enables character synchronization of the Receiver on two successive matches with the SYN register.

**SYN REGISTER** — This 8-bit register is loaded from the DAL lines by a Write operation and holds the synchronization code used to establish receiver character synchronization. It serves as a fill character when no new data is available in the Transmitter Holding Register during transmission. This register cannot be read onto the DAL lines. It must be loaded with logic zeroes in all unused high-order bits.

**DLE REGISTER** — This 8-bit register is loaded from the DAL lines by a Write operation and holds the "DLE" character used in the Transparent mode of operation in which an idle transmit period is filled with the combination DLE-SYN pair of characters rather than a single SYN character. In addition the ASTRO may be programmed to force a single DLE character prior to any data character transmission while in the transmitter transparent mode.

TRANSMITTER HOLDING REGISTER — This 8-bit parallel buffer register holds parallel transmitted data transferred from the DAL lines by a Write operation. This data is transferred to the Transmitter Register when the transmitter section is enabled and the Transmitter Register is ready to send new data.

**TRANSMITTER REGISTER** — This 8-bit shift register is loaded from the Transmitter Holding Register, SYN register, or DLE register. The purpose of this register is to serialize data and present it to the transmitted Data output.

CONTROL REGISTERS — There are two 8-bit Control Registers which hold device programming signals such as mode selection, clock selection, interface signal control, and data format. Each of the Control Registers can be loaded from the DAL lines by a Write operation or read onto the DAL lines by a Read operation. The registers are cleared by a Master Reset.

STATUS REGISTER — This 8-bit register holds information on communication errors, interface data register status, match character conditions, and communication equipment status. This register may be read onto the DAL lines by a Read operation.

DATA ACCESS LINES — The DAL is an 8-bit bidirectional bus port over which all address, data, control, and status transfers occur. In addition to transferring data and control words the DAL lines also transfer information related to addressing of the device, reading and writing requests, and interrupting information.

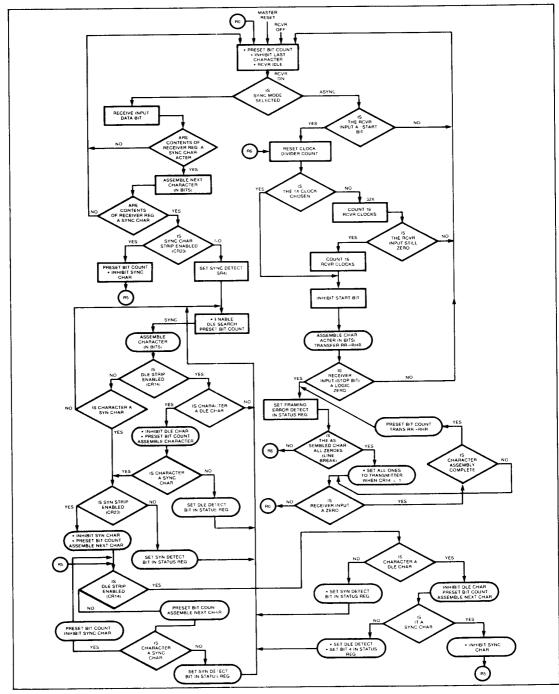

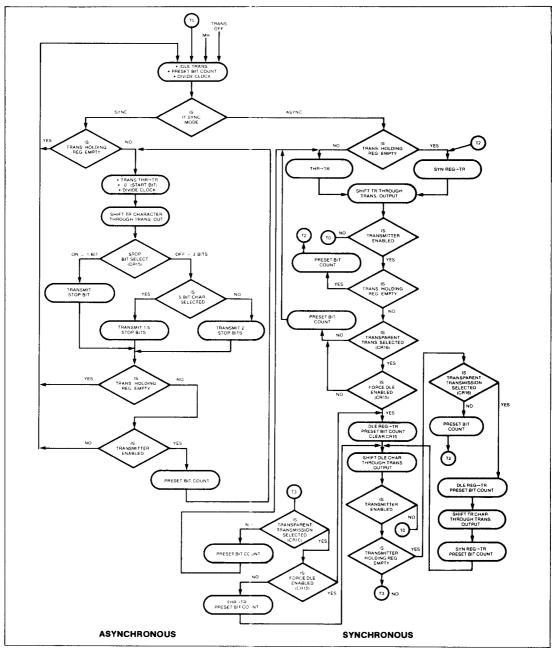

# ASTRO OPERATION ASYNCHRONOUS MODE

Framing of asynchronous characters is provided by a Start bit (logic low) at the beginning of a character and a Stop bit (logic high) at the end of a character. Reception of a character is initiated on recognition of the first Start bit by a positive transition of the receiver clock, after a preceding Stop bit. The Start and Stop bits are stripped off while assembling the serial input into a parallel character.

The character assembly is completed by the reception of the Stop bit after reception of the last character or parity bit. If this bit is a logic high, the character is determined to have correct framing and the ASTRO is prepared to receive the next character. If the Stop bit is a logic low the Framing Error Status flag is set and the Receiver assumes this bit to be the Start bit of the next character. Character assembly continues from this point if the input is still a logic low when sampled at the theoretical center of the assumed

Start bit. As long as the Receive input is spacing, all zero characters are assembled and error flags and data received interrupts are generated so that line breaks can be determined. After a character of all zeroes is assembled along with a zero in the Stop bit location, the first received logic high is determined as a Stop bit and this resets the Receiver circuit to a Ready state for assembly of the next character.

In the Asynchronous mode the character transmission occurs when information contained in the Transmitter Holding Register is transferred to the Transmitter Register. Transmission is initiated by the Insertion of a Start bit, followed by the serial output of the character least significant bit first with parity, if enabled, following the most significant bit; then the insertion of a 1-, 1.5-, or 2-bit length Stop condition. If the Transmitter Holding Register is full, the next character transmission starts after the transmission of the Stop bit of the present character in the Transmitter Register. Otherwise, the Mark (logic high) condition is continually transmitted until the Transmitter Holding Register is loaded.

In order to allow re-transmission of data received at a slightly faster character rate, means are provided for shortening the Stop bit length to allow transmission of characters to occur at the same rate as the reception of characters. The Stop bit is shortened by 1/16 of a bit period for 1-Stop bit selection and 3/16 of a bit period for 1.5-, or 2-Stop bit selection, if the next character is ready in the Transmitter Holding Register.

# SYNCHRONOUS MODE

Framing of characters is carried out by a special Synchronization Character Code (SYN) transmitted at the beginning of a block of characters. The Receiver, when enabled, searches for two continuous characters matching the bit pattern contained in the SYN register. During the time the Receiver is searching, data is not transferred to the Receiver Holding Register, status bits are not updated, and the Receiver interrupt is not activated. After the detection of the first SYN character, the Receiver assembles subsequent bits into characters whose length is determined by contents of the Control Register. If, after the first SYN character detection, a second SYN character is present, the Receiver enters the Synchronization mode until the Receiver Enable Bit is turned off. If a second successive SYN character is not found, the Receiver reverts back to the Search mode.

In the Synchronous mode a continuous stream of characters are transmitted once the Transmitter is enabled. If the Transmitter Holding Register is not loaded at the time the Transmitter Register has completed transmission of a character, this idle time will be filled by a transmission of the character contained in the SYN register in the Nontransparent mode, or the characters contained in the DLE and SYN registers respectively while in the Transparent mode of operation.

#### **DETAILED OPERATION**

Receiver — The Receiver Data input is clocked into the Receiver Register by a 1X Receiver Clock from a modem Data Set, or by a local 32X bit rate clock selected from one of four externally supplied clock inputs. When using the 1X clock, the Receiver Data is sampled on the positive transition of the clock in both the Asynchronous and Synchronous modes. When using a 32X clock in the Asynchronous mode, the Receive Sampling Clock is phased to the Mark-To-Space transition of the Received Data Start bit and defines, through clock counts, the center of each received Data bit within +0%, -3% at the positive transition 16 clock periods later.

In the Synchronous mode the Sampling Clock is phased to all Mark-To-Space transitions of the Received Data inputs when using a 32X clock. Each transition of the data causes an incremental correction of the Sampling Clock by 1/32nd of a bit period. The Sampling Clock can be immediately phased to every Mark-To-Space Data transition by setting Bit 4 of Control Register 1 to a logic high, while the Receiver is disabled.

When the complete character has been shifted into the Receiver Register it is then transferred to the Receiver Holding Register, the unused, higher number bits are filled with zeroes. At this time the Receiver Status bits (Framing Error/Sync Detect, Parity Error/DLE Detect, Overrun Error, and Data Received) are updated in the Status Register and the Data Received interrupt is activated. Parity Error is set, if encountered while the Receiver parity check is enabled in the Control Register. Overrun Error is set if the Data Received status bit is not cleared through a

Read operation by an external device when a new character is ready to be transferred to the Receiver Holding Register. This error flag indicates that a character has been lost, as new data is lost and the old data and its status flags are saved.

The characters assembled in the Receiver Register that match the contents of the SYN or DLE register are not loaded into the Receiver Holding Register, and the DR interrupt is not generated, if Bit 3 of Control Register 2 (CR23 = SYN Strip) or Bit 4 of Control Register 1 (CR14 = DLE Strip) are set respectively, the SYN-DET and DLE-DET status bits are set with the next non SYN or DLE character. When both CR23 and CR14 are set (Transparent mode), the DLE-SYN combination is stripped. The SYN comparison occurs only with the character received after the DLE character. If two successive DLE characters are received only the first DLE character is stripped. No parity check is made while in this mode.

Transmitter - Information is transferred to the Transmitter Holding Register by a Write operation. Information can be loaded into this register at any time, even when the Transmitter is not enabled. Transmission of data is initiated only when the Request To Send bit is set to a logic one in the Control Register and the Clear To Send input is a logic low. Information is normally transferred from the Transmitter Holding Register to the Transmitter Register when the latter has completed transmission of a character. However, information in the DLE register may be transferred prior to the information contained in the Transmitter Holding Register if the Force DLE signal condition is enabled (Bit 5 = Force DLE and 6 = TX Transparent Control Register 1 set to a logic one). The control bit CR15 must be set prior to loading of a new character in the transmitter holding register to insure forcing the DLE character prior to transmission of the data character. The Transmitter Register output passes through a flip-flop which delays the output by one clock period. When using the 1X clock generated by the Modem Data Set, the output data changes state on the negative clock transition and the delay is one bit period. When using a local 32X clock the transmitter section selects one of the four selected rate inputs and divides the clock down to the baud rate. This clock is phased to the Transmitter Holding Register empty flag such that transmission of characters occurs within two data bit times of the loading of the Transmitter Holding Register when the Transmitter Register is empty.

When the Transmitter is enabled, a Transmitter interrupt is generated each time the Transmitter Holding Register is empty. If the Transmitter Holding Register is empty when the Transmitter Register is ready for a new character the Transmitter enters an idle state. During this idle time a logic high will be presented to the Transmitted Data output in the Asynchronous mode or the contents of the SYN register will be presented in the Synchronous Nontransparent mode (CR16=0). In the Synchronous Transmit Transparent mode (enabled by Bit 6 of Control Register 1 = Logic 1), the idle state will be filled by a DLE-SYN character transmission in that order. When entering the Transparent mode the DLE-SYN fill will not occur until the first forced DLE.

If the Transmitter section is disabled by a reset of the Request to Send, any partially transmitted character is completed before the transmitter section of the ASTRO is disabled. As soon as the CTS goes high the transmitted data output will go high.

When the Transmit parity is enabled, the selected Odd or Even parity bit is inserted into the last bit of the character in place of the last bit of the Transmitted Register. This limits transfer of character information to a maximum of seven bits plus parity or eight bits without parity. Parity cannot be enabled in the Synchronous Transparency mode.

## **DEVICE PROGRAMMING**

The two 8-bit Control Registers of the ASTRO determine the operative conditions of the ASTRO chip. Control Register 1 is shown in the following table.

| BIT 7 7                                       | 6                                                                                                                | 5                                                       | 4                                                                                                                                                                                            | 3                                                                                                                                                                                            | 2                                                   | 1                                  | 0                                  |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------|------------------------------------|

| SYNC/ASYNC<br>0—LOOP MODE<br>1—NORMAL<br>MODE | ASYNC  0—NON BREAK MODE  1—BREAK MODE  SYNC  0—NON TRANS- MITTER TRANS- PARENT MODE  1—TRANSMIT TRANSPARENT MODE | ASYNC (TRANS. ENABLED)  0-1 1/2 or 2 STOP BIT SELECTION | ASYNC  0-NON ECHO MODE  1-AUTO ECHO MODE  SYNC (CR12 = 1)  0-DLE STRIPPING NOT ENABLED  1-DLE STRIPPING STRIPPING STRIPPING O-DLE O-DLE O-DLE O-DLE O-DLE STRIPPING O-MISC RESET  1-MISC SET | ASYNC  0 - NO PARITY ENABLED 1 - PARITY CHECK ENABLED ON RECEIVER PARITY GENERATION ENABLED ON TRANSMITTER  SYNC  0 - RECEIVER PARITY CHECK IS DISABLED 1 - RECEIVER PARITY CHECK IS ENABLED | SYNC/ASYNC  0—RECEIVER DISABLED  1—RECEIVER ENABLED | SYNC/ASYNC  0—RTS RESET  1—RTS SET | SYNC/ASYNC  0-DTR RESET  1-DTR SET |

### **CONTROL REGISTER 1**

# **Control Register 1**

**Bit 7** — A logic 0 configures the ASTRO into an Internal Data and Control Loop mode and disables the Ring interrupt. In this diagnostic mode the following loops are connected internally:

- a. The Transmit Data is connected to the Receive Data with the TD pin held in a Mark condition and the input to the RD pin disregarded.

- b. With a 1X clock selected, the Transmitter Clock also becomes the Receive Clock.

- c. The Data Terminal Ready (DTR) is connected to the Data Set Ready (DSR) input, with the DTR output in held in an Off condition (logic high), and the DSR input pin is disregarded.

- d. The Request to Send Control bit is connected to the Clear To Send (CTS) and Carrier Detector inputs, with the RTS output pin held in an Off condition (logic high), and the CTS and Carrier Detector input pins are disregarded.

- The Miscellaneous pin is held in an Off (logic high) condition.

A logic 1 on Bit 7 enables the Ring interrupt and returns the ASTRO to the normal full duplex configuration.

Bit 6 — In the Asynchronous mode a logic 1 holds the Transmitted Data output in a Spacing (Logic 0) condition, starting at the end of any current transmitted character, when the Transmitter is enabled. Normal Transmitter timing continues so that this Break condition can be timed out after the loading of new characters into the Transmitter Holding Register.

In the Synchronous mode a logic 1 sets the Transmitter in a transparent transmission which implies that idle transmitter time will be filled by DLE-SYN character transmission and a DLE can be forced ahead of any character in the Transmitter Holding

Register when CR15 is a logic one in the sync mode.

Bit 5 — In the Asynchronous mode a logic 1, with the Transmitter enabled, causes a single Stop bit to be transmitted. A logic 0 causes 2-Stop bit transmission for character lengths of 6, 7, or 8 bits and one-and-ahalf Stop bits for a character length of 5 bits.

With the Transmitter disabled this bit controls the Miscellaneous output on Pin 19, which may be used for Make Busy on 103 Data Sets, Secondary Transmit on 202 Data Sets, or dialing on CBS Data Couplers.

In the Synchronous mode a logic 1 combined with a logic 0 on Bit 6 of control Register 1 enables Transmit parity; if CR15 = 0 or CR15 = 1 no parity is generated. When set to a logic 1 with Bit 6 also a logic 1, the contents of the DLE register are transmitted prior to the next character loaded in the Transmitter Holding Register as part of the Transmit Transparent mode.

Bit 4 — In the Asynchronous mode a logic 1 enables the Automatic Echo mode when the receiver section is enabled. In this mode the clocked regenerated data is presented to the Transmit Data output in place of normal transmission through the Transmitter Register. This serial method of echoing does not present any abnormal restrictions on the transmit speed of the terminal. Only the first character of a Break condition of all zeroes (null character) is echoed when a Line Break condition is detected. For all subsequent null characters, with logic zero Stop bits, a steady Marking condition is transmitted until normal character reception resumes. Echoing does not start until a character has been received and the Transmitter is idle. The Transmitter does not have to be enabled during the Echo mode.

In the Synchronous mode a logic 1, with the Receiver enabled, does not allow assembled Receiver data matching the DLE register contents to be transferred to the Receiver Holding Register, also, parity checking is disabled.

When the Receiver is not enabled this bit controls the Miscellaneous output on Pin 19, which may be used for New Sync on a 201 Data Set. When operating with a 32X clock and a disabled Receiver a logic 1 on this bit also causes the Receiver timing to synchronize on Mark-To-Space transitions.

**Bit 3** — In the *Asynchronous* mode a logic 1 enables check of parity on received characters and generation of parity for transmitted characters.

In the Synchronous mode a logic 1 bit enables check of parity on received characters only. **Note:** Transmitter parity enable is controlled by CR15.

Bit 2 — A logic 1 enables the ASTRO to receive data into the Receiver Holding Register, update Receiver Status Bits 1, 2, 3, and 4, and to generate Data Received interrupts. A logic 0 disables the Receiver and clears the Receiver Status bits.

Bit 1 — Controls the Request To Send output on Pin 38 to control the CA circuit of the Data Set The RTS output is inverted from the state of CR11. A logic 1 combined with a low logic Clear To Send input enables the Transmitter and allows THRE interrupts to be generated. A logic 0 disables the Transmitter and turns off the external Request To Send signal. Any character in the Transmitter Register will be completely transmitted before the Transmitter is turned off. The Request To Send output may be used for other functions such as "Make Busy" on 103 Data Sets.

**Bit 0** — Controls the Data Terminal Ready output on Pin 16 to control the CD circuit of the Data Set. A logic 1 enables the Carrier and Data Set Ready interrupts. A logic 0 enables only the telephone line Ring interrupt. The DTR output is inverted from the state of CR10.

# **Control Register 2**

Control Register 2, unlike Control Register 1, cannot be changed at any time. This register should be changed only while both the receiver and transmitter sections of the ASTRO are in the idle state.

Bits 7-6 — These bits select the character length as follows:

| Bits 7-6 | Character Length |

|----------|------------------|

| 00       | 8 bits           |

| 01       | 7 bits           |

| 10       | 6 bits           |

| 11       | 5 bits           |

When parity is enabled it must be considered as a bit when making character length selection, i.e. 5 character bits plus parity = 6 bits.

**Bit 5** — A logic 1 selects the Synchronous Character mode. A logic 0 selects the Asynchronous Character mode.

**Bit 4** — A logic 1 selects odd parity and a logic 0 selects even parity, when parity is enabled by CR13 and/or CR15.

Bit 3 — In the Asynchronous mode a logic 0 selects the rate 1(-32X) clock input (pin 30) as the Receiver Clock rate and a logic 1 selects the same clock rate for the Receiver as selected by Bits 2-0 for the Transmitter. This bit must be a logic 1 for the 1X clock selection by Bits 2-0.

In the Synchronous mode a logic 1 causes all DLE-SYN combination characters in the Transparent mode when DLE strip CR14 is a logic 1, or all SYN characters in the Non-transparent mode to be stripped and no Data Received interrupt to be generated. The SYN Detect status bit is set with reception of the next assembled character as it is transferred to the Receiver Holding Register.

**Bits 2-0** — These bits select the Transmit and Receive clocks. The Input Clock to the Rate 4 pin may be divided down to form the 32X clock from a multiple clock as shown:

| Bits 2-0 | Clock                                 |

|----------|---------------------------------------|

| 000      | 1X clock for Transmit and Receive     |

|          | (Pins 35 and 34 respectively)         |

| 001      | 32X clock — Rate 1 input (Pin 30)     |

| 010      | 32X clock — Rate 2 input (Pin 31)     |

| 011      | 32X clock — Rate 3 input (Pin 32)     |

| 100      | 32X clock — Rate 4 input ÷ 1 (Pin 33) |

| 101      | 32X clock — Rate 4 input + 2 (Pin 33) |

| 110      | 32X clock — Rate 4 input ÷ 4 (Pin 33) |

| 111      | 32X clock — Rate 4 input ÷ 8 (Pin 33) |

| BIT 7 6                                                                              | 5                                                     | 4                                                    | 3                                                                                                                                                                     | 2 1 0                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYNC/ASYNC  CHARACTER LENGTH SELECT  00 = 8 BITS 01 = 7 BITS 10 = 6 BITS 11 = 5 BITS | MODE SELECT  0-ASYNCHRONO JS MODE  1-SYNCHRONOUS MODE | SYNC/ASYNC  1-ODD PARITY SELECT 0-EVEN PARITY SELECT | ASYNC  1—RECEIVER CLOCK DETERMINED BY BITS 2-0 0—RECEIVER CLK = RATE 1  SYNC (CR14 = 0) 0—NO SYN STRIP 1—SYN STRIP 5YNC (CR14 = 1) 0—NO DLE-SYN STRIP 1—DLE-SYN STRIP | SYNCIASYNC  CLOCK SELECT  000 - IX CLOCK 001 - RATE 1 CLOCK 010 - RATE 2 CLOCK 010 - RATE 2 CLOCK 100 - RATE 4 CLOCK 101 - RATE 4 CLOCK + 2 110 - RATE 4 CLOCK + 4 111 - RATE 4 CLOCK + 8 |

**CONTROL REGISTER 2**

# Status Register

The data contained in the Status Register define Receiver and Transmitter data conditions and status of the Data Set. The Status word is shown and defined below.

Bit 7 — This bit is set to a logic 1 whenever there is a change in state of the Data Set Ready or Carrier Detector inputs while Data Terminal Ready (Bit 0 of Control Register 1) is a logic 1 or the Ring Indicator is turned on, with DTR a logic 0. This bit is cleared when the Status Register is read onto the Data Access Lines.

**Bit 6** — This bit is the logic complement of the Data Set Ready input on Pin 28. With 202-type Data Sets it can be used for Secondary Receive.

**Bit 5** — This bit is the logic complement of the Carrier Detector input on Pin 29.

**Bit 4** — In the Asynchronous mode a logic 1 indicates that received data contained a log 0 bit after the last data bit of the character in the stop bit slot, while the Receiver was enabled. This indicates a Framing error. This bit is set to a logic 0 if the proper logic 1 condition for the Stop bit was detected.

In the Synchronous mode a logic 1 indicates that the contents of the Receiver Register matched the contents of the SYN Register. The condition of this bit remains for a full character assembly time. If SYN strip (CR23) is enabled this status bit is updated with the character received after the SYN character. In both modes the bit is cleared when the Receiver is disabled.

Bit 3 — When the DLE Strip is enabled (Bit 4 of Control Register 1) the Receiver parity check is disabled and this bit is set to a logic 1 if the previous character to the presently assembled character matched the contents of the DLE register, otherwise it is cleared. The DLE DET remains for one character time and is reset on the next character transfer or on a Status Register Read. If DLE Strip is not enabled, this bit is set to a logic 1 when the Receiver is enabled, Receiver parity (Bit 3 of Control Register 1) is also enabled, and the last received character has a Parity error. A logic 0 on this bit indicates correct parity. This bit is cleared in either of the above modes when the Receiver is disabled.

Bit 2 — A logic 1 indicates an Overrun error which occurs if the previous character in the Receiver Holding Register has not been read and Data

Received is not reset, at the time a new character is to be transferred to the Receiver Holding Register. This bit is cleared when no Overrun condition is detected, i.e., the next character transfer time or when the Receiver is disabled.

Bit 1 — A logic 1 indicates that the Receiver Holding Register is loaded from the Receiver Register, if the Receiver is enabled. It is cleared to a logic 0 when the Receiver Holding Register is read onto the Data Access Lines, or the Receiver is disabled.

Bit 0 — A logic 1 indicates that the Transmitter Holding Register does not contain a character while the Transmitter is enabled. It is set to a logic 1 when the contents of the Transmitter Holding Register is transferred to the Transmitter Register. It is cleared to a 0 bit when the Transmitter Holding Register is loaded from the DAL, or when the Transmitter is disabled.

#### INPUT/OUTPUT OPERATIONS

All Data, Control, and Status words are transferred over the Data Access Lines (DAL 0-7). Additional input lines provide controls for addressing a particular unit, and regulating all input and output operations. Other lines provide interrupt capability to indicate to a Controller that an input operation is requested by the ASTRO. All input/output terminology below is referenced to the Controller so that a Read or Input takes data from the ASTRO and places it on the DAL lines, while a Write or Output places data from the DAL lines into the ASTRO. Bit 0 (DALO) must be a logic low in a Read or Write operation.

#### Read

A Read Operation is initiated by the placement of an eight-bit address on the DAL by the Controller. When the Chip Select signal goes to a logic low state, the ASTRO compares Bits 7-3 of the DAL with its hardwired ID code (Pins 17, 22, 24, 25, and 26) and becomes selected on a Match condition. The ASTRO then sets its REPLY line low to acknowledge its readiness to transfer data. Bits 2-0 of the address are used to select ASTRO registers to read from as follows:

| Bits 2-0 | Selected Register         |

|----------|---------------------------|

| 000      | Control Register 1        |

| 010      | Control Register 2        |

| 100      | Status Register           |

| 110      | Receiver Holding Register |

| BIT 7                   | 6                      | 5                   | 4                                     | 3                                    | 2                | 1                 | 0                                           |

|-------------------------|------------------------|---------------------|---------------------------------------|--------------------------------------|------------------|-------------------|---------------------------------------------|

| DATA     SET     CHANGE | DATA     SET     READY | CARRIER<br>DETECTOR | • FRAMING<br>ERROR<br>• SYN<br>DETECT | • DLE<br>DETECT<br>• PARITY<br>ERROR | OVERRUN<br>ERROR | DATA     RECEIVED | TRANSMITTER<br>HOLDING<br>REGISTER<br>EMPTY |

STATUS REGISTER

When the Read Enable (RE) line is set to a logic low condition by the Controller the ASTRO gates the contents of the addressed register onto the DAL. The Read operation terminates, and the devices becomes unselected, when both the Chip Select and Read Enable return to a logic high condition. Reading of the Receiver Holding Register clears the DR Status bit

#### Write

A Write operation is initiated by the placement of an eight-bit address on the DAL by the Controller. The ASTRO compares Bits 7-3 of the DAL with its ID code when the Chip Select input goes to a logic low state. If a Match condition exists, the device is selected and makes it's RPLY line low to acknowledge its readiness to transfer data. Bits 2-0 of the address are used to select ASTRO registers to be written into as follows:

| Bits 2-0 | Selected Register            |

|----------|------------------------------|

| 000      | Control Register 1           |

| 010      | Control Register 2           |

| 100      | SYN and DLE Register         |

| 110      | Transmitter Holding Register |

When the Write Enable (WE) line is set to a logic low condition by the Controller the ASTRO gates the data from the DAL into the addressed register. If data is written into the Transmitter Holding Register, the THRE Status bit is cleared to a logic zero.

The 100 address loads both the SYN and DLE registers. After writing into the SYN register the device is conditioned to write into the DLE if followed by another Write pulse with the 100 address. Any intervening Read or Write operation with other addresses resets this condition such that the next 100 will address the SYN register.

## Interrupts

The following conditions generate interrupts:

Data Received (DR) — Indicates transfer of a new character to the Receiver Holding Register while the Receiver is enabled.

- Transmitter Holding Register Empty (THRE) —

Indicates that the THR register is empty while the

Transmitter is enabled. The first interrupt occurs

when the Transmitter becomes enabled if there is

an empty THR, or after the character is transferred

to the Transmitter Register making the THR empty.

- Carrier On Indicates Carrier Detector input goes low when DTR is on.

- 4. Carrier Off Indicates Carrier Detector input goes high when DTR is on.

- DSR On Indicates the Data Set Ready input goes low when DTR is on.

- DSR Off Indicates the Data Set Ready input goes high when DTR is on.

- Ring On Indicates the Ring Indicator input goes low when DTR is off.

Each time an Interrupt condition exists the INTR output from the ASTRO is made a logic low. The following interrupt procedure is then carried out even if the interrupt condition is removed.

The Controller acknowledges the Interrupt request by setting the Chip Select (CS) and the Interrupt Acknowledge Input (IACKI) to the ASTRO to a Low state. On this transition all non-interrupting devices receiving the IACKI set their Interrupt Acknowledge Output (IACKO) low, enabling lower priority daisy-chained devices to respond to the Interrupt request. The highest priority device that is interrupting will then set its RPLY low. This device places its ID code on Bit Positions 7-3 of the DAL when a low RE signal is received. In addition Bit 2 is set to a logic one if any of the interrupt numbers 1 and 3-7 above occurred, and remains a logic zero if the THRE has caused the interrupt.

To reset the Interrupt condition (INTR) Chip Select (CS) and (IACKI) must be received by the ASTRO. A setup time must exist between CS and the RE or WE signals to allow chip selection prior to read/write operations and deselection control through the latter signals. The data is removed from the DAL when the RE signal returns to the logic high state.

### **MAXIMUM RATINGS**

VDD With Respect to VSS (Ground)

+ 20 to − 0.3V

Max Voltage To Any Input With Respect to VSS Operating Temperature

+ 20 to − 0.3V

Operating Temperature Storage Temperature

Plastic Ceramic

− 55° C to + 125° C

Power Dissipation

1000 mW

Absolute maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended and should be limited to those conditions specified under DC Electrical Characteristics.

# **OPERATING CHARACTERISTICS**

$T_A = 0$ °C to 70°C,  $V_{DD} = +12.0V \pm 5\%$ ,  $V_{BB} = -5.0V \pm 5\%$ ,  $V_{SS} = 0V$ ,  $V_{CC} = +5V \pm 5\%$

| SYMBOL | CHARACTERISTIC                    | MIN | TYP | MAX | UNITS | CONDITIONS        |

|--------|-----------------------------------|-----|-----|-----|-------|-------------------|

| ILI    | Input Leakage                     |     |     | 10  | μΑ    | VIN = VDD         |

| ILO    | Output Leakage                    |     |     | 10  | μA    | VOUT = VDD        |

| IBB    | VBB Supply Current                |     |     | 1   | mA    | $V_{BB} = -5V$    |

| ICCAVE | VCC Supply Current                |     |     | 80  | mA    |                   |

| IDDAVE | V <sub>DD</sub> Supply Current    |     |     | 10  | mA    |                   |

| ViH    | Input High Voltage                | 2.4 |     | ļ   | V     |                   |

| VIL    | Input Low Voltage<br>(All Inputs) |     |     | .8  | V     |                   |

| Voн    | Output High Voltage               | 2.8 |     |     | V     | $IO = -100 \mu A$ |

| VOL    | Output Low Voltage                |     |     | .45 | V     | IO = 1.6 mA       |

Note:

## **AC CHARACTERISTICS**

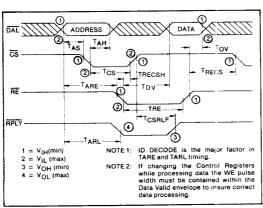

$T_A = 0$ °C to 70°C,  $V_{DD} = +12.0V \pm 5\%$ ,  $V_{BB} = -5.0V \pm 5\%$ ,  $V_{CC} = +5.0 \pm 5\%$ ,  $V_{SS} = 0V$  CL<sub>MAX</sub> = 20 pf

|       | SYMBOL           | CHARACTERISTIC           | MIN | TYP | MAX  | UNITS | CONDITIONS                  |

|-------|------------------|--------------------------|-----|-----|------|-------|-----------------------------|

|       | TAS              | Address Set-Up Time      | 0   |     |      | ns    |                             |

|       | t <sub>A</sub> H | Address Hold Time        | 150 |     |      | ns    |                             |

|       | TARL             | Address to RPLY Delay    |     |     | 400  | ns    | !                           |

|       | TCS              | CS Width                 | 250 |     |      | ns    |                             |

|       | TCSRLF           | CS to Reply OFF Delay    | 0   |     | 250  | ns    | $R_L = 2.7  \text{K}\Omega$ |

|       | TMR              | MR Width                 | 1.0 |     |      | μS    |                             |

| READ  |                  |                          |     |     |      |       |                             |

|       | TARE             | Address and RE Spacing   | 250 |     |      | ns    |                             |

|       | TRECSH           | RE and CS Overlap        | 20  |     |      | ns    |                             |

|       | TRECS            | RE to CS Spacing         | 250 |     |      | ns    |                             |

|       | $T_{DV}$         | RE to Data Out Delay     |     |     | 180  | ns    | C <sub>L</sub> = 20 pf      |

|       | $T_{OV}$         | RE Off to DAL Open Delay | 20  |     | 250  | ns    |                             |

|       | TRE              | RE Width                 | 200 |     | 1000 | ns    |                             |

| WRITE |                  |                          |     |     |      |       |                             |

|       | TAWE             | Address to WE Spacing    | 250 |     |      | ns    |                             |

|       | TWECSH           | WE and CS Overlap        | 20  |     |      | ns    |                             |

|       | TWE              | WE Width                 | 200 |     | 1000 | ns    |                             |

|       | TDS              | Data Set-Up Time         | 150 |     |      | ns    |                             |

|       | $T_DH$           | Data Hold Time           | 100 |     |      | ns    |                             |

|       | TWECS            | WE to CS Spacing         | 250 |     |      | ns    |                             |

ADDRESS DATA @<sup>©</sup> 2 ① TWECSH TWECS ...TAWE -Tos -T<sub>WE</sub> TCSRLF -TARL WRITE CYCLE TIMING DIAGRAM

**READ CYCLE TIMING DIAGRAM**

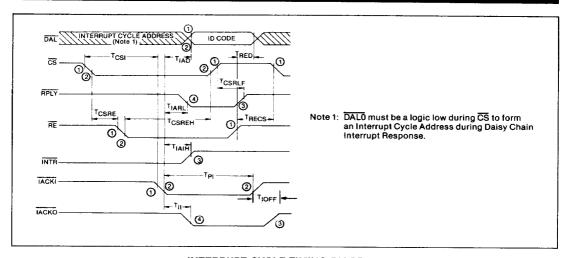

#### INTERRUPT

|        | CHARACTERISTIC                                                  | MIN | TYP | MAX | UNITS | CONDITIONS           |

|--------|-----------------------------------------------------------------|-----|-----|-----|-------|----------------------|

| TCSI   | CS to IACKI Delay                                               | 0   |     |     | ns    |                      |

| TCSRE  | CS to RE Delay                                                  | 250 |     |     | ns    |                      |

| TCSREH | CS and RE Overlap                                               | 20  |     |     | ns    |                      |

| TRECS  | RE to CS Spacing                                                | 250 |     |     | ns    |                      |

| Tpl    | IACKI Pulse Width                                               | 200 |     |     | ns    |                      |

| TIAD   | IACKI to Valid ID                                               |     |     | 250 | ns    | See Note 1.          |

|        | Code Delay                                                      |     |     |     |       |                      |

| Tov    | RE OFF to DAL Open Delay                                        | 20  |     | 250 | ns    |                      |

| TIARL  | IACKI to RPLY Delay                                             |     |     | 250 | ns    |                      |

| TCSRLF | CS to RPLY OFF Delay                                            | 0   |     | 250 | ns    | $R_L = 2.7  K\Omega$ |

| TIAIH  | IACKI ON to INTR OFF                                            |     |     | 300 | ns    |                      |

|        | Delay                                                           |     |     | i   |       |                      |

| TII    | IACKI to IACKO Delay                                            |     |     | 200 | ns    |                      |

| TIOFF  | IACKO OFF Delay                                                 |     |     | 250 | ns    | See Note 2.          |

|        | From $\overline{\text{CS}}$ OFF, $\overline{\text{RE}}$ OFF, or |     |     |     |       |                      |

|        | IACKI HIGH.                                                     |     |     |     |       |                      |

Note 1: If  $\overline{RE}$  goes low after  $\overline{IACKI}$  goes low, the delay will be from the falling edge of  $\overline{RE}$ .

Note 2:  $\overline{IACKO}$  goes false after the last one of the following three signals go false:  $\overline{CS}$ ,  $\overline{RE}$  and

IACKI. TIOFF is measured from the last signal going false.

INTERRUPT CYCLE TIMING DIAGRAM

RECEIVER SECTION

TRANSMITTER SECTION