#

# **Dual Channel Power Driver**

UC1707 UC2707 UC3707

## FEATURES

- Two independent Drivers

- 1.5A Totem Pole Outputs

- Inverting and Non-Inverting Inputs

- 40ns Rise and Fall into 1000pF

- High-Speed, Power MOSFET Compatible

- Low Cross-Conduction Current Spike

- Analog Shutdown with Optional Latch

- Low Quiescent Current

- 5V to 40V Operation

- Thermal Shutdown Protection

- 16-Pin Dual-In-Line Package

- 20-Pin PLCC and CLCC Package

#### DESCRIPTION

The UC1707 family of power drivers is made with a high-speed Schottky process to interface between low-level control functions and high-power switching devices - particularly power MOSFETs. These devices contain two independent channels, each of which can be activated by either a high or low input logic level signal. Each output can source or sink up to 1.5A as long as power dissipation limits are not exceeded.

Although each output can be activated independently with its own inputs, it can be forced low in common through the action either of a digital high signal at the Shutdown terminal or a differential low-level analog signal. The Shutdown command from either source can either be latching or not, depending on the status of the Latch Disable pin.

Supply voltage for both VIN and VC can independently range from 5V to 40V.

These devices are available in two-watt plastic "bat-wing" DIP for operation over a 0°C to 70°C temperature range and, with reduced power, in a hermetically sealed cerdip for -55°C to +125°C operation. Also available in surface mount DW, Q, L packages.

#### **TRUTH TABLE (Each Channel)**

| OUT = INV and N.I.                      | OUT | N.I. | INV. |

|-----------------------------------------|-----|------|------|

| $\overline{OUT} = INV \text{ or } N.I.$ | L   | Н    | Н    |

|                                         | Н   | Н    | L    |

|                                         | L   | L    | Н    |

|                                         | L   | L    | L    |

| •                                       |     |      |      |

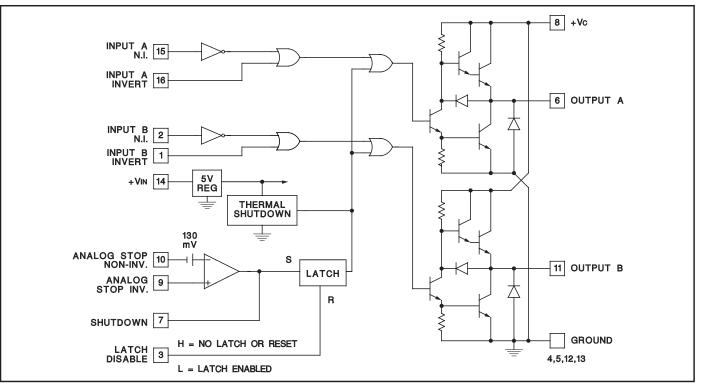

#### BLOCK DIAGRAM

#### **ABSOLUTE MAXIMUM RATINGS**

Note: All voltages are with respect to the four ground pins which must be connected together. All currents are positive into, negative out of the specified terminal. Digital Drive can exceed 5.5V if input current is limited to 10mA. Consult Packaging section of Databook for thermal limitations and considerations of package.

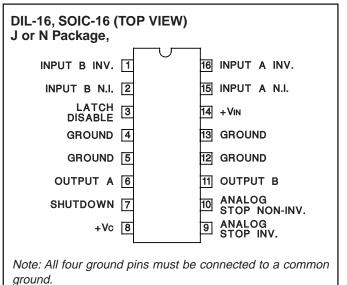

#### **CONNECTION DIAGRAMS**

| PARAMETERS                                       | TEST CONDITIONS                      | MIN | TYP   | MAX  | UNITS |

|--------------------------------------------------|--------------------------------------|-----|-------|------|-------|

| V <sub>IN</sub> Supply Current                   | $V_{IN} = 40V$                       |     | 12    | 15   | mA    |

| V <sub>C</sub> Supply Current                    | $V_{C} = 40V$ , Outputs Low          |     | 5.2   | 7.5  | mA    |

| V <sub>C</sub> Leakage Current                   | V <sub>IN</sub> =0, VC =30V, No Load |     | .05   | 0.1  | mA    |

| Digital Input Low Level                          |                                      |     |       | 0.8  | V     |

| Digital Input High Level                         |                                      | 2.2 |       |      | V     |

| Input Current                                    | $V_I = 0$                            |     | -0.06 | -1.0 | mA    |

| Input Leakage                                    | $V_{I} = 5V$                         |     | .05   | 0.1  | mA    |

| Output High Sat., V <sub>C</sub> -V <sub>O</sub> | $I_{O} = -50 \text{mA}$              |     |       | 2.0  | V     |

|                                                  | I <sub>O</sub> = -500mA              |     |       | 2.5  | V     |

| Output Low Sat., V <sub>O</sub>                  | $I_{O} = -50 \text{mA}$              |     |       | 0.4  | V     |

|                                                  | I <sub>O</sub> = -500mA              |     |       | 2.5  | V     |

| Analog Threshold                                 | $V_{CM} = 0$ to 15V                  | 100 | 130   | 160  | mV    |

| Input Bias Current                               | $V_{CM} = 0$                         |     | -10   | -20  | μΑ    |

| Thermal Shutdown                                 |                                      |     | 155   |      | °C    |

| Shutdown Threshold                               | Pin 7 Input                          | 0.4 | 1.0   | 2.2  | V     |

| Latch Disable Threshold                          | Pin 3 Input                          | 0.8 | 1.2   | 2.2  | V     |

# **ELECTRICAL CHARACTERISTICS:** Unless otherwise stated, these specifications apply for $T_A = -55^{\circ}C$ to $+125^{\circ}C$ for the UC1707, $-25^{\circ}C$ to $+85^{\circ}C$ for the UC2707 and 0°C to $+70^{\circ}C$ for the UC3707; $V_{IN} = V_C = 20V$ . $T_A = T_J$ .

## **TYPICAL SWITCHING CHARACTERISTICS:** $V_{IN} = V_C = 20V$ , $T_A = 25^{\circ}C$ . Delays measured to 10% output change.

| PARAMETERS                      | TEST CONDITIONS       | OU <sup>.</sup> | OUTPUT CL = |     | UNITS |

|---------------------------------|-----------------------|-----------------|-------------|-----|-------|

| From Inv. Input to Output       |                       | open            | 1.0         | 2.2 | nF    |

| Rise Time Delay                 |                       | 40              | 50          | 60  | ns    |

| 10% to 90% Rise                 |                       | 25              | 40          | 50  | ns    |

| Fall Time Delay                 |                       | 30              | 40          | 50  | ns    |

| 90% to 10% Fall                 |                       | 25              | 40          | 50  | ns    |

| From N.I. Input to Output       |                       |                 |             |     |       |

| Rise Time Delay                 |                       | 30              | 40          | 50  | ns    |

| 10% to 90% Rise                 |                       | 25              | 40          | 50  | ns    |

| Fall Time Delay                 |                       | 45              | 55          | 65  | ns    |

| 90% to 10% Fall                 |                       | 25              | 40          | 50  | ns    |

| V <sub>C</sub> Cross-Conduction | Output Rise           | 25              |             |     | ns    |

| Current Spike Duration          | Output Fall           | 0               |             |     | ns    |

| Analog Shutdown Delay           | Stop non-Inv. = 0V    | 180             |             |     | ns    |

|                                 | Stop Inv. = 0 to 0.5V | 180             |             |     | ns    |

| Digital Shutdown Delay          | 2V Input on Pin 7     | 50              |             |     | ns    |

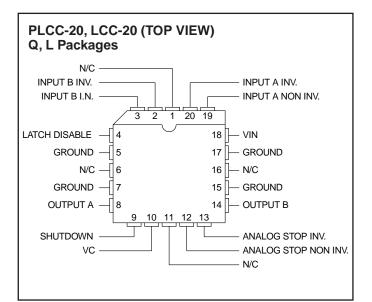

#### SIMPLIFIED INTERNAL CIRCUITRY

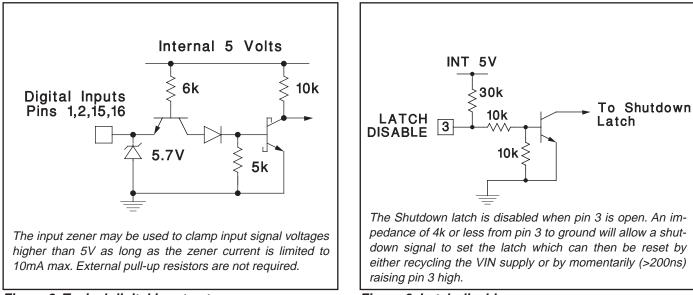

Figure 1. Typical digital input gate.

Figure 2. Typical digital input gate.

#### SIMPLIFIED INTERNAL CIRCUITRY (cont.)

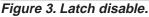

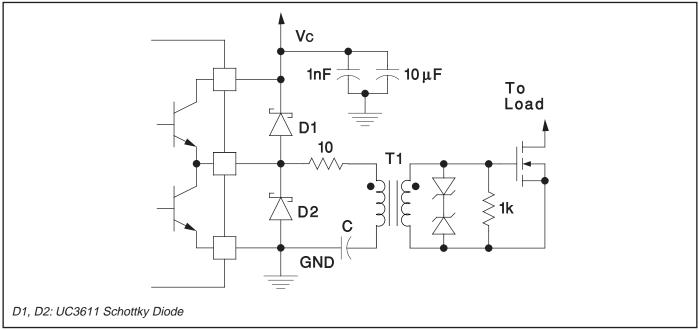

Figure 4. Transformer coupled push-pull MOSFET drive circuit.

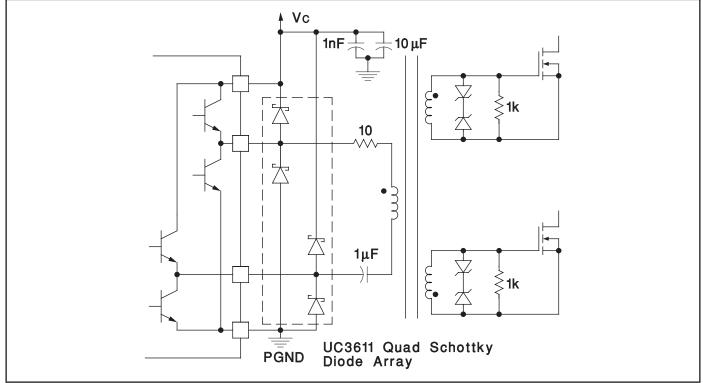

Figure 5. Current limiting.

#### **APPLICATIONS**

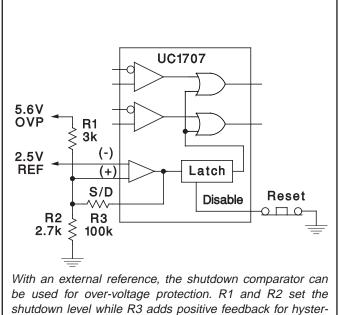

esis.

Figure 6. Over-voltage protection.

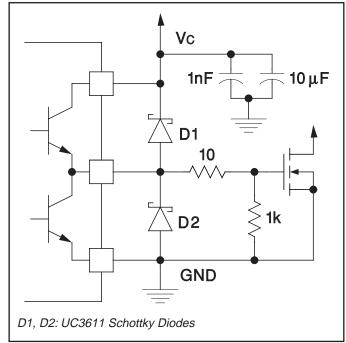

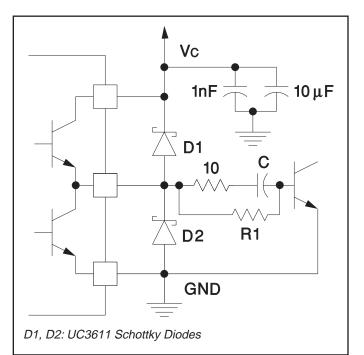

Figure 7. Power MOSFET drive circuit.

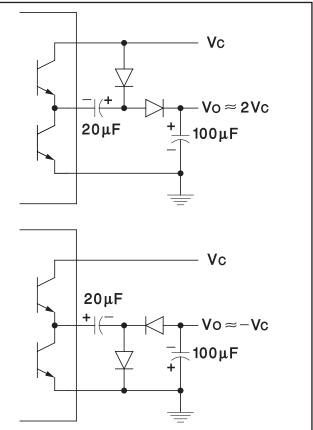

When driven with a TTL square wave drive, the low output impedance of the UC1707 allows ready implementation of charge pump voltage converters.

Figure 8. Charge pump circuits.

Figure 9. Power bipolar drive circuit.

#### TRANSFORMER COUPLING

Figure 10. Transformer coupled MOSFET drive circuit.

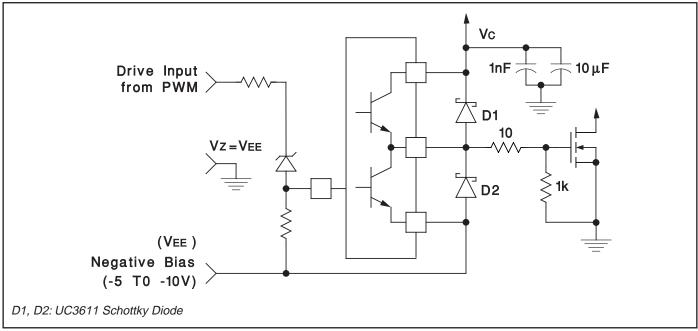

Figure 11. Power MOSFET drive circuit using negative bias voltage and level shifting to ground reference PWM.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated