# 10-Bit Serial D/A Converter

### FEATURES

- 10 Bit Resolution

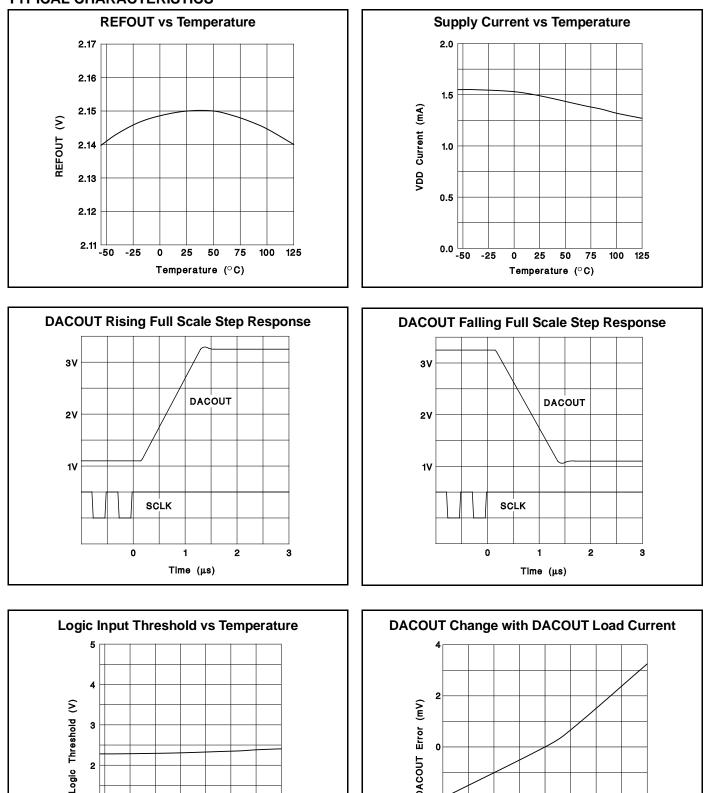

- 1.1µs Output Rise Time

- 2.5µs Settling Time to 1%

- Single +5V Supply

- Monotonic

- Low Power Sleep Mode

- Three-wire Serial Interface

- 20MHz Data Rate

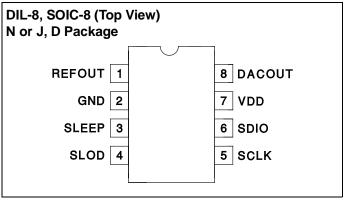

- 8 Pin SOIC and DIL Package

#### DESCRIPTION

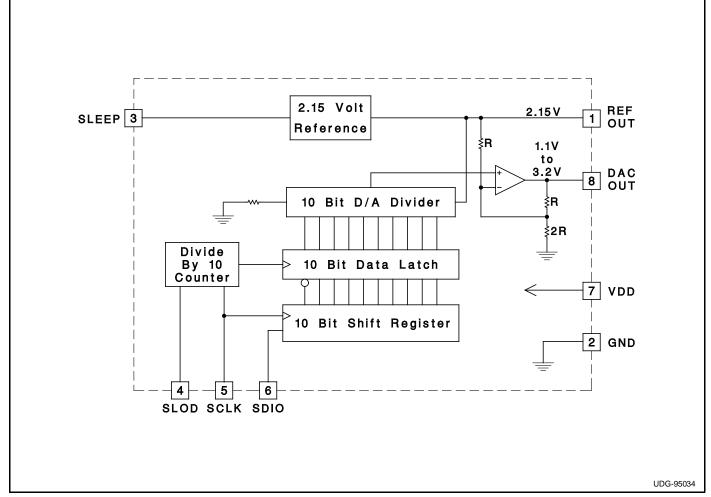

The UCC5950 is a self-contained, microprocessor-compatible 10-bit D/A converter. It contains all of the functions required to take data directly from a threewire serial data bus and convert it to a precise voltage, including: an input shift register, data latches, a precision voltage reference, a precision 10-bit digital to analog converter, and an output buffer amplifier.

The serial data interface is capable of clock frequencies as high as 20MHz, allowing update rates as high as two words per microsecond. The UCC5950 accepts commands encoded as 2's-complement binary.

The data converter in the UCC5950 is inherently monotonic, making this part ideal for use in closed-loop servo control systems as well as open-loop data conversion. The UCC5950 uses a unique segmented data converter which offers differential linearity better than 1 LSB, integral linearity better than 2 LSB, and fast conversion.

#### BLOCK DIAGRAM

#### **ABSOLUTE MAXIMUM RATINGS**

| VDD Supply Voltage 6.5V                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Voltage, Any Input –0.3V to VDD+0.3V                                                                                                                                                                          |

| Output Current, Any Output ±5mA                                                                                                                                                                                     |

| Operating Temperature                                                                                                                                                                                               |

| Storage Temperature                                                                                                                                                                                                 |

| Lead Temperature                                                                                                                                                                                                    |

| All voltages with respect to GND. All currents are positive into,<br>negative out of, the specified terminal. Consult Packaging Sec-<br>tion of Databook for thermal limitations and considerations of<br>packages. |

|                                                                                                                                                                                                                     |

#### **CONNECTION DIAGRAM**

ELECTRICAL CHARACTERISTICS Unless otherwise stated, all specifications apply for 4.5V < VDD < 5.5V, REFOUT Load < 100pF, DACOUT Load < 100pF, 0°C < TA < +70°C, and TA = TJ.

| PARAMETER                               | TEST CONDITIONS                          | MIN. | TYP. | MAX. | UNITS |

|-----------------------------------------|------------------------------------------|------|------|------|-------|

| OVERALL SECTION                         |                                          |      |      |      |       |

| Supply Current                          | SLEEP = 0V                               |      | 1.5  | 5    | mA    |

| Supply Current                          | irrent SLEEP = 5V 0                      |      | 0.1  | 10   | μA    |

| REFERENCE SECTION                       |                                          | -    |      |      | -     |

| REFOUT Output Voltage                   |                                          | 2.10 | 2.15 | 2.20 | V     |

| REFOUT Change with VDD                  | 4.5V < VDD < 5.5V                        |      | 1    | 10   | mV    |

| REFOUT Change with Load                 | –1mA < IREFOUT < 1mA                     |      | 1    | 10   | mV    |

| D/A SECTION                             |                                          |      |      |      |       |

| Integral Nonlinearity                   | (Note 1)                                 |      |      |      | LSB   |

| Differential Nonlinearity               |                                          |      |      | 1    | LSB   |

| Full Scale Difference from 1.4924 x REF | le Difference from 1.4924 x REF –8       |      |      | 8    | LSB   |

| Zero Scale Difference from 0.5089 x REF | fference from 0.5089 x REF –8            |      |      | 8    | LSB   |

| DACOUT Full Scale Rise/Fall Time        | From 10% to 90% of swing (Note 4)        | 0.7  |      | 1.1  | μs    |

| DACOUT Full Scale Settling Time (TS)    | (Note 2, 3, 4)                           | 1.4  |      | 2.5  | μs    |

| DACOUT Change with VDD                  | 4.5V < VDD < 5.5V                        | 1.5  |      | 10   | mV    |

| DACOUT Change with Load                 | hange with Load -1mA < IDACOUT < 1mA     |      | 1.2  | 10   | mV    |

| LOGIC SECTION                           |                                          |      |      |      |       |

| Logic Input Threshold                   |                                          | 1.5  | 2.5  | 3.5  | V     |

| Logic Input Current                     | 0V < VIN < VDD                           |      |      | 5    | μA    |

| Logic Input Capacitance                 | (Note 4)                                 |      | 2.7  | 10   | pF    |

| SLOD Setup Time to SCLK low (TSLS)      | (Note 4)                                 | 50   |      |      | ns    |

| SLOD Hold Time from SCLK high (TSLH)    | From 10 <sup>TH</sup> SCLK high (Note 4) | 50   |      |      | ns    |

| SDIO Setup Time to SCLK high (TDS)      | (Note 4)                                 | 15   |      |      | ns    |

| SDIO Hold Time from SCLK high (TDH)     | (Note 4)                                 | 7    |      |      | ns    |

Note 1: Integral nonlinearity is defined as the worst deviation of the converter output from the best-fit straight line through all converter output codes. Note 2: From 10<sup>TH</sup> Rising Edge of SCLK.

Note 3: Settling time is to 1% of final value.

Note 4: Guaranteed by design. Not 100% tested in production.

2

1

0 25 50 75

Temperature (°C)

100 125

DACOUT

-4∟ -2

-1

0

Load Current (mA)

1

2

#### **PIN DESCRIPTIONS**

DACOUT: The output of the 10-bit D/A Converter. For best settling time, minimize load capacitance.

DACOUT will go to a voltage between 1.094V and 3.208V depending on the digital code loaded into the latches. The digital code follows this pattern:

| Input Code | Typical DACOUT | Significance |

|------------|----------------|--------------|

| 100000000  | 1.094V         | Zero Scale   |

| 100000001  | 1.096V         |              |

| 100000010  | 1.098V         |              |

|            |                |              |

| 1111111111 | 2.151V         |              |

| 000000000  | 2.153V         | Mid Scale    |

| 000000001  | 2.155V         |              |

|            |                |              |

| 0111111110 | 3.206V         |              |

| 0111111111 | 3.208V         | Full Scale   |

GND: All signals are referenced to GND.

**REFOUT:** The output of the temperature-compensated 2.15V reference. DO NOT BYPASS REFOUT! For best stability and transient response, minimize capacitance on REFOUT.

SERIAL DATA INTERFACE TIMING AND LOGIC TABLE

SCLK: Data is clocked into the D/A after SLOD goes low on rising edges of SCLK. After 10 rising edges of SCLK, the data is latched into the D/A output register and the output is updated. Further clock signals on SCLK are ignored until SLOD initiates a new read cycle.

SDIO: After SLOD goes low, data is clocked into the D/A from the SDIO input, on rising edges of SCLK, LSB first. After 10 rising edges, data is latched and converted, and further SCLK and SDIO information is ignored.

SLEEP: SLEEP is the power-down input to the D/A. In systems not requiring this function, wire SLEEP to GND.

SLOD: SLOD is the chip-select input to the UCC5950. SLOD going low selects the D/A and enables clocking of data from SDIO into the D/A. After 10 SCLK pulses, the D/A is updated and SLOD is ignored until SLOD goes high and again goes low.

VDD: All analog and digital functions are powered from VDD. VDD should be a well-regulated supply to minimize output variations. Bypass VDD to GND with a ceramic capacitor very close to the UCC5950.

## SLOD SCLK TSLS TPER TDC TSLH SDIO XX MSB TDS TDH DACOUT ΤS UDG-95035

| SLOD | Internal Flag | SCLK        | SDIO       | Internal Count | Action                                             | DACOUT |

|------|---------------|-------------|------------|----------------|----------------------------------------------------|--------|

| 1    | 1             | don't care  | don't care | 0              | no action                                          | V(t)   |

| 0    | 0             | rising edge | DATA       | <10            | Shift In DATA                                      | V(t)   |

| 0    | 0             | rising edge | DATA       | 10             | Latch New DATA<br>Set Internal Flag<br>Reset Count | V(t+1) |

| 0    | 1             | don't care  | don't care | 0              | no action                                          | V(t)   |

UNITRODE INTEGRATED CIRCUITS 7 CONTINENTAL BLVD. • MERRIMACK, NH 03054 TEL. (603) 424-2410 • FAX (603) 424-3460

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated