**TECHNICAL DATA**

## DRIVER/AMPLIFIER CIRCUIT C4070

## For Serial/Current Output Type MOS Linear Image Sensors

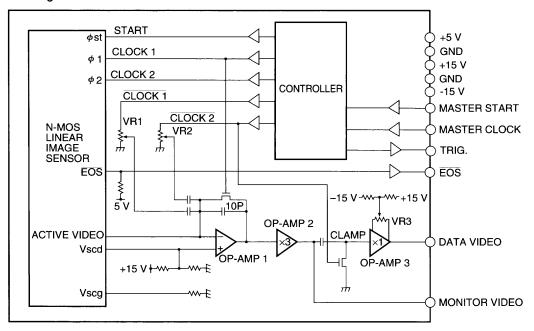

The C4070 is a low-noise driver/amplifier circuit designed specifically for use with Hamamatsu serial/current output type MOS linear image sensors (S3901, S3904, S3902, S3903). The C4070 driver/amplifier circuit includes a generator for a start pulse and two-phase clock pulses used to drive a MOS linear image sensor and the charge amplifier used to read out the video signal in the integration mode. The signal inputs required are only a master start pulse, a master clock pulse, +5V and ±15V.

In addition, the C4091 pulse generator is available, which supplies the C4070 with a master start pulse and a master clock pulse.

## **FEATURES**

- Structure allows easy cooling and optical alignment of MOS image sensor

- Simple operation: only a master start pulse, a master clock pulse, +5V and ±15V required

- Low noise

- Wide dynamic range

- Simple adjustment

## **DESCRIPTIONS OF TERMINALS**

|        | Terminals        | Symbols                                              | Descriptions                                                                                                                                                                             |

|--------|------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input  | Supply Voltage   | V <sub>d</sub> (+5)<br>V <sub>a</sub> (+15)<br>(-15) | +5 Vdc, 70 mA<br>+15 Vdc, 30 mA<br>-15 Vdc, 30 mA                                                                                                                                        |

|        | Master Start φms | St.                                                  | CMOS logic compatible. Positive logic. For initializing the circuit and the MOS shift register.                                                                                          |

|        | Master Clock φmc | CLK                                                  | CMOS logic compatible. The maximum frequency is 375 kHz. For synchronizing the circuit and the MOS shift register.                                                                       |

| Output | Monitor Video    | M.V.                                                 | Positive output. This is the integrated video signal from the MOS image sensor, and it is used for monitoring when cancelling the switching noises. Obtained synchronized with $\phi$ 2. |

|        | Data Video       | D.V.                                                 | Positive output. This is the integrated, low-noise video signal of the MOS image sensor.                                                                                                 |

|        | Sample-and-hold  | Trig.                                                | CMOS logic compatible. Positive logic. This output can be used as the trigger signal for the sample-and-hold or A/D conversion.                                                          |

|        | End of Scan      | EOS                                                  | CMOS logic compatible. Negative logic. This is the end-of-scan signal of the MOS shift register and it is obtained synchronized with $\phi 2$ right after the last element is scanned.   |

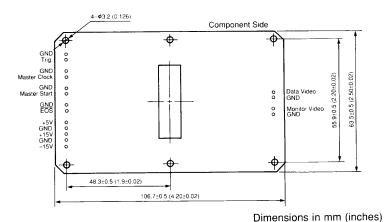

Figure 1: Dimensional Outline and Terminals

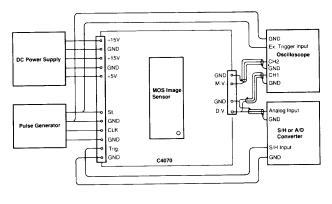

Figure 2: Wiring Example

Figure 3: Block Diagram

Caution)

KACCC0062EA

The relation between the output charge from the MOS image sensor and the output voltage of the data video in the C4070 is represented by next equation.

$$V_{out}$$

(DATA VIDEO) (V) = 3 ×  $\frac{\text{OUTPUT CHARGE (C)}}{10 \times 10^{-12} \text{ (F)}}$

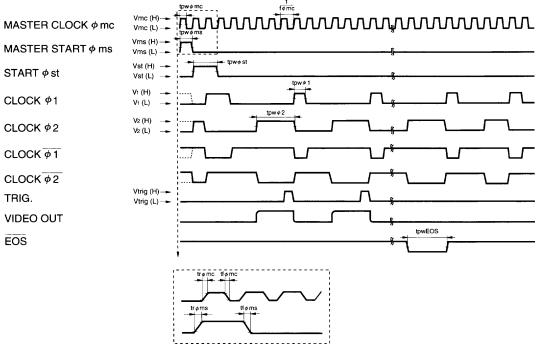

Figure 4: Timing Diagram

If an EOS pulse is output, the trigger output stops and the frequency of  $\phi 1$  and  $\phi 2$  changes from 6 times to 5 times the master clock.

KACCC0053EA