Integrated Circuits

## ULN8510A/EP/R ULN8511A/EP/R

)ata Shee **2744**!

#### ULN8510A/R ULN8511A/R

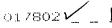

Dwg. PS-005

### OCTAL LOW-SPEED EIA RECEIVERS

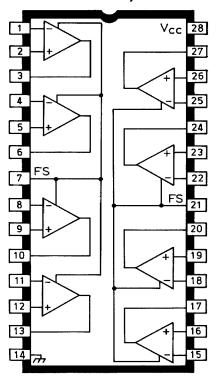

Each containing eight differential line receivers, the ULN8510A/EP/R and ULN8511A/EP/R are designed for cost-effective data communications meeting the requirements of RS-232C, RS-423A and CCITT recommendations V.10, V.11, and V.28 for low-speed applications without external components. The receivers include failsafing for protection against certain input fault conditions, Schottky TTL output stages, and output current limiting. The ULN8510A/EP/R includes internal low-pass filtering for data transmission rates up to 200 kb/s and meets the low-speed applications of RS-422A. The ULN8511A/EP/R is for use with increased data rates up to 10 Mb/s. Except for the internal low-pass filtering, the ULN8510x and ULN8511x are pin-compatible and completely interchangeable.

The ULN8510A and ULN8511A are supplied in 28-pin dual in-line plastic packages with copper lead frames for improved power dissipation capabilities; devices with package suffix code 'R' are supplied in 28-pin dual in-line cer-DIP hermetic packages for operation under adverse environmental conditions; suffix code 'EP' indicates a 28-lead PLCC for minimum-area, surface-mount applications.

#### **FEATURES**

- Dual, Four-Channel, Failsafing Control

- Schottky TTL Output Stages

- Output Current Limiting

- Meets EIA RS-232C, RS-422A, and RS-423A

- Replaces NE5180/81 & UC5180/81

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>CC</sub>             | <b>7.0 V</b> |

|---------------------------------------------|--------------|

| V <sub>IC</sub>                             | ± 15 V       |

| Differential Input Voltage, V <sub>ID</sub> |              |

| Output Current, IOUT                        |              |

| Package Power Dissipation,                  |              |

| P <sub>D</sub>                              | 1.2 W        |

| Operating Temperature Range,                |              |

| T <sub>A</sub> 0°C                          | to +70°C     |

| Storage Temperature Range,                  |              |

| T <sub>S</sub> – <b>55°C</b> to             | +125°C       |

SPRAGUE

SEMICONDUCTOR GROUP

# ULN8510A/EP/R and ULN8511A/EP/R octal low-speed eia receivers

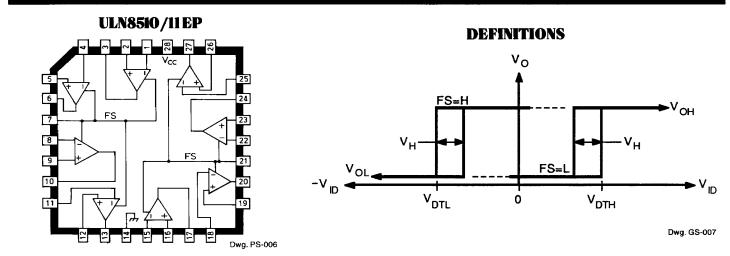

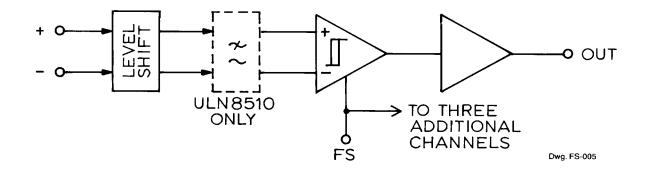

#### SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM (ONE OF EIGHT CHANNELS SHOWN)

#### TRUTH TABLE

| Input                                                     | Failsafe<br>Input | Output |

|-----------------------------------------------------------|-------------------|--------|

| $V_{ID} \ge 0.2 \text{ V}$<br>$V_{ID} \ge -0.2 \text{ V}$ | X                 | - T    |

| $\begin{array}{l} V_{ID} = 0 \\ V_{ID} = 0 \end{array}$   | Û<br>H            | L<br>H |

X = Don't Care.

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000 Copyright © 1988 Sprague Electric Company, December 1988

#### **APPLICATIONS INFORMATION**

**Failsafing.** These devices provide a failsafe operating mode to guard against input faults as defined in RS-422A and RS-423A. The receivers are programmed by connecting the appropriate failsafe input to  $V_{CC}$  or ground. A failsafe connection to  $V_{CC}$  provides a logic '1' output under fault conditions (both inputs to ground, to  $V_{CC}$ , opened, or shorted together), a failsafe connection to ground provides a logic '0' under fault conditions. Under normal operating conditions (1  $V_{pp}$ ), if either input is faulted (to ground, to  $V_{CC}$ , or opened), but not both, the system will continue to function but with reduced noise immunity.

Limited failsafing for single-ended operation (RS-232 operation) is provided by tying the unused input to ground. A failsafe connection to  $V_{\rm CC}$  provides a logic '1' output under fault conditions to ground, a failsafe connection to ground provides a logic '0' output under fault conditions to ground.

**Input Filtering.** The ULN8510A/EP/R has input low-pass filtering for improved noise rejection. The filtering is a function of both signal level and frequency. These devices are intended for low-speed data applications to 200 kb/s.

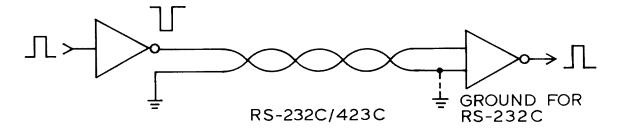

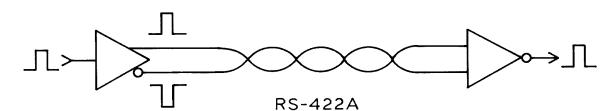

#### **DATA COMMUNICATIONS**

Dwg. OS-002

SEMICONDUCTOR GROUP

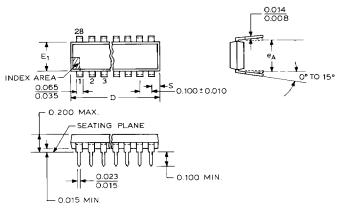

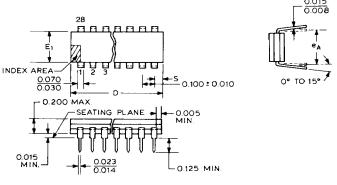

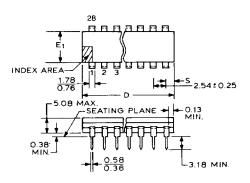

#### **ULN8510A and ULN8511A — PLASTIC DUAL IN-LINE PACKAGE**

#### **DIMENSIONS IN INCHES**

| Dwg. No. A | 4-13.642 IN |

|------------|-------------|

|------------|-------------|

| D              | Body Length    | 1.380/1.460 |

|----------------|----------------|-------------|

| E,             | Body Width     | 0.480/0.560 |

| e <sub>A</sub> | Row Spacing    | 0.600 BSC   |

| S              | Lead CL to End | 0.075 REF   |

### DIMENSIONS IN MILLIMETERS (BASED ON I" = 25.40 mm)

Dwg. No. A-13.642 MM

| D              | Body Length    | 35.05/37.08 |

|----------------|----------------|-------------|

| E,             | Body Width     | 12.19/14.22 |

| e <sub>A</sub> | Row Spacing    | 15.24/BSC   |

| S              | Lead CL to End | 1.90 REF    |

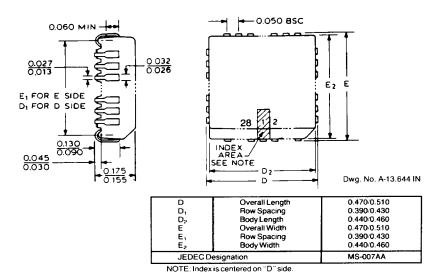

#### **ULN8510R and ULN8511R — HERMETIC CerDIP PACKAGE**

#### **DIMENSIONS IN INCHES**

Dwg. No. A-13.650 IN

| D              | Body Length    | 1.490 Max.           |  |

|----------------|----------------|----------------------|--|

| E <sub>1</sub> | Body Width     | 0.500/0.610          |  |

| e <sub>A</sub> | Row Spacing    | 0.590/0.620          |  |

| S              | Lead CL to End | 0.100 Max.           |  |

| M38510H, Case  | e Outline      | D-10 Configuration 1 |  |

### DIMENSIONS IN MILLIMETERS (BASED ON I" = 25.40 mm)

Dwg. No. A-13.650 MM

| D                     | Body Length    | 37.85 Max.  |

|-----------------------|----------------|-------------|

| E <sub>1</sub>        | Body Width     | 12.70/15.49 |

| e <sub>A</sub>        | Row Spacing    | 14.99/15/75 |

| S                     | Lead CL to End | 2.54 Max.   |

| M38510H, Case Outline |                |             |

- A. Dimensions shown as \_\_\_\_\_/ \_\_\_ are Min./Max.

- **B.** Lead thickness is measured at seating plane or below.

- C. Lead spacing tolerance is non-cumulative.

- D. Exact body and lead configuration at vendor's option within limits shown.

- E. Lead gauge plane is 0.030" (0.762 mm) max. below seating plane.

## ELECTRICAL CHARACTERISTICS at $T_A=+25^{\circ}C$ , $V_{CC}=4.75$ V to 5.25 V, $V_{IC}=\pm7.0$ V (unless otherwise noted).

|                               |                  |                                                                    | Limits |              |       |

|-------------------------------|------------------|--------------------------------------------------------------------|--------|--------------|-------|

| Characteristic                | Symbol           | Test Conditions                                                    | Min.   | Max.         | Units |

| Diff. Input Threshold Voltage | V <sub>DTH</sub> | Output High                                                        | _      | 0.2          | V     |

| •                             |                  | Output High (Note 1)                                               | _      | 0.4          | V     |

|                               | V <sub>DTL</sub> | Output Low                                                         | _      | 0.2          | V     |

|                               |                  | Output Low (Note 1)                                                | _      | -0.4         | V     |

| Hysteresis                    | V <sub>H</sub>   |                                                                    | 40     | 140          | mV    |

| Open-Circuit Input Voltage    | V <sub>IOC</sub> |                                                                    | _      | 0.5          | ٧     |

| Input Current                 | I <sub>IN</sub>  | V <sub>CC</sub> = 5.25 V, V <sub>IN</sub> = 10 V (Note 2)          |        | 3.25         | mA    |

|                               |                  | $V_{CC} = 5.25 \text{ V}, V_{IN} = -10 \text{ V} \text{ (Note 2)}$ |        | - 3.25       | mA    |

| Input Resistance              | R <sub>IN</sub>  | $V_{IN} = 0$                                                       | 4.0    | 7.0          | kΩ    |

|                               |                  | 3.0 V ≤ V <sub>in</sub>  ≤25V                                      | 3.0    | 7.0          | kΩ    |

| Input Capacitance             | C <sub>in</sub>  |                                                                    | _      | 100          | pF    |

| Failsafe Input Voltage        | V <sub>IH</sub>  |                                                                    | 4.0    | _            | V     |

|                               | V <sub>IL</sub>  |                                                                    | -      | 0.5          | V     |

| Failsafe Input Current        | I <sub>IH</sub>  | $V_{IN} = 4.0 V$                                                   | _      | <b>- 100</b> | μΑ    |

|                               | I <sub>IL</sub>  | $V_{IN} = 0.5 V$                                                   | _      | <b>-500</b>  | μΑ    |

| Output Voltage                | V <sub>OH</sub>  | $V_{ID} = 1.0 \text{ V}, I_{OUT} = -440 \mu\text{A}$               | 2.7    | _            |       |

|                               | V <sub>OL</sub>  | $V_{ID} = 1.0 \text{ V}, I_{OUT} = 4.0 \text{ mA}$                 | _      | 0.4          | V     |

|                               |                  | $V_{ID} = 1.0 \text{ V}, I_{OUT} = 8.0 \text{ mA}$                 | _      | 0.5          | V     |

| Output Short-Circuit Current  | los              | V <sub>ID</sub> = 1.0 V (Note 3)                                   | _      | <b>- 100</b> | mA    |

| Propagation Delay             | t <sub>PLH</sub> | $C_L = 50 \text{ pF}, V_{in} = 1.0 \text{ V}$                      | _      | 500          | ns    |

|                               | t <sub>PHL</sub> | $C_L = 50 \text{ pF}, V_{in} = 1.0 \text{ V}$                      | _      | 500          | ns    |

| Frequency Response            |                  | V <sub>in</sub> = 400 mVpp, 100 kHz Square Wave                    | Note 4 | _            |       |

|                               |                  | V <sub>in</sub> = 1.0 Vpp, 5.0 MHz Square Wave                     | Note 5 | _            | _     |

|                               |                  | V <sub>in</sub> = 1.0 Vpp, 5.5 MHz Square Wave                     | _      | Note 6       |       |

|                               |                  | V <sub>in</sub> = 2.0 Vpp, 12.5 MHz Square Wave                    | _      | Note 7       |       |

| Supply Current                | Icc              | No Signal                                                          | _      | 135          | mA    |

Notes: 1. 500  $\Omega$  resistor in series with both inputs.

2. Inputs not under test grounded.

3. Each output tested separately.

4. Presence of 100 kHz TTL output (All devices).

5. Presence of 5.0 MHz TTL output (ULN8511A/EP/R only).

6. No 5.5 MHz TTL output component present (ULN8510A/EP/R only).

7. No 12.5 MHz TTL output component present (ULN8510A/EP/R only).

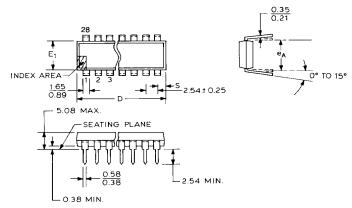

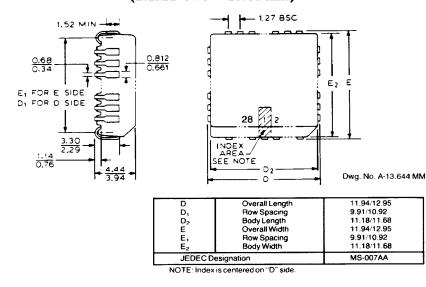

#### ULN8510EP and ULN8511EP PLASTIC LEADED CHIP CARRIER

#### **DIMENSIONS IN INCHES**

### DIMENSIONS IN MILLIMETERS (BASED ON I" = 25.40 mm)

The Sprague Electric Company reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the design of its products. Components made under military approvals will be in accordance with the approval requirements.

The information included herein is believed to be accurate and reliable. However, the Sprague Electric Company assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

- A. Dimensions shown as \_\_\_\_\_ / \_\_\_\_ are Min./Max.

- B. Lead thickness is measured at seating plane or below.

- C. Lead spacing tolerance is non-cumulative.

- D. Exact body and lead configuration at vendor's option within limits shown.

**SPRAGUE**

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000