### **Product Features**

- Dedicated clock buffer power pins for reduced noise, crosstalk and jitter

- Buffer XIN Reference clock output

- Input clock frequency 33.3 MHz

- Output frequencies of 33.3, 66.6, 100 and 133.3 MHz selectable (PCIX requirements)

- One output bank of 5 clocks.

- SMBus clock control interface for individual clock disabling and SSCG control

- Output clock duty cycle is 50% (± 5%)

- <250 pS skew between output clocks within a bank

- Output jitter <175 pSec.

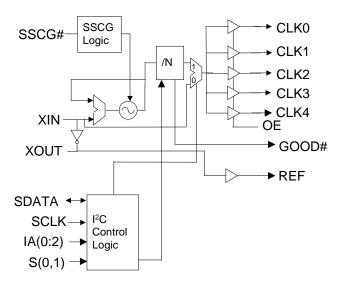

**Block Diagram**

- Spread Spectrum feature for reduced EMI

- OE pins for entire output bank enable control and testability

- 28 Pin SSOP and TSSOP package

### Test Mode Logic Table

| INPUT PINS |      |      | OUTPUT PINS |           |  |  |  |

|------------|------|------|-------------|-----------|--|--|--|

| OE         | S1   | S0   | CLK(0:4)    | REF       |  |  |  |

| HIGH       | LOW  | LOW  | XIN         | XIN       |  |  |  |

| HIGH       | LOW  | HIGH | 2 * XIN     | XIN       |  |  |  |

| HIGH       | HIGH | LOW  | 3 * XIN     | XIN       |  |  |  |

| HIGH       | HIGH | HIGH | 4 * XIN     | XIN       |  |  |  |

| LOW        | Х    | Х    | Tri-State   | Tri-State |  |  |  |

**Note:** XIN is the frequency of the clock on the device's XIN pin.

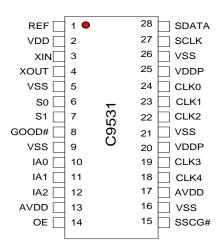

# **Pin Configuration**

| Pin No.               | Pin      | PWR  | I/O | Description                                                                                                                                                                                    |

|-----------------------|----------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | Name     |      |     |                                                                                                                                                                                                |

| 3                     | XIN      | VDDA | I   | Crystal Buffer input pin. Connects to a crystal, or an external clock source. Serves as input clock TCLK, in Test mode.                                                                        |

| 4                     | XOUT     | VDDA | 0   | Crystal Buffer output pin. Connects to a crystal only. When a Can Oscillator is used or in Test mode, this pin is kept unconnected.                                                            |

| 1                     | REF      | VDD  | 0   | Buffered inverted outputs of the signal applied at Xin, typically 33.33 MHz                                                                                                                    |

| 14*                   | OE       | VDD  | I   | Output Enable for clock bank. Causes the CLK (0:4) output clocks to be in a Tri-state condition when driven to a logic low level.                                                              |

| 24, 23, 22,<br>19, 18 | CLK(0:4) | VDDP | 0   | A bank of Five 33.3, 66.6, 100.0 or 133.3 MHz output clocks (1x, 2x, 3x or 4x Xin clock).                                                                                                      |

| 8                     | GOOD#    | VDD  | 0   | When his output signal is a logic low level, it indicates that the output clocks of the bank are locked to the input reference clock. This output is latched.                                  |

| 6*, 7*                | S(0,1)   | VDD  | I   | Clock Bank selection bits. These control the clock frequency that will<br>be present on the outputs of the bank of buffers. See table on page<br>one for frequency codes and selection values. |

| 20, 25                | VDDP     |      | PWR | 3.3V common power supply pin for all PCI clocks CLK (0:4).                                                                                                                                     |

| 10*, 11*,<br>12*      | IA(0:2)  | VDD  | I   | SMBus address selection input pins. See SMBus Address table, pg. 4.                                                                                                                            |

| 15*                   | SSCG#    | VDD  | Ι   | Enables Spread Spectrum clock modulation when at a logic low level, see pg. 3.                                                                                                                 |

| 28                    | SDATA    | VDD  | I/O | Data for the internal SMBus circuitry, see pg. 4.                                                                                                                                              |

| 27                    | SCLK     | VDD  | I   | Clock for the internal SMBus circuitry, see pg. 4.                                                                                                                                             |

| 13, 17                | AVDD     | -    | Ι   | Power for internal analog circuitry. This supply should have a separately decoupled current source from VDD.                                                                                   |

| 2                     | VDD      | -    | PWR | Power supply for internal Core logic                                                                                                                                                           |

| 5, 9, 16, 21,<br>26   | VSS      | -    | PWR | Ground pins for the device                                                                                                                                                                     |

Note: Pin numbers ending with a \* indicate that they contain device internal pull-up resistors that will insure that they are sensed as a logic 1 if no external circuitry is connected to them.

A bypass capacitor (0.1  $\mu$ F) should be placed as close as possible to each VDD pin. If these bypass capacitors are not close to the pins, their high frequency filtering characteristic will be cancelled by the lead inductance of the trace. PWR = Power connection, I = Input, O = Output and I/O = both input and output functionality of the pin(s).

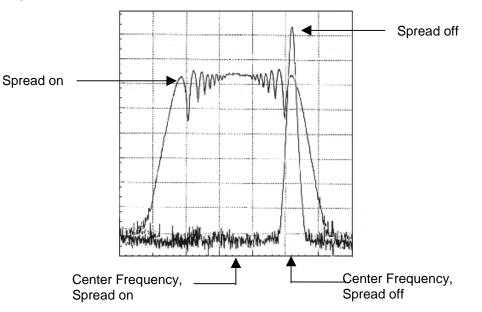

### **Spectrum Spread Clocking**

#### **Down Spread Description**

Spread Spectrum is a modulation technique for distributing clock period over a certain bandwidth (called Spread Bandwidth). This technique allows the distribution of the undesirable electromagnetic energy (EMI) over a wide range of frequencies therefore reducing the average radiated energy present at any frequency over a given time period. As the spread is specified as a percentage of the resting (non-spread) frequency value, it is effective at the fundamental and, to a greater extent, at all of its harmonics.

In this device Spread Spectrum is enabled externally through pin 15 (SSCG#) or internally via SMBus Byte 0 Bit 0 and 6. Spread spectrum is enabled externally when the SSCG# pin is low. This pin has an internal device pull up resistor, which causes its state to default to a HIGH (spread spectrum modulation disabled) unless externally forced to a low. It may also be enabled by programming SMBus Byte 0 Bit 0 LOW (to enable SMBus control of the function) and then programming SMBus byte 0 bit 6 low to set the feature active.

#### **Spectrum Spreading Selection Table**

| Output clock      | % OF FREQUE           | NCY SPREADING         |             |

|-------------------|-----------------------|-----------------------|-------------|

| Frequency         | SMBus Byte 0 Bit 5 =0 | SMBus Byte 0 Bit 5 =1 | MODE        |

| 33.3 MHz (XIN)    | 1.0% (-1.0% + 0%)     | 0.5% (-0.5% + 0%)     | Down Spread |

| 66.6 MHz (XIN*2)  | 1.0% (-1.0% + 0%)     | 0.5% (-0.5% + 0%)     | Down Spread |

| 100.0 MHz (XIN*3) | 1.0% (-1.0% + 0%)     | 0.5% (-0.5% + 0%)     | Down Spread |

| 133.3 MHz (XIN*4) | 1.0% (-1.0% + 0%)     | 0.5% (-0.5% + 0%)     | Down Spread |

When SSCG is enabled, the device will down spread the clock over a range that is 1% of its resting frequency. This means that for a 100 MHz output clock the frequency will sweep through a spectral range from 99 to 100 MHz.

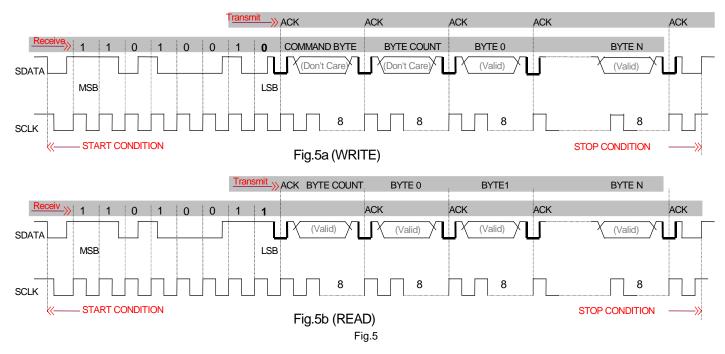

### 2-Wire SMBus Control Interface

The 2-wire control interface implements a write slave only interface according to SMBus specification. The device can be read back. Sub addressing is not supported, thus all <u>preceding bytes must be sent</u> in order to change one of the control bytes. The 2-wire control interface allows each clock output to be individually enabled or disabled. 100 Kbits/second (standard mode) data transfer is supported.

Through the use of the IA0, IA1, and IA2 pins the SMBus address of the device may be changed so that multiple devices may reside on a single SMBus control signaling bus and not interfere with each other.

#### SMBus Address Selection Table

| SMBus address of the device | IA0 BIT (Pin 10) | IA1 BIT (Pin 11) | IA2 BIT (Pin 12) |

|-----------------------------|------------------|------------------|------------------|

| DE                          | 0                | 0                | 0                |

| DC                          | 1                | 0                | 0                |

| DA                          | 0                | 1                | 0                |

| D8                          | 1                | 1                | 0                |

| D6                          | 0                | 0                | 1                |

| D4                          | 1                | 0                | 1                |

| D0                          | 0                | 1                | 1                |

| D2                          | 1                | 1                | 1                |

During normal data transfer, the SDATA signal only changes when the SCLK signal is low, and is stable when SCLK is high. There are two exceptions to this. A high to low transition on SDATA while SCLK is high is used to indicate the start of a data transfer cycle. A low to high transition on SDATA while SCLK is high indicates the end of a data transfer cycle. Data is always sent as complete 8-bit bytes, after which an acknowledge is generated. The first byte of a transfer cycle is a 7-bit address with a Read/Write bit (R/W#) as the LSB. R/W# = 1 in read mode.

The device will respond to writes to 10 bytes (max) of data to its selected address by generating the acknowledge (low) signal on the SDATA wire following reception of each byte.

### **Serial Control Registers**

**NOTE:** The Pin# column lists the affected pin number where applicable. The @Pup column gives the state at true power up. Bytes are set to the values shown only after true power up event occurs. Following the acknowledge of the Address Byte (D2), two additional bytes must be sent:

- 1) "Command Code " byte, and

- 2) "Byte Count" byte.

Although the data (bits) in these two bytes are considered "don't care"; they must be sent and will be acknowledged.

#### Byte 0: Function Select Register

| Bit | @Pup | Pin# | Description                                                                                                   |

|-----|------|------|---------------------------------------------------------------------------------------------------------------|

| 7   | 1    | -    | Test Mode Enable. 1=normal operation, 0 = Test mode                                                           |

| 6   | 0    | 15   | Spread Spectrum modulation control bit (effective only when Bit 0 of this register is set to a 0) 0=OFF, 1=ON |

| 5   | 1    | -    | SSCG Spread width select. $1 = 0.5\%$ , $0 = 1.0\%$ See Table below for clarification                         |

| 4   | 0    | 7    | S1 Bank A MSB frequency control bit (effective only when Bit 0 of this register is set to a 0)                |

| 3   | 0    | 6    | S0 Bank A LSB frequency control bit (effective only when Bit 0 of this register is set to a 0)                |

| 2   | 0    | -    | Not used                                                                                                      |

| 1   | 0    | -    | Not used                                                                                                      |

| 0   | 1    | -    | Hardware/SMBus frequency control. 1=Hardware (pins 6, 7, and 15), 0=SMBus Byte 0 bits 3, 4, and 6             |

#### Clarification Table for Byte0, bit5

| Byte 0, bit6 | Byte0, bit5 | Description                         |

|--------------|-------------|-------------------------------------|

| 0            | 0           | Frequency generated from second PLL |

| 0            | 1           | Frequency generated from XIN        |

| 1            | 0           | Spread @ -1.0%                      |

| 1            | 1           | Spread @ -0.5%                      |

### Test Table

These output frequencies will be present when SMBus byte 0 bit 7 has been set to a logic 0 state.

| Test Function |              | Outputs |  |  |  |  |  |  |  |

|---------------|--------------|---------|--|--|--|--|--|--|--|

| Clock         | CLK(0:4) REF |         |  |  |  |  |  |  |  |

| Frequency     | XIN/4        | XIN     |  |  |  |  |  |  |  |

| Table 3       |              |         |  |  |  |  |  |  |  |

#### Note:

1. XIN is the frequency of the clock that is present on the XIN input during test mode.

#### **Byte 1: CPU Register (1 = Enable, 0 = Stopped)**

| Bit | @Pup | Pin# | Description        |

|-----|------|------|--------------------|

| 7   | 1    | -    | Reserved           |

| 6   | 1    | -    | Reserved           |

| 5   | 1    | 1    | REF Enable/Stopped |

| 4   | 1    | -    | Reserved           |

| 3   | 1    | -    | Reserved           |

| 2   | 1    | -    | Reserved           |

| 1   | 1    | -    | Reserved           |

| 0   | 1    | -    | Reserved           |

Byte 2: PCI Register (1 = Enable, 0 = Stopped)

| Bit | @Pup | Pin# | Description         |

|-----|------|------|---------------------|

| 7   | 1    | -    | Reserved            |

| 6   | 1    | -    | Reserved            |

| 5   | 1    | -    | Reserved            |

| 4   | 1    | 18   | CLK4 Enable/Disable |

| 3   | 1    | 19   | CLK3 Enable/Disable |

| 2   | 1    | 22   | CLK2 Enable/Disable |

| 1   | 1    | 23   | CLK1 Enable/Disable |

| 0   | 1    | 24   | CLK0 Enable/Disable |

Note: Stopping a clock indicated that the clock output is fixed in a logic low state. This effect will occur within 2 clock cycles from the time the bit is set and does so in a manner so as not to cause any short or runt clock cycles. When the stop is bit is changed from a stopped state to a running state the same (maximum 2 click latency) delay occurs with the first cycle being full in period (for the frequency that is selected).

#### Internal Crystal Oscillator

This device will operate in two input reference clock configurations. In its simplest mode a 33.33 MHz fundamental cut parallel resonant crystal is attached to the XIN and XOUT pins.

In the second mode a 33.33MHz input reference clock is driven in on the XIN clock from an external source. In this application the XOUT pin is left disconnected.

### **Output Clock Tri-state Control**

All of the clocks in the Bank may be placed in a tri-state condition by bringing their relevant OE pins to a logic low state. This transition to and from a tristate and active condition is a totally asynchronous event and clock glitching may occur during the transitioning states. This function is intended as a board level testing feature. When output clocks are being enabled and disabled in active environments the SMBus control register bits are the preferred mechanism to control these signals in an orderly and predictable manner.

Both output enable pins contain internal pull-up resistors that will insure that a logic 1 (high) is maintained and sensed by the device if no external circuitry is connected to these pins.

### **Output Clock Frequency Control**

All of the output clocks have their frequency selected by the logic state of the S0 and S1 control bits. The source of these control signals is determined by the SMBus register Byte 0 Bit 0. At initial power up this bit is set of a logic 1 state and

## **Output Clock Frequency Control (Cont.)**

thus the frequency selections are controlled by the logic levels present on the device's S(0,1) pins. If the application does not use an SMBus interface then hardware frequency selection S(0,1) must be used. If it is desired to control the output clocks using an SMBus interface, then this bit (Byte 0 Bit 0) must first be set to a low state. After this is done the device will use the contents of the internal SMBus register Bytes 0 Bits 3 and 4 to control the output clock's frequency.

### **Absolute Maximum Ratings**

| Maximum Power Supply:             | 5.5               |

|-----------------------------------|-------------------|

| Storage Temperature:              | -65ºC to + 150ºC  |

| Operating Temperature:            | 0°C to +70°C      |

| Maximum ESD protection            | 2000V             |

| Maximum Input Voltage Relative to | o VDD: VDD + 0.3V |

| Maximum Input Voltage Relative to | o VSS: VSS - 0.3V |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, Vin and Vout should be constrained to the range: VSS<(Vin or Vout)<VDD Unused inputs must always be tied to an appropriate logic voltage level (either VSS or VDD).

| DC Parameters                     |                   |          |          |         |          |                                                             |  |  |  |  |

|-----------------------------------|-------------------|----------|----------|---------|----------|-------------------------------------------------------------|--|--|--|--|

| Characteristic                    | Symbol            | Min      | Тур      | Max     | Units    | Conditions                                                  |  |  |  |  |

| Input Low Voltage                 | VIL1              | -        | -        | 1.0     | Vdc      | note 1                                                      |  |  |  |  |

| Input High Voltage                | VIH1              | 2.0      | -        | -       | Vdc      |                                                             |  |  |  |  |

| Input Low Voltage                 | VIL2              | -        | -        | 1.0     | Vdc      | note 2                                                      |  |  |  |  |

| Input High Voltage                | VIH2              | 2.2      | -        | -       | Vdc      |                                                             |  |  |  |  |

| Input Low Current (@VIL =<br>VSS) | IIL               | -66      |          | -5      | μA       | For internal Pull up resistors, note 1 and note 3           |  |  |  |  |

| Input High Current (@VIL = VDD)   | IIH               |          |          | 5       | μA       |                                                             |  |  |  |  |

| Tri-State leakage Current         | loz               | -        | -        | 10      | μA       |                                                             |  |  |  |  |

| Dynamic Supply Current            | Idd3.3V           | -        | -        | 160     | mA       | note 4                                                      |  |  |  |  |

| Unloaded Supply Current           | Isdd              | -        | -        | 30      | mA       | Device running, OE at a logic low level (outputs disabled). |  |  |  |  |

| Input pin capacitance             | Cin               | -        | -        | 5       | pF       |                                                             |  |  |  |  |

| Pin inductance                    | Lpin              | -        | -        | 7       | nH       |                                                             |  |  |  |  |

| Crystal pin capacitance           | Cxtal             | 32       | 34       | 38      | pF       | from XIN and XOUT Pins to Ground.<br>note 5                 |  |  |  |  |

| Crystal DC Bias Voltage           | V <sub>BIAS</sub> | 0.3Vdd   | Vdd/2    | 0.7Vdd  | V        |                                                             |  |  |  |  |

| Crystal Startup time              | Txs               | -        | -        | 40      | μS       | From Stable 3.3V power supply.                              |  |  |  |  |

|                                   | VDD = A           | VDD = VD | DP = 3.3 | SV ±5%, | TA = 0°0 | C to +70⁰C                                                  |  |  |  |  |

Note1: Applicable to input signals: S0, S1, OE and SSCG#

Note2: Applicable to Sdata, and Sclk.

Note3: Although internal pull-up resistors have a typical value of 250K, this value may vary between 200K and 500K.

Note4: All outputs load in accordance with table 1.

Note5: Although the device will reliably interface with crystals of a  $17pF - 20pF C_{L}$  range, it is optimized to interface with a typical  $C_{L} = 18pF$  crystal specifications.

#### **AC Parameters**

| Symbol     | Deremeter                      | Output Frequency |         |      |         |      |        |      |        | Units | Notes   |

|------------|--------------------------------|------------------|---------|------|---------|------|--------|------|--------|-------|---------|

| Symbol     | Parameter                      | 133 N            | 133 MHz |      | 100 MHz |      | 66 MHz |      | 33 MHz |       | notes   |

|            |                                | Min              | Min Max |      | Max     | Min  | Max    | Min  | Max    |       |         |

| Тсус       | CLK(0:4) period                | 7.0              | 8.0     | 9.5  | 10.5    | 14.5 | 15.5   | 29.5 | 30.5   | ns    | 1, 2, 4 |

| THIGH      | CLK(0:4) period                | 3                | -       | 4    | -       | 6    | -      | 11   | -      | ns    | 2,6     |

| TLOW       | CLK(0:4) low time              | 3                | -       | 4    | -       | 6    | -      | 11   | -      | ns    | 2, 7    |

| Tr / Tf    | CLK(0:4) rise and fall times   | 0.50             | 1.33    | 0.50 | 1.33    | 0.50 | 1.33   | 0.50 | 1.33   | ns    | 2, 3    |

| TSKEW      | (Any CLK ) to (Any CLK)        | -                | 250     | -    | 250     | -    | 250    | -    | 250    | ps    | 2, 4,   |

|            | Skew time                      |                  |         |      |         |      |        |      |        |       | 5.9     |

| TCCJ       | CLK(0:4) Cycle to Cycle        | -                | 175     | -    | 175     | -    | 175    | -    | 175    | ps    | 2, 4, 5 |

|            | Jitter                         |                  |         |      |         |      |        |      |        |       |         |

| Tr / Tf    | REFOUT rise and fall times     | 1.0              | 4.0     | 1.0  | 4.0     | 1.0  | 4.0    | 1.0  | 4.0    | ns    | 2, 3    |

| TCCJ       | REFOUT Cycle to Cycle          |                  |         |      | 750     |      |        |      |        | pS    | 2, 4    |

|            | Jitter                         |                  |         |      | -       |      |        |      | -      |       |         |

| tpZL, tpZH | OE to clock enable delay (all  | -                | 10.0    | -    | 10.0    | -    | 10.0   | -    | 10.0   | ns    |         |

|            | outputs)                       |                  |         |      |         |      |        |      |        |       |         |

| tpLZ, tpHZ | OE to clock disable delay (all | -                | 10.0    | -    | 10.0    | -    | 10.0   | -    | 10.0   | ns    |         |

|            | outputs)                       |                  |         |      |         |      |        |      |        |       |         |

| tstable    | All clock Stabilization from   | -                | 3       | -    | 3       | -    | 3      | -    | 3      | ms    | 8       |

|            | power-up                       |                  |         |      |         |      |        |      |        |       |         |

Note 1: This parameter is measured as an average over 1uS duration, with an input frequency of 33.333 MHz

Note 2: All outputs loaded as per table 1 below.

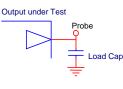

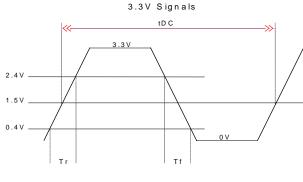

Note 3: Probes are placed on the pins, and measurements are acquired between 0.4V and 2.4V (see Fig.6A and Fig.6B)

Note 4: Probes are placed on the pins, and measurements are acquired at 1.5V. (See Figs.6A & 6B)

Note 5: This measurement is applicable with Spread ON or OFF.

Note 6: Probes are placed on the pins, and measurements are acquired at 2.4Vs, (see Figs. 6A & 6B)

Note 7: Probes are placed on the pins, and measurements are acquired at 0.4V.

Note 8: The time specified is measured from when all VDD's reach their respective supply rail (3.3V) till the frequency output is stable and operating within the specifications

Note 9: Applicable only to clocks within the same bank

| Output Name | Max Load (in pF) |

|-------------|------------------|

| CLK(0:4)    | 30               |

| REF         | 20               |

Table 1

### **Test and Measurement Setup**

Fig. 6A

Fig. 6B

### **Output Buffer Characteristics**

#### Buffer Characteristics for CLK(0:4), and REF

| Characteristic                                         | Symbol           | Min | Тур | Мах | Units | Conditions |  |

|--------------------------------------------------------|------------------|-----|-----|-----|-------|------------|--|

| Pull-Up Current                                        | IOH <sub>1</sub> | -33 | -   | -   | mA    | VDD-0.5    |  |

| Pull-Up Current IOH <sub>2</sub> -11 - mA 1.2V         |                  |     |     |     |       | 1.2V       |  |

| Pull-Down Current                                      | IOL <sub>1</sub> | 9.4 | -   | -   | mA    | 0.4V       |  |

| Pull-Down Current IOL <sub>2</sub> 22 - mA 1.2V        |                  |     |     |     |       |            |  |

| VDD = AVDD = VDDP = $3.3V \pm 5\%$ , TA = 0°C to +70°C |                  |     |     |     |       |            |  |

#### **Suggested Oscillator Crystal Parameters**

| Characteristic                       | Symbol           | Min   | Тур   | Max                 | Units | Conditions                                    |

|--------------------------------------|------------------|-------|-------|---------------------|-------|-----------------------------------------------|

| Frequency                            | Fo               | 33.00 | 33.33 | 33.5                | MHz   |                                               |

| Tolerance                            | Tc               | -     | -     | - +/-100 PPM Note 1 |       | Note 1                                        |

|                                      | Τs               | -     | -     | +/- 100             | PPM   | Stability (T <sub>A</sub> -10 to +60C) Note 1 |

|                                      | T <sub>A</sub>   | -     | -     | 5                   | PPM   | Aging (first year @ 25C) Note 1               |

| Operating Mode                       | -                | -     | -     | -                   |       | Parallel Resonant, Note 1                     |

| Load Capacitance                     | $C_{XTAL}$       | -     | 20    | -                   | pF    | The crystal's rated load. Note 1              |

| Effective Series<br>Resistance (ESR) | R <sub>ESR</sub> | -     | 40    | -                   | Ohms  | Note 2                                        |

Note1: For best performance and accurate frequencies from this device, It is recommended but not mandatory that the chosen crystal meets or exceeds these specifications

Note 2: Larger values may cause this device to exhibit oscillator startup problems

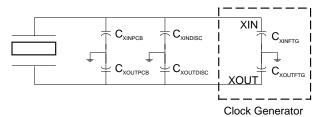

To obtain the maximum accuracy, the total circuit loading capacitance should be equal to  $C_{XTAL}$ . This loading capacitance is the effective capacitance across the crystal pins and includes the clock generating device pin capacitance ( $C_{FTG}$ ), any circuit traces ( $C_{PCB}$ ), and any onboard discrete load capacitors ( $C_{DISC}$ ).

# Suggested Oscillator Crystal Parameters (Cont.)

The following formula and schematic may be used to understand and calculate either the loading specification of a crystal for a design or the additional discrete load capacitance that must be used to provide the correct load to a known load rated crystal.

$C_{L} = \frac{(C_{XINPCB} + C_{XINFTG} + C_{XINDISC}) X (C_{XOUTPCB} + C_{XOUTFTG} + C_{XOUTDISC})}{(C_{XINPCB} + C_{XINFTG} + C_{XINDISC}) + (C_{XOUTPCB} + C_{XOUTFTG} + C_{OUTDISC})}$

Where:

$C_{XTAL}$  = the load rating of the crystal

$C_{XOUTFTG}$  = the clock generators XIN pin effective device internal capacitance to ground

C<sub>XOUTFTG</sub> = the clock generators XOUT pin effective device internal capacitance to ground

$C_{XINPCB}$  = the effective capacitance to ground of the crystal to device PCB trace

$C_{XOUTPCB}$  = the effective capacitance to ground of the crystal to device PCB trace

$C_{XINDISC}$  = any discrete capacitance that is placed between the XIN pin and ground

$C_{XOUTDISC}$  = any discrete capacitance that is placed between the XOUT pin and ground

As an example, and using this formula for this datasheet's device, a design that has no discrete loading capacitors ( $C_{DISC}$ ) and each of the crystal to device PCB traces has a capacitance ( $C_{PCB}$ ) to ground of 4pF (typical value) would calculate as:

$C_{L} = (\underline{4pF + 36pF + 0pF}) \times (\underline{4pF + 36pF + 0pF}) = \underline{40 \times 40} = \underline{1600} = 20pF$ (4pF + 36pF + 0pF) + (4pF + 36pF + 0pF) 40 + 40 80

Therefore to obtain output frequencies that are as close to this data sheets specified values as possible, in this design example, you should specify a parallel cut crystal that is designed to work into a load of 20pF.

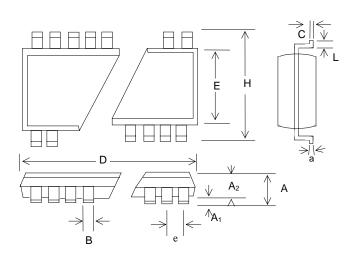

## **Package Drawing and Dimensions**

## 28 Pin TSSOP Outline Dimensions

|                |       | INCHES    |       |      | MILLIMETERS |      |  |

|----------------|-------|-----------|-------|------|-------------|------|--|

| SYMBOL         | MIN   | NOM       | MAX   | MIN  | NOM         | MAX  |  |

| A              | -     | -         | 0.047 | -    | -           | 1.20 |  |

| A <sub>1</sub> | 0.002 | -         | 0.006 | 0.05 | -           | 0.15 |  |

| A2             | 0.031 | 0.039     | 0.041 | 0.80 | 1.00        | 1.05 |  |

| В              | 0.007 | -         | 0.012 | 0.19 | -           | 0.30 |  |

| С              | 0.004 | -         | 0.008 | 0.09 | -           | 0.20 |  |

| D              | 0.378 | 0.382     | 0.386 | 9.60 | 9.70        | 9.80 |  |

| E              | 0.169 | 0.173     | 0.177 | 4.30 | 4.40        | 4.50 |  |

| е              |       | 0.026 BSC |       |      | 0.65 BSC    | ;    |  |

| Н              | 0.244 | 0.252     | 0.260 | 6.20 | 6.40        | 6.60 |  |

| L              | 0.018 | 0.024     | 0.030 | 0.45 | 0.60        | 0.75 |  |

| а              | 0°    | -         | 8°    | 0°   | -           | 8°   |  |

# **28 Pin SSOP Outline Dimensions**

|                |       | INCHES    |       | MILLIMETERS |          |       |

|----------------|-------|-----------|-------|-------------|----------|-------|

| SYMBOL         | MIN   | NOM       | MAX   | MIN         | NOM      | MAX   |

| А              | -     | -         | 0.079 | -           | -        | 2.0   |

| A <sub>1</sub> | 0.002 | -         | 0.006 | 0.05        | -        | 0.15  |

| A2             | 0.065 | 0.069     | 0.073 | 1.65        | 1.75     | 1.85  |

| В              | 0.009 | -         | 0.015 | 0.22        | -        | 0.38  |

| С              | 0.004 | -         | 0.010 | 0.09        | -        | 0.25  |

| D              | 0.390 | 0.402     | 0.413 | 9.90        | 10.20    | 10.50 |

| E              | 0.197 | 0.209     | 0.220 | 5.00        | 5.30     | 5.60  |

| е              |       | 0.026 BS0 | 2     |             | 0.65 BSC | ;     |

| Н              | 0.291 | 0.307     | 0.323 | 7.40        | 7.80     | 8.20  |

| L              | 0.022 | 0.030     | 0.037 | 0.55        | 0.75     | 0.95  |

| а              | 0°    | -         | 8°    | 0°          | -        | 8°    |

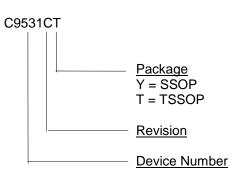

#### **Ordering Information**

| Part Number | Package Type | Production Flow          |

|-------------|--------------|--------------------------|

| C9531CY     | 28 Pin SSOP  | Commercial, 0°C to +70°C |

| C9531CT     | 28 Pin TSSOP | Commercial, 0°C to +70°C |

<u>Note</u>: The ordering part number is formed by a combination of device number, device revision, package style, and screening as shown below.

Marking: Example: Cypress C9531 Date Code, Lot #

#### Notice

Cypress Semiconductor Corporation reserves the right to make changes to its products in order to improve design, performance or reliability. Cypress Semiconductor Corporation assumes no responsibility for the use of its products in life supporting and medical applications where the failure or malfunction of the product could cause failure of the life supporting and medical systems. Products are not authorized for use in such applications unless a written approval is requested by the manufacturer and an approval is given in writing by Cypress Semiconductor Corporation for the use of its products in the life supporting and medical applications.

|      | Document Title: C9531 PCIX I/O System Clock Generator with EMI Control Features<br>Document Number: 38-07034 |               |                                       |                             |  |  |  |

|------|--------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------|-----------------------------|--|--|--|

| Rev. | ECN<br>No.                                                                                                   | Issue<br>Date | Orig. of Description of Change Change |                             |  |  |  |

| **   | 106962                                                                                                       | 06/12/01      | IKA                                   | Convert from IMI to Cypress |  |  |  |