# CALINOS"

# CA80C85B

# HIGH PERFORMANCE 8-BIT CMOS MICROPROCESSOR

- Enhanced, high performance CA80C85B microprocessor features pin and functional compatibility with industry standard 8085 and 8085A

- Very low power consumption achieved with proven CMOS implementation

- TTL compatible input/output voltages

- Fast Available in 6 MHz, 5 MHz and 3 MHz speed versions

- Full support of extended instruction set, and standard 8080 and 8085/8085A instruction sets

- Runs over 10,000 CP/M® programs

- On-chip clock generator (using external crystal, LC or RC network)

- · Direct addressing to 64K bytes

- · Four Interrupt inputs (one non-maskable)

- One of the multi-sourced, Calmos<sup>™</sup> 8000 series products

The CA80C85B is an 8-bit microprocessor having complete pin and functional compatibility with industry standard 8085s and 8085s. In addition, it supports the special 8085 extended instruction set. The CA80C85B includes an on-board system controller, clock generator, serial I/O port and direct addressing capability to 64K bytes of memory. The device also utilizes a multiplexed data bus, with 16-bit addresses split between an 8-bit address bus and an 8-bit data bus.

The CA80C85B is manufactured in CMOS and supplied in PDIP and PLCC package configurations suitable for commercial industrial and military applications.

The CA80C85B provides the systems designer with single component CPU functionality, thereby reducing the parts count. Its low power consumption and TTL VO compatibility make the CA80C85B particularly well suited to portable or standby type applications.

The CA80C85B is also available as a macrocell building block for custom circuit/Complex Array Logic design. Thus it can be used in conjunction with existing industry standard 8000 peripheral devices, or incorporated into original IC designs for even lower overall system costs.

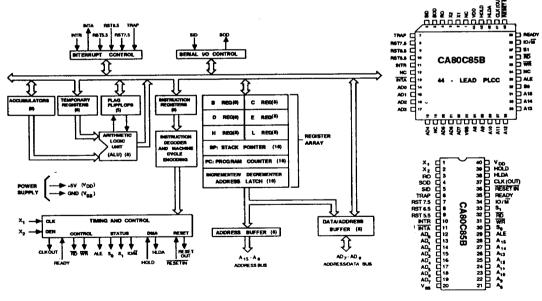

Figure 1: CA80C85B BLOCK DIAGRAM

Figure 2: PDIP and PLCC PIN CONFIGURATIONS

Document: 808085.MD500.01

Table 1: PIN DESCRIPTIONS

| Symbol                                    | ol Pins            |               | Туре | Name and Function                                                                                                                                                                                                                                                                                                         |  |

|-------------------------------------------|--------------------|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                           | PLCC               | PDIP          | 1    |                                                                                                                                                                                                                                                                                                                           |  |

| A <sub>8</sub> - A <sub>15</sub>          | 24-31              | 21 - 28       | 0    | High Address Bus: the most significant 8 bits of the memory address.                                                                                                                                                                                                                                                      |  |

| AD <sub>0</sub> - AD <sub>7</sub>         | 14 - 18<br>20 - 22 | 12-19         | Ю    | Low Address and Data Bus: the least significant 8 bits of the memory address multiplexed wi<br>an 8-bit data bus.                                                                                                                                                                                                         |  |

| ALE                                       | 33                 | 30            | 0    | Address Latch Enable Out: This signal occurs during the first clock state of a machine cycle. The falling edge of the ALE may be used to strobe the status information.                                                                                                                                                   |  |

| CLK                                       | 41                 | 37            | 0    | Clock: This signal can be used as a system clock. The period of CLK is twice the period of the 3 input.                                                                                                                                                                                                                   |  |

| HLDA                                      | 42                 | 38            | 0    | Hold Acknowledge: indicates that the CPU has received the HOLD request and that the bus will be relinquished in the next clock cycle.                                                                                                                                                                                     |  |

| HOLD                                      | 43                 | 39            | 1    | Hold Request: is used to indicate that another master is requesting the use of the address and dat buses. When HOLD is acknowledged (HLDA), the Address, Data, RD, WR and IOM lines are set to the high impedance state. Note that the CPU can regain control of the bus only after the HOLD is removed.                  |  |

| INTA                                      | 13                 | 11            | 0    | Interrupt Acknowledge: This active low signal indicates that the interrupt request input (INTR) habeen recognized and acknowledged.                                                                                                                                                                                       |  |

| INTR                                      | 11                 | 10            | ı    | Interrupt Request: This is a general purpose interrupt. When INTR goes HIGH, it will inhibit the Program Counter, generate an interrupt acknowledge (INTA) signal, and sample the data bus for RESTART or CALL instruction.                                                                                               |  |

| Ю/ <b>М</b>                               | 38                 | 34            | 0    | Machine Cycle Status: see S <sub>0</sub> and S <sub>1</sub> status bits for further details.                                                                                                                                                                                                                              |  |

| RD                                        | 36                 | 32            | 0    | Read Control: Active low signal is used to indicate that selected memory or I/O device is to with the data bus available for the data transfer. RD is set to a high impedance state during HALT and RESET modes.                                                                                                          |  |

| READY                                     | 39                 | 35            | 1    | Ready: This signal is set to HIGH during read or write cycles to indicate that the selected memory of VO device is ready to send or receive data.                                                                                                                                                                         |  |

| RESET IN                                  | 40                 | 36            | . I  | Reset In: Active low signal sets the Program Counter to zero, and resets the interrupt enable (INTE and HLDA flipflop. Note that so long as RESET IN is held low, the CPU is held in a reset condition.                                                                                                                   |  |

| RO                                        | 4                  | 3             | 0    | Reset Out: indicates that the CPU is being reset. This signal can be used as a system RESET.                                                                                                                                                                                                                              |  |

| RST7.5<br>RST6.5<br>RST5.5                | 8, 9, 10           | 7, 8, 9       | ı    | Restart Interrupts: These inputs provide three maskable interrupts which invoke an automati-<br>internal restart. RST7.5 is the highest relative priority, followed by RST6.5 and RST5.5. All three interrupts have a higher priority than INTR.                                                                          |  |

| S <sub>0</sub> , S <sub>1</sub> ,<br>IO/M | 32, 37,<br>38      | 29, 33,<br>34 | 0    | Status Outputs: These signals provide an indication of the machine status during any given cycle<br>All become valid at the beginning of a machine cycle, and remain stable for the duration of that cycle<br>The status may be latched by the falling edge of the ALE signal.                                            |  |

| SID                                       | 6                  | 5             | ı    | Serial Input Data: Data on SID is loaded into accumulator bit 7 when a RIM instruction is executed.                                                                                                                                                                                                                       |  |

| SOD                                       | 5                  | 4             | 0    | Serial Output Data: This signal is set or reset by the SIM instruction.                                                                                                                                                                                                                                                   |  |

| TRAP                                      | 7                  | 6             | 1    | Trap Interrupt: is a non-maskable restart interrupt. It is the highest priority interrupt, and is unaffected by an interrupt enable (INTE).                                                                                                                                                                               |  |

| V <sub>DD</sub>                           | 44                 | 40            |      | Power: +5 V Supply.                                                                                                                                                                                                                                                                                                       |  |

| v <sub>ss</sub>                           | 23                 | 1             | -    | Ground: Ground reference.                                                                                                                                                                                                                                                                                                 |  |

| WR                                        | 35                 | 31            |      | Write Control: This active low signal is used to indicate that selected memory or I/O device is to be written to, with the data bus available for the data transfer. WR is set to a high impedance state during HOLD, HALT and RESET modes.                                                                               |  |

| x <sub>1</sub> , x <sub>2</sub>           | 2,3                | 1,2           |      | $X_1$ , $X_2$ : These two inputs are connected to clock source which is used to drive the internal clock generator. The clock source may be a crystal, LC or RC network. An external clock can also be connected directly to $X_1$ , to produce an internal processor clock frequency of one half of the input frequency. |  |

#### FUNCTIONAL DESIGN

The CA80C85B utilizes a stack architecture to enable any part of the external memory to be employed as a Last In/First Out (LIFO) memory stack. A 16-bit stack pointer controls the addressing of this stack. The arrangement allows extensive subroutine nesting and multiple level interrupts to be handled without losing the system status. In addition, the device accepts serial input data and provides serial output data, functions which are controlled by the interrupt mask instructions.

The CA80C85B provides 16-bit arithmetic operation with immediate operators and decimal capability. An 8-bit accumulator, four user accessible flag bits, an 8-bit parallel binary arithmetic unit and six 8-bit data registers, all shown in the block diagram of Figure 1, are also provided. CA80C85B timing signals are supplied by an internal clock generator (which can be used with either crystal or RC timing circuits), or by an external clock input signal. Status outputs convey memory I/O instruction and Read/Write timing indications.

For typical, single function type configurations, the CA80C85B is supplied in a 40-pin package, the low pin count a result of multiplexing the Address and Data Bus lines. Pin functions are described in Table 1, with the 40-pin DIP pin configuration illustrated in Figure 2. The lower processor pin count of this device can be reflected throughout a system design by similar pin count reductions in peripheral chips. Further, this optimization can be achieved without incurring complex or critical timing problems.

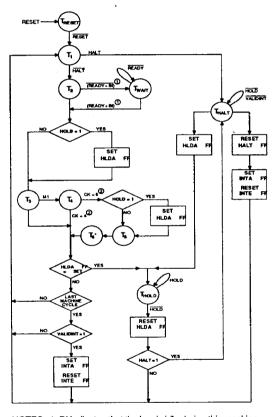

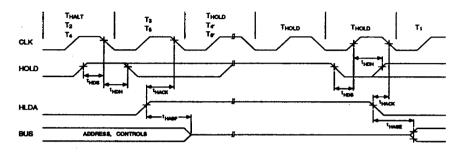

The CA80C85B has five levels of interrupts, including three maskable restart interrupts, one non-maskable TRAP interrupt and a bus vectored interrupt, INTR. Bus control is provided by the  $\overline{\text{ND}}$ ,  $\overline{\text{WR}}$ ,  $S_0$ ,  $S_1$ ,  $IO/\overline{\text{M}}$  and INTA interrupt acknowledge signals. When a HOLD control input signal is received, both Address and Data Bus are set to a high-impedance state, and an HLDA output signal acknowledges that microprocessor operation is stopped, and that the buses are available for use by other devices. Note that HOLD and all other interrupt signals are synchronized with the processor's internal clock. This is illustrated in the processor state transition diagram of Figure 3.

In addition to the Data Bus, a simple serial interface is provided by the Serial Input Data (SID) and Serial Output Data (SOD) lines.

At the software level, the CA80C85B supports the full extended instruction set, offering 10 additional instructions for the production of more efficient code. The five existing condition code flags have also been enhanced with two additional flag bits, one of which indicates a 2s complement overflow.

NOTES: 1. BI indicates that the bus is idle during this machine cycle, though the processor itself is active

CK indicates the number of clock cycles in this machine cycle

Figure 3: STATE TRANSITION DIAGRAM

Table 2: 3 MHz AC CHARACTERISTICS

$T_A = -40^{\circ} \text{ to } +85^{\circ}\text{C}, \ V_{DD} = +5\text{v} \pm 10\%, \ t_{CYC} = 320 \text{ ns, } C_L = 150 \text{ pF}$

| Complete 1        | Danamatan                                                          | Lim      | Units |       |  |

|-------------------|--------------------------------------------------------------------|----------|-------|-------|--|

| Symbol            | Parameter                                                          | Min      | Max   | Units |  |

| t <sub>1</sub>    | CLK Low Time                                                       | 80       | -     | ns    |  |

| t <sub>2</sub>    | CLK High Time                                                      | 120      | -     | ns    |  |

| tAC               | A <sub>8</sub> - A <sub>15</sub> Valid to Leading Edge of Control  | 270      | -     | ns    |  |

| †ACL              | A <sub>0</sub> - A <sub>7</sub> Valid to Leading Edge of Control   | 240      | -     | ns    |  |

| t <sub>AD</sub>   | A <sub>0</sub> - A <sub>15</sub> Valid to Valid Data In            | -        | 575   | ns    |  |

| tAFR              | Address Float After Leading Edge of RD, INTA                       | -        | 0     | ns    |  |

| t <sub>AL</sub>   | A <sub>8</sub> - A <sub>15</sub> Valid Before Trailing Edge of ALE | 115      | -     | ns    |  |

| †ALL              | A <sub>0</sub> - A <sub>7</sub> Valid Before Trailing Edge of ALE  | 90       | -     | ns    |  |

| t <sub>ARY</sub>  | READY Valid from Address Valid                                     | -        | 220   | ns    |  |

| <sup>t</sup> CA   | Address (A <sub>8</sub> - A <sub>15</sub> ) Valid After Control    | 120      | -     | ns    |  |

| tcc               | Width of Control Low (RD, WR, INTA)                                | 400      |       | ns    |  |

| t <sub>CL</sub>   | Trailing Edge of Control to Leading Edge of ALE                    | 50       | -     | ns    |  |

| tcyc              | CLK Cycle Period                                                   | 320      | 2000  | ns    |  |

| tow               | Data Valid to Trailing Edge of WR                                  | 420      | -     | ns    |  |

| te                | CLK Fall Time                                                      | -        | 30    | ns    |  |

| t <sub>HABE</sub> | HLDA to Bus Enable                                                 | <b>-</b> | 210   | ns    |  |

| tHABE             | Bus Float After HLDA                                               | -        | 210   | ns    |  |

| THACK             | HLDA Valid to Trailing Edge of CLK                                 | 110      |       | ns    |  |

| tHDH              | HOLD Hold Time                                                     | 0        | -     | ns    |  |

| tHDS              | HOLD Setup Time to Trailing Edge of CLK                            | 170      | -     | ns    |  |

| t <sub>INH</sub>  | INTR Hold Time                                                     | 0        | -     | ns    |  |

| tins              | INTR RST and TRAP Setup Time to Falling Edge of CLK                | 160      |       | ns    |  |

| t <sub>LA</sub>   | Address Hold Time After ALE                                        | 100      |       | ns    |  |

| tLC               | Trailing Edge of ALE to Leading Edge of Control                    | 130      | -     | ns    |  |

| t <sub>LCK</sub>  | ALE Low During CLK High                                            | 100      | -     | ns    |  |

| t <sub>LDR</sub>  | ALE to Valid Data During Read                                      | -        | 460   | ns    |  |

| tLDW              | ALE to Valid Data During Write                                     | -        | 200   | ns    |  |

| tLL               | ALE Width                                                          | 140      |       | ns    |  |

| tLRY              | ALE to Ready Stable                                                | -        | 110   | ns    |  |

| t <sub>r</sub>    | CLK Rise Time                                                      | -        | 30    | ns    |  |

| †RAE              | Trailing Edge of RD to re-Enabling of Address                      | 150      |       | ns    |  |

| t <sub>RD</sub>   | RD (or INTA) to Valid Data                                         | -        | - 300 | ns    |  |

| <sup>t</sup> RDH  | Data Hold Time After RD, INTA                                      | 0        |       | ns    |  |

| t <sub>RV</sub>   | Control Trailing Edge to Leading Edge of Next Control              | 400      |       | ns    |  |

| <sup>t</sup> RYH  | READY Hold Time                                                    | 0        |       | ns    |  |

| tRYS              | READY Setup Time to Leading Edge of CLK                            | 110      |       | ns    |  |

| two               | Data Valid After Trailing Edge of WR                               | 100      | _     | ns    |  |

| twoL              | Leading Edge of WR to Data Valid                                   | -        | 40    | ns    |  |

| TXKF              | X <sub>1</sub> Rising to CLK Falling                               | 20       | 150   | ns    |  |

| txkR              | X <sub>1</sub> Rising to CLK Rising                                | 20       | 120   | ns    |  |

Q

#### Table 3: 5 MHz AC CHARACTERISTICS

$T_A = -40^{\circ}$  to +85°C,  $V_{DD} = +5v \pm 10\%$ ,  $t_{CYC} = 200$  ns,  $C_L = 150$  pF

|                  |                                                                    | Limi | 11   |       |  |

|------------------|--------------------------------------------------------------------|------|------|-------|--|

| Symbol           | Parameter                                                          | Min  | Max  | Units |  |

| t <sub>1</sub>   | CLK Low Time                                                       | 40   |      | ns    |  |

| t <sub>2</sub>   | CLK High Time                                                      | 70   | -    | ns    |  |

| tAC              | A <sub>8</sub> - A <sub>15</sub> Valid to Leading Edge of Control  | 115  |      | ns    |  |

| †ACL             | A <sub>0</sub> - A <sub>7</sub> Valid to Leading Edge of Control   | 115  | •    | ns    |  |

| t <sub>AD</sub>  | A <sub>0</sub> - A <sub>15</sub> Valid to Valid Data In            | -    | 330  | ns    |  |

| t <sub>AFR</sub> | Address Float After Leading Edge of RD, INTA                       | -    | 0    | ns    |  |

| t <sub>AL</sub>  | A <sub>8</sub> - A <sub>15</sub> Valid Before Trailing Edge of ALE | 50   |      | ns    |  |

| t <sub>ALL</sub> | A <sub>0</sub> - A <sub>7</sub> Valid Before Trailing Edge of ALE  | 50   |      | ns    |  |

| tARY             | READY Valid from Address Valid                                     | -    | 100  | ns    |  |

| <sup>t</sup> CA  | Address (A <sub>B</sub> - A <sub>15</sub> ) Valid After Control    | 60   | -    | ns    |  |

| tcc              | Width of Control Low (RD, WR, INTA)                                | 230  | -    | ns    |  |

| t <sub>CL</sub>  | Trailing Edge of Control to Leading Edge of ALE                    | 25   | -    | ns    |  |

| tcyc             | CLK Cycle Period                                                   | 200  | 2000 | ns    |  |

| tow              | Data Valid to Trailing Edge of WR                                  | 230  | -    | ns    |  |

| t <sub>f</sub>   | CLK Fall Time                                                      | -    | 30   | ns    |  |

| †HABE            | HLDA to Bus Enable                                                 | •    | 150  | ns    |  |

| †HABF            | Bus Float After HLDA                                               | •    | 150  | ns    |  |

| tHACK            | HLDA Valid to Trailing Edge of CLK                                 | 40   | -    | ns    |  |

| tHDH             | HOLD Hold Time                                                     | 0    | •    | ns    |  |

| tHDS             | HOLD Setup Time to Trailing Edge of CLK                            | 120  | -    | ns    |  |

| tINH             | INTR Hold Time                                                     | 0    | -    | ns    |  |

| tins             | INTR RST and TRAP Setup Time to Falling Edge of CLK                | 150  |      | ns    |  |

| ЦA               | Address Hold Time After ALE                                        | 50   | T -  | ns    |  |

| tLC              | Trailing Edge of ALE to Leading Edge of Control                    | 60   | -    | ns    |  |

| tLCK             | ALE Low During CLK High                                            | 50   | -    | ns    |  |

| t <sub>LDR</sub> | ALE to Valid Data During Read                                      | -    | 250  | ns    |  |

| t <sub>LDW</sub> | ALE to Valid Data During Write                                     | -    | 140  | ns    |  |

| t <sub>LL</sub>  | ALE Width                                                          | 80   | -    | ns    |  |

| tLRY             | ALE to Ready Stable                                                | -    | 30   | ns    |  |

| <u> </u>         | CLK Rise Time                                                      | -    | 30   | ns    |  |

| t <sub>RAE</sub> | Trailing Edge of RD to Re-enabling of Address                      | 85   | -    | ns    |  |

| t <sub>RD</sub>  | RD (or INTA) to Valid Data                                         | -    | 150  | ns    |  |

| <sup>t</sup> RDH | Data Hold Time After RD, INTA                                      | 0    | -    | ns    |  |

| tev              | Control Trailing Edge to Leading Edge of Next Control              | 220  | -    | ns    |  |

| <sup>t</sup> RYH | READY Hold Time                                                    | 0    | -    | ns    |  |

| t <sub>RYS</sub> | READY Setup Time to Leading Edge of CLK                            | 100  | -    | ns    |  |

| two              | Data Valid After Trailing Edge of WR                               | 60   | -    | ns    |  |

| twoL             | Leading Edge of WR to Data Valid                                   | -    | 20   | ns    |  |

| txkF             | X <sub>1</sub> Rising to CLK Falling                               | 20   | 110  | ns    |  |

| txka             | X <sub>1</sub> Rising to CLK Rising                                | 20   | 100  | ns    |  |

Table 4: 6 MHz AC CHARACTERISTICS

$T_A = -40^{\circ}$  to +85°C,  $V_{DD} = +5v \pm 5\%$ ,  $t_{CYC} = 167$  ns,  $C_L = 150$  pF

| Symbol                      | Parameter                                                          | Lim            |      |       |  |

|-----------------------------|--------------------------------------------------------------------|----------------|------|-------|--|

| Syllibol                    | Parameter                                                          | Min            | Max  | Units |  |

| t <sub>1</sub> CLK Low Time |                                                                    | 34             | -    | ns    |  |

| t <sub>2</sub>              | CLK High Time                                                      | 59             | -    | ns    |  |

| <sup>t</sup> AC             | A <sub>8</sub> - A <sub>15</sub> Valid to Leading Edge of Control  | 96             | -    | ns    |  |

| t <sub>ACL</sub>            | A <sub>0</sub> - A <sub>7</sub> Valid to Leading Edge of Control   | 96             | -    | ns    |  |

| <sup>t</sup> AD             | A <sub>0</sub> - A <sub>15</sub> Valid to Valid Data In            | -              | 292  | ns    |  |

| †AFR                        | Address Float After Leading Edge of RD, INTA                       | -              | 0    | ns    |  |

| t <sub>AL</sub>             | A <sub>8</sub> - A <sub>15</sub> Valid Before Trailing Edge of ALE | 42             | -    | ns    |  |

| †ALL                        | A <sub>0</sub> - A <sub>7</sub> Valid Before Trailing Edge of ALE  | 42             | -    | ns    |  |

| t <sub>ARY</sub>            | READY Valid from Address Valid                                     | -              | 83   | ns    |  |

| <sup>t</sup> CA             | Address (A <sub>8</sub> - A <sub>15</sub> ) Valid After Control    | 50             |      | ns    |  |

| tcc                         | Width of Control Low (RD, WR, INTA)                                | 192            | -    | ns    |  |

| <sup>t</sup> CL             | Trailing Edge of Control to Leading Edge of ALE                    | 20             |      | ns    |  |

| tcyc                        | CLK Cycle Period                                                   | 167            | 2000 | ns    |  |

| t <sub>DW</sub>             | Data Valid to Trailing Edge of WR                                  | 192            | -    | ns    |  |

| ¥                           | CLK Fall Time                                                      | -              | 25   | ns    |  |

| †HABE                       | HLDA to Bus Enable                                                 | -              | 125  | ns    |  |

| 1HABF                       | Bus Float After HLDA                                               |                | 125  | ns    |  |

| †HACK                       | HLDA Valid to Trailing Edge of CLK                                 | 33             |      | ns    |  |

| tHDH                        | HOLD Hold Time                                                     | 0              | -    | ns    |  |

| tHDS                        | HOLD Setup Time to Trailing Edge of CLK                            | 100            | -    | ns    |  |

| t <sub>INH</sub>            | INTR Hold Time                                                     | 0              |      | ns    |  |

| tins                        | INTR RST and TRAP Setup Time to Falling Edge of CLK                | 125            | -    | ns    |  |

| t <sub>LA</sub>             | Address Hold Time After ALE                                        | 42             | -    | ns    |  |

| ЦC                          | Trailing Edge of ALE to Leading Edge of Control                    | 50             |      | ns    |  |

| tLCK                        | ALE Low During CLK High                                            | 42             | -    | ns    |  |

| tLDR                        | ALE to Valid Data During Read                                      | -              | 225  | ns    |  |

| tLDW                        | ALE to Valid Data During Write                                     | <b>—</b> •     | 100  | ns    |  |

| t <sub>LL</sub>             | ALE Width                                                          | 67             |      | ns    |  |

| tLRY                        | ALE to Ready Stable                                                | •              | 25   | กร    |  |

| Ļ                           | CLK Rise Time                                                      | -              | 25   | ns    |  |

| <sup>t</sup> RAE            | Trailing Edge of RD to Re-enabling of Address                      | 65             | -    | ns    |  |

| t <sub>RD</sub>             | RD (or INTA) to Valid Data                                         | -              | 125  | ns    |  |

| <sup>t</sup> RDH            | Data Hold Time After RD, INTA                                      | 0              | -    | ns    |  |

| t <sub>RV</sub>             | Control Trailing Edge to Leading Edge of Next Control              | 183            | -    | ns    |  |

| <sup>t</sup> RYH            | READY Hold Time                                                    | 0              | -    | ns    |  |

| tRYS                        | READY Setup Time to Leading Edge of CLK                            | 84             | -    | ns    |  |

| t <sub>WD</sub>             | Data Valid After Trailing Edge of WR                               | 50             | -    | ns    |  |

| <sup>†</sup> WDL            | Leading Edge of WR to Data Valid                                   | <del>  -</del> | 16   | ns    |  |

| †XKF                        | X <sub>1</sub> Rising to CLK Falling                               | 20             | 110  | ns    |  |

| txkB                        | X <sub>1</sub> Rising to CLK Rising                                | 20             | 100  | ns    |  |

С

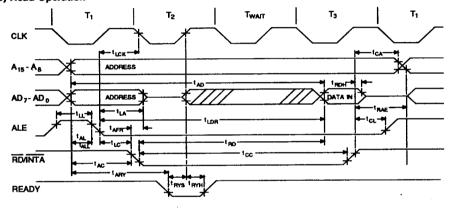

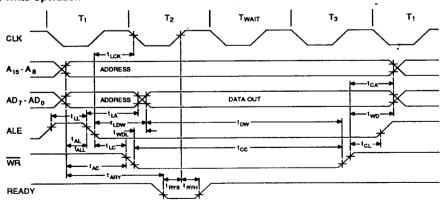

Figure 4: TIMING DIAGRAMS

# b) Read Operation

## c) Write Operation

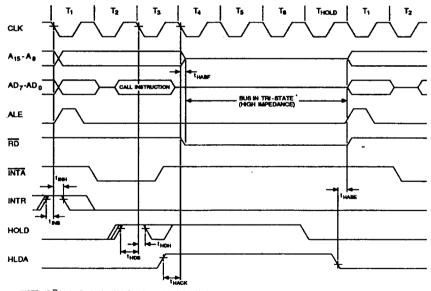

Figure 4: TIMING DIAGRAMS con't

# d) Hold Operation

# e) Interrupt Timing

С

Table 5 : DC CHARACTERISTICS (Commercial and Industrial Temperature Range Devices)  $T_A = -40^\circ$  to +85°C,  $V_{DD} = +50 \pm 10\%$ ,  $t_{CYC} = 320$  ns (except as noted)

|                  |                         |                                                    | Limits |                      |       |  |

|------------------|-------------------------|----------------------------------------------------|--------|----------------------|-------|--|

| Symbol           | Parameter               | Test Conditions                                    | Min    | Max                  | Units |  |

| I <sub>DD1</sub> | Power Supply Current    | t <sub>CYC</sub> = 320 ns, T <sub>A</sub> = -40 °C |        | 24                   | mA    |  |

|                  |                         | t <sub>CYC</sub> = 320 ns, T <sub>A</sub> = +25 °C |        | 17                   | mA    |  |

| I <sub>DD2</sub> | Power Supply Current    | t <sub>CYC</sub> = 200 ns, T <sub>A</sub> = -40 °C |        | 29                   | mA    |  |

|                  |                         | t <sub>CYC</sub> = 200 ns, T <sub>A</sub> = +25 °C |        | 21                   | mA    |  |

| I <sub>1</sub> L | Input Leakage Current   | VIN=VDD and VIN=0                                  |        | 10                   | μΑ    |  |

| lor.             | Output Leakage Current  | 0v≤V <sub>OUT</sub> ≤V <sub>DD</sub>               |        | 10                   | μА    |  |

| V <sub>HY</sub>  | Hysteresis, RESET       |                                                    | 0.25   |                      | V     |  |

| VIH              | Input High Voltage      |                                                    | 2.2    | V <sub>DD</sub> +0.3 | ٧     |  |

| VIHR             | Input High Level, RESET |                                                    | 2.4    | V <sub>DD</sub> +0.3 | ٧     |  |

| VIL              | Input Low Voltage       |                                                    | -0.3   | +0.8                 | V     |  |

| VILR             | Input Low Level, RESET  |                                                    | -0.3   | +0.8                 | V     |  |

| Vol              | Output Low Voltage      | i <sub>OL</sub> =2 mA                              |        | 0.45                 | ٧     |  |

| Voн              | Output High Voltage     | l <sub>OH</sub> = -400 μA                          | 2.4    |                      | V     |  |

|                  |                         | l <sub>OH</sub> = -40 μA                           | 4.2    |                      | V     |  |

Table 6: ABSOLUTE MAXIMUM RATINGS

| Storage Temperature                         | -65°C to +160°C                    |  |

|---------------------------------------------|------------------------------------|--|

| All Input Voltages                          | -1.0 to +5.5 Volts                 |  |

| All Output or Supply Voltages               | -0.5 to +7 Volts                   |  |

| Voltage On Any Pin with respect to Ground   | -0.3 to V <sub>DD</sub> +0.3 Volts |  |

| Output Currents                             | 100mA                              |  |

| Power Dissipation                           | 1 Watt                             |  |

| Lead Temperature<br>(Soldering: 10 seconds) | 300℃                               |  |

Stresses beyond those listed above may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Clock Inputs**

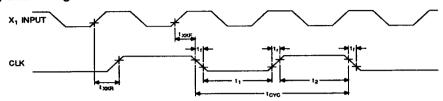

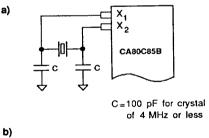

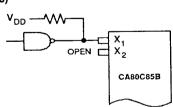

Clock inputs to the CA80C85B are supplied via the two inputs  $X_1$  and  $X_2$ . The  $X_1$  input can be driven either from an external clock, or used with the  $X_2$  input and a crystal to produce an oscillator function. The minimum input frequency required in both cases is 1 MHz. The actual internal microprocessor clock frequency is one half of the frequency applied or generated externally. For example, a 6 MHz crystal or external clock waveform is required for 3 MHz operation, and a 12 MHz clock source is required for 6 MHz operation.

The  $\rm X_1/X_2$  circuitry is intended to be used with a crystal cut for parallel resonance at the required clock frequency. Such crystals require closely controlled load capacitance in order to resonate at the specified frequency. The CA80C85B has an equivalent parallel capacitance of between 10 and 20 pF. Since most crystals will require higher values of capacitance to resonate at precisely their specified frequency, additional capacitance must be added as shown in Figure 5(a).

When the  $X_1$  input is driven from an external clock,  $X_2$  is left open. In this case,  $X_1$  should be driven with a CMOS driver or a TTL device with a pull-up resistor, as shown in Figure 5(b). The clock low time must be greater than 80 ns for the 3 MHz device and 30 ns for the 6 MHz.

Figure 5: EXTERNAL CLOCK CIRCUITS

#### Serial I/O

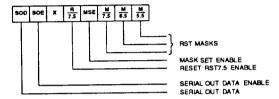

The Set Interrupt Mask (SIM) and Read Interrupt Mask (RIM) instructions provide several functions related to serial port I/O and interrupt mask operations. The SIM instruction is used to output serial data, and to program the interrupt mask register. The output signal, SOD, is set or reset as specified by the SIM instruction, with the accumulator contents constructed as shown in Figure 6.

Figure 6: SIM INSTRUCTION DATA BYTE

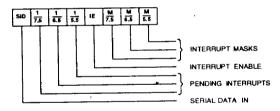

The RIM instruction is used to read the serial input data (SID), as well as the interrupt mask. The accumulator contents after a RIM instruction has been executed are as shown in Figure 7.

Figure 7: RIM INSTRUCTION DATA BYTE

#### Interrupts

The five interrupt levels provided by the CA80C85B are listed by descending order of priority in Table 7. TRAP and RSTx.5 are RESTART interrupts. When acknowledged, these four interrupts cause the processor to save the program counter (PC) on the stack, then branch to the restart address specified in the table.

The TRAP interrupt is non-maskable. It is set with a rising edge (low to high) followed by a stable high level until sampled by the processor. To reactivate the TRAP interrupt, the input signal must first go low, then high.

To preserve the status of the Interrupt Enable (IE) flag after a TRAP interrupt has occurred, the interrupt mask must be read and saved immediately after the interrupt has been acknowledged (refer to RIM instruction).

The RST7.5 is a maskable interrupt, set on a rising edge only, and then latched.

The RST6.5 and RST5.5 are maskable interrupts, set with a high level applied to their respective inputs. The status of the three RST interrupt masks can only be affected by the SIM instruction and RESET IN.

The INTR interrupt is also set by a high level applied to the input pin. It is similar in operation to the 8080 *INT* interrupt in that the action of the processor is dependent on the instruction placed on the bus during the INTA.

Note that the servicing of any of the five interrupts disables all future interrupts (except TRAPS) until an El instruction is executed. Of course, an interrupt of higher priority may interrupt a previous interrupt in process if the interrupts have been re-enabled within the interrupt service routine.

Table 7: INTERRUPT RESTART ADDRESSES

| Interrupt | Restart Address (HEX)                                             |

|-----------|-------------------------------------------------------------------|

| TRAP      | 24H                                                               |

| RST7.5    | зсн                                                               |

| RST6.5    | 34H                                                               |

| RST5.5    | 2CH                                                               |

| INTR      | Dependent upon the instruction received on the bus during an INTA |

#### **Status Outputs**

The status of the CA80C85B can be determined from the combination of  $S_0,\ S_1$  and  $IO/\overline{M}$  output signals. These signals are latched on the falling edge of an ALE signal, and are valid while ALE is low. Table 8 lists the seven possible types of machine cycles as defined by  $S_0,\ S_1$  and  $IO/\overline{M}$ . Note in the Figure 4 timing diagrams that the  $\overline{RD}$  and  $\overline{WR}$  control lines become active after the status signals, when the transfer of data is to take place.

Table 8: MACHINE CYCLE STATUS

CONDITIONS

| S <sub>0</sub> | S <sub>1</sub> | IO/M | Status                |

|----------------|----------------|------|-----------------------|

| 1              | 0              | 0    | Memory Write          |

| 0              | 1              | 0    | Memory Read           |

| 1              | 0              | 1    | I/O Write             |

| 0              | 1              | 1    | I/O Read              |

| 1              | 1              | 0    | Opcode Fetch          |

| 1              | 1              | 1    | Opcode Fetch          |

| 1              | 1              | 1    | Interrupt Acknowledge |

| Z              | 0              | 0    | Halt                  |

| Z              | X              | Х    | Hold                  |

| Z              | Х              | Х    | Reset                 |

Z - High impedance state

X - Don't care condition

## **Extended Instructions and Condition Codes**

The CA80C85B Flag Register features two additional condition code flags, for a total of seven. These are illustrated in Figure 8. The ten op codes which comprise the extended instruction set of the CA80C85B microprocessor are described in Table 9.

| s | z | UI | AC | 0 | Р | ν | С | FLAG |

|---|---|----|----|---|---|---|---|------|

| 7 | 6 | 5  | 4  | 3 | 2 | 1 | 0 | BIT  |

V - 2's complement overflow for both 8 and 16-bit arithmetic operations

UI - Underflow indicator (DCX instruction) or Overflow indicator (INX instruction)

UI = 01.02 + 01.R + 02.R, where:

01 - sign of operand 1

02 - sign of operand 2

R - sign of result

For subtraction and comparisons, replace 02 with  $\overline{02}$ .

Figure 8: EXTENDED CONDITION CODES

g

Table 9: CA80C85B EXTENDED INSTRUCTION SET

| Name | Opcodes                                                                                | Flags                     | Cycles | States  | Description                                                                                                                                                                                                                                                                                                                                                                                |

|------|----------------------------------------------------------------------------------------|---------------------------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARHL | 0 0 0 1 0 0 0 0  Addressing: Register                                                  | CY                        | 2      | 7       | Arithmetic Shift of H and L to the Right: The contents of registers H and L are shifted right one bit. The high-order bit is duplicated while the low-order bit is shifted into the carry bit. The result is saved in registers H and L.  H7=H7; H <sub>n-1</sub> =H <sub>n</sub> ; L <sub>7</sub> =H <sub>0</sub> ; L <sub>n-1</sub> =L <sub>n</sub> ; CY=L <sub>0</sub>                  |

| DSUB | 0 0 0 0 1 0 0 0  Addressing: Register                                                  | Z, S, P, CY,<br>AC, UI, V | 3      | 10      | Double Subtraction: The contents of registers B and C are subtracted from the contents of registers H and L. The result is saved in registers H and L (H) (L)=(H) (L) - (B) (C)                                                                                                                                                                                                            |

| IUNL | 1 1 0 1 1 1 0 1<br>low-order address<br>high-order address<br>Addressing:<br>Immediate | none                      | 2 or 3 | 7 or 10 | Jump on NOT UI Flag: Control is transferred to the instruction address specified in bytes 2 and 3 of the current instruction if the Unsigned Indicator Flag (UI) is reset. Otherwise control continues sequentially.  If NOT (UI): PC = (byte 3)(byte 2)                                                                                                                                   |

| JUI  | 1 1 1 1 1 0 1<br>low-order address<br>high-order address<br>Addressing:<br>Immediate   | none                      | 2 or 3 | 7 or 10 | Jump on UI Flag: Control is transferred to the instruction address specified in bytes 2 and 3 of the current instruction if the Unsigned Indicator Flag (UI) is set. Otherwise control continues sequentially.  If (UI): PC = (byte 3)(byte 2)                                                                                                                                             |

| LDHI | 0 0 1 0 1 0 0 0 data Addressing: Immediate Register                                    | none                      | 3      | 10      | Load D, E with H, L Plus Immediate Byte: The immediate byte is added to the contents of registers H and L, and the result is saved in registers D and E.  (D) (E) = (H) (L) + (byte 2)                                                                                                                                                                                                     |

| LDSI | 0 0 1 1 1 0 0 0 data  Addressing: Immediate Register                                   | лопе                      | 3      | 10      | Load D and E with SP Plus Immediate Byte: The 2 bytes of register SP are added to the immediate byte, and the result saved in registers D and E. (D) (E) = (SPH) (SPL) + (byte 2)                                                                                                                                                                                                          |

| LHLX | 1 1 1 0 1 1 0 1  Addressing: Register Indirect                                         | none                      | 3      | 10      | Load H and L Indirect Through D and E: The contents of the memory location given by registers D and E are moved to register L. The contents of the next location are moved to register H.  L=((D) (E)); H=((D)(E) + 1)                                                                                                                                                                     |

| RDEL | 0 0 0 1 1 0 0 0  Addressing: Register                                                  | CY, V                     | 3      | 10      | Rotate D and E Left Through Carry: The contents of registers D and E are rotated one bit left through the carry flag. The low-order bit is set equal to the CY flag and the CY flag is set to the value shifted out of the high-order bit.  D <sub>n+1</sub> =D <sub>n</sub> ; D <sub>0</sub> ; E <sub>7</sub> ; CY=D <sub>7</sub> ; E <sub>n+1</sub> =E <sub>n</sub> ; E <sub>0</sub> =CY |

| RSTV | 1 1 0 0 1 0 1 1  Addressing: Register Indirect                                         | none                      | 1 or 3 | 6 or 12 | Restart on Overflow: If overflow flag V is set, then the actions below are performed. Otherwise, control continues sequentially.  If (V): SP - 1=PCH; SP - 2=PCL; SP=SP - 2; PC=40HEX                                                                                                                                                                                                      |

| SHLX | 1 1 0 1 1 0 0 1  Addressing: Register Indirect                                         | none                      | 3      | 10      | Store H and L Indirect Through D and E:<br>The contents of register L are moved to the memory location given by registers D and E. The contents of register H are moved to the next memory location. $(D)(E) = L; ((D)(E) + 1) = H$                                                                                                                                                        |