# CA91C014

# VMEbus AVICS CONTROL CIRCUIT (ACC)

- Full VMEbus system controller functions

- · Auto-ID slot identification

- · Automatic VMEbus SYSCON identification

- Bus isolation (Bi-mode™) controller

- · Multiple VMEbus request and release options

- · Local bus requester/arbiter

- · Bus request on any of the four VMEbus levels

- Multiple VMEbus arbitration schemes

- VMEbus interrupt handler for all seven VMEbus interrupts

- VMEbus Interrupter on any of the seven VMEbus interrupts

- Local interrupt handler

- Watchdog timer and local bus timeout

- · Reset and clock generation

- Four general purpose clocks

14µs DRAM refresh clock

2.4615 MHz baud clock

1µs and 14 ms general purpose clocks

Tick clocks from 200µs to 100ms

- Low power CMOS, with power dissipation < 1W)</li>

- 144 Pin Grid Array package

- · Available in MIL-STD 883C Class B version

The CA91C014 Advanced System Architecture Control Circuit (ACC) is part of the Advanced VMEbus Interface Chip Set (AVICS); the other part being the CA91C015 Data and Address Register File (DARF). The AVICS integrates all the functions commonly required to interface a card to the VMEbus, while adding features that provide major architectural improvements.

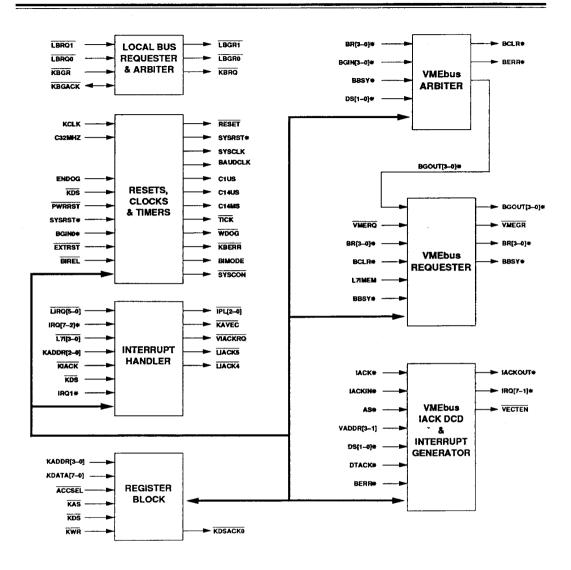

The ACC is designed to work with the DARF, but is also capable of being used as a stand-alone device to provide the feature list above. The functions of the ACC are separated into seven distinct modules:

- · Reset, Clock, and BI-mode™ Module

- · Local Bus Requester/Arbiter

- · Interrupt Handler

- VMEbus Requester

- VMEbus Arbiter

- · IACK Daisy Chain Driver

- · Register Block

The Reset, Clocks, and BI-mode™ module and the Local Bus Requester module are basically service functions and have very little interaction with software. The Register Block module provides the programming interface to the device. The remaining four modules; the Interrupt Handler, the VMEbus Arbiter, VMEbus Requester and IACK Daisy Chain Driver modules, can be configured by software to operate in various modes. They are accessed via the Register Block module.

BI-mode™ is a trademark of DY-4 Systems Inc, denoting the Bus Isolation mode.

Figure 1: CA91C014 ACC BLOCK DIAGRAM

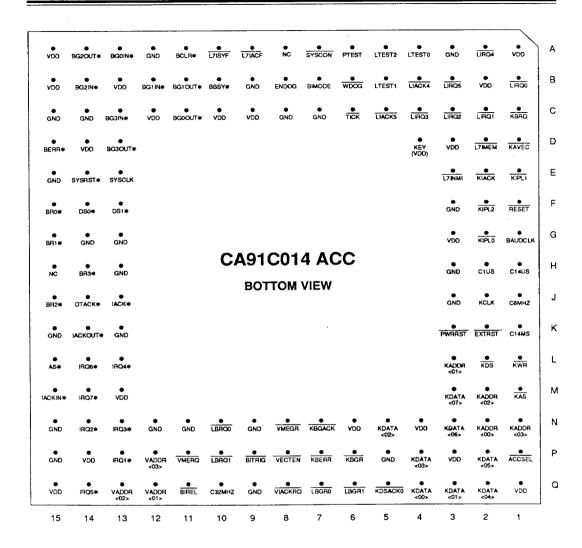

Figure 2: PIN CONFIGURATION for 144-PIN PGA PACKAGE

Table 1: ACC PGA PINOUT

| Pin        | Signal          | Signal Group        |       | Pin | Signal          | Signal Group        |

|------------|-----------------|---------------------|-------|-----|-----------------|---------------------|

| A1         | V <sub>DO</sub> |                     |       | C9  | V <sub>DD</sub> |                     |

| A2         | LIRQ4           | Interrupt           |       | C10 | V <sub>DD</sub> |                     |

| А3         | v <sub>ss</sub> |                     |       | C11 | BG0OUT*         | VMEbus              |

| A4         | LTEST0          | Reset, Clock & Mode |       | C12 | V <sub>DD</sub> |                     |

| A5         | LTEST2          | Reset, Clock & Mode |       | C13 | BG3IN*          | VMEbus              |

| A6         | PTEST           | Reset, Clock & Mode |       | C14 | v <sub>ss</sub> |                     |

| A7         | SYSCON          | Reset, Clock & Mode |       | C15 | v <sub>ss</sub> |                     |

| A8         | N/C             |                     |       | D1  | KAVEC           | Interrupt           |

| <b>A</b> 9 | L7IACF          | Interrupt           |       | D2  | L7IMEM          | Interrupt           |

| A10        | L7ISYF          | Interrupt           |       | D3  | V <sub>DD</sub> |                     |

| A11        | BCLR*           | VMEbus              |       | D13 | BG3OUT*         | VMEbus              |

| A12        | v <sub>ss</sub> |                     |       | D14 | V <sub>DD</sub> |                     |

| A13        | BG0IN*          | VMEbus              |       | D15 | BERR*           | VMEbus              |

| A14        | BG2OUT*         | VMEbus              |       | E1  | KIPL1           | Interrupt           |

| A15        | V <sub>DD</sub> |                     |       | E2  | KIACK           | interrupt           |

| B1         | LIRGO           | Interrupt           |       | E3  | L7INMI          | Interrupt           |

| B2         | V <sub>DD</sub> |                     |       | E13 | SYSCLK          | Reset, Clock & Mode |

| B3         | LIRQ5           | Interrupt           |       | E14 | SYSRST*         | Reset, Clock & Mode |

| B4         | LIACK4          | Interrupt           |       | E15 | v <sub>ss</sub> |                     |

| B5         | LTEST1          | Reset, Clock & Mode |       | F1  | RESET           | Reset, Clock & Mode |

| B6         | WDOG            | Reset, Clock & Mode |       | F2  | KIPL2           | Interrupt           |

| B7         | BIMODE          | Reset, Clock & Mode |       | F3  | v <sub>ss</sub> |                     |

| B8         | ENDOG           | Reset, Clock & Mode |       | F13 | DS1*            | VMEbus              |

| B9         | v <sub>ss</sub> |                     |       | F14 | DS0*            | VMEbus              |

| B10        | BBSY*           | VMEbus              |       | F15 | BR0*            | VMEbus              |

| B11        | BG1OUT*         | VMEbus              |       | G1  | BAUDCLK         | Reset, Clock & Mode |

| B12        | BG1IN*          | VMEbus              |       | G2  | KIPLO           | Interrupt           |

| B13        | V <sub>DD</sub> |                     |       | G3  | V <sub>DO</sub> |                     |

| B14        | BG2IN*          | VMEbus              |       | G13 | v <sub>ss</sub> |                     |

| B15        | V <sub>DD</sub> |                     |       | G14 | ν <sub>ss</sub> |                     |

| C1         | KBRQ            | Local Bus           | 200   | G15 | BR1*            | VMEbus              |

| C2         | LIRQ1           | Interrupt           |       | H1  | C14US           | Reset, Clock & Mode |

| СЗ         | LIRQ2           | Interrupt           |       | H2  | C1US            | Reset, Clock & Mode |

| C4         | LIRQ3           | Interrupt           | *     | нз  | v <sub>ss</sub> |                     |

| C5         | LIACK5          | Interrupt           |       | H13 | v <sub>ss</sub> |                     |

| C6         | TICK            | Reset, Clock & Mode | N. P. | H14 | BR3*            | VMEbus              |

| C7         | v <sub>ss</sub> |                     |       | H15 | N/C             |                     |

| C8         | v <sub>ss</sub> |                     |       | J1  | C8MHZ           | Reset, Clock & Mode |

Table 1: ACC PGA PINOUT CON'T

| Pin | Signal          | Signal Group        | 1000          | Pin | Signal            | Signal Group        |

|-----|-----------------|---------------------|---------------|-----|-------------------|---------------------|

| J2  | KCLK            | Reset, Clock & Mode |               | N12 | V <sub>ss</sub>   |                     |

| J3  | V <sub>SS</sub> |                     |               | N13 | IRQ3*             | Interrupt           |

| J13 | IACK*           | VMEbus              | . 3781<br>200 | N14 | iRQ2 <b>∗</b>     | Interrupt           |

| J14 | DTACK*          | VMEbus              |               | N15 | v <sub>ss</sub> ' |                     |

| J15 | BR2*            | VMEbus              |               | P1  | ACCSEL            | Local Bus           |

| К1  | C14MS           | Reset, Clock & Mode |               | P2  | KDATA 05          | Local Bus           |

| К2  | EXTRST          | Reset, Clock & Mode |               | P3  | V <sub>DD</sub>   |                     |

| кз  | PWRRST          | Reset, Clock & Mode |               | P4  | KDATA 03          | Local Bus           |

| K13 | v <sub>ss</sub> |                     |               | P5  | v <sub>ss</sub>   |                     |

| K14 | IACKOUT*        | VMEbus              |               | P6  | KBGR              | Local Bus           |

| K15 | v <sub>ss</sub> |                     |               | P7  | KBERR             | Local Bus           |

| L1  | KWR             | Local Bus           |               | P8  | VECTEN            | Interrupt           |

| L2  | KDS             | Local Bus           |               | P9  | BITRIG            | Reset, Clock & Mode |

| L3  | KADDR 01        | Local Bus           |               | P10 | LBRQ1             | Local Bus           |

| L13 | IRQ4 <b>∗</b>   | Interrupt           |               | P11 | VMERQ             | VMEbus              |

| L14 | IRQ6∗           | Interrupt           | 8.50          | P12 | VADDR 03          | VMEbus              |

| L15 | AS*             | VMEbus              |               | P13 | IRQ1*             | Interrupt           |

| M1  | KAS             | Local Bus           |               | P14 | v <sub>DD</sub>   |                     |

| M2  | KADDR 02        | Local Bus           | - 1           | P15 | v <sub>ss</sub>   |                     |

| M3  | KDATA 07        | Local Bus           |               | Q1  | V <sub>DD</sub>   |                     |

| M13 | V <sub>DD</sub> |                     |               | Q2  | KDATA 04          | Local Bus           |

| M14 | IRQ7 <b>∗</b>   | Interrupt           |               | Q3  | KDATA 01          | Local Bus           |

| M15 | IACKIN*         | VMEbus              |               | Q4  | KDATA 00          | Local Bus           |

| N1  | KADDR 03        | Local Bus           |               | Q5  | KDSACK0           | Loçal Bus           |

| N2  | KADDR 00        | Local Bus           |               | Q6  | LBGR1             | Local Bus           |

| N3  | KDATA 06        | Local Bus           |               | Q7  | LBGR0             | Local Bus           |

| N4  | V <sub>DD</sub> |                     | ĝ.            | Q8  | VIACKRO           | Interrupt           |

| N5  | KDATA 02        | Local Bus           |               | Q9  | v <sub>ss</sub>   |                     |

| N6  | V <sub>DD</sub> |                     |               | Q10 | C32MHZ            | Reset, Clock & Mode |

| N7  | KBGACK          | Local Bus           |               | Q11 | BIREL             | Reset, Clock & Mode |

| N8  | VMEGR           | VMEbus              |               | Q12 | VADDR 01          | VMEbus              |

| N9  | v <sub>ss</sub> |                     |               | Q13 | VADDR 02          | VMEbus              |

| N10 | LBROO           | Local Bus           |               | Q14 | IRQ5*             | Interrupt           |

| N11 | v <sub>ss</sub> |                     |               | Q15 | V <sub>DD</sub>   |                     |

Note: Ceramic PGA packages have an additional pin, D4, that is internally connected to pin D3 (V<sub>DD</sub>).

Table 2a: VMEbus SIGNALS

| Symbol             | Pin(s)             | Туре | Name and Function                     |

|--------------------|--------------------|------|---------------------------------------|

| AS*                | L15                | 1    | VMEbus address strobe                 |

| BBSY*              | B10                | 1/0  | Bus Busy indicator                    |

| BCLR*              | A11                | ИО   | Bus Clear request                     |

| BERR*              | D15                | 1/0  | VMEbus data transfer error            |

| BG3IN* - BG0IN*    | C13, B14, B12, A13 | 3    | Bus Grant in of grant daisy chain     |

| BG3OUT#<br>BG0OUT# | D13, A14, B11, C11 | 0    | Bus Grant Out of grant daisy chain    |

| BR3* - BR0*        | H14, J15, G14, F15 | 1/0  | Bus request lines                     |

| DS1* - DS0*        | F13, F14           | 1    | VMEbus data strobes 1, 0              |

| DTACK*             | J14                | 1    | VMEbus data transfer acknowledge      |

| IACK*              | J13                | 1    | Interrupt Acknowledge cycle indicator |

| IACKIN*            | M15                | 1    | IACK daisy chain                      |

| IACKOUT*           | K14                | 0    | IACK daisy chain                      |

| VADDR 03 - 01      | P12, Q13, Q12      | 1    | VMEbus address bits 3, 2, 1           |

| VMEGR              | N8                 | 0    | VMEbus grant to the DARF              |

| VMERQ              | P11                | ī    | VMEbus request from the DARF          |

Table 2b: LOCAL BUS SIGNALS

| Symbol        | Pin(s)                            | Туре | Name and Function                      |

|---------------|-----------------------------------|------|----------------------------------------|

| ACCSEL        | P1                                | 1    | ACC select                             |

| KADDR 03 00   | N1, M2, L3, N2                    | ı    | Address lines 3 through 0              |

| KAS           | M1                                | ı    | Local address strobe                   |

| KBERR         | P7                                | 0    | Local bus timeout error signal         |

| KBGACK        | N7                                | 1/0  | Bus grant acknowledge                  |

| KBGR          | . P6                              | I    | Local bus grant from the local CPU     |

| KBRQ          | C1                                | 0    | Local bus request to the local CPU     |

| KDATA 07 - 00 | M3, N3, P2, Q2,<br>P4, N5, Q3, Q4 | 1/0  | Data lines 7 through 0                 |

| KDS           | L2                                | 1    | Local data strobe                      |

| KDSACK0       | Q5                                | 0    | Data transfer acknowledge signal       |

| KWR           | L1                                | 1    | Local write control                    |

| LBGR0         | Q7                                | 0    | Local bus grant to the DARF            |

| LBGR1         | Q6                                | 0    | Local bus grant to the second device   |

| LBRQ0         | N10                               |      | Local bus request from the DARF        |

| LBRQ1         | P10                               | 1    | Local bus request from a second device |

Table 2c: INTERRUPT SIGNALS

| Symbol        | Pin(s)                          | Туре | Name and Function                                |

|---------------|---------------------------------|------|--------------------------------------------------|

| IRQ1*         | P13                             | 1/0  | VMEbus interrupt 1 and Bl-mode™ trigger          |

| IRQ7* - IRQ2* | M14, L14, Q14,<br>L13, N13, N14 | VO   | VMEbus interrupts 7-2                            |

| KAVEC         | D1                              | 0    | Autovector response to acknowledge cycle         |

| KIACK         | E2                              | ı    | Interrupt acknowledge cycle indicator            |

| KIPL2 - KIPL0 | F2, E1, G2                      | 0    | Interrupt level code to CPU                      |

| L7INMI        | E3                              | 1    | Local level 7 non maskable interrupt             |

| L7IMEM        | D2                              | 1    | Local level 7 interrupt typically memory failure |

| L7IACF        | A9                              | 1    | Level 7 interrupt, typically ACFAIL*             |

| L7ISYF        | A10                             | ı    | Level 7 interrupt, typically SYSFAIL*            |

| LIACK4        | B4                              | 0    | Acknowledge to interrupt on LIRQ4                |

| LIACK5        | C5                              | 0    | Acknowledge to interrupt on LIRQ5                |

| LIRQ5 - LIRQ0 | B3, A2, C4,<br>C3, C2, B1       | 1    | Local general purpose interrupts 5 - 0           |

| VECTEN        | P8                              | 0    | Vector enable signal to DARF                     |

| VIACKRQ       | Q8                              | 0    | Signal to DARF to acknowledge VMEbus interrupt   |

# Table 2d: RESET, CLOCK, and MODE SIGNALS

| Symbol          | Pin(s)     | Туре | Name and Function                       |

|-----------------|------------|------|-----------------------------------------|

| BAUDCLK         | G1         | 0    | 2.4615 megahertz baud rate cłock        |

| BIMODE          | B7         | 0    | Bl-mode™ indicator                      |

| BIREL           | Q11        | 1    | Bi-mode™ exit signal                    |

| BITRIG          | P9         | ı    | Bl-mode™ trigger signal                 |

| C1US            | H2         | 0    | 1 microsecond clock output              |

| C14MS           | K1         | 0    | 14 millisecond clock output             |

| C14US           | H1         | 0    | 14 microsecond clock output             |

| C8MHZ           | J1         | 0    | 8 MHz clock output                      |

| C32MHZ          | Q10        | 1    | 32 megahertz clock input                |

| ENDOG           | 88         | ı    | Enable watchdog control pin             |

| EXTRST          | K2         | ī    | External reset                          |

| KCLK            | J2         | 1    | CPU clock                               |

| LTEST2 - LTEST0 | A5, B5, A4 | ı    | IC manufacturing test                   |

| PTEST           | A6         | 0    | IC manufacturing test                   |

| PWRRST          | КЗ         | ı    | Power up reset input, from R-C network  |

| RESET           | F1         | 0    | Local (card) reset output               |

| SYSCLK          | E13        | 1/0  | VMEbus SYSCLK signal                    |

| SYSCON          | A7         | 0    | VMEbus system controller indicator      |

| SYSRST*         | E14        | 1/0  | VMEbus SYSRST* signal                   |

| TICK            | C6         | 0    | Tick output, available for interrupting |

| WDOG            | B6         | 0    | Watchdog signal, 2 second period        |

### **TERMINOLOGY**

| Signals on the VMEbus and those within the circuit card  |

|----------------------------------------------------------|

| may be active high or active low. Active low signals are |

| defined as being true or asserted when they are at a low |

| voltage, and conversely for active high signals. VMEbus  |

| active low signals are indicated by the * suffix. Local  |

| active low signals are indicated by an OVERBAR.          |

Where there is a need to clarify whether a signal is a VMEbus or local signal, a V may be prefixed for VMEbus signals, an L for general local signals, or a K for signals only connecting to the local CPU.

The I/O type abbreviations used in Tables 3 and 14 are defined in this section. A number suffix (where appended) indicates the current rating of the output.

| TP       | Totem pole output                                |

|----------|--------------------------------------------------|

| TS       | Tri-state totem pole output                      |

| OD       | Open drain output                                |

| VOD      | VMEbus specification open drain output           |

| VTS      | VMEbus specification tri-state totem pole output |

|          |                                                  |

| CMOS SCH | Schmitt trigger input with CMOS thresholds       |

| TTL      | Input with TTL thresholds                        |

| TTL PD   | Input with TTL thresholds and integral pull down |

| TTL PU   | Input with TTL thresholds and integral pull up   |

| TTL SCH  | Schmitt trigger input with TTL thresholds        |

Table 3: SIGNAL INPUT and OUTPUT TYPE CLASSIFICATION

| Signal            | Input   | Output |         | Signal          | Input    | Output |

|-------------------|---------|--------|---------|-----------------|----------|--------|

| ACCSEL            | TTL     |        |         | KBRQ            |          | TP4    |

| AS*               | ∏L      |        |         | KCLK            | Π.       |        |

| BAUDCLK           |         | TP8    |         | KDATA 07 - 00   | TTL      | TS6    |

| BBSY*             | TTL SCH | VOD48  |         | KDS             | 171.     |        |

| BCLR*             | TTL SCH | VTS64  |         | KDSACK0         | i i      | TS8    |

| BERR*             | TTL SCH | VOD48  |         | KIACK           | TTL      |        |

| BG2IN* - BG0IN*   | TTL PU  |        |         | KWR             | 111.     |        |

| BG3IN*            | TTLPD   |        |         | LBGR0           |          | TP4    |

| BG3OUT# - BG0OUT# |         | TP8    |         | LBGR1           | ]        | TP4    |

| BIMODE            |         | TP8    |         | LBRQ0           | π.       |        |

| BIREL             | ™∟      |        |         | LBRQ1           | TTL      |        |

| BR3* - BR0*       | TTL SCH | VOD48  |         | LIACK4          | 1        | TP4    |

| C1US              |         | TP8    |         | LIACK5          |          | TP4    |

| C14MS             | ļ       | TP4    |         | LIRQ5 - LIRQ0   | TTL      |        |

| C14US             | -       | TP8    |         | LTEST2 - LTEST0 | TTL      |        |

| C8MHZ             |         | TP8    |         | L7!ACF          | п.       |        |

| C32MHZ            | τπ∟     |        |         | L7IMEM          | π.       |        |

| DS1*, DS0*        | ττι∟    |        |         | L7INMI          | TIL      |        |

| DTACK*            | TTL     |        |         | L7ISYF          | π.       |        |

| ENDOG             | TTL     |        |         | PTEST           | 1        | TP4    |

| EXTRST            | ΠL      |        |         | PWRRST          | CMOS SCH |        |

| IACK*             | TTL :   |        |         | RESET           |          | TP12   |

| IACKIN*           | πι      |        |         | SYSCLK          | TTLSCH   | VTS64  |

| IACKOUT*          |         | TP8    |         | SYSCON          |          | TP8    |

| KIPL2 - KIPL0     |         | TP4    |         | SYSRST*         | TTL SCH  | VOD48  |

| IRQ7* - IRQ1*     | TTL SCH | VOD48  |         | TICK            |          | TP4    |

| KADDR 03 00       | TTL     |        |         | VADDR 03 01     | mL       |        |

| KAS               | TTL     |        |         | VECTEN          |          | TP4    |

| KAVEC             | ł       | TP4    |         | VIACKRO         |          | TP4    |

| KBERR             | ,       | TS8    |         | VMEGR           |          | TP4    |

| KBGACK            | TTL     | OD8    |         | VMERQ           | TTL      | •      |

| KBGR              | TTL     |        | To door | WDOG            |          | TP4    |

Table 4 : AC CHARACTERISTICS (CLOCK and TIMING SIGNALS) Commercial:  $T_A = 0^\circ$  to +70°C,  $V_{DD} = 5V \pm 5\%$ , Military  $T_A = -55^\circ$  to +125°C,  $V_{DD} = 5V \pm 10\%$

|                 |                               |      | Lit  | nits |      |      |

|-----------------|-------------------------------|------|------|------|------|------|

| Symbol          | Description                   | Min  | Тур  | Max  |      | Unit |

|                 |                               |      |      | Com  | Mil  |      |

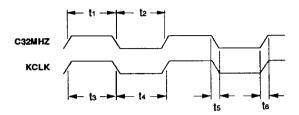

| t <sub>i</sub>  | C32MHZ high time              | 10.6 | 15.6 | 20.6 | 20.6 | ns   |

| t <sub>2</sub>  | C32MHZ low time               | 10.6 | 15.6 | 20.6 | 20.6 | ns   |

| t <sub>3</sub>  | KCLK high time (Note 1)       | 20   | •    | •    | -    | ns   |

| t <sub>4</sub>  | KCLK low time (Note 1)        | 20   | -    |      | -    | ns   |

| t <sub>s</sub>  | C32MHZ and KCLK fall time     | 0    | •    | 5    | 5    | ns   |

| t <sub>e</sub>  | C32MHZ and KCLK rise time     | 0    | •    | 5    | 5    | ns   |

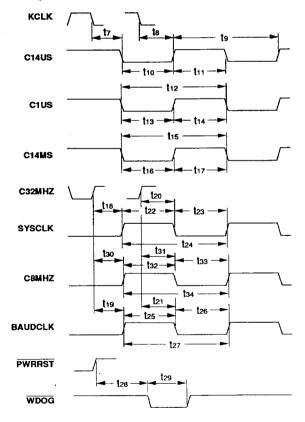

| t <sub>7</sub>  | C14US low from KCLK fall      | 3.9  | 10   | 20   | 25   | ns   |

| t <sub>s</sub>  | C14US high from KCLK fall     | 3.2  | 8    | 16   | 20   | ns   |

| t <sub>9</sub>  | C14US period (Note 2)         | -    | 14   | •    | •    | μs   |

| t <sub>10</sub> | C14US low time (Note 2)       | -    | 7    | -    | -    | μs   |

| t <sub>11</sub> | C14US high time (Note 2)      |      | 7    |      | •    | μs   |

| t <sub>12</sub> | C1US period                   | 1    | 1    | 1    | 1    | μs   |

| t <sub>13</sub> | C1US low time                 | 500  | 500  | 500  | 500  | ns   |

| t <sub>14</sub> | C1US high time                | 500  | 500  | 500  | 500  | ns   |

| t <sub>15</sub> | C14MS period (Note 3)         | 14.3 | 14.3 | 14.3 | 14.3 | ms   |

| t <sub>16</sub> | C14MS low time (Note 3)       | 7.16 | 7.16 | 7.16 | 7.16 | ms   |

| t <sub>17</sub> | C14MS high time (Note 3)      | 7.16 | 7.16 | 7.16 | 7.16 | ms   |

| t <sub>18</sub> | SYSCLK high from C32MHZ rise  | 3.9  | 9    | 18   | 22   | ns   |

| t <sub>19</sub> | BAUDCLK high from C32MHZ rise | 3.2  | 8    | 15   | 18   | ns   |

| t <sub>20</sub> | SYSCLK low from C32MHZ rise   | 4.7  | 12   | 23   | 29   | ns   |

| t <sub>21</sub> | BAUDCLK low from C32MHZ rise  | 3.9  | 10   | 19   | 23   | ns   |

| t <sub>22</sub> | SYSCLK high time              | 25.0 | 31.3 | 37.5 | 37.5 | ns   |

| t <sub>23</sub> | SYSCLK low time               | 25.0 | 31.3 | 37.5 | 37.5 | ns   |

| t <sub>24</sub> | SYSCLK period                 | 62.5 | 62.5 | 62.5 | 62.5 | กร   |

| t <sub>25</sub> | BAUDCLK high time (Note 4)    | 187  | 187  | 187  | 187  | ns   |

| t <sub>26</sub> | BAUDCLK low time (Note 4)     | 219  | 219  | 219  | 219  | ns   |

| t <sub>27</sub> | BAUDCLK period (Note 4)       | 406  | 406  | 406  | 406  | ns   |

| t <sub>28</sub> | WDOG expiry period (Note 5)   | 2.0  | 2.0  | 2.0  | 2.0  | s    |

| t <sub>29</sub> | WDOG assertion time (Note 5)  | 200  | 200  | 200  | 200  | ms   |

| t <sub>30</sub> | C8MHZ high from C32MHZ rise   | 4.4  | 11   | 21   | 26   | กร   |

| t <sub>31</sub> | C8MHZ low from C32MHZ rise    | 5.0  | 13   | 25   | 31   | ns   |

| t <sub>32</sub> | C8MHZ high time               |      | 62.5 | -    |      | ns   |

| t <sub>33</sub> | C8MHZ low time                | -    | 62.5 | -    | - 1  | กร   |

| t <sub>34</sub> | C8MHZ period                  | 125  | 125  | 125  | 125  | ns   |

- 1. KCLK must be the same as the CPU clock; any frequency up to 25 MHz is valid.

- 2. C14US changes are synchronized by ACC to falling edge of KCLK, causing jitter on each KCLK edge equal to the KCLK period.

- 3. The exact frequency of C14MS is 14,3333... ms, equal to 14 µs times 1024.

- 4. BAUDCLK is 32 MHz divided by 13, high 6 parts out of 13. High time is 187.5 ns, low time is 218.75 ns, frequency is 2.461538 MHz.

- 5. Expiry period begins at last reset, deassertion of ENDOG pin, or clearing of counter by software. Period and low time tolerance is ±1 μs.

# Figure 3: CLOCK and TIMING SIGNALS

# a) Required Clock Input Characteristics

# b) Generated Timing Clock Characteristics

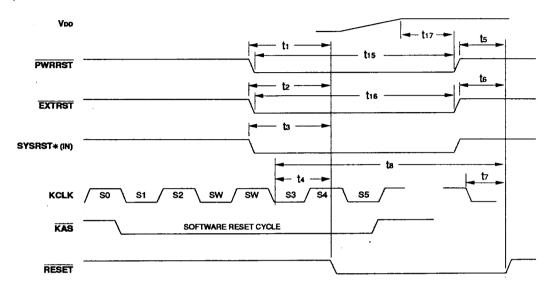

Table 5 : AC CHARACTERISTICS (RESET SIGNAL TIMING) Commercial:  $T_A = 0^\circ$  to +70°C,  $V_{DD} = 5V \pm 5\%$ , Military  $T_A = -55^\circ$  to +125°C,  $V_{DD} = 5V \pm 10\%$

|                 |                                             | Limite |      |      |      |      |  |

|-----------------|---------------------------------------------|--------|------|------|------|------|--|

| Symbol          | Description                                 | Min    | Тур  | Ma   | x    | Unit |  |

|                 |                                             |        |      | Com  | Mil  |      |  |

| t,              | RESET assertion from PWRRST (Note 1)        | 6.2    | 16   | 32   | 39   | ns   |  |

| t <sub>2</sub>  | RESET assertion from EXTRST                 | 5.4    | 13   | 27   | 32   | ns   |  |

| t <sub>3</sub>  | RESET assertion from SYSRST*                | 5.6    | 13   | 26   | 31   | ns   |  |

| t <sub>4</sub>  | RESET assert from s/w reset (Note 2)        | 10     | 26   | 51   | 62   | ns   |  |

| t <sub>5</sub>  | RESET negate from PWRRST                    | 0.21   | 0.22 | 0.23 | 0.23 | s    |  |

| t <sub>e</sub>  | RESET negate from EXTRST                    | 0.21   | 0.22 | 0.23 | 0.23 | 8    |  |

| t <sub>7</sub>  | RESET negate from KCLK low                  | 3.9    | 9.2  | 18   | 22   | ns   |  |

| t <sub>8</sub>  | RESET negate from s/w reset (Note 2)        | 0.21   | 0.22 | 0.23 | 0.23 | 8    |  |

| t <sub>o</sub>  | SYSRST* assert from PWRRST (Note 1)         | 6.6    | 17   | 34   | 41   | ns   |  |

| t,0             | SYSRST* assert from s/w reset (Note 2)      | 10     | 27   | 52   | 64   | ns   |  |

| t,,             | SYSRST* assert from BG0IN* (Note 3)         | 43     | 50   | 58   | 58   | ms   |  |

| t <sub>12</sub> | SYSRST* negate from PWRRST                  | 0.21   | 0.22 | 0.23 | 0.23 | 8    |  |

| t <sub>13</sub> | SYSRST* negate from s/w reset (Note 2)      | 0.21   | 0.22 | 0.23 | 0.23 | 8    |  |

| t,4             | SYSRST* negate from BG0IN* (Note 4)         | 0.21   | 0.22 | 0.23 | 0.23 | 8    |  |

| t <sub>15</sub> | PWRRST width, low (Note 1)                  | 50     | -    | -    |      | กร   |  |

| t,6             | EXTRST width, low (Note 1)                  | 50     | -    | -    |      | กร   |  |

| t,7             | PWRRST hold low from V <sub>DD</sub> = 4.5V | 100    | -    |      |      | ns   |  |

- 1. Assumes V<sub>DD</sub> stable at 5.0 V prior to PWRRST asserting.

- 2. Measured from indicated edge of S3 of CPU cycle.

- 3. Four successive samples of a low level on BG0IN\* by the rising edge of the internal 14 ms clock are required to initiate reset.

- 4. Measured from the first high level sampled on BG0IN\* after SYSRST\* has been started.

# Figure 4: RESET SIGNAL TIMING

# a) Local Reset Generation

# b) System Reset Generation

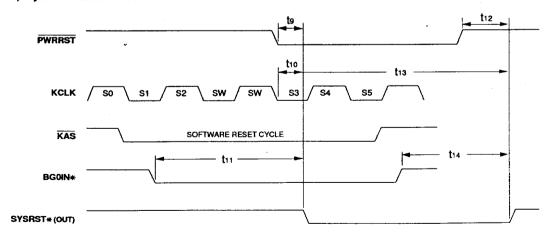

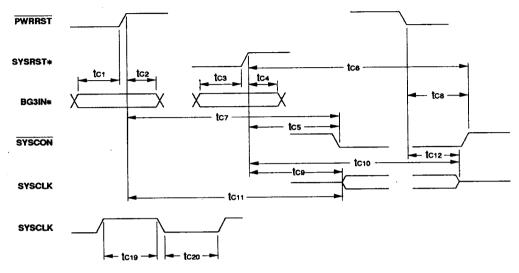

Table 6 : AC CHARACTERISTICS (SYSCON and BI-MODE™ TIMING)

Commercial: T<sub>A</sub> = 0° to +70°C, V<sub>DO</sub> = 5V ± 5%, Military T<sub>A</sub> = -55° to +125°C, V<sub>DO</sub> = 5V ± 10%

| Symbol           | Description                      | Min | Тур                                              | M   | MII | Unit |

|------------------|----------------------------------|-----|--------------------------------------------------|-----|-----|------|

|                  |                                  |     |                                                  | Com | Mil | 1    |

| tcı              | BG3IN* setup to PWRRST (Note 1)  | 200 |                                                  | -   | -   | ns   |

| t <sub>c2</sub>  | BG3IN* hold from PWRRST (Note 1) | 565 |                                                  | -   | -   | ns   |

| t <sub>C3</sub>  | BG3IN* setup to SYSRST*          | 10  | -                                                |     |     | ns   |

| t <sub>C4</sub>  | BG3IN* hold from SYSRST*         | 10  | <del>                                     </del> | -   | -   | ns   |

| t <sub>C5</sub>  | SYSCON assert from SYSRST* high  | 7.2 | 17                                               | 34  | 41  | ns   |

| t <sub>C6</sub>  | SYSCON negate from SYSRST* high  | 6.4 | 16                                               | 31  | 38  | ns   |

| t <sub>C7</sub>  | SYSCON assert from PWRRST up     | 465 | 500                                              | 565 | 565 | ns   |

| t <sub>C8</sub>  | SYSCON negate from PWRRST down   | 5.0 | 13                                               | 25  | 31  | ns   |

| t <sub>C9</sub>  | SYSCLK driving from SYSRST* high | 7.8 | 18                                               | 37  | 45  | ns   |

| t <sub>C10</sub> | SYSCLK high-z from SYSRST* high  | 8.1 | 20                                               | 40  | 49  | ns   |

| t <sub>C11</sub> | SYSCLK driving from PWRRST up    | 465 | 500                                              | 565 | 565 | ns   |

| t <sub>C12</sub> | SYSCLK high-z from PWRRST low    | 6.8 | 17                                               | 34  | 42  | ns   |

| t <sub>C13</sub> | BIMODE assert from IRQ1*         | 37  | 60                                               | 89  | 95  | ns   |

| t <sub>C14</sub> | IRQ1* assert by ABI s/w bit      | 8.6 | 22                                               | 43  | 52  | ns   |

| t <sub>C15</sub> | BIMODE assert by SBI s/w bit     | 7.4 | 19                                               | 37  | 45  | ns   |

| t <sub>C16</sub> | BIMODE negate from BIREL         | 3.6 | 9                                                | 17  | 21  | ns   |

<sup>1.</sup> BG3IN\* is sampled 500 ± 31.25 ns after PWRRST reaches logic 1.

# Figure 5: SYSCON and BI-MODE™ TIMING

# a) SYSCON and SYSCLK Characteristics

# b) BI-MODE™ Entry and Exit Timing

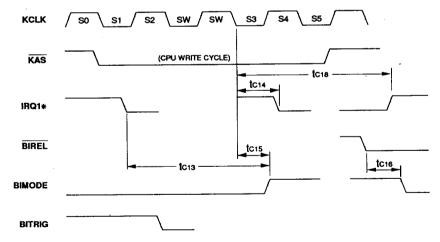

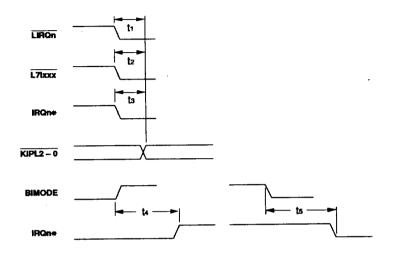

Table 7 : AC CHARACTERISTICS (INTERRUPT SIGNAL TIMING) Commercial:  $T_A$  = 0° to +70°C,  $V_{DD}$  = 5V ± 5%, Military  $T_A$  = -55° to +125°C,  $V_{DD}$  = 5V ± 10%

|                |                                       | Limits   |     |     |     |      |

|----------------|---------------------------------------|----------|-----|-----|-----|------|

| Symbol         | Description                           | Min      | Тур | Max |     | Unit |

|                |                                       | 1.       |     | Com | Mil | 1    |

| t <sub>t</sub> | KIPL change from local interrupt      | 9.3      | 24  | 48  | 59  | ns   |

| t <sub>2</sub> | Level 7 KIPL change from C32MHZ high  | 10.8     | 28  | 55  | 68  | ns   |

| t <sub>s</sub> | KIPL change from VME int              | 8.2      | 22  | 43  | 53  | ns   |

| t <sub>4</sub> | VME interrupt negate from BIMODE high | 3.0      | 8   | 15  | 39  | ns   |

| t <sub>s</sub> | VME interrupt reassert from KCLK high | 5.7      | 15  | 29  | 35  | ns   |

|                | (Note 1)                              | <u> </u> |     |     |     |      |

| t <sub>6</sub> | lack generation from KCLK             | 5.4      | 14  | 28  | 35  | ns   |

| t <sub>7</sub> | KIPL change from KCLK down            | 8.1      | 25  | 49  | 60  | ns   |

| t <sub>e</sub> | VME interrupt assert from KCLK        | 5.7      | 15  | 29  | 35  | ns   |

| t <sub>9</sub> | IACK negate from KDS negate           | 4.2      | 11  | 22  | 27  | ns   |

<sup>1.</sup> After next KCLK falling edge at which BIMODE is negated.

# Figure 6: INTERRUPT SIGNAL TIMING

# a) IPL Generation, BI-MODE Effect on IRQ Generation

# b) IRQ Assertion, Interrupt Enabling and Acknowledging

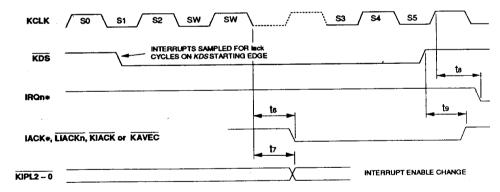

Table 8 : AC CHARACTERISTICS (REGISTER ACCESS READ and WRITE TIMING) Commercial:  $T_A = 0^\circ$  to +70°C,  $V_{DD} = 5V \pm 5\%$ , Military  $T_A = -55^\circ$  to +125°C,  $V_{DD} = 5V \pm 10\%$

| ĺ                |                                           |      | L   | imits    |                                                  |         |

|------------------|-------------------------------------------|------|-----|----------|--------------------------------------------------|---------|

| Symbol           | Description                               | Min  | Тур | N.       | lax                                              | Unit    |

|                  |                                           |      |     | Com      | Mil                                              | <u></u> |

| t,               | KAS hold high from KCLK (Note 1)          | 3.0  | -   | -        | -                                                | ns      |

| t <sub>2</sub>   | KAS setup low to KCLK (Note 1)            | 3.0  | -   | 1        | <b> </b> -                                       | ns      |

| t <sub>3</sub>   | KAS hold low from KCLK (Note 1)           | 0.0  | -   | •        | -                                                | ns      |

| t <sub>4</sub>   | KAS setup high to KCLK (Note 1)           | 3.0  | -   | -        | -                                                | ns      |

| t <sub>s</sub>   | KWR setup to KDS & ACCSEL low             | 7.0  | -   | <b> </b> | T -                                              | ns      |

| t <sub>6A</sub>  | KWR hold from either KDS or ACCSEL high   | 4.4  | -   | -        | <del>                                     </del> | ns      |

| t <sub>6B</sub>  | KWR hold from S4 end                      | 5    | -   | T        | <del>  -</del>                                   | ns      |

| t <sub>7</sub>   | KIACK setup to KCLK                       | 10.0 | -   | -        | <del>  -</del>                                   | ns      |

| t <sub>e</sub>   | KIACK hold from KCLK                      | 10.0 | -   | -        | 1 -                                              | ns      |

| t <sub>g</sub>   | Write cycle KADDR setup to KCLK (Note 2)  | 40.0 | -   | -        | <del>  -</del> -                                 | ns      |

| t <sub>10</sub>  | Write cycle KADDR hold from KCLK (Note 2) | 20.0 | ·   |          | -                                                | ns      |

| t,,              | KDATA setup to KCLK                       | 20.0 | -   | -        | 1 -                                              | ns      |

| t,2              | KDATA hold from KCLK                      | 20.0 | -   | -        | <del>-</del>                                     | ns      |

| t <sub>13</sub>  | KDSACK0 low from SW1 low (Note 6)         | 4.4  | 11  | 23       | 28                                               | ns      |

| t <sub>14</sub>  | KDATA driven from SW1 (KWR/ high)         | 4.1  | 10  | 17       | 21                                               | ns      |

| t <sub>15A</sub> | KDATA valid from KDS & ACCSEL low         | 6.5  | 16  | 32       | 39                                               | ns      |

| t <sub>158</sub> | KDATA valid from KADDR valid              | 7.1  | 17  | 35       | 43                                               | ns      |

| t <sub>16</sub>  | KDATA invalid from KADDR change           | 4.8  | 9   | 19       | 23                                               | ns      |

| t <sub>17</sub>  | KDATA high-z from KDS high (Note 7)       | 3.3  | 8   | 16       | 22                                               | ns      |

| t,8              | KDATA high-z from ACCSEL high (Note 7)    | 2.9  | 7   | 14       | 20                                               | ns      |

| t <sub>19</sub>  | KDATA high-z from KWR low (Note 7)        | 3.6  | 9   | 19       | 23                                               | ns      |

| t <sub>20</sub>  | KDSACKO high from KAS high (Note 8)       | 3.1  | 8   | 16       | 20                                               | ns      |

| t <sub>22</sub>  | KDSACKO high from ACCSEL high (Note 8)    | 2.2  | 6   | 12       | 15                                               | ns      |

| t <sub>23</sub>  | KDSACKO high-z from KCLK                  | 2.8  | 7   | 14       | 17                                               | ns      |

| t <sub>24</sub>  | KBERR low from KDS low (Note 9)           | 511  | 512 | 513      | 513                                              | μs      |

| t <sub>25</sub>  | KBERR high from KDS high                  | 3.3  | 8   | 16       | 20                                               | ns      |

| t <sub>26</sub>  | KBERR high-z from KCLK                    | 3.1  | 8   | 18       | 19                                               | ns      |

| t <sub>27</sub>  | TICK negate from KCLK                     | 7    | 15  | 31       | 38                                               | ns      |

- As detected at ACC pins at applicable logic low or high thresholds.

- Required for write cycles only; use parameters 15 and 16 for read cycles.

- Affects wait states inserted by 68020/68030; during write cycles under worst case conditions with a 25 MHz CPU, 2 wait states may be inserted instead of the normal 1 state.

- 4. KDS already low and first wait state SW1 already begun.

- 5. ACCSEL already low and first wait state SW1 already begun.

- 6. ACCSEL and KDS already low.

- 7. First signal to negate will disable data bus drivers.

- 8. First signal to negate will set KDSACKO high.

- 9. Unless disabled by software.

- 10.t21 is not used.

Figure 7: REGISTER ACCESS TIMING

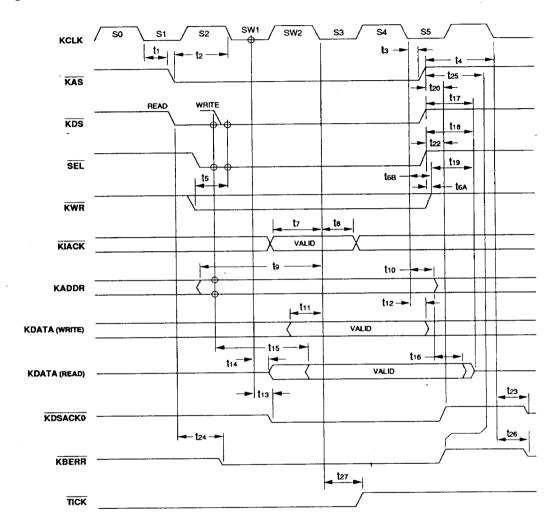

Table 9 : AC CHARACTERISTICS (LOCAL BUS REQUESTER TIMING) Commercial:  $T_A = 0^\circ$  to +70°C,  $V_{DD} = 5V \pm 5\%$ , Military  $T_A = -55^\circ$  to +125°C,  $V_{DD} = 5V \pm 10\%$

|                |                                                 | Limits |     |     |     |      |

|----------------|-------------------------------------------------|--------|-----|-----|-----|------|

| Symbol         | Description                                     | Min    | Тур | Max |     | Unit |

|                |                                                 |        |     | Com | Mil | 1    |

| t,             | State variable setup time                       | 15     | •   | -   |     | ns   |

| t <sub>2</sub> | State variable hold time                        | 15     | -   | •   | -   | ns   |

| t <sub>3</sub> | LBRQ1 or LBRQ0 to KBRQ low                      | 6.3    | 18  | 37  | 45  | ns   |

| t <sub>4</sub> | KCLK falling edge to LBGRn low                  | 5.4    | 14  | 27  | 33  | ns   |

| t <sub>5</sub> | KCLK falling edge to LBGRn high                 | 4.1    | 11  | 21  | 26  | ns   |

| t <sub>e</sub> | KCLK falling edge to KBGACK low (Note 1)        | 4.9    | 12  | 24  | 30  | ns   |

| L <sub>7</sub> | LBRQ0 and KAS high to KBGACK high-z<br>(Note 1) | 3.0    | 8   | 16  | 20  | ns   |

<sup>1.</sup> KBGACK is only asserted while device 0 (the DARF) is using the bus; when device 1 is using the bus, the ACC monitors KBGACK.

Figure 8: LOCAL BUS REQUESTER TIMING

Requester state machine transitions will occur if parameters  $t_1$  and  $t_2$  are met. If the signal involved in the present state does not meet parameters  $t_1$  and  $t_2$ , the state transition may or may not occur, but will not fail.

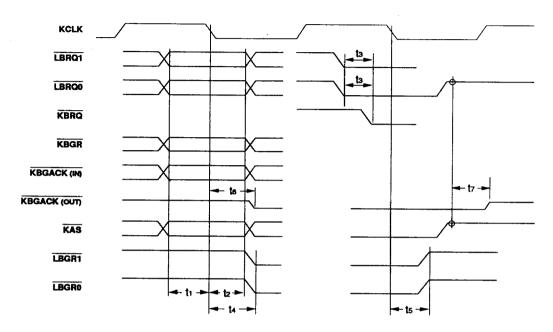

Table 10 : AC CHARACTERISTICS (VMEbus REQUESTER TIMING) Commercial:  $T_A = 0^\circ$  to +70°C,  $V_{DD} = 5V \pm 5\%$ , Military  $T_A = -55^\circ$  to +125°C,  $V_{DD} = 5V \pm 10\%$

|                 |                                                 |     | L   | lmits | •   |      |

|-----------------|-------------------------------------------------|-----|-----|-------|-----|------|

| Symbol          | Description                                     | Min | Тур | Ma    | ax  | Unit |

|                 |                                                 |     |     | Com   | Mil | 1    |

| t,              | VMERQ setup to C32MHZ rising edge<br>(Note 1)   | 5.0 | -   | -     |     | ns   |

| t <sub>2</sub>  | VMERQ hold from C32MHZ rising edge<br>(Note 1)  | 5.0 | -   | -     | -   | ns   |

| t <sub>3</sub>  | VMEGR low from C32MHZ rising edge               | 6.9 | 17  | 34    | 42  | ns   |

| t <sub>4</sub>  | VMEGR high from C32MHZ rising edge              | 5.5 | 14  | 27    | 32  | ns   |

| t <sub>5</sub>  | BRn* low from C32MHZ rising edge<br>(Note 2)    | 7.2 | 18  | 35    | 43  | ns   |

| t <sub>6</sub>  | BRn* high-z from C32MHZ rising edge<br>(Note 2) | 4.9 | 12  | 23    | 28  | ns   |

| t <sub>7</sub>  | BBSY* low from C32MHZ rising edge               | 8.2 | 21  | 41    | 50  | ns   |

| t <sub>8</sub>  | BBSY* high-z from VMERQ rising edge             | 4.1 | 10  | 18    | 28  | ns   |

| t <sub>9</sub>  | BGnOUT* low from C32MHZ rising edge<br>(Note 2) | 4.8 | 12  | 23    | 28  | ns   |

| t <sub>10</sub> | BGnOUT* high from C32MHZ rising edge (Note 2)   | 4.5 | 11  | 22    | 28  | ns   |

| t,,             | BGnOUT* low from BGnIN* low (Note 3)            | 3.5 | 9   | 19    | 23  | ns   |

| t <sub>12</sub> | BGnOUT* high from BGnIN* high (Note 3)          | 3.1 | 8   | 15    | 19  | ns   |

- Meeting parameters 1 and 2 ensure a requester state machine transition on the clock edge shown; otherwise the transition will occur on that edge or the next edge.

- 2. Applies to the Bus Request and Bus Grant of the level the ACC is configured to use.

- 3. Applies to the three Bus Grant levels the ACC is not configured to use.

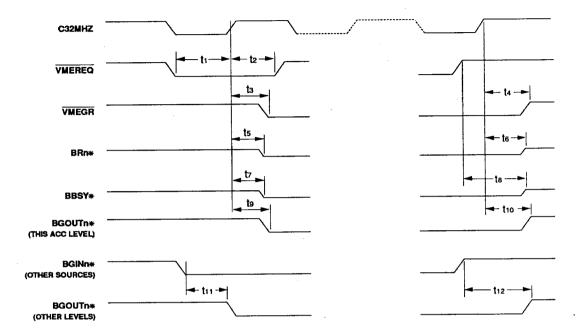

Figure 9: VMEbus REQUESTER TIMING

Table 11 : AC CHARACTERISTICS (VMEbus ARBITER TIMING) Commercial:  $T_A = 0^{\circ}$  to +70°C,  $V_{DD} = 5V \pm 5\%$ , Military  $T_A = -55^{\circ}$  to +125°C,  $V_{DD} = 5V \pm 10\%$

| ļ              |                                       |         |            |              |             |      |

|----------------|---------------------------------------|---------|------------|--------------|-------------|------|

| Symbol         | Description (Note 1)                  | Min     | т Тур      | Max          |             | Unit |

|                |                                       |         | •          | Com          | Mil         |      |

| t <sub>i</sub> | BGnOUT* low from C32MHZ rising edge   | 4.8     | 13         | · 26         | 32          | ns   |

| Ļ              | BCLR* low from C32MHZ rising edge     | 5.7     | 19 .       | 37           | 45          | ns   |

| t <sub>a</sub> | BCLR* high from C32MHZ rising edge    | 5.7     | 14         | 28           | 34          | ns   |

| t <sub>4</sub> | First DS* low to BERR* asserted       | progran | nmable: 10 | 6, 32, 64 μs | ±1 µs or ne | ever |

| t <sub>s</sub> | Last DS* high to BERR* high impedance | 2.6     | 7          | 13           | 16          | ns   |

| t <sub>e</sub> | BGn* low time                         | -       | -          | 17           | 17          | μs   |

| t <sub>7</sub> | BGn* high timeout recovery time       | 15      | 16         | 17           | 17          | μs   |

Bus Request setup and hold specifications are not provided. The BGn\*s are sampled on every C32MHZ rising edge. If a BGn\*s is not recognized on one edge, it will be recognized on the next edge.

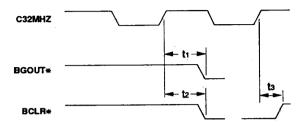

# Figure 10: VMEbus ARBITER TIMING

# a) VMEbus Arbiter Signals

# b) VMEbus Data Transfer Timeout

# c) Arbitration Timeout

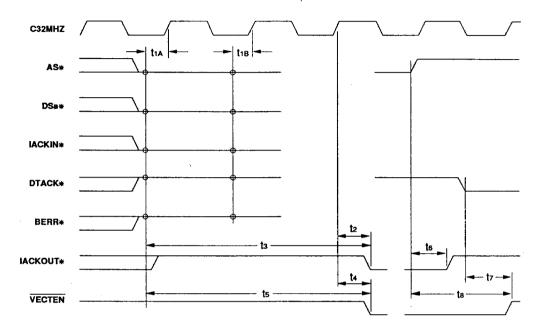

Table 12 : AC CHARACTERISTICS (VMEbus IACK DAISY CHAIN DRIVER TIMING) Commercial:  $T_A = 0^\circ$  to +70°C,  $V_{DD} = 5V \pm 5\%$ , Military  $T_A = -55^\circ$  to +125°C,  $V_{DD} = 5V \pm 10\%$

| İ               |                                            |      |     |     |     |      |

|-----------------|--------------------------------------------|------|-----|-----|-----|------|

| Symbol          | Description                                | Min  | Тур | Max |     | Unit |

|                 |                                            |      |     | Com | Mil | 1    |

| t <sub>IA</sub> | lack cycle start conditions setup (Note 1) | 10.0 | -   | -   | -   | ns   |

| t <sub>1B</sub> | lack cycle start conditions setup (Note 2) | 10.0 | -   | -   | -   | ns   |

| t <sub>2</sub>  | IACKOUT* low from C32MHZ high              | 4.8  | 12  | 23  | 28  | ins  |

| t <sub>3</sub>  | IACKOUT* from IACK* cycle start            | · 65 | 84  | 120 | 125 | ns   |

| t <sub>4</sub>  | VECTEN low from C32MHZ rising edge         | 6.2  | 15  | 30  | 37  | ns   |

| t <sub>s</sub>  | VECTEN low from lack cycle received        | 69   | 83  | 124 | 131 | ns   |

| t <sub>6</sub>  | IACKOUT* high from AS* high (Note 4)       | 2.1  | 6   | 12  | 14  | ns   |

| t <sub>7</sub>  | VECTEN high from DTACK* low                | 3.8  | 10  | 19  | 24  | ns   |

| t <sub>8</sub>  | VECTEN high from AS* high                  | 5.0  | 13  | 25  | 30  | ns   |

- lack cycle start conditions are: AS\* low, either DS1\* or DS0\* low, IACKIN\* low, DTACK\* high, and BERR\* high. If the setup

time is not met, the IACK\* cycle start may not be detected on C32MHZ clock edge shown, and would start on the next edge.

- 2. The lack cycle start conditions must remain valid on the subsequent edge for the cycle to continue being daisy chained. If the second sample is not valid, two new successive samples are required.

- 3. Addresses are only required when the ACC is generating an interrupt itself.

- 4. Applies to all types of lack cycles, including Auto-ID.

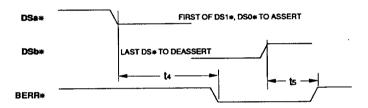

Figure 11: VMEbus IACK DAISY CHAIN DRIVER TIMING

Signal timing is the same for both ACC as SYSCON and not SYSCON in Slot 1. IACK is connected to IACK by the backplane.

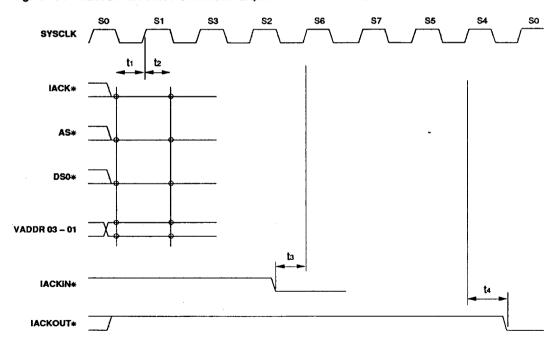

Table 13 : AC CHARACTERISTICS (VMEbus IACK DAISY CHAIN DRIVER, AUTO-ID CYCLES) Commercial:  $T_A = 0^\circ$  to +70°C,  $V_{DD} = 5V \pm 5\%$ , Military  $T_A = -55^\circ$  to +125°C,  $V_{DD} = 5V \pm 10\%$

| Symbol         | Description                                  | Min | Тур | Ma  | ax . | Unit |

|----------------|----------------------------------------------|-----|-----|-----|------|------|

|                |                                              |     | Com | Mil | 1    |      |

| t,             | lack cycle start conditions setup (Note 1)   | 10  | -   | -   | -    | ns   |

| t <sub>2</sub> | lack cycle start conditions hold (Note 1)    | -   |     | -   | -    | ns   |

| t <sub>3</sub> | IACKIN* setup to SYSCLK rising edge (Note 2) | -   | •   | • . | -    | ns   |

| t <sub>4</sub> | IACKOUT* low from SYSCLK rising edge         | 4.8 | 12  | 24  | 30   | ns   |

- If these conditions are not met, the Auto-ID counter may not start counting on this edge of SYSCLK. The protocol accommodates some modules beginning on a given edge, and others not until the subsequent edge.

- The module in slot 1 would meet this condition at the same time as condition 1; modules in other slots will wait in state S2 until, one after another, this condition is met. They will then move into S6, finally S4 and generate IACKOUT\*.

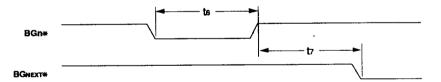

Figure 12: VMEbus IACK DAISY CHAIN DRIVER, AUTO-ID CYCLE TIMING

Table 14 : DC CHARACTERISTICS Commercial:  $T_A = 0^{\circ}$  to +70°C,  $V_{DO} = 5V \pm 5\%$ , Military  $T_A = -55^{\circ}$  to +125°C,  $V_{DD} = 5V \pm 10\%$

| Symbol            | Parameter                        | Test                              |          | Limits     |            | Unit |

|-------------------|----------------------------------|-----------------------------------|----------|------------|------------|------|

|                   |                                  | Conditions                        | Min      | Тур        | Max        |      |

| I <sub>BH</sub>   | Input HIGH Current               | V <sub>IN</sub> = V <sub>DD</sub> |          |            |            |      |

|                   | смоз эсн                         | 55                                |          | 1          | 10         | μА   |

|                   | ΠL                               |                                   |          | 1          | 10         | μА   |

|                   | TTL PD                           |                                   | 10       | 35         | 120        | μA   |

|                   | TTL PU                           |                                   |          |            | 40         | μА   |

|                   | TTL SCH                          |                                   |          | 1          | 10         | μΑ   |

| <br> L            | Input LOW Current                | V <sub>IN</sub> = V <sub>SS</sub> |          |            |            |      |

|                   | CMOS SCH                         | 55                                |          | <b>-</b> 1 | -10        | μA·  |

|                   | ΠL                               |                                   |          | -1         | -10        | μA   |

|                   | TTLPD                            |                                   |          |            | -40        | μА   |

|                   | TTL PU                           |                                   | -8       | -30        | -100       | μA   |

|                   | TTL SCH                          |                                   | -        | -1         | <b>-10</b> | μА   |

| loz               | Tri-state Output Leakage Current |                                   | -10      | ±1         | 10         | μА   |

| V <sub>HYST</sub> | Schmitt Trigger Hysteresis       |                                   | 1        |            |            |      |

|                   | CMOS SCH                         |                                   | 1.0      | 1.5        |            | V    |

|                   | TTL SCH                          |                                   |          | 0.7        |            | V    |

| V <sub>T+</sub>   | Positive-going Schmitt Threshold |                                   |          |            |            |      |

| ••                | CMOS SCH                         |                                   |          | 3.0        | 4.0        | V    |

|                   | TTL SCH                          |                                   |          | 1.7        | 2.0        | ٧    |

| V <sub>T</sub>    | Negative-going Schmitt Threshold |                                   |          |            |            |      |

| •-                | CMOS SCH                         |                                   | 1.0      | 1.5        |            | V    |

|                   | TTL SCH                          |                                   | 0.8      | 1.0        |            | V    |

| V <sub>IH</sub>   | Input HIGH voltage               |                                   | 1        |            | 1          |      |

|                   | TTL                              | 0° to +70°C                       | 2.0      |            |            | V    |

|                   | TTL PD                           | 0° to +70°C                       | 2.0      |            |            | ٧    |

|                   | TTL PU                           | 0° to +70°C                       | 2.0      |            |            | ٧    |

|                   | ΠL                               | -55° to +125°C                    | 2.25     |            |            | V    |

|                   | TTL PD                           | -55° to +125°C                    | 2.25     |            |            | V    |

|                   | TTL PU                           | -55° to +125°C                    | 2.25     |            |            | V    |

| V <sub>IL</sub>   | Input LOW Voltage                |                                   |          |            | 1          |      |

| ıL                | TπL                              |                                   |          |            | 0.8        | V    |

|                   | TTL PD                           |                                   |          | <u> </u>   | 0.8        | V    |

|                   | TTL PU                           |                                   | <u> </u> |            | 0.8        | V    |

Table 14: DC CHARACTERISTICS CON'T

| Symbol          | Parameter           | Test                      |          | Limits |     | Unit |

|-----------------|---------------------|---------------------------|----------|--------|-----|------|

|                 |                     | Conditions                | Min      | Тур    | Max |      |

| V <sup>OH</sup> | Voltage Output HIGH | 0° to +70°C               |          |        |     |      |

|                 | TP4                 | I <sub>OH</sub> = -4 mA   | 2.4      | 4.5    |     | V    |

|                 | TS6                 | I <sub>OH</sub> = -6 mA   | 2.4      | 4.5    |     | ٧    |

|                 | TP8                 | I <sub>OH</sub> = -8 mA   | 2.4      | 4.5    |     | ٧    |

|                 | TS8                 | I <sub>OH</sub> = -8 mA   | 2.4      | 4.5    |     | ٧    |

|                 | TP12                | I <sub>OH</sub> = -12 mA  | 2.4      | 4.5    |     | ٧    |

|                 | VTS64               | I <sub>OH</sub> = -22 mA  | 2.4      |        |     | ٧    |

| V <sub>OH</sub> | Voltage Output HIGH | -55° to 125°C             | 1        |        |     |      |

|                 | TP4                 | I <sub>OH</sub> = -3.2 mA | 2.4      | 4.5    |     | V    |

|                 | TS6                 | I <sub>OH</sub> = -4.8 mA | 2.4      | 4.5    |     | ٧    |

|                 | TP8                 | I <sub>OH</sub> = -6.4 mA | 2.4      | 4.5    |     | ٧    |

|                 | TS8                 | I <sub>OH</sub> = -6.4 mA | 2.4      | 4.5    |     | V    |

|                 | TP12                | I <sub>OH</sub> = -9.6 mA | 2.4      | 4.5    | ,   | ٧    |

|                 | VTS64               | I <sub>OH</sub> = -22 mA  | 2.4      |        |     | V    |

| V <sub>OL</sub> | Voltage Output LOW  | 0° to +70°C               | <b>†</b> |        |     |      |

| -               | TP4                 | I <sub>OL</sub> = 4 mA    |          | 0.2    | 0.4 | ٧    |

|                 | TS6 .               | I <sub>OL</sub> = 6 mA    |          | 0.2    | 0.4 | V    |

|                 | OĐ8                 | I <sub>OL</sub> = 8 mA    |          | 0.2    | 0.4 | V    |

|                 | TP8                 | I <sub>OL</sub> = 8 mA    |          | 0.2    | 0.4 | ·V   |

|                 | TS8                 | I <sub>OL</sub> = 8 mA    |          | 0.2    | 0.4 | ٧    |

|                 | TP12                | I <sub>OL</sub> = 12 mA   |          | 0.2    | 0.4 | V    |

|                 | VOD48               | I <sub>OL</sub> = 48 mA   |          |        | 0.6 | ٧    |

|                 | VTS64               | I <sub>OL</sub> = 64 mA   |          |        | 0.6 | V    |

| V <sub>OL</sub> | Voltage Output LOW  | -55° to 125°C             | 1        |        |     |      |

|                 | TP4                 | I <sub>OL</sub> = 3.2 mA  | 1        | 0.2    | 0.4 | V    |

|                 | TS6                 | I <sub>OL</sub> = 4.8 mA  |          | 0.2    | 0.4 | v    |

|                 | OD8                 | I <sub>OL</sub> = 6.4 mA  | 1        | 0.2    | 0.4 | V    |

|                 | TP8                 | I <sub>OL</sub> = 6.4 mA  | 1        | 0.2    | 0.4 | v    |

|                 | TS8                 | I <sub>OL</sub> = 6.4 mA  |          | 0.2    | 0.4 | ٧    |

|                 | TP12                | I <sub>OL</sub> = 9.6 mA  | 1        | 0.2    | 0.4 |      |

|                 | VOD48               | I <sub>OL</sub> = 48 mA   | <u> </u> |        | 0.6 | V    |

|                 | VTS64               | I <sub>OL</sub> = 64 mA   | <u> </u> |        | 0.6 |      |

Note that the type abbreviations used above have a number suffix which indicate the current rating. The letter prefixes are defined in the Terminology section, just before Table 3.

**Table 15: CAPACITIVE LOADING**

| Symbol          | Parameter                                            | Test<br>Conditions | Limits |      |     | Unit |

|-----------------|------------------------------------------------------|--------------------|--------|------|-----|------|

| 1               | c                                                    |                    | Min    | Тур  | Max |      |

| C <sub>IN</sub> | Input Pin Capacitance                                |                    |        | 10   | •   | ρF   |

| c <sup>ю</sup>  | Bi-directional Pin Capacitance<br>VOD48              |                    |        | 24   |     | pF   |

|                 | VTS64                                                |                    |        | 32   |     | pF   |

| Солт            | Output Pin Capacitance TP4, TS6, OD8, TP8, TS8, TP12 |                    |        | - 13 |     | pF   |

The nominal capacitive load under operating conditions for outputs driving local signals is 50pF; for outputs driving the VMEbus, the rated load is 500pF.

**Table 16: RECOMMENDED OPERATING CONDITIONS**

| DC Supply Voltage (V <sub>DD</sub> )                      | +4.5 V to +5.5 V |

|-----------------------------------------------------------|------------------|

| Power Dissipation (P <sub>DD</sub> )                      | 0.625 W          |

| Ambient Operating Temperature (T <sub>A</sub> Commercial) | 0° to +70°C      |

| Ambient Operating Temperature (T <sub>A</sub> Military)   | -55° to +125°C   |

The power dissipation figure is based on typical internal logic dissipation plus the worst case set of outputs simultaneously active with maximum rated loads.

Table 17: ABSOLUTE MAXIMUM RATINGS

| DC Supply Voltage (V <sub>DD</sub> )             | -0.3 to +7.0 V                 |

|--------------------------------------------------|--------------------------------|

| Input Voltage (V <sub>IN</sub> )                 | -0.3 to V <sub>DO</sub> +0.3 V |

| DC Input Current (I <sub>IN</sub> )              | -10 to +10 mA                  |

| Storage Temperature, ceramic (T <sub>STG</sub> ) | 65° to +150°C                  |

| Storage Temperature, plastic (T <sub>STG</sub> ) | -40° to +125°C                 |

Stresses beyond those listed above may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### **FUNCTIONAL DESCRIPTION**

#### Reset, Clocks, and Bl-mode™ Module

#### Reset

This module generates the local and VMEbus reset signals, clock signals of several different rates, and contains the local bus timer, tick timer, and watchdog timer. The BI-mode™ controller is also located in this module.

The ACC will assert the local reset (RESET) signal when any of the power-up reset (PWRRST), external reset (EXTRST), or VMEbus system reset (SYSRST\*) pins are asserted, or when software initiates a reset via a control register in the ACC.

Clocks: Inputs

The ACC requires two clocks for operation: a constant 32 MHz input to generate clocks of specific frequencies, and the CPU clock for sections that must be synchronous to the CPU. The  $1\mu S$ ,  $14\mu S$ , 8MHz and SYSCLK (16MHz) signals are exact, within the limits defined by the 32MHz input.

Clocks: Outputs

The ACC provides five clock outputs as described below:

| • 1µs       | General purpose                                     |

|-------------|-----------------------------------------------------|

| • 14μs      | General purpose (DRAM refresh clock); ±1 CPU clock  |

| • 14.34ms   | General purpose (14µs times 1024)                   |

| • 2.4615MHz | Baud clock for serial devices (32MHz divided by 13) |

| • 8MHz      | General purpose                                     |

| · SYSCLK    | SYSCLK for the VMEbus (16MHz)                       |

# Tick Clock, Watchdog timer, and Bus Time Out

The ACC provides a tick clock output which can be connected to any of the interrupt inputs and is programmable to one of 200µs, 400µs, 2ms, 4ms, 5ms, 10ms, 50ms or 100 ms. The tick defaults to 100ms. As well as a tick clock the ACC provides a watchdog timer. The watchdog timer, unless restarted, counts out two seconds and then asserts WDOG for 200 ms, then begins again. The WDOG output can be used for resetting the system or as a source for an interrupt. The local CPU is

capable of restarting the watchdog timer via a control bit in the ACC device. The watchdog timer, when used with software, provides a method of detecting when a CPU has stopped functioning. This feature is capable of being disabled via a input pin on the ACC (ENDOG).

The ACC also provides a Local Bus Time Out (LBTO) function. This function asserts the KBERR signal when the KDS signal has been asserted for 512µs. This provides a method for the CPU to recover if a bad address or device is accessed. This feature can be enabled or disabled under software control (defaults to enabled). The ACC sets a status bit when it asserts KBERR.

#### BI-mode™

BI-mode™ entry and exit is controlled by the ACC. The ACC asserts the BI-mode™ pin (BIMODE) on any of the following conditions: local reset, assertion of IRQ1\* (programmable), assertion of the SELFBI bit in the ACC device or assertion of BITRIG pin. The ACC will only exit BI-mode™ when the BIREL signal on the ACC is active and all BI-mode™ entry signals are negated.

#### Local Bus Requester/Arbiter

The local Bus Requester/Arbiter (LBRA) expands the bus request logic of the 68xxx to handle two sources of requests. The bus request for channel 1 can be programmed to have a higher priority then channel 0. This module receives the two requests from the external sources, obtains the bus from the CPU and passes the grant onto the highest priority device requesting the local bus. The LBRA module uses the standard three wire handshaking to the 68xxx on channel 1, and a modified protocol on channel 0 for the DARF.

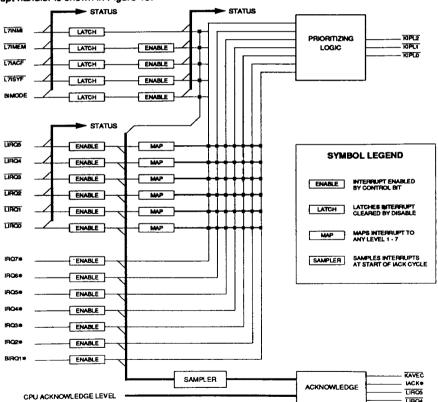

### Interrupt Handler

The interrupt handler module prioritizes interrupts from dedicated local level 7 sources, general purpose local sources, and the VMEbus. It generates acknowledge signals for the appropriate source when the CPU services an interrupt.

The module also allows each source to be individually enabled, each of the six general purpose sources to be mapped to any of the seven interrupt levels, and the status of any local interrupt to be read.

4

There are five level seven interrupt inputs of which only four can be disabled. The fifth level seven interrupt is a nonmaskable interrupt.

All of the local interrupt sources are auto-vectored interrupts except that interrupts four and five can be either vectored or auto-vectored. The ACC provides the lack signals for level four and five interrupts when they are programmed as vectored interrupts. The VMEbus interrupts are always handled as vectored interrupts. The priority of acknowledges when there are multiple interrupts on a level is autovectored first, local vectored, then VMEbus interrupts.

### **VMEbus Requester**

The VMEbus Requester obtains ownership of the VMEbus when requested, and can also request that the requesting device (the DARF) cease using the VMEbus when certain conditions exist, such as a Bus Clear or if the programmed ownership period has expired.

Several request and release modes are available and are programmable via the Requester Control Register in the ACC device. The ACC can be programmed to use any of the four VMEbus request levels.

The interrupt handler is shown in Figure 13.

FIgure 13: INTERRUPT HANDLER BLOCK DIAGRAM

#### Requester Modes

Two request modes are supported: FAIR and DEMAND.

#### FAIR Mode

In FAIR mode, the ACC does not request the VMEbus until the level that will be used for the request is inactive. This mode ensures that each VME master in a large multi-master VME system will obtain the VMEbus.

#### DEMAND Mode

In DEMAND mode, the ACC requests the VMEbus regardless of the current state of the VMEbus request lines. This method may prevent other cards on the same bus request level farther down the daisy chain from obtaining the VMEbus, but can be used if the VMEbus is urgently required by this card.

#### Release Modes

Four release modes are supported by the ACC: Release On Request (ROR), Release When Done (RWD), Release on Bus Clear (ROBCLR), and Release Ownership Timeout (ROTO). The ROR and RWD modes are mutually exclusive, while the ROBCLR and ROTO modes are independently enabled.

### Release On Request (ROR)

In ROR mode the ACC requests that the requesting device (eg: DARF) cease using the VMEbus when another VMEbus master asserts its request on the VMEbus. This prevents other VMEbus masters from being starved from the VMEbus, and allows the current VMEbus master to retain bus mastership if no other VMEbus master requires the VMEbus.

#### Release When Done (RWD)

In RWD mode the ACC gives up the VMEbus when the current cycle is complete. This avoids the *release* overhead of ROR mode.

### Release On Bus Clear (ROBCLR)

In ROBCLR mode the ACC requests that the requesting device cease using the VMEbus when the VMEbus Bus Clear (BCLR\*) signal is asserted on the VMEbus. The system controller asserts BCLR\* when a higher priority request is made while a lower priority request owns the VMEbus. This allows higher priority VMEbus masters to obtain the VMEbus from lower priority VMEbus masters.

### Release Ownership Timeout (ROTO)

In ROTO mode the ACC requests that the requesting device cease using the VMEbus after a programmable timeout has expired. The timer can be programmed for 2, 4, or 8 µs or disabled. This mode both limits the time the card owns the VMEbus and, by allowing the card to own the VMEbus for at least that time, it reduces the time spent re-arbitrating the VMEbus.

### **VMEbus System Controller Functions**

VMEbus System Controller functions are provided by the ACC when it is enabled as the System Controller. Internal circuitry detects whether the card is installed at the beginning of the bus grant daisy chain, normally slot 1, at reset and sets the SYSCON mode automatically. Software can also enable or disable the SYSCON mode. The functions that are provided by the ACC as systems controller are listed below:

- · Data Transfer Bus Programmable Timeout

- · 4 level programmable multi-mode arbiter with timeout

- · lack Daisy Chain Driver

- SYSCLK Generator

- SYSRST\* Driver

- · Off-card Status Bit Inputs and Reset Input

- SYSCON detection

The system controller functions remain available when the ACC is in BI-mode $^{\text{TM}}$ .

### Data Transfer Bus Programmable Timeout

The ACC provides a timeout circuit, to terminate VMEbus data transfers with bus error (BERR\*) signal if no slave responds within a programmed time. The timeout period can be 16, 32 or 64 μs, or *never*.

#### Four Level VMEbus Arbiter

The arbiter circuitry is enabled whenever the ACC is the system controller, and provides four programmable arbitration schemes along with arbitration timeout.

### Arbitration Modes

Four bus arbitration modes are available on the ACC. The arbitration modes are Full Priority, BR3 Priority, BR3,2 Priority and Round Robin Priority. These arbitration modes are software selectable via the ACC device.

#### Full Priority Mode

While the ACC is in Full Priority mode it issues a bus grant to the highest BR\* signal active and assert BCLR\* if a lower priority card is using the VMEbus. The priority of the bus request lines are BR3\* as the highest to BR0\* as the lowest.

#### **BR3** Priority

When the ACC is in BR3 Priority mode the BR3\* request has the highest priority and the BR2\*, BR1\*, and BR0\* are placed in round robin mode. BCLR\* is asserted due to assertion of BR3\*, if required.

### BR3, 2 Priority Mode

When the ACC is in BR3,2 Priority mode the BR3\*, and BR2\* requests are handled in Full Priority mode while BR1\* and BR0\* are in round robin mode. BCLR\* is asserted as required.

#### Round Robin Mode

When the ACC is in the round robin mode of arbitration, the priority of the request lines is BR3\* to BR0\*. Once a level has been given a grant a request, it becomes the lowest priority in the chain. For example if BR2\* is given a grant the new priority would be: BR3\*, BR1\*, BR0\*, BR2\*, BCLR\* is not asserted.

#### IACK Daisy Chain Driver

The IACK Daisy Chain Driver (DCD) circuitry participates in the interrupt acknowledge daisy chain, and either asserts IACKOUT\* to the next card on the VMEbus or asserts the VECTEN/ signal to the on-board logic. The VECTEN/ signal indicates to the on-board logic that current acknowledge cycle is for this card.

# SYSCLK Generator

The ACC provides a 16 MHZ 50% duty-cycle clock meeting IEEE 1014 when the device is the SYSCON.

#### SYSRST\* Driver

The SYSRST\* signal is capable of being driven by the ACC, whether it is the system controller or not. The SYSRST\* is asserted when PWRRST is asserted, or while BG0IN\* is asserted while the ACC is SYSCON. SYSRST\* can also be asserted via a control bit in the ACC regardless of whether the ACC is SYSCON or not. The BG0IN\* signal is used as the off-card reset input when the ACC is SYSCON.

### Off-Card Status Bit Inputs and Reset Input

The Bus Grant In pins of the card at the beginning of the bus grant daisy chain are not needed by the VMEbus, since the arbiter on that card can drive the local requester directly, instead of via the BGnIN\* pins. The use of the BGnIN\* pins when the ACC is the SYSCON controller are described below:

BG0IN\* Off-card reset input

BG1IN\* Status input

BG2IN\* Status input

BG3IN\* Used to determine if the card is the system

controller

#### SYSCON Detection

Determining if the card is the system controller is done at reset by sampling the BG3IN\* signal. If the card is positioned to the right of another card then the other card is driving the BG3IN\* signal inactive (high). If the card is at top of the arbitration chain (SLOT 1) then the BG3IN\* line is floating. A 10K $\Omega$  external pull-down resistor is required on the BG3IN\* signal for SYSCON detection to work. After reset the BG3IN\* signal is sampled and depending on the level the ACC can determine if it is the system controller or not.

#### **ACC REGISTERS**

The ACC has four address lines (KADDR 00 – KADDR 03) which are used to determine which register is accessed during a CPU access. The 68020/030 processors have an A0 address line last so the four address lines can be mapped directly to the ACC. However the 68000/010 processors do not have this A0 address line so the 68000/010 address lines should be mapped as shown in Table 18, to ensure interrupt acknowledge cycles work correctly.

The ACC registers are summarized in Tables 19 and 20, and more fully described in Tables 21 through 36.

Table 18: 68000/010 ADDRESS LINE MAP

| 68000/010 | ACC Address Line | 68020/030 |

|-----------|------------------|-----------|

| A4        | KADDR 00         | A0        |

| A1        | VADDR 01         | A1        |

| A2        | VADDR 02         | A2        |

| A3        | VADDR 03         | A3        |

Table 19: ACC Registers

| Number | Name   | Register Function                                  |

|--------|--------|----------------------------------------------------|

| F      | IC54   | Map and autovector bits for local interrupts 5 & 4 |

| E      | IC32   | Map bits for local interrupts 3 & 2                |

| D      | IC10   | Map bits for local interrupts 1 & 0                |

| С      | VIE    | Enable bits for VMEbus interrupts                  |

| В      | LIE    | Enable bits for local general interrupts           |

| A      | 71E    | Enable bits for dedicated level 7 interrupts       |

| 9      | LIS    | Status bits for local interrupts                   |

| 8      | 718    | Status bits for dedicated level 7 interrupts       |

| 7      | CTL2   | Control and status bits                            |

| 6      | ID     | Card ID from Auto-ID                               |

| 5      | VARB   | VMEbus Arbiter & Syscon control bits               |

| 4      | VREQ   | VMEbus Requester control bits                      |

| 3      | VINT   | VMEbus Interrupter control bits                    |

| 2      | GENCTL | General control bits                               |

| 1      | STAT1  | General status bits                                |

| 0      | STAT0  | General status bits                                |

Table 20: ACC REGISTER SUMMARY

| Name   | # | D7                             | D6                                 | D5                                         | . D4                                                        | D3                          | D2                               | D1                         | DO                                          |  |

|--------|---|--------------------------------|------------------------------------|--------------------------------------------|-------------------------------------------------------------|-----------------------------|----------------------------------|----------------------------|---------------------------------------------|--|

| IC54   | F | AVECIVECT                      | LII                                | RQ5 Interrupt L                            | .evel                                                       | AVECIVECT                   | LIF                              | Q4 Interrupt L             | .evel                                       |  |