**JANUARY 1993**

# CA95C68/18/09

# DES DATA CIPHERING PROCESSORS (DCP)

- Encrypts/Decrypts data using National Bureau of Standards Data Encryption Standard (DES)

- High speed, pin and function compatible version of industry standard AMD AM9568, AM9518 and VLSI VM009

- Supports four standard ciphering modes: Electronic Code Book (ECB), Cipher Block Chaining (CBC), as well as 1 and 8 bit Cipher Feedback (CFB)

- Data rates greater than 11 Mbytes per second (25 MHz) in ECB or CBC modes

- Three separate registers for encryption, decryption and master keys improve system security and throughput by eliminating the need to reload keys frequently

- Fully static CMOS, TTL I/O compatible device, operates at up to 25 MHz

- Low power consumption allows battery back-up of internal key registers

- Three separate programmable ports (master, slave and key data)

- Available in 44 pin PLCC and 40 pin PDIP packages

The Newbridge Microsystems CA95C58/18/09 DES Data Ciphering Processors (DCPs) implement the National Bureau of Standards Data Encryption Standard (DES), FIPS PUB 46(1-15-1977). The DCPs were designed to be used in a variety of environments where computer and communications security is essential.

The DCPs provide a high throughput rate (up to 11 Mbytes per second) using ECB or CBC modes of operation. The DCPs provide a unique 1 bit CFB mode as well as the standard 8 bit mode. Separate ports for key input, clear data and enciphered data enhance security for your application.

The system communicates with the DCP using commands entered in the Master Port or through auxiliary control lines. Once the DCP is set up, data can flow through at high speeds since input, output and ciphering activities are performed concurrently. External DMA control can easily be used to enhance throughput in many system configurations.

The CA95C68 is designed to interface directly to the iAPX86, 88 CPU bus, and with a minimum of external logic, to the 2900 and 8051 families of processors. The CA95C18 is designed to interface directly with Z8000, 68000 type bus interfaces.

The CA95C09 may be configured to behave as either the CA95C68 or the CA95C18 (see OPTION pin in Table 1), the only difference being the order of the signal names on the device package.

### **Table of Contents**

| CA95C68/18/09 Block Diagrams                               |      |

|------------------------------------------------------------|------|

| Table 1 : CA95C68/18/09 Data Transfer Rates                | 2    |

| Packages                                                   | 3    |

| Pin Description                                            | 4    |

| AC Characteristics                                         |      |

| Figure 7: CA95C68/18 Clock and Reset Timing                | 16   |

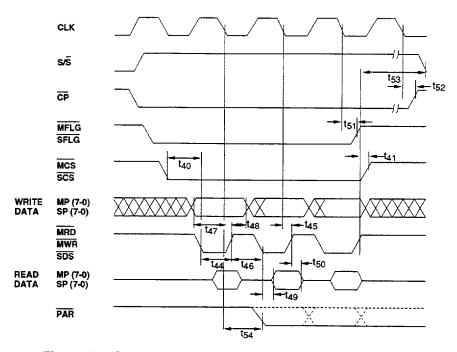

| Figure 8 : CA95C68/18 Control and Status Signals Timing    |      |

|                                                            | . 16 |

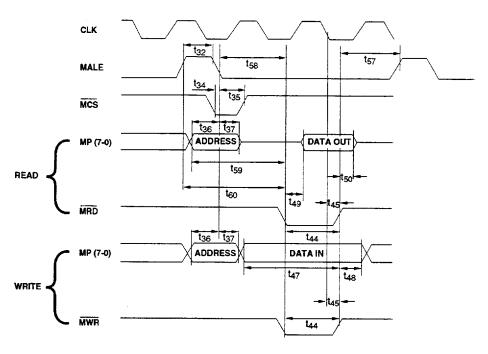

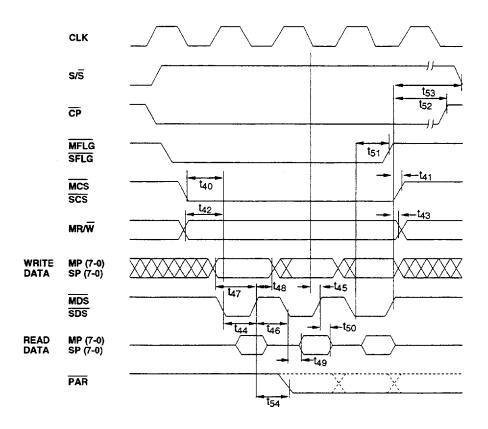

| Figure 9 : CA95C68 Master Port, Multiplexed Control Mode   |      |

| Read/Write Timing                                          | . 17 |

| Figure 10: CA95C68 Master (Slave) Port Read/Write Timing   | . 17 |

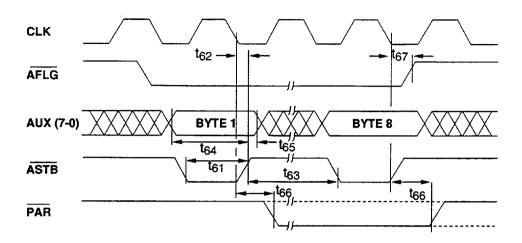

| Figure 11 : CA95C68 and CA95C18 Auxiliary-Port Key         |      |

| Entry Timing                                               | 18   |

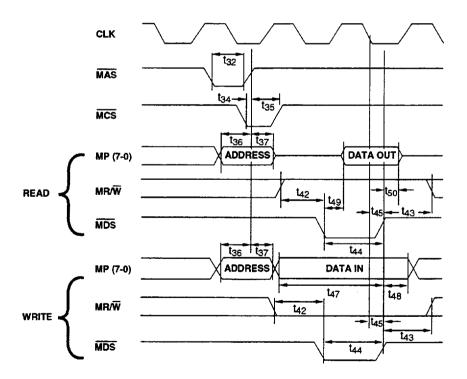

| Figure 12: CA95C18 Master Port, Multiplexed Control Mode,  |      |

| Read/Write Timing                                          |      |

| Figure 13: CA95C18 Master (Slave) Port Read/Write Timing   | . 19 |

| DC Characteristics                                         |      |

| Table 5 : Recommended Operating Conditions                 | .20  |

| Table 6 : Absolute Maximum Ratings                         |      |

| Functional Description                                     | .21  |

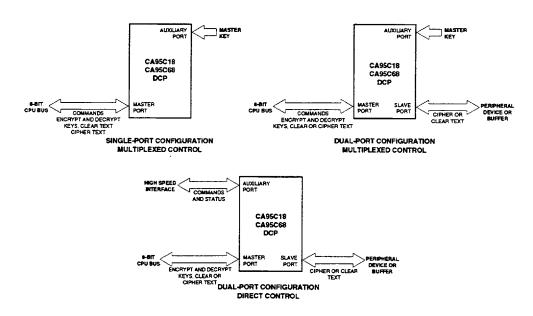

| Figure 14: CA95C68 and CA95C18 Data Flow Options           | .23  |

| Register Description                                       | .24  |

| Table 7 : Master Port Register Address                     | .24  |

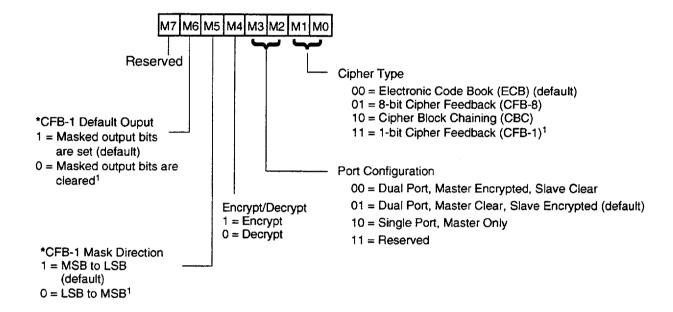

| Figure 15 : Mode Register Bit Assignments                  | .25  |

| Table 8 : Command Codes in Multiplexed Control Mode        |      |

| Table 9 : Implicit Command Sequences in Direct             |      |

| Control Mode                                               | .26  |

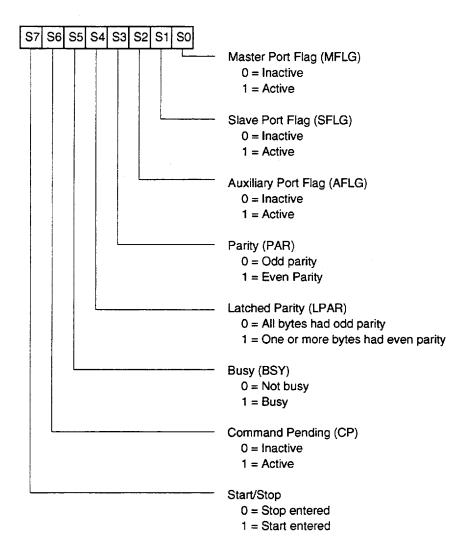

| Figure 16 : Status Register Bit Assignments                | .27  |

| Table 10: Association of Master Port Flag (MFLG) and Slave |      |

| Port Flag ( SFLG) with Input and Output Registers          | .28  |

| Maximum Throughput                                         |      |

| Pipelining                                                 |      |

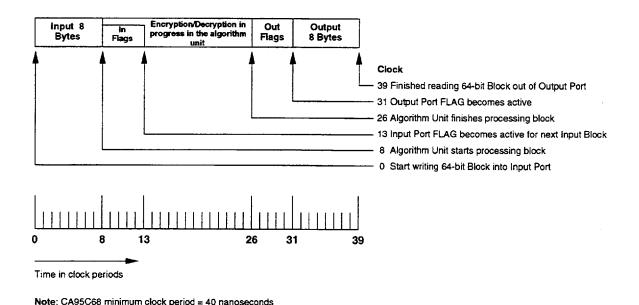

| Figure 17 : Detailed Timing of One Block                   | 29   |

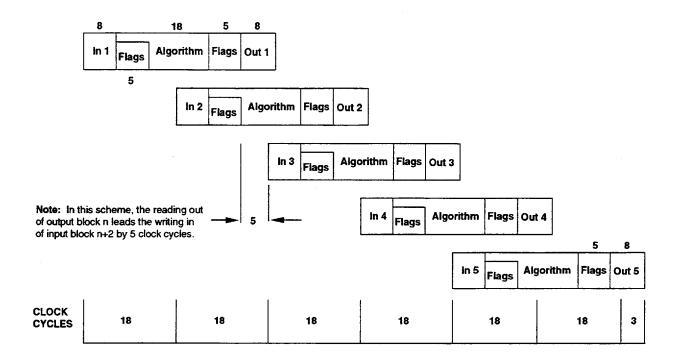

| Figure 18: Pipelining (Minimum Timing Operation)           | .30  |

| Command Description                                        |      |

| Mechanicals                                                |      |

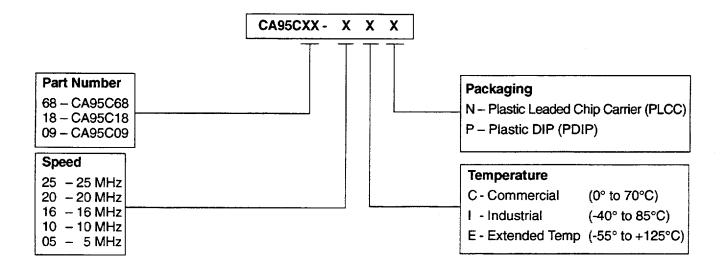

| Ordering Information                                       |      |

|                                                            |      |

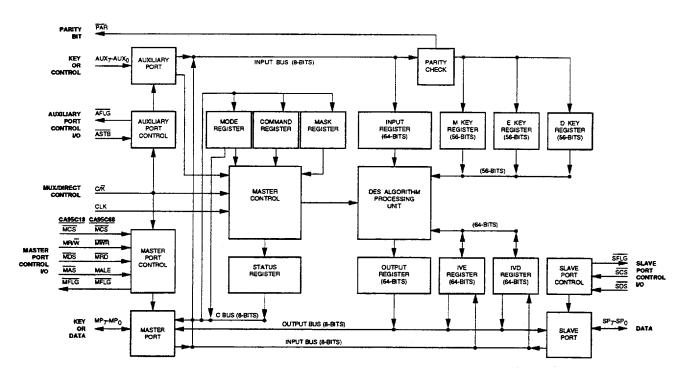

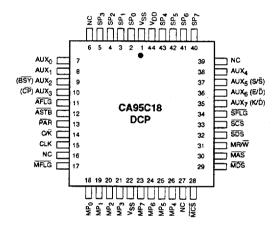

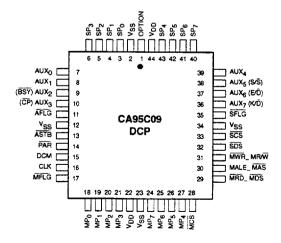

Figure 1: CA95C68/18/09 Block Diagrams

Table 1: CA95C68/18/09 Data Transfer Rates

| Product<br>Code | Data Transfer Rates ECB or CBC Mode (Mbytes per second) | System Clock<br>(MHz) |

|-----------------|---------------------------------------------------------|-----------------------|

| CA95Cxx - 5     | 2.22                                                    | 5                     |

| CA95Cxx - 10    | 4.44                                                    | 10                    |

| CA95Cxx - 16    | 7.10                                                    | 16                    |

| CA95Cxx - 20    | 8.88                                                    | 20                    |

| CA95Cxx - 25    | 11.10                                                   | 25                    |

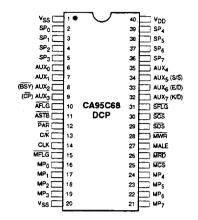

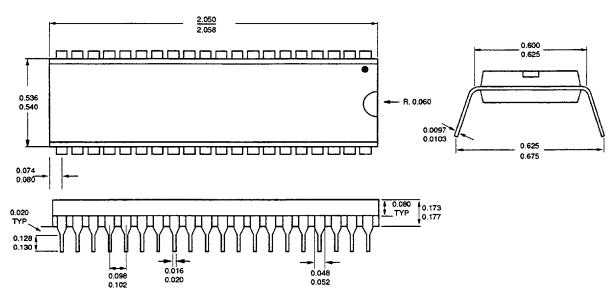

Figure 2: CA95C68 40-Pin PDIP

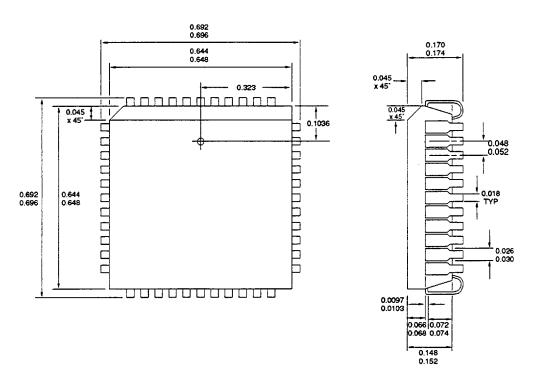

Figure 3: CA95C68 44-Pin PLCC

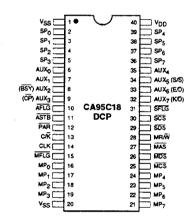

Figure 4: CA95C18 40-Pin PDIP

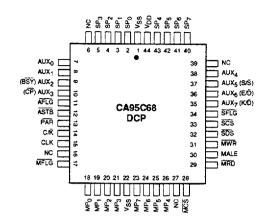

Figure 5: CA95C18 44-Pin PLCC

Figure 6: CA95C09 44-Pin PLCC

Table 2 : Pin Description

| Symbol                             | Pi<br>PLC      |                | Pin<br>PDIP    | TYPE | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|------------------------------------|----------------|----------------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                    | 95C68/18       | 95C09          | PUIF           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| CLK                                | 15             | 16             | 14             | I    | Clock: An external timing source is input via this pin. The Master and Slave Port data strobe signals (MWR, MRD, SDS for CA95C68 and MDS, SDS for CA95C18) must change synchronously with the clock input. In direct control mode the AUX <sub>5</sub> -S/S must also be synchronous. The output flags for the three ports (AFLG, MFLG, SFLG) will all change synchronously with the clock.                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| C/K                                | 14             | _              | 13             | ı    | Control/Key Mode Control: This input controls the mode of operation of the DCP. The DCP enters into Multiplexed Control Mode when a low input is placed on the C/K pin, enabling programmed access to internal registers through the Master Port and enabling input of keys through the Auxiliary Port. In Direct Control Mode (C/K HIGH), several of the Auxiliary Port pins become direct control/status signals which can be driven/sensed by high-speed controller logic, and access to internal registers through the Master Port is limited to the Input and Output Registers.                                                                                                                                            |  |  |  |  |  |

| DCM                                | _              | 15             | -              | ı    | <b>Direct Control Mode</b> : ( <b>For CA95C09</b> ) This input functions identical to the C/K input. (See C/K pin description).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| MP <sub>7</sub><br>MP <sub>0</sub> | 23-26<br>21-18 | 24-27<br>21-18 | 21-24<br>19-16 | I/O  | Master Port Bus: These eight bi-directional signals are used to input and output data, as well as specify the internal register addresses in Multiplexed Control Mode. The Master Port provides software access to the Status, Command, Mode, Mask, Input and Output Registers. For the CA95C68, the tri-state Master Port outputs will be enabled only when the Master Port is selected by Master Port Chip Select (MCS) LOW, and when Master Port Read (MRD) is strobed LOW. For the CA95C18, the Master Port outputs are enabled when selected by MCS, and when MR/W is HIGH and MDS is LOW. MP <sub>0</sub> is the low-order bit. Data and key information are entered into this port with the most significant byte first. |  |  |  |  |  |

| MCS                                | 28             | 28             | 25             | ı    | Master Port Chip Select: This active LOW input signal is used to select the Master Port. In Multiplexed Control Mode (C/K LOW), the level on MCS is latched internally on the falling edge of Master Port Address Latch Enable (MALE). This latched level is maintained as long as MALE is LOW; when MALE is HIGH, the latch becomes transparent and the internal signal will follow the MCS input. No latching of MCS occurs in Direct Control Mode (C/K HIGH). The level on MCS is passed directly to the internal select circuitry regardless of the state of Master Port Address Latch Enable (MALE).                                                                                                                       |  |  |  |  |  |

Newbridge Microsystems

January, 1993

CA95C68/18/09

Table 2 : Pin Description<sup>Cont'd</sup>

| Symbol | Pi<br>PL0 |              | Pin<br>PDIP | TYPE | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|--------|-----------|--------------|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|        | 95C68/18  | 95C09        | FDIF        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| MALE   | 30        | <del>-</del> | 27          | 1    | Master Port Address Latch Enable: (For CA95C68) In Multiplexed Control Mode (C/ $\overline{K}$ LOW), an active HIGH signal on this pin indicates the presence of valid address and chip select information at the Master Port. This information will be latched internally on the falling edge of MALE. When C/ $\overline{K}$ is HIGH (Direct Control Mode), MALE has no affect on DCP operation.                                             |  |  |  |  |  |

| MRD    | 29        | _            | 26          | ı    | Master Port Read: (For CA95C68) This active LOW input is used with valid MCS to indicate that data is to be output on the Master Port by Master Port Read (MRD) and Master Port Write (MWR) are normal mutually exclusive; if both become active simultaneously, the DCP is resto ECB Mode and all flags go inactive.                                                                                                                          |  |  |  |  |  |

| MWR    | 31        | -            | 28          | I    | Master Port Write: (For CA95C68) This active low input signal indicates to the DCP that valid data is present on MP <sub>7</sub> -MP <sub>0</sub> for an input operation. The rising edge of MWR latches the data into the selected internal register. If MWR and MRD both go LOW simultaneously, the DCP is reset.                                                                                                                            |  |  |  |  |  |

| MAS    | 30        | <del>-</del> | 27          | l    | Master Port Address Strobe: (For CA95C18) In Multiplexed Control Mode (C/K HIGH), a LOW on MAS indicates the presence of a valid chip select signal and address information. This information will be latched on the rising edge of MAS. In Direct Control Mode, MAS has no affect on the DCP operation. The DCP will be reset if MAS and MDS both go low simultaneously.                                                                      |  |  |  |  |  |

| MDS    | 29        | _            | 26          | I    | Master Port Data Strobe: (For CA95C18) This active low input is used in conjunction with a valid Master Port Chip Select (MCS) to indicate that valid data is present on the MP <sub>7</sub> -MP <sub>0</sub> bus for an input operation or that data is to be placed on the Master Port Bus during output. MDS and MAS are mutually exclusive; if they both go active simultaneously, the DCP is reset to ECB mode and all flags go inactive. |  |  |  |  |  |

| MR/W   | 31        | _            | 28          | 1    | Master Port Read/Write: (For CA95C18) This input signal indicates to the DCP whether the current Master Port operation is a read (HIGH) where data is transferred from the device, or a write (LOW) where data is stored to an internal register. MR/W is not latched internally and must be held stable while MDS is LOW.                                                                                                                     |  |  |  |  |  |

Table 2 : Pin Description<sup>Cont'd</sup>

| Symbol                           | Pi<br>PL0    |              | Pin<br>PDIP  | TYPE | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|----------------------------------|--------------|--------------|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                  | 95C68/18     | 95C09        | PUIP         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| MRD_<br>MDS                      | 29           | _            | _            | ı    | Master Port Read or Master Port Data Strobe: (For CA95C09) When the OPTION pin is HIGH this input functions as MRD. When the OPTION pin is LOW this input functions as MDS. (See appropriate pin description).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| MALE_<br>MAS                     | 30           | _            | -            | I    | Master Port Address Latch Enable or Master Port Address Strob (For CA95C09) When the OPTION pin is HIGH this input functions and MALE and when OPTION is LOW it functions as MAS. (See that appropriate pin description).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| MWR_<br>MR/W                     | 31           | _            | _            | 1    | Master Port Write or Master Port Read/Write: (For CA95C09) When the OPTION pin is HIGH this input functions as MWR and when OPTION is LOW it functions as MR/W. (See the appropriate pin description).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| MFLG                             | 17           | 17           | 15           | 0    | Master Port Flag: This active LOW flag indicates the need for a data transfer into or out of the Master Port during normal ciphering operation. The Master Port will be associated with either the Input or Output Register depending upon the setting of the control bits in the Mode Register (See Register Description).  If data is to be transferred through the Master Port to the Input Register, then MFLG reflects the contents of the Input Register. After any Start command is entered, MFLG will go active (LOW) whenever the Input Register is not full. MFLG is forced HIGH by any command other than a Start. Conversely, if the Master Port is associated with the Output Register, MFLG reflects the contents of the Output Register (except in Single Port configuration; see Functional Description). Whenever the Output Register is not empty MFLG will be active (LOW). In Single Port Mode of operation, the Master Port Flag reflects the contents of the Input Register, while the Slave Port Flag (SFLG, see below) is associated with the Output Register. |  |  |  |

| SP <sub>7</sub> -SP <sub>0</sub> | 40-43<br>5-2 | 40-43<br>6-3 | 36-39<br>5-2 | I/O  | Slave Port Bus: This 8 bit bi-directional data bus provides a second input/output interface to the DCP, allowing overlapped input, ciphering and output operations. The tri-state Slave Port will be accessed only when the Mode Register is configured for Dual Port operation, Slave Port Chip Select (SCS) and Slave Port Data Strobe (SDS) are both LOW and SFLG=0. Data entered or retrieved through this port is the most significant byte in/out first (SP <sub>7</sub> is the most significant bit).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| SCS                              | 33           | 33           | 30           | ı    | Slave Port Chip Select: This active LOW signal is logically combined with the Slave Port Data Strobe (SDS) to facilitate Slave Port data transfers in a bus environment. SCS is not latched internally, and may be tied permanently LOW without impairing Slave Port operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| SDS                              | 32           | 32           | 29           | I    | <b>Slave Port Data Strobe</b> : This active LOW input, in conjunction with Slave Port Chip Select (SCS) LOW indicates to the DCP that valid data is on the $SP_{\mathcal{T}}SP_0$ lines for an input operation, or that data is to be driven onto $SP_{\mathcal{T}}SP_0$ lines for output. The direction of data flow is determined by control bits in the Mode Register. (See Register Description).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

Newbridge Microsystems

January, 1993

CA95C68/18/09

Table 2 : Pin Description<sup>Cont'd</sup>

| Symbol                                 | Pi<br>PL0     |               | Pin          | TYPE | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------|---------------|---------------|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | 95C68/18      | 95C09         | PUIP         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SFLG                                   | 34            | 35            | 31           | 0    | Slave Port Flag: This active LOW output indicates the state of either the Input Register or the Output Register, depending on the Mode Register configuration. In Single Port Configuration, SFLG will go active whenever the Output Register is not empty during normal processing. In Dual Port Configuration, SFLG will reflect the content of whichever register is associated with the Slave Port. If the Input Register is assigned to the Slave Port, SFLG will go active whenever the Input Register is not full, once any of the Start commands has been entered; SFLG will be forced inactive if any other command is entered. Conversely, if the Slave Port is assigned to the Output Register, SFLG will go active whenever the Output Register is not empty.                                                                                                                                                                                                                                                                   |

| AUX <sub>7</sub> –<br>AUX <sub>0</sub> | 35-38<br>10-7 | 36-39<br>10-7 | 32-35<br>9-6 | I/O  | Auxiliary Port Bus: In Multiplexed Control Mode (C/ $\overline{K}$ LOW), these eight lines form a key byte input port which may be used to enter the Master and Session Keys. The Master Key can only be entered through this port but Session Keys may alternatively be entered via the Master Port. AUX $_0$ is the low-order bit, and is considered to be the parity bit in key bytes. The most significant byte of the key is entered first. When the DCP is operated in Direct Control Mode, (C/ $\overline{K}$ HIGH), the Auxiliary Port's key-entry function is disabled and five of the eight lines become direct control/status lines for interfacing to high-speed microprogrammed controllers. In this case, AUX $_0$ , AUX $_1$ and AUX $_4$ have no function (they may be tied HIGH) and the other pins are defined on the following pages.                                                                                                                                                                                    |

| AUX <sub>5</sub> –<br>S/S              | 37            | 38            | 34           | I    | <b>Start/Stop</b> : In Direct Control Mode, when this pin goes LOW (Stop) the DCP will follow the sequence that would normally occur when a Stop Command is entered. Conversely, when this input goes HIGH, a sequence equivalent to a Start Encryption or Start Decryption command will be followed. At the time AUX <sub>5</sub> -S/S goes HIGH, the level on AUX <sub>6</sub> -E/D selects either the Start Encryption or Start Decryption ciphering operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AUX <sub>6</sub> –<br>E/D              | 36            | 37            | 33           | I    | <b>Encrypt/Decrypt</b> : In Direct Control Mode, this input specifies whether the ciphering algorithm is to encrypt (E/ $\overline{D}$ HIGH) or decrypt (E/ $\overline{D}$ LOW) when AUX <sub>5</sub> -S/ $\overline{S}$ goes HIGH to initiate a normal data ciphering operation. When AUX <sub>7</sub> -K/ $\overline{D}$ goes HIGH, initiating entry of key bytes, the level on AUX <sub>6</sub> -E/ $\overline{D}$ specifies whether the bytes are to be written into the E Key Register (E/ $\overline{D}$ HIGH) or the D Key Register (E/ $\overline{D}$ LOW). The AUX <sub>6</sub> -E/ $\overline{D}$ input is not latched internally, and must be held constant whenever one or more of AUX <sub>5</sub> -S/ $\overline{S}$ , AUX <sub>7</sub> -K/ $\overline{D}$ , AUX <sub>2</sub> - $\overline{BSY}$ , or AUX <sub>3</sub> - $\overline{CP}$ are active. Corrupted data in the internal registers will occur if the proper level on AUX <sub>6</sub> -E/ $\overline{D}$ is not maintained during loading or ciphering operations. |

CA95C68/18/09

January, 1993

Newbridge Microsystems

Table 2 : Pin Description<sup>Cont'd</sup>

| Symbol                    | Pi<br>PL |       | Pin<br>PDIP | TYPE | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|---------------------------|----------|-------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                           | 95C68/18 | 95C09 | PUIP        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AUX7 –<br>K/D             | 35       | 36    | 32          | 1    | <b>Key/Data</b> : In Direct Control Mode, when this signal goes HIGH, the DCP initiates a key-data input sequence as if a Clear E (or D) Key through the Master Port command had been entered. The level on AUX <sub>6</sub> -E/D will determine whether the subsequently entered clear-key bytes are written into the E Key Register (E/D HIGH) or the D Key Register (E/D LOW). AUX <sub>7</sub> -K/D and AUX <sub>5</sub> -S/S are mutually exclusive control lines. When one goes active HIGH, the other must be inactive (LOW) and remain in this state until the first signal returns to an inactive state. Whenever a transition occurs on C/K (switching between Direct Control Mode and Multiplexed Control Mode) both of these signals must be inactive (LOW). |  |  |  |  |  |

| AUX <sub>2</sub> –<br>BSY | 9        | 9     | 8           | 0    | <b>Busy</b> : In Direct Control Mode, this active LOW status output gives a hardware indication that BSY the ciphering algorithm is in operation. This status line is driven by the BSY bit in the Status Register, such that when the BSY bit is "1" (active), AUX <sub>2</sub> -BSY is LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| AUX <sub>3</sub> –<br>CP  | 10       | 10    | 9           | 0    | <b>Command Pending</b> : In Direct Control Mode, this active LOW status output gives a hardware indication that the DCP is ready to accept input of key bytes following a LOW-to-HIGH transition on $AUX_7$ -K/ $\overline{D}$ . This signal line is driven by the $\overline{CP}$ bit in the Status Register, such that when the $\overline{CP}$ bit is "1" (active), $AUX_3$ - $\overline{CP}$ is LOW.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| ASTB                      | 12       | 13    | 11          | I    | Auxiliary Port Strobe: The rising edge of ASTB strobes the key-data on pins AUX <sub>7</sub> -AUX <sub>0</sub> into the appropriate internal key register in Multiplexed Control Mode (C/K LOW). This input is ignored unless AFLG and C/K are both LOW. One byte of key-data (most significant byte first) is entered on each ASTB.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

Table 2 : Pin Description<sup>Cont'd</sup>

| Symbol          |          | Pin<br>PLCC Pin<br>PDIP TYPE |       | TYPE | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|----------|------------------------------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | 95C68/18 | 95C09                        | PUIP  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ĀFLG            | 11       | 11                           | 10    | 0    | <b>Auxiliary Port Flag:</b> This active LOW output signal indicates that the DCP is expecting key-data to be entered on the Auxiliary Port Bus. This can occur only when $C/\overline{K}$ is LOW (Multiplexed Control $\underline{\text{Mode}}$ ) and a Load Key Through AUX Port command has been entered. $\overline{\text{AFLG}}$ will remain active (LOW) during input of all eight bytes, and will go inactive with the falling edge of the eighth $\overline{\text{ASTB}}$ .                                                                                                                                                                |

| PAR             | 13       | 14                           | 12    | 0    | Parity: The DCP checks all key bytes for correct (odd) parity as they are entered through either the Master Port (Multiplexed or Direct Control Mode) or the Auxiliary Port (Multiplexed Control Mode only). If any key byte contains even parity, the PAR bit in the Status Register is set to a "1" and PAR goes active (LOW). (See Parity Checking of Keys.). The parity bit is the least significant bit of the key byte.                                                                                                                                                                                                                     |

| OPTION          |          | 1                            | _     | 1    | Option: (For CA95C09) This input allows the user to configure the Master Port Control interface to function as either a CA95C68 or a CA95C18. When the OPTION pin is tied to $V_{DD}$ , the device will function with the interface of a CA95C68. Conversely, tying the OPTION pin to $V_{SS}$ will cause the DCP to function as a CA95C18. This OPTION pin must be tied to either $V_{SS}$ or $V_{DD}$ , or erratic operation of the device will occur. The CA95C09 DCP will perform identically to the CA95C68 or the CA95C18 (depending on the OPTION pin) with the only difference being the order of the signal names on the device package. |

| V <sub>DD</sub> | 44       | 44,22                        | 40    | PWR  | Power Supply: +5 Volts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>SS</sub> | 1, 22    | 2, 12<br>23, 34              | 1, 20 | GND  | Ground: 0 Volts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Table 3a : AC Characteristics ( $T_A = 0$  to  $70^{\circ}$ C,  $V_{DD} = +5.0V \pm 10\%$ ,  $V_{SS} = 0V$ )

| Number          | Description                                                                                                                |

|-----------------|----------------------------------------------------------------------------------------------------------------------------|

| Clock           |                                                                                                                            |

| t <sub>1</sub>  | CLK Width HIGH (t <sub>WH</sub> )                                                                                          |

| t <sub>2</sub>  | CLK Width LOW (t <sub>WL</sub> )                                                                                           |

| t <sub>3</sub>  | CLK HIGH to Next Clock HIGH (Clock Cycle, t <sub>C</sub> )                                                                 |

| Reset           |                                                                                                                            |

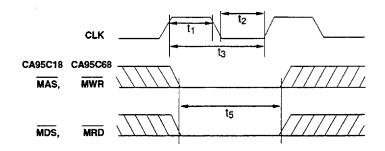

| t <sub>5</sub>  | MRD • MWR LOW to MRD • MWR HIGH (Reset Pulse Width), (Note 11)                                                             |

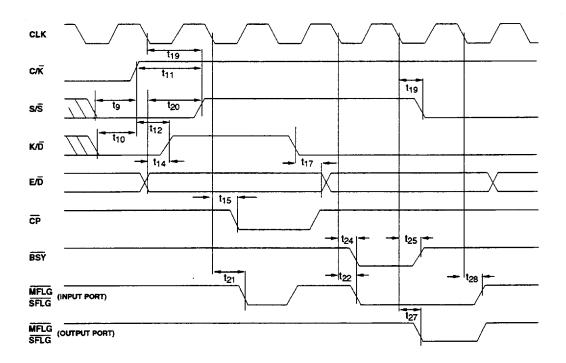

| Direct Conti    | rol Mode                                                                                                                   |

| t <sub>9</sub>  | S/S LOW to C/K HIGH (Setup), (Note 11)                                                                                     |

| t <sub>10</sub> | K/D LOW to C/K HIGH (Setup), (Note 11)                                                                                     |

| t <sub>11</sub> | C/K HIGH to S/S HIGH (Note 11)                                                                                             |

| t <sub>12</sub> | C/K HIGH to K/D HIGH (Note 11)                                                                                             |

| t <sub>14</sub> | E/D VALID to K/D HIGH (Setup) (Note 11)                                                                                    |

| t <sub>15</sub> | K/D HIGH • CLK ↓ to CP LOW                                                                                                 |

| t <sub>17</sub> | K/D LOW to E/D INVALID (Hold), (Note 11)                                                                                   |

| t <sub>19</sub> | CLK LOW to S/S VALID (Note 10)                                                                                             |

| t <sub>20</sub> | E/D VALID to S/S HIGH (Setup), (Note 11)                                                                                   |

| t <sub>21</sub> | S/S HIGH • CLK ↓ to MFLG (SFLG) LOW (Port Input Flag)                                                                      |

| t <sub>22</sub> | CLK LOW to MFLG (SFLG) LOW (Port Input Flag) (Note 2)                                                                      |

| t <sub>24</sub> | CLK LOW to BSY LOW                                                                                                         |

| t <sub>25</sub> | CLK LOW to BSY HIGH                                                                                                        |

| t <sub>27</sub> | CLK LOW to MFLG (SFLG) LOW (Port Output Flag)                                                                              |

| t <sub>28</sub> | S/S LOW • CLK ↓ to MFLG (SFLG) HIGH (Port Input Flag), (Note 3)                                                            |

| Multiplexed     | Control Mode - Master Port                                                                                                 |

| t <sub>32</sub> | For CA95C68: MALE Width (HIGH) For CA95C18: MAS Width (LOW)                                                                |

| t <sub>34</sub> | For CA95C68: MCS LOW to MALE LOW (Setup) For CA95C18: MCS LOW to MAS HIGH (Setup)                                          |

| t <sub>35</sub> | For CA95C68: MALE LOW to MCS HIGH (Hold) For CA95C18: MAS HIGH to MCS HIGH (Hold)                                          |

| t <sub>36</sub> | For CA95C68: Address INVALID to MALE LOW (Address Setup Time For CA95C18: Address INVALID to MAS HIGH (Address Setup Time) |

| t <sub>37</sub> | For CA95C68: MALE LOW to Address INVALID (Address Hold Time) For CA95C18: MAS HIGH to Address INVALID (Address Hold Time)  |

Table 3b : AC Characteristics (T<sub>A</sub> = 0 to 70°C,  $V_{DD}$  = +5.0V  $\pm 10\%$ ,  $V_{SS}$  = 0V)

| Manakan         | 5 MHz           | Limits                                | 10 MHz          | z Limits        | 16 MHz          | Limits          | 20 MHz          | Limits          | 25 MHz          | Limits          | I Imita  |

|-----------------|-----------------|---------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------|

| Number          | Min             | Max                                   | Min             | Max             | Min             | Max             | Min             | Max             | Min             | Max             | Units    |

| Clock           |                 |                                       |                 |                 |                 |                 |                 | •               |                 |                 |          |

| t <sub>1</sub>  | 85              | <u> </u>                              | 40              | _               | 27              | <del>-</del>    | 20              | _               | 17              | _               | ns       |

| t <sub>2</sub>  | 85              |                                       | 40              | _               | 27              | -               | 20              | -               | 17              | _               | ns       |

| t <sub>3</sub>  | 200             | _                                     | 100             | _               | 62.5            | -               | 50              | -               | 40              | -               | ns       |

| Reset           | 1               |                                       |                 |                 |                 | ·•              |                 | ·               |                 |                 |          |

| t <sub>5</sub>  | t <sub>C</sub>  | _                                     | t <sub>C</sub>  | _               | t <sub>C</sub>  | -               | tc              | -               | tc              | -               | ns       |

| Direct Contro   | ol Mode         | · · · · · · · · · · · · · · · · · · · | •               |                 |                 |                 |                 |                 |                 |                 |          |

| tg              | t <sub>C</sub>  | _                                     | t <sub>C</sub>  | _               | t <sub>C</sub>  | -               | t <sub>C</sub>  | -               | t <sub>C</sub>  | -               | ns       |

| t <sub>10</sub> | t <sub>C</sub>  | -                                     | t <sub>C</sub>  | _               | t <sub>C</sub>  |                 | t <sub>C</sub>  | -               | t <sub>C</sub>  | -               | ns       |

| t <sub>11</sub> | 2t <sub>C</sub> | -                                     | 2t <sub>C</sub> | -               | 2t <sub>C</sub> |                 | 2t <sub>C</sub> | -               | 2t <sub>C</sub> | _               | ns       |

| t <sub>12</sub> | 2t <sub>C</sub> | -                                     | 2t <sub>C</sub> | -               | 2t <sub>C</sub> | _               | 2t <sub>C</sub> | -               | 2t <sub>C</sub> | -               | ns       |

| t <sub>14</sub> | t <sub>C</sub>  | -                                     | tc              | -               | t <sub>C</sub>  | _               | t <sub>C</sub>  | -               | t <sub>C</sub>  | -               | ns       |

| t <sub>15</sub> | -               | 75                                    | _               | 50              | -               | 25              | _               | 20              | _               | 15              | ns       |

| t <sub>17</sub> | t <sub>C</sub>  | _                                     | tc              | -               | t <sub>C</sub>  | -               | t <sub>C</sub>  | -               | t <sub>C</sub>  | _               | ns       |

| t <sub>19</sub> | 0               | t <sub>WL</sub>                       | 0               | t <sub>WL</sub> | 0               | t <sub>WL</sub> | 0               | t <sub>WL</sub> | 0               | t <sub>WL</sub> | ns       |

| t <sub>20</sub> | t <sub>C</sub>  | _                                     | t <sub>C</sub>  | -               | t <sub>C</sub>  | -               | t <sub>C</sub>  | -               | t <sub>C</sub>  | _               | ns       |

| t <sub>21</sub> | <del>-</del>    | 75                                    | _               | 50              | _               | 25              | -               | 20              | -               | 15              | ns       |

| t <sub>22</sub> | <u> </u>        | 75                                    | -               | 50              | _               | 25              |                 | 20              | _               | 15              | ns       |

| t <sub>24</sub> | -               | 75                                    | -               | 50              | _               | 25              | _               | 20              | _               | 15              | ns       |

| t <sub>25</sub> | <del> </del>    | 75                                    | _               | 50              | . –             | 25              | -               | 20              | _               | 15              | ns       |

| t <sub>27</sub> | -               | 75                                    | -               | 50              | _               | 25              | -               | 20              | -               | 15              | ns       |

| t <sub>28</sub> | _               | 75                                    | _               | 50              | _               | 25              | _               | 20              | _               | 15              | ns       |

| Multiplexed     | Control M       | ode - Ma                              | ster Port       |                 |                 | ·               |                 | ·               |                 | ·               | •        |

| t <sub>32</sub> | 75<br>75        | _                                     | 50<br>50        | -               | 30<br>30        | <u>-</u>        | 20<br>20        | _<br>_          | 15<br>15        | -               | ns<br>ns |

| t <sub>34</sub> | 25<br>25        |                                       | 15<br>15        | _               | 5<br>5          | -               | 0               | -               | 0               | -               | ns<br>ns |

| t <sub>35</sub> | 35<br>35        |                                       | 30<br>30        |                 | 20<br>20        | -               | 15<br>15        | <u>-</u>        | 15<br>15        | -               | ns<br>ns |

| t <sub>36</sub> | 35<br>35        | -                                     | 30<br>30        | -               | 20<br>20        | -               | 15<br>15        | -               | 15<br>15        | -               | ns<br>ns |

| t <sub>37</sub> | 35<br>35        | _                                     | 30<br>30        | -               | 20<br>20        | -               | 15<br>15        | -               | 15<br>15        | -               | ns<br>ns |

JA95C68/18/09

January, 1993

Newbridge Microsystems

Table 3a : AC Characteristics (T<sub>A</sub> = 0 to 70°C,  $V_{DD}$  = +5.0V  $\pm 10\%$ ,  $V_{SS}$  = 0V)  $^{Cont'd}$

| Number          | Description                                                                                                                                                                                         |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Master/Slav     | e Port Read/Write                                                                                                                                                                                   |

| t <sub>40</sub> | For CA95C68: MCS LOW to MRD, MWR LOW (Select Setup), (Note 4) For CA95C18: MCS LOW to MDS LOW (Select Setup), (Note 4) For CA95C68/18: SCS LOW to SDS LOW (Select Setup), (Note 4)                  |

| t <sub>41</sub> | For CA95C68: MRD, MWR HIGH to MCS HIGH (Select Hold), (Note 4) For CA95C18: MDS HIGH to MCS HIGH (Select Hold), (Note 4) For CA95C68/18: SDS HIGH to SCS HIGH (Select Hold), (Note 4)               |

| t <sub>42</sub> | MR/W VALID to MDS LOW (Setup)                                                                                                                                                                       |

| t <sub>43</sub> | MDS HIGH to MR/W INVALID (Hold)                                                                                                                                                                     |

| t <sub>44</sub> | For CA95C68: MRD, MRW LOW to MRD, MRW HIGH (Width-Write, Read) For CA95C18: MDS LOW to MDS HIGH (Width-Write, Read) For CA95C68/18: SDS LOW to SDS HIGH (Read, Write)                               |

| t <sub>45</sub> | For CA95C68: CLK LOW to MRD, MWR HIGH (Note 10) For CA95C18: CLK LOW to MDS HIGH (Note 10) For CA95C68/18: CLK LOW to SDS HIGH (Note 10)                                                            |

| t <sub>46</sub> | For CA95C68: MRD, MWR HIGH to MRD, MWR LOW (Data Strobe Recovery Time) For CA95C18: MDS HIGH to MDS LOW (Data Strobe Recovery Time) For CA95C68/18: SDS HIGH to SDS LOW (Data Strobe Recovery Time) |

| t <sub>47</sub> | For CA95C68: Write Data VALID to MWR (SDS) HIGH (Write Setup Time) For CA95C18: Write Data VALID to MDS (SDS) HIGH (Write Setup Time)                                                               |

| t <sub>48</sub> | For CA95C68: MWR HIGH to Write Data INVALID (Hold Time) For CA95C18: MDS HIGH to Write Data INVALID (Hold Time) For CA95C68/18: SDS HIGH to Write Data INVALID (Hold Time)                          |

| t <sub>49</sub> | For CA95C68: MRD LOW to Read Data VALID (Read Access Time) For CA95C18: MDS LOW to Read Data VALID (Read Access Time) For CA95C68/18: SDS LOW to Read Data VALID (Read Access Time)                 |

| t <sub>50</sub> | For CA95C68: MRD (SDS) HIGH to Read Data INVALID (Hold Time) For CA95C18: MRD (SDS) HIGH to Read Data INVALID (Hold Time)                                                                           |

| t <sub>51</sub> | For CA95C68: MRD, MWR LOW • CLK ↓ to MFLG (SFLG) HIGH (Last Strobe), (Note 5) For CA95C18: MDS LOW • CLK ↓ to MFLG (SFLG) HIGH (Last Strobe), (Note 5)                                              |

| t <sub>52</sub> | For CA95C68: MWR HIGH • CLK ↓ to CP HIGH (Note 4,11), (Last Strobe-Key Load) For CA95C18: MDS HIGH • CLK ↓ to CP HIGH (Note 4,11), (Last Strobe-Key Load)                                           |

| t <sub>53</sub> | For CA95C68: MRD, MWR (SDS) HIGH to S/S LOW (Hold Time) (Note 11) For CA95C18: MDS (SDS) HIGH to S/S LOW (Hold Time) (Note 11)                                                                      |

| t <sub>54</sub> | For CA95C68: MWR HIGH • CLK ↓ to PAR VALID (Key Write) For CA95C18: MDS HIGH • CLK ↓ to PAR VALID (Key Write)                                                                                       |

| t <sub>57</sub> | MRD, MWR HIGH to MALE HIGH                                                                                                                                                                          |

| t <sub>58</sub> | MALE LOW to MRD, MWR LOW                                                                                                                                                                            |

| t <sub>59</sub> | Address Valid to MRD, MWR LOW (to guarantee t <sub>49</sub> )                                                                                                                                       |

| t <sub>60</sub> | MALE HIGH to MRD, MWR LOW                                                                                                                                                                           |

Table 3b : AC Characteristics ( $T_A = 0$  to 70°C,  $V_{DD} = +5.0V \pm 10\%$ ,  $V_{SS} = 0V$ ) Cont'd

| Number                                | 5 MH <sub>2</sub>                                | Limits             | 10 MHz Limits   |                    | 16 MH           | z Limits           | 20 MHz Limits   |                    | 25 MHz Limits   |                    | 11-:4-   |

|---------------------------------------|--------------------------------------------------|--------------------|-----------------|--------------------|-----------------|--------------------|-----------------|--------------------|-----------------|--------------------|----------|

| Humber                                | Min                                              | Max                | Min             | Max                | Min             | Max                | Min             | Max                | Min             | Max                | Units    |

| Master/Slav                           | e Port Re                                        | ad/Write           | <del>'</del>    | . <del></del>      | <u> </u>        |                    | ·               | <u> </u>           |                 |                    | <b>!</b> |

|                                       | 35                                               | _                  | 30              | _                  | 20              | T -                | 15              | T -                | 15              | T -                | ns       |

| t <sub>40</sub>                       | 35                                               | _                  | 30              | -                  | 20              | _                  | 15              | _                  | 15              | -                  | ns       |

|                                       | 35                                               | -                  | 30              | _                  | 20              | -                  | 15              | -                  | 15              | -                  | ns       |

|                                       | 35                                               | -                  | 30              | _                  | 20              | -                  | 15              | -                  | 15              | _                  | ns       |

| t <sub>41</sub>                       | 35                                               | -                  | 30              | -                  | 20              | -                  | 15              | -                  | 15              | -                  | ns       |

|                                       | 35                                               | _                  | 30              |                    | 20              |                    | 15              | -                  | 15              | _                  | ns       |

| t <sub>42</sub>                       | 35                                               | _                  | 30              | _                  | 20              | _                  | 15              | _                  | 15              | <b>–</b>           | ns       |

| t <sub>43</sub>                       | 35                                               | -                  | 30              |                    | 20              | -                  | 15              | _                  | 15              | -                  | ns       |

|                                       | 140                                              | _                  | 70              | _                  | 45              | T -                | 35              | _                  | 30              | -                  | ns       |

| t <sub>44</sub>                       | 140                                              | -                  | 70              | -                  | 45              | -                  | 35              | -                  | 30              | _                  | ns       |

|                                       | 140                                              |                    | 70              | _                  | 45              | -                  | 35              | _                  | 30              | -                  | ns       |

|                                       | 0                                                | t <sub>WL</sub>    | 0               | t <sub>WL</sub>    | 0               | t <sub>WL</sub>    | 0               | t <sub>WL</sub>    | 0               | t <sub>WL</sub>    | ns       |

| t <sub>45</sub>                       | 0                                                | t <sub>WL</sub>    | 0               | twL                | 0               | t <sub>WL</sub>    | 0               | t <sub>WL</sub>    | 0               | t <sub>WL</sub>    | ns       |

|                                       | 0                                                | t <sub>WL</sub>    | 0               | twL                | 0               | t <sub>WL</sub>    | 0               | t <sub>WL</sub>    | 0               | t <sub>WL</sub>    | ns       |

|                                       | 160                                              | -                  | 80              | -                  | 50              | -                  | 40              | _                  | 35              | -                  | ns       |

| t <sub>46</sub>                       | 160                                              | -                  | 80              | -                  | 50              | _                  | 40              | -                  | 35              | -                  | ns       |

|                                       | 160                                              |                    | 80              | _                  | 50              | _                  | 40              |                    | 35              | -                  | ns       |

| t <sub>47</sub>                       | 80                                               | -                  | 40              | -                  | 30              | -                  | 25              | -                  | 20              | -                  | ns       |

| · · · · · · · · · · · · · · · · · · · | 80                                               |                    | 40              |                    | 30              | _                  | 25              |                    | 20              | _                  | ns       |

| •                                     | 5                                                | -                  | 5               | -                  | 0               | -                  | 0               | -                  | 0               | -                  | ns       |

| t <sub>48</sub>                       | 5<br>5                                           | _                  | 5<br>5          | _                  | 0               | _                  | 0               | _                  | 0               | _                  | ns       |

|                                       | <del>                                     </del> | 150                |                 |                    |                 | 15                 | ļ               |                    |                 |                    | ns       |

| t <sub>49</sub>                       |                                                  | 150                | _               | 75<br>75           | _               | 45<br>45           | _               | 35<br>35           | _<br>_          | 30<br>30           | ns       |

| 49                                    | _                                                | 150                | _               | 75                 | _               | 45                 | _               | 35                 | _               | 30                 | ns<br>ns |

| <del></del>                           | 10                                               | _                  | 10              | _                  | 5               |                    | 5               | -                  | 5               | -                  | ns       |

| t <sub>50</sub>                       | 10                                               | _                  | 10              | _                  | 5               | _                  | 5               | _                  | 5               | _                  | ns       |

|                                       | _                                                | 75                 |                 | 50                 | <del>-</del>    | 25                 | _               | 20                 | _               | 15                 | ns       |

| t <sub>51</sub>                       | _                                                | 75                 | _               | 50                 | -               | 25                 | _               | 20                 | _               | 15                 | ns       |

|                                       |                                                  | t <sub>C</sub> +75 | _               | t <sub>C</sub> +50 |                 | t <sub>C</sub> +25 | <del>-</del>    | t <sub>C</sub> +20 |                 | t <sub>C</sub> +15 | ns       |

| t <sub>52</sub>                       | _                                                | t <sub>C</sub> +75 | _               | t <sub>C</sub> +50 | _               | t <sub>C</sub> +25 | _               | t <sub>C</sub> +20 | -               | t <sub>C</sub> +15 | ns       |

| +                                     | 2t <sub>C</sub>                                  | -                  | 2t <sub>C</sub> | _                  | 2t <sub>C</sub> | -                  | 2t <sub>C</sub> | _                  | 2t <sub>C</sub> | _                  | ns       |

| t <sub>53</sub>                       | 2t <sub>C</sub>                                  | -                  | 2t <sub>C</sub> | -                  | 2t <sub>C</sub> | -                  | 2t <sub>C</sub> | _                  | 2t <sub>C</sub> | -                  | ns       |

| t                                     |                                                  | 75                 | _               | 50                 | _               | 25                 | _               | 20                 | _               | 15                 | ns       |

| t <sub>54</sub>                       | _                                                | 75                 | _               | 50                 | -               | 25                 | -               | 20                 | -               | 15                 | ns       |

| t <sub>57</sub>                       | 140                                              | -                  | 70              | _                  | 45              | -                  | 35              | -                  | 30              | -                  | ns       |

| t <sub>58</sub>                       | 90                                               | _                  | 50              | _                  | 30              | _                  | 25              | _                  | 20              | -                  | ns       |

| t <sub>59</sub>                       | 130                                              | _                  | 70              | -                  | 45              | _                  | 35              | _                  | 30              | -                  | ns       |

| t <sub>60</sub>                       | 200                                              | _                  | 100             | _                  | 62.5            | _                  | 50              | _                  | 40              | _                  | ns       |

| -OU                                   |                                                  |                    | .50             | <u> </u>           |                 | L                  |                 |                    | <del></del>     |                    | 113      |

Table 3a : AC Characteristics (T<sub>A</sub> = 0 to 70°C,  $V_{DD}$  = +5.0V  $\pm 10\%$ ,  $V_{SS}$  = 0V)  $^{Cont'd}$

| Number                   | Description                                      |  |  |  |  |  |

|--------------------------|--------------------------------------------------|--|--|--|--|--|

| Auxiliary Port Key Entry |                                                  |  |  |  |  |  |

| t <sub>61</sub>          | ASTB LOW to ASTB HIGH (Width)                    |  |  |  |  |  |

| t <sub>62</sub>          | CLK LOW to ASTB HIGH (Note 10)                   |  |  |  |  |  |

| t <sub>63</sub>          | ASTB HIGH to Next ASTB LOW (Recovery Time)       |  |  |  |  |  |

| t <sub>64</sub>          | Write-Data VALID to ASTB HIGH (Data Setup Time)  |  |  |  |  |  |

| t <sub>65</sub>          | ASTB HIGH to Write-Data INVALID (Data Hold Time) |  |  |  |  |  |

| t <sub>66</sub>          | ASTB HIGH • CLK ↓ to PAR VALID                   |  |  |  |  |  |

| t <sub>67</sub>          | ASTB LOW • CLK ↓ to AFLG HIGH (Last Strobe)      |  |  |  |  |  |

Table 3b : AC Characteristics (T<sub>A</sub> = 0 to 70°C,  $V_{DD}$  = +5.0V ±10%,  $V_{SS}$  = 0V)  $^{Cont'd}$