# Analog Master

We can find various size of waves generated in the ocean. The wave is sometimes energetic sometimes week according to the forces of nature and the gravitational effect of the moon, an infinitely continuous activity.

We can also find another kind of wave in electric circuits: the wave of an analog signal. This wave has great significance for humankind, despite it being much smaller than the wave in the ocean.

Engineers seek to control the analog signal, this tiny and great wave, to improve the performance and accelerate downsizing of an application system.

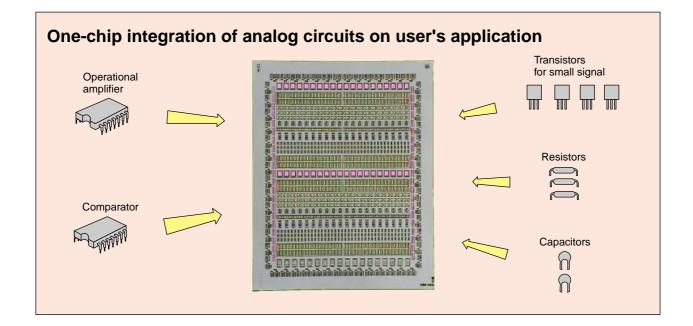

NEC introduces Analog Master, which is a semi-custom LSI just for handling the wave of analog signals, and proposes the use the Analog Master to integrate analog circuits on one-chip, supporting powerful library of macros, variety of masters and reliable development tools.

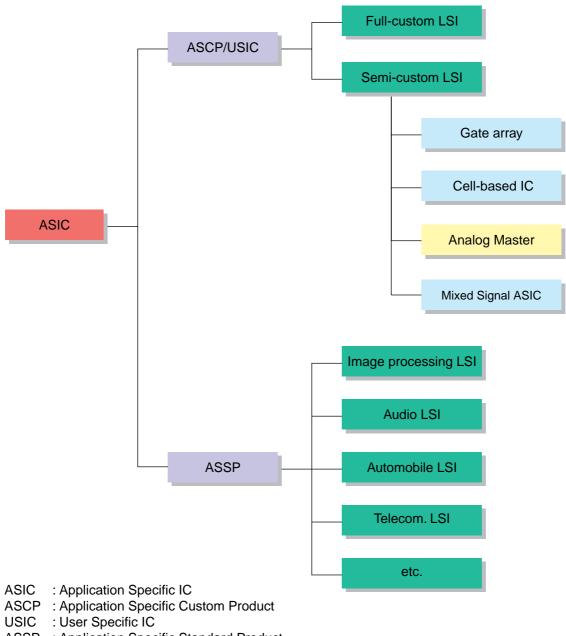

## **NEC's ASICs**

### **Classification of ASICs**

ASSP : Application Specific Standard Product

Remark For details about the Gate array and Cell-based IC, please refer to ASIC Line-up Pamphlet(A10696E).

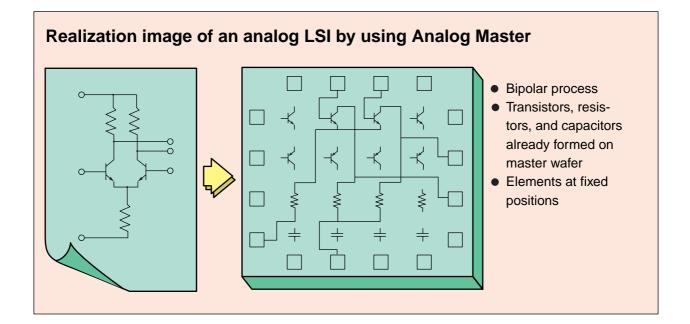

## What is Analog Master?

The Analog Master is a semi-custom LSI for creating analog circuits on a master wafer by inter-connecting pre-diffused elements (bipolar transistors, resistors, and capacitors, already formed on the wafer) with the user-defined wiring.

Analog Master is ideal for users who want to develop small-lot analog LSIs with low development cost in a short development period.

## **Features of Analog Master**

### Very short development period

Four to eight weeks from layout design to ES (Engineering Sample) production

### Powerful line-up

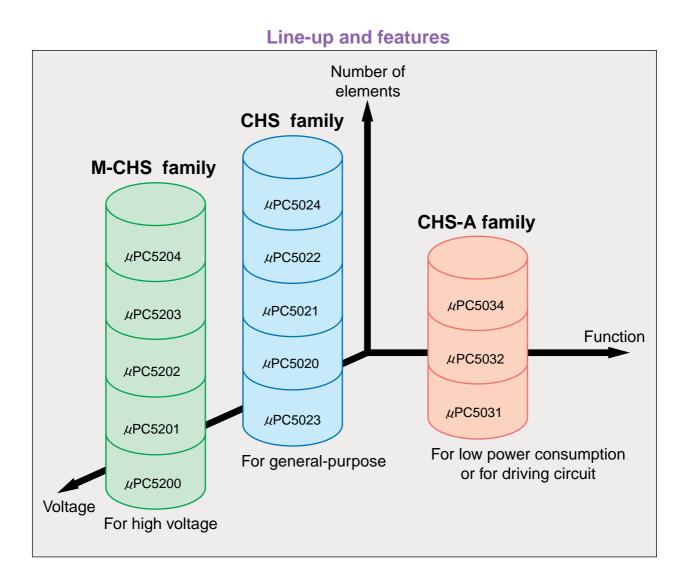

3 families (13 masters) are provided to cover wide range of operating frequency, voltage, and number of elements used.

General-purpose Analog Master General-purpose Analog Master High voltage Analog Master CHS family : 5 masters CHS-A family : 3 masters M-CHS family : 5 masters

### Various macro libraries

To reduce user's works, variety of macros are provided such as operational amplifier, comparator, regulator, etc.

## **Product Line-up of Analog Master**

NEC's Analog Master is classified in the following 3 families(refer to the figure below).

- CHS family and CHS-A family for wide application field

- M-CHS family for high voltage

From this wide line-up (3 families 13 masters), user can achieve the optimum analog LSI.

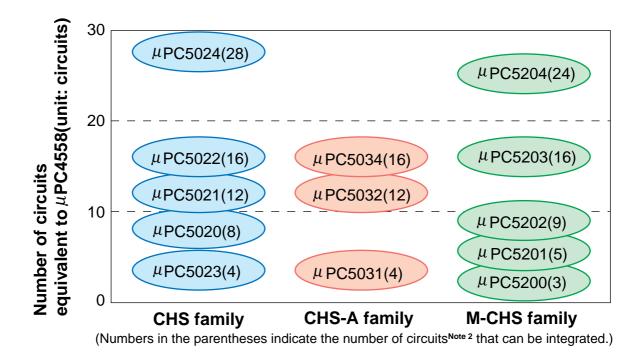

## **Circuit Scale of Each Family**

The scale of the circuit that can be integrated on the analog master differs depending on the model of each family.

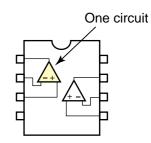

The scale of the circuit that can be integrated shown below is roughly calculated in terms of the number of circuits where one circuit is equivalent to the general-purpose operational amplifier  $\mu$ PC4558<sup>Note 1</sup>.

**Notes 1.** One of the two operational amplifiers in the general-purpose operational amplifier  $\mu$ PC4558 package (8-pin DIP) is counted as one circuit.

2. The number of circuits shown above is a guideline in which only operational amplifiers are integrated, and does not include operational amplifier peripheral circuits (such as feedback circuits). When selecting a model, estimate the circuit scale by taking these peripheral circuits into consideration.

## **CHS Family**

## **Features of CHS family**

- High speed transistors (NPN : 6 GHz, Vertical PNP : 280 MHz)

- Excellent h<sub>FE</sub> linearity of transistor

- Easy to configure low power circuits

- Adequate for circuit operating at up to 12 V and 50 MHz

- Variety of macro libraries

## **Element characteristics of CHS family**

| Element    | Item                             | Description                                                           |  |  |

|------------|----------------------------------|-----------------------------------------------------------------------|--|--|

|            | Voltage                          | 14 V (Absolute maximum ratings)                                       |  |  |

|            |                                  | NPN CHT1 : 4.5 GHz                                                    |  |  |

|            | <b>T</b>                         | CTW4 : 6.0 GHz                                                        |  |  |

|            | Transient frequency $(f_T)$      | PNP CLP1: 7.0 MHz                                                     |  |  |

| Transistor |                                  | CVP1 : 280 MHz                                                        |  |  |

| Transistor |                                  | NPN CHT1 : 100 (Ic = 500 μA)                                          |  |  |

|            | h <sub>FE</sub> standard value   | CTW4 : 100 (Ic = 500 µA)                                              |  |  |

|            |                                  | PNP CLP1 : 200 (Ic = 10 μA)                                           |  |  |

|            |                                  | CVP1 : 75 (Ic = 10 μA)                                                |  |  |

|            | h <sub>FE</sub> linearity (CHT1) | $h_{FE} (I_c = 10 \mu\text{A})/h_{FE} (I_c = 100 \mu\text{A}) = 1.00$ |  |  |

|            |                                  | Absolute accuracy : ±15 % (Ion-implanted)                             |  |  |

|            |                                  | : ±20 % (Polysilicon)                                                 |  |  |

| Resistor   | Resistance accuracy              | Relative accuracy (between adjacent resistors)                        |  |  |

|            |                                  | : ±2 % (Ion-implanted)                                                |  |  |

|            |                                  | : ±3 % (Polysilicon)                                                  |  |  |

| Capacitor  |                                  | Absolute accuracy : ±15 %                                             |  |  |

| Capacitor  | Capacitance accuracy             | Relative accuracy : ±2 % (between adjacent resistors)                 |  |  |

### **Element characteristics of CHS family**

## **Element configuration of CHS family**

- 5 masters are available from µPC5023 to µPC5024 for small to large complexity circuit, respectively.

- The CHS family should be designed so that the utilization rate of each element is up to 70 % (Only μPC5023 should be designed up to 60 %).

| Part Nu                | umber          | μ <b>ΡC5020</b> | μ <b>ΡC5021</b> | μ <b>ΡC5022</b>  | μ <b>PC5023</b> | μ <b>ΡC5024</b> | Remarks                                                                  |

|------------------------|----------------|-----------------|-----------------|------------------|-----------------|-----------------|--------------------------------------------------------------------------|

| Techno                 | ology          |                 | High-           | speed bipolar te | chnology        |                 | Name : CHS                                                               |

| Supply v               | /oltage        |                 |                 | 14 V             |                 |                 | Abusolute maximum ratings                                                |

| Number                 | of pads        | 28              | 32              | 50               | 22              | 80              |                                                                          |

| Total number           | of elements    | 1627            | 2327            | 3041             | 726             | 6151            |                                                                          |

| Total number of        | of transistors | 484             | 688             | 892              | 245             | 1508            |                                                                          |

|                        | CHT1           | 224             | 320             | 416              | 112             | 672             | I <sub>C(MAX.)</sub> = 2 mA <sup>Note1</sup>                             |

| NPN                    | CTW4           | 28              | 40              | 52               | 13              | 84              | $I_{C(MAX.)} = 18 \text{ mA}^{Note2}$                                    |

| transistors            | CEW4           | 8               | 8               | 8                | 4               | 80              | $I_{C(MAX.)} = 18 \text{ mA}^{Note2}$<br>(For electro-static protection) |

| PNP                    | CLP1           | 168             | 240             | 312              | 84              | 504             | I <sub>C(MAX.)</sub> = 0.05 mA <sup>Note1</sup><br>(Lateral type)        |

| transistors            | CVP1           | 56              | 80              | 104              | 32              | 168             | I <sub>C(MAX.)</sub> = 0.5 mA <sup>Note1</sup><br>(Vertical type)        |

| Total number           | of resistors   | 1116            | 1600            | 2098             | 468             | 4560            |                                                                          |

| lon-                   | <b>500</b> Ω   | 544             | 784             | 1024             | 224             | 1664            | P <sup>+</sup> resistor                                                  |

| implanted<br>resistors | <b>5 k</b> Ω   | 544             | 784             | 1024             | 200             | 2496            | P <sup>-</sup> resistor                                                  |

| Polysilicon            | <b>2.5 k</b> Ω | 28              | 32              | 50               |                 |                 | N <sup>+</sup> resistor                                                  |

| resistors              | <b>3 k</b> Ω   |                 |                 |                  | 44              | 400             | N <sup>+</sup> resistor                                                  |

| Number of cap          | acitors(5 pF)  | 27              | 39              | 51               | 13              | 83              | MOS capacitor                                                            |

### **Masters of CHS family**

Notes 1. Ic(MAX.) is a collector current value that reduces the value of DC current amplification factor hFE by 30 % compared to its peak value.

2. Maximum collector current value whose reliability can be guaranteed because it is limited by the maximum current density.

## **Macro library**

• TEGs are also provided.

| Function    | Library Name | Feature                                    | Specifications                                               | Equivalent | Availability |  |  |  |  |

|-------------|--------------|--------------------------------------------|--------------------------------------------------------------|------------|--------------|--|--|--|--|

|             | OA01A        | General-purpose                            | V <sub>IO</sub> : 1.4 mV (TYP.)                              | μPC4558    | Available    |  |  |  |  |

|             | OA02A        | Single power supply, high-speed            | SR⁺: 8 V/ <i>μ</i> s (TYP.)                                  | μPC842     | Available    |  |  |  |  |

|             | OA03A        | Low power                                  | $I_{CC}$ : 5 $\mu$ A (TYP., ISET = 1 $\mu$ A)                | μPC4250    | Available    |  |  |  |  |

|             | OA04B        | High input impedance                       | I <sub>B</sub> : 1nA (TYP.)                                  |            | Available    |  |  |  |  |

|             | OA06B        | Single power supply, stable                | $V_{ICM}$ : 0 to $V^{+}$ – 1.5V                              | μPC358     | Available    |  |  |  |  |

| Operational | OA06C        | Single power supply, $V_{om}^{+}$ improved | V <sub>om</sub> <sup>+</sup> : V <sup>+</sup> - 1.2 V (MIN.) | μPC358     | Available    |  |  |  |  |

| amplifier   | OA07A        | High-speed, high stability                 | SR⁺: 70 V/µs (TYP.)                                          |            | Available    |  |  |  |  |

|             | OA07B        | High-speed, wide band                      | GBW : 200 MHz (TYP.)                                         |            | Available    |  |  |  |  |

|             | OA08         | Low noise                                  | e <sub>n</sub> : 6.5 nV/√H <sub>Z</sub> (TYP.)               |            | Available    |  |  |  |  |

|             | OA09         | General-purpose (reduced element version)  | Vio: 1.2 mV (TYP.)                                           |            | Available    |  |  |  |  |

|             | OA10         | NPN input low noise                        | e <sub>n</sub> ∶3 nV/√H <sub>Z</sub> (TYP.)                  |            | Available    |  |  |  |  |

| 0           | CP02A        | High-speed                                 | t <sub>PD</sub> : 80 ns (TYP.)                               | μPC319     | Available    |  |  |  |  |

| Comparator  | CP04         | Single power supply                        | t <sub>PD</sub> : 0.5 μs (TYP.)                              | μPC393     | Available    |  |  |  |  |

|             | RG01A        | General-purpose                            | V <sub>o</sub> : 1.3 to 9.0 V                                |            | Available    |  |  |  |  |

| Regulator   | RG02A        | General-purpose                            | $V_{0}$ : 2.7 to 9.5 V                                       |            | Available    |  |  |  |  |

|             | RG03         | Low saturation                             |                                                              |            | Available    |  |  |  |  |

|             | SW01A        | Bi-directional switch<br>(High-active)     |                                                              |            | Available    |  |  |  |  |

| Switch      | SW01B        | Bi-directional switch<br>(Low-active)      |                                                              |            | Available    |  |  |  |  |

|             | SW02         | Signal switch                              |                                                              |            | Available    |  |  |  |  |

| Timer       | TM01         | Timer                                      |                                                              | μPC1555    | Available    |  |  |  |  |

### Macro library of CHS family

Remark TEG (Test Element Group) is a sample of macro.

## **CHS-A Family**

## **Features of CHS-A family**

- Compatible with the CHS family (same process as CHS family is employed)

- Many-pin masters solving shortage of number of pins

- Total internal resistance 2 times higher than the CHS family

- Internal transistor for output driver (drive up to 50 mA)

- Super white TEG supporting application to microcontroller's peripheral analog circuits

## **Element characteristics of CHS-A family**

| Element    | Item                             | Description                                                 |  |  |

|------------|----------------------------------|-------------------------------------------------------------|--|--|

|            | Voltage                          | 14 V (Absolute maximum ratings)                             |  |  |

|            |                                  | NPN CST1 : 4.5 GHz                                          |  |  |

|            | Transient franziene (f.)         | CTW3 : 5.0 GHz                                              |  |  |

|            | Transient frequency $(f_T)$      | PNP CLP1 : 7.0 MHz                                          |  |  |

| Transistor |                                  | CVP1 : 280 MHz                                              |  |  |

| Transistor |                                  | NPN CST1 : 100 (l <sub>c</sub> = 500 μA)                    |  |  |

|            | h <sub>FF</sub> standard value   | CTW3 : 100 (I <sub>c</sub> = 500 μA)                        |  |  |

|            | HFE Standard Value               | PNP CLP1 : 200 (l <sub>c</sub> = 10 μA)                     |  |  |

|            |                                  | CVP1 : 75 (I <sub>c</sub> = 10 µA)                          |  |  |

|            | h <sub>FE</sub> linearity (CST1) | $h_{FE} (I_C = 10 \mu A) / h_{FE} (I_C = 100 \mu A) = 1.00$ |  |  |

|            |                                  | Absolute accuracy : ±15 % (Ion-implanted)                   |  |  |

|            |                                  | ±20 % (Polysilicon)                                         |  |  |

| Resistor   | Resistance accuracy              | Relative accuracy (between adjacent resistors)              |  |  |

|            |                                  | : ±2 % (Ion-implanted)                                      |  |  |

|            |                                  | ±3 % (Polysilicon)                                          |  |  |

| Consoltor  | Canacitanaa aaguragy             | Absolute accuracy : ±15 %                                   |  |  |

| Capacitor  | Capacitance accuracy             | Relative accuracy : ±2 % (between adjacent resistors)       |  |  |

### **Element characteristics of CHS-A family**

## **Element configuration of CHS-A family**

- Three masters with a different circuit scale and number of output driver transistors are available.

- The CHS-A family should be designed so that the utilization rate of each element is up to 70 %.

| Part N                   | umber          | $\mu$ PC5031        | μ <b>ΡC5032</b>             | μ <b>ΡC5034</b>      | Remarks                                                               |

|--------------------------|----------------|---------------------|-----------------------------|----------------------|-----------------------------------------------------------------------|

| Technology               |                | Н                   | ligh-speed bipolar technolo | ogy                  | Name : CHS                                                            |

| Supply                   | voltage        |                     | 14 V                        |                      | Absolute maximum ratings                                              |

| Number                   | of pads        | 36                  | 56                          | 82                   |                                                                       |

| Total number             | r of elements  | 575                 | 1471                        | 2251                 |                                                                       |

| Total number             | of transistors | 223                 | 578                         | 896                  |                                                                       |

|                          | CST1           | 90                  | 240                         | 360                  | Ic(MAX.) = 2 mA <sup>Note1</sup>                                      |

| NPN                      | CTW3           | 15                  | 40                          | 60                   | Ic(max.) = 18 mA <sup>Note2</sup>                                     |

| transistors              | CEW4           | 13 <sup>Note3</sup> | 18 <sup>Note3</sup>         | 26 <sup>Note 3</sup> | $I_{C(MAX.)} = 25 \text{ mA}^{Note2}$ (For electro-static protection) |

| PNP                      | CLP1           | 90                  | 240                         | 360                  | Ic <sub>(MAX.)</sub> = 0.05 mA <sup>Note1</sup><br>(Lateral type)     |

| transistors              | CVP1           | 15                  | 40                          | 90                   | Ic <sub>(MAX.)</sub> = 0.5 mA <sup>Note1</sup><br>(Vertical type)     |

| Total number             | of resistors   | 338                 | 854                         | 1266                 |                                                                       |

| lon-<br>implanted        | <b>2 k</b> Ω   | 58                  | 154                         | 234                  | P <sup>-</sup> resistor                                               |

| resistors                | 10 kΩ          | 232                 | 616                         | 936                  | P <sup>-</sup> resistor                                               |

| Polysilicon<br>resistors | <b>3 k</b> Ω   | 48                  | 84                          | 96                   | N <sup>+</sup> resistor                                               |

| Number of cap            | oacitors(5 pF) | 14                  | 39                          | 89                   | MOS capacitor                                                         |

### **Masters of CHS-A family**

Notes 1. Ic(MAX.) is a collector current value that reduces the value of DC current amplification factor h<sub>FE</sub> by 30 % compared to its peak value.

2. Maximum collector current value whose reliability can be guaranteed because it is limited by the maximum current density.

3. When used as 50-mA output drivers, the number of elements is halved.

## **Macro library**

• TEGs are also provided.

#### Specifications Function Library Name Feature Equivalent **Availability** OA0301 General-purpose V<sub>IO</sub>: 1.4 mV (TYP.) μPC4558 Available OA0302 Single power supply, high-speed SR<sup>+</sup>: 5 V/µs (TYP.) μPC842 Available OA0303 $I_{CC}$ : 6 $\mu$ A (TYP., ISET = 1 $\mu$ A) μPC4250 Low power Available Operational OA0304 High input impedance I<sub>B</sub>:1 nA (TYP.) Available amplifier V<sub>ICM</sub>: 0 to V<sup>+</sup>-1.4 V (TYP.) OA0306B Single power supply, general-purpose μPC358 Available OA0309 General-purpose (reduced element version) Available t<sub>PD</sub>: 0.5 μs (TYP.) Comparator CP0304 Single power supply μPC393 Available Regulator RG0301 General-purpose $V_{\rm O}$ : 1.3 to Vcc – 2 V Available Switch SW0302 Signal switch Available Super Operational amplifier x 2, regulator, white WT03A Available signal switch, driver x 2 TEG<sup>Note</sup>

Macro library of CHS-A family

Note Provided with an analog circuit for use microcontroller peripherals. (package : 30-pin shrink DIP)

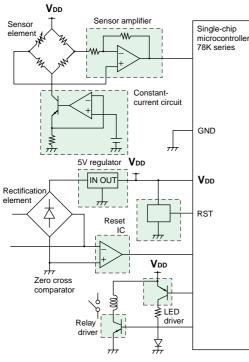

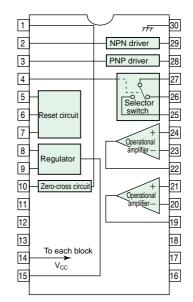

Super white TEG block diagram

Example of using super white TEG

Use the Super White TEG at the locations enclosed by the dotted lines in figure.

## **M-CHS Family**

## **Features of M-CHS family**

- Maximum supply voltage : 44 V

- High speed transistors (NPN : 2 GHz, vertical PNP : 50 MHz)

- Incorporates low noise lateral PNP transistors (HLP2A transistor)

- Adequate for circuit operating at up to 40 V and 10 MHz

## **Element characteristics of M-CHS family**

| Element    | ltem                             | Description                                                 |

|------------|----------------------------------|-------------------------------------------------------------|

|            | Voltage                          | 44 V (Absolute maximum ratings)                             |

|            |                                  | NPN HDT1:2 GHz                                              |

|            | Transient frequency (fr)         | HTW4 : 2 GHz                                                |

|            |                                  | PNP HLP2 : 2 MHz                                            |

| Transistor |                                  | HVP3 : 50 MHz                                               |

| Transistor |                                  | NPN HDT1 : 100 (I <sub>c</sub> = 500 μA)                    |

|            | h <sub>FE</sub> standard value   | HTW4 : 100 (I <sub>c</sub> = 500 μA)                        |

|            |                                  | PNP HLP2 : 100 ( $I_c = 10 \mu A$ )                         |

|            |                                  | HVP3 : 100 (I <sub>c</sub> = 10 μA)                         |

|            | h <sub>FE</sub> linearity (HDT1) | $h_{FE} (I_C = 10 \mu A) / h_{FE} (I_C = 100 \mu A) = 1.00$ |

|            |                                  | Absolute accuracy : ±15 % (Ion-implanted)                   |

|            |                                  | ±20 % (Polysilicon)                                         |

| Resistor   | Resistance accuracy              | Relative accuracy (between adjacent resistors)              |

|            |                                  | : ±2 % (Ion-implanted)                                      |

|            |                                  | : ±3 % (Polysilicon)                                        |

| Compositor |                                  | Absolute accuracy : ±15 %                                   |

| Capacitor  | Capacitance accuracy             | Relative accuracy : $\pm 2$ % (between adjacent capacitors) |

### **Element characteristics of M-CHS family**

## **Element configuration of M-CHS family**

- 5 masters are available from μPC5200 to μPC5204 for small to large complexity circuit, respectively.

- The M-CHS family should be designed so that the utilization rate of each element is up to 70 %.

| Part N                   | umber          | μ <b>ΡC5200</b> | μ <b>ΡC5201</b> | μ <b>ΡC5202</b>   | μ <b>ΡC5203</b> | μ <b>ΡC5204</b> | Remarks                                                                            |

|--------------------------|----------------|-----------------|-----------------|-------------------|-----------------|-----------------|------------------------------------------------------------------------------------|

| Techn                    | ology          |                 | High-speed, I   | nigh voltage bipc | lar technology  |                 | Name : M-CHS                                                                       |

| Supply                   | voltage        |                 |                 | 44 V              |                 |                 | Absolute maximum ratings                                                           |

| Number                   | of pads        | 24              | 28              | 40                | 52              | 62              |                                                                                    |

| Total number             | r of elements  | 653             | 1029            | 1786              | 3087            | 4561            |                                                                                    |

| Total number             | of transistors | 189             | 303             | 535               | 932             | 1382            |                                                                                    |

|                          | HDT1           | 72              | 120             | 216               | 384             | 576             | IC(MAX.) = 1.0 mA <sup>Note1</sup>                                                 |

| NPN                      | HTW4           | 9               | 15              | 27                | 48              | 72              | IC(MAX.) = 10 mA <sup>Note1</sup>                                                  |

| transistors              | HEW4           | 12              | 14              | 20                | 26              | 31              | IC(MAX.) = 10 mA <sup>Note1</sup>                                                  |

|                          | HTT5           | 12              | 14              | 20                | 26              | 31              | IC(MAX.) = 18 mA <sup>Note2</sup>                                                  |

|                          | HLP2           | 48              | 80              | 144               | 256             | 384             | I <sub>C(MAX.)</sub> = 0.12 mA <sup>Note1</sup><br>(Lateral type)                  |

| PNP<br>transistors       | HLP2A          | 18              | 30              | 54                | 96              | 144             | Low noise PNP<br>I <sub>C(MAX.)</sub> = 0.12 mA <sup>Note1</sup><br>(Lateral type) |

|                          | HVP3           | 18              | 30              | 54                | 96              | 144             | I <sub>C(MAX.)</sub> = 1.0 mA <sup>Note1</sup><br>(Vertical type)                  |

| Total number             | of resistors   | 456             | 712             | 1225              | 2108            | 3108            |                                                                                    |

| lon-<br>implanted        | <b>500</b> Ω   | 144             | 240             | 426               | 760             | 1144            | P <sup>+</sup> resistor                                                            |

| resistors                | 1 <b>0 k</b> Ω | 216             | 360             | 639               | 1140            | 1716            | P <sup>-</sup> resistor                                                            |

| Polysilicon<br>resistors | 500 Ω          | 96              | 112             | 160               | 208             | 248             | N <sup>+</sup> resistor                                                            |

| Number of cap            | oacitors(5 pF) | 8               | 14              | 26                | 47              | 71              | MOS capacitor                                                                      |

### **Masters of M-CHS family**

Notes 1. Ic(MAX.) is a collector current value that reduces the value of DC current amplification factor hFE by 30 % compared to its peak value.

2. Maximum collector current value whose reliability can be guaranteed because it is limited by the maximum current density.

## **Macro library**

• TEGs are also provided.

### Macro library of M-CHS family

| Function    | LibraryName | Feature                                | Specifications                              | Equivalent | Availability |

|-------------|-------------|----------------------------------------|---------------------------------------------|------------|--------------|

|             | OA201       | General-purpose                        | V <sub>IO</sub> : 1.0 mV (TYP.)             | μPC4558    | Available    |

|             | OA202       | Single power supply, stable            | $V_{ICM}$ : 0 to V <sup>+</sup> – 1.5 V     | μPC358     | Available    |

|             | OA203       | Low power                              | I <sub>CC</sub> : 16 μA (TYP., ISET = 2 μA) | μPC4250    | Available    |

|             | OA204       | High input impedance                   | I <sub>B</sub> : 1.2 nA (TYP.)              |            | Available    |

| Operational | OA205A      | High-speed, high stability             | SR⁺: 30 V/µs (TYP.)                         |            | Available    |

| amplifier   | OA205B      | High-speed, wide band                  | funity : 50 MHz (TYP.)                      |            | Available    |

|             | OA205C      | High-speed, 1 block version            |                                             |            | Available    |

|             | OA206       | Low noise                              | e <sub>n</sub> : 4.5 nV/√Hz (TYP.)          | μPC4570    | Available    |

|             | OA207       | Single power supply, high-speed        | SR⁺: 7.5 V/µs (TYP.)                        | μPC842     | Available    |

| Comparator  | CP201       | Single power supply                    | t <sub>PD</sub> : 3μs (TYP.)                |            | Available    |

| Comparator  | CP202       | High-speed                             | t <sub>PD</sub> : 180 ns (TYP.)             | μPC319     | Available    |

| Regulator   | RG201       | General-purpose                        |                                             |            | Available    |

|             | SW201A      | Bi-directional switch<br>(High-active) |                                             |            | Available    |

| Switch      | SW201B      | Bi-directional switch<br>(Low-active)  |                                             |            | Available    |

|             | SW202       | Signal switch                          |                                             |            | Available    |

Remark TEG (Test Element Group) is a sample of macro.

## Packages

To meet various requirements about the package type and the number of pins, variety of packages are available for the Analog Master. User can select optimum combination for each application. For availability, refer to the tables of the following pages.

### Packages available for Analog Master

### DIP

14-pin (7.62 mm(300)) 16-pin (7.62 mm(300)) 18-pin (7.62 mm(300)) 22-pin (10.16 mm(400))

### Shrink DIP

18-pin (7.62 mm(300)) 20-pin (7.62 mm(300)) 22-pin (7.62 mm(300)) 24-pin (7.62 mm(300)) 28-pin (10.16 mm(400)) 30-pin (10.16 mm(400)) 42-pin (15.24 mm(600)) 48-pin (15.24 mm(600))

## SOP

8-pin (5.72mm (225)) 14-pin (5.72mm (225)) 16-pin (5.72mm (225)) 16-pin (7.62mm (300)) 20-pin (7.62mm (300)) 24-pin (7.62mm (300)) 24-pin (9.53mm (375)) 28-pin (9.53mm (375))

### Shrink SOP

14-pin (5.72mm (225)) 16-pin (5.72mm (225)) 20-pin (5.72mm (225)) 20-pin (7.62mm (300)) 16-pin (9.53mm (375)) 24-pin (7.62mm (300)) 30-pin (7.62mm (300)) 36-pin (7.62mm (300)) 38-pin (7.62mm (300))

QFP

48-pin ( $7 \times 7$ ) 48-pin (10 × 10) 48-pin (10 × 14) 56-pin (10 × 10) 64-pin (14 × 20) 68-pin (10 × 14) 72-pin (10 × 10) 80-pin (14 × 14) 80-pin (14 × 20) TQFP

48-pin (7 × 7)

| Pacl          | kage                   | Lead Pitch | μ <b>PC5020</b> | μ <b>PC5021</b> | μ <b>ΡC5022</b> | μ <b>PC5023</b> | μ <b>ΡC5024</b> |

|---------------|------------------------|------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|               | 8-pin                  | 2.54 mm    |                 |                 |                 |                 |                 |

|               | 14-pin                 | 2.54 mm    |                 |                 |                 | 0               |                 |

| DIP           | 16-pin                 | 2.54 mm    |                 |                 |                 | 0               |                 |

| Dii           | 18-pin <sup>Note</sup> | 2.54 mm    |                 |                 |                 | 0               |                 |

|               | 22-pin                 | 2.54 mm    |                 |                 | 0               |                 |                 |

|               | 14-pin                 | 1.778 mm   |                 |                 |                 |                 |                 |

|               | 18-pin                 | 1.778 mm   |                 | 0               |                 | 0               |                 |

|               | 20-pin                 | 1.778 mm   |                 |                 |                 | 0               |                 |

|               | 22-pin                 | 1.778 mm   |                 |                 |                 | 0               |                 |

| Shrink<br>DIP | 24-pin                 | 1.778 mm   | 0               | 0               |                 |                 |                 |

|               | 28-pin                 | 1.778 mm   |                 |                 | 0               |                 |                 |

|               | 30-pin                 | 1.778 mm   |                 | 0               | 0               |                 |                 |

|               | 42-pin <sup>Note</sup> | 1.778 mm   |                 |                 | 0               |                 |                 |

|               | 48-pin                 | 1.778 mm   |                 |                 |                 |                 |                 |

|               | 8-pin                  | 1.27 mm    |                 |                 |                 | (5.72 mm)       |                 |

|               | 14-pin                 | 1.27 mm    |                 |                 |                 | (5.72 mm)       |                 |

|               | 16-pin                 | 1.27 mm    | (7.62 mm)       | (9.53 mm)       |                 | (5.72 mm)       |                 |

| SOP           | 20-pin                 | 1.27 mm    | (7.62 mm)       | (7.62 mm)       |                 | (7.62 mm)       |                 |

|               | 24-pin                 | 1.27 mm    | (7.62 mm)       | (7.62 mm)       | (9.53 mm)       | (7.62 mm)       |                 |

|               | 28-pin                 | 1.27 mm    | (9.53 mm)       | (9.53 mm)       | (9.53 mm)       |                 |                 |

|               | 14-pin                 | 0.65 mm    |                 |                 |                 | (5.72 mm)       |                 |

|               | 16-pin                 | 0.65 mm    |                 |                 |                 | (5.72 mm)       |                 |

| Shrink        | 20 min                 | 0.65 mm    | (5.72 mm)       |                 |                 | (5.72 mm)       |                 |

| SOP           | 20-pin                 | 0.65 mm    | (7.62 mm)       |                 |                 |                 |                 |

|               | 24-pin                 | 0.65 mm    | (7.62 mm)       |                 |                 | (7.62 mm)       |                 |

|               | 30-pin                 | 0.65 mm    |                 | (7.62 mm)       |                 |                 |                 |

|               | 36-pin                 | 0.8 mm     | (7.62 mm)       |                 |                 |                 |                 |

|               |                        | 0.5 mm     |                 | (7 x 7)         | ○(7 x 7)        |                 |                 |

|               | 48-pin                 | 0.65 mm    |                 |                 | ⊖(10 x 10)      |                 |                 |

| QFP           |                        | 0.8 mm     |                 |                 | ⊖(10 x 14)      |                 | ⊖(10 x 14)      |

| wi i          | 64-pin                 | 1.0 mm     |                 |                 |                 |                 | ⊖(14 x 20)      |

|               | 68-pin                 | 0.65 mm    |                 |                 |                 |                 | ⊖(10 x 14)      |

|               | 80-pin                 | 0.8 mm     |                 |                 |                 |                 | ⊖(14 x 20)      |

| TQFP          | 48-pin                 | 0.5 mm     |                 | (7 x 7)         | (7 x 7)         |                 |                 |

## Package availability of CHS family

Note Because the time is required to prepare for production, consult NEC before development. Also consult NEC when you use 42-pin shrink DIP packages. **Remarks1.** In the above table, 'O' indicates a package that is available, and ' – ' indicates a package that is unavailable.

2. Some packages may have unavailable pins. Please refer to the Analog Master Package Manual (A10495E) for unavailable pins.

| Pack   | kage              | Lead Pitch | μ <b>ΡC5031</b> | μ <b>ΡC5032</b> | μ <b>ΡC5034</b> |

|--------|-------------------|------------|-----------------|-----------------|-----------------|

|        | 18-pin            | 1.778 mm   |                 |                 |                 |

| Shrink | 22-pin            | 1.778 mm   | (7.62 mm)       |                 |                 |

| -      | 24-pin            | 1.778 mm   |                 |                 |                 |

| DIP    | 28-pin            | 1.778 mm   |                 |                 |                 |

|        | 30-pin            | 1.778 mm   |                 | (10.16mm)       |                 |

|        | 16-pin            | 1.27 mm    | (7.62 mm)       | (7.62 mm)       |                 |

| COD    | 20-pin            | 1.27 mm    | (7.62 mm)       | (7.62 mm)       |                 |

| SOP    | 24-pin            | 1.27 mm    | (7.62 mm)       | (7.62 mm)       | ().53 mm)       |

|        | 28-pin            | 1.27 mm    |                 | (9.53 mm)       | (9.53 mm)       |

|        | 24-pin            | 0.65 mm    |                 | (7.62 mm)       |                 |

| Shrink | 30-pin            | 0.65 mm    |                 | (7.62 mm)       |                 |

| SOP    | 36-pin            | 0.80 mm    | (7.62 mm)       | (7.62 mm)       |                 |

| 38-pin |                   | 0.65 mm    |                 | (7.62 mm)       |                 |

| 48-pin |                   | 0.5 mm     | ○(7x7)          | ○(7x7)          | ○(7x7)          |

| QFP    | 56-pin            | 0.65 mm    |                 | ◯ ( 10 x 10 )   | ○ ( 10 x 10 )   |

|        | 80-pin            | 0.65 mm    |                 |                 | ○ ( 14 x 14 )   |

| TQFP   | TQFP 48-pin 0.5 m |            |                 | ○(7x7)          | ○(7x7)          |

## Package availability of CHS-A family

Remarks1. In the above table, 'O' indicates a package that is available, and ' - ' indicates a package that is unavailable.

2. Some packages may have unavailable pins. Please refer to the Analog Master Package Manual (A10495E) for unavailable pins.

| Pack   | age                    | Lead Pitch | μ <b>ΡC5200</b> | μ <b>ΡC5201</b> | μ <b>ΡC5202</b> | μ <b>ΡC5203</b> | μ <b>ΡC5204</b> |

|--------|------------------------|------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|        | 8-pin                  | 2.54 mm    |                 |                 |                 |                 |                 |

|        | 14-pin                 | 2.54 mm    |                 |                 |                 |                 |                 |

|        | 16-pin                 | 2.54 mm    |                 |                 |                 |                 |                 |

| 212    | 18-pin                 | 2.54 mm    |                 |                 |                 |                 |                 |

| DIP    | 22-pin                 | 2.54 mm    |                 |                 |                 |                 |                 |

|        | 24-pin                 | 2.54 mm    |                 |                 |                 |                 |                 |

|        | 28-pin                 | 2.54 mm    |                 |                 |                 |                 |                 |

|        | 42-pin                 | 2.54 mm    |                 |                 |                 |                 |                 |

|        | 14-pin                 | 1.778 mm   |                 |                 |                 |                 |                 |

|        | 20-pin                 | 1.778 mm   |                 |                 |                 |                 |                 |

| Shrink | 24-pin                 | 1.778 mm   | 0               | 0               |                 |                 |                 |

| DIP    | 28-pin                 | 1.778 mm   |                 |                 | 0               |                 |                 |

| Dii    | 30-pin                 | 1.778 mm   |                 |                 |                 |                 |                 |

|        | 42-pin <sup>Note</sup> | 1.778 mm   |                 |                 | 0               |                 |                 |

|        | 48-pin <sup>Note</sup> | 1.778 mm   |                 |                 |                 | 0               |                 |

|        | 16-pin                 | 1.27 mm    | ○(7.62 mm)      |                 |                 |                 |                 |

| COD    | 20-pin                 | 1.27 mm    | ○(7.62 mm)      |                 |                 |                 |                 |

| SOP    | 24-pin                 | 1.27 mm    | ○(7.62 mm)      | (7.62 mm)       | (9.53 mm)       |                 |                 |

|        | 28-pin                 | 1.27 mm    |                 | ○(9.53 mm)      | ⊖ (9.53 mm)     |                 |                 |

| Shrink | 20-pin                 | 0.65 mm    | ○(7.62 mm)      | ○(7.62 mm)      |                 |                 |                 |

| SOP    | 24-pin                 | 0.65 mm    |                 | (7.62 mm)       |                 |                 |                 |

|        |                        | 0.5 mm     |                 | ○(7x7)          |                 |                 |                 |

|        | 48-pin                 | 0.65 mm    |                 |                 | ○ (10 x 10 )    |                 |                 |

|        |                        | 0.8 mm     | ⊖ (10 x 14)     |                 |                 | ⊖ (10 x 14 )    |                 |

| QFP    | 56-pin                 | 0.65 mm    |                 |                 |                 |                 | ⊖ (10 x 10 )    |

|        | 64-pin                 | 1.0 mm     |                 |                 |                 | ⊖( 14 x 20 )    |                 |

|        | 72-pin                 | 0.5 mm     |                 |                 |                 |                 | ⊖ (10 x 10 )    |

|        | 80-pin                 | 0.65 mm    |                 |                 |                 |                 | ⊖ (14 x 14 )    |

| TQFP   | 48-pin                 | 0.5 mm     |                 | ○(7x7)          |                 |                 |                 |

## Package availability of M-CHS family

**Note** Because the time is required to prepare for production, consult NEC before development. Also consult NEC when you use 42-pin, or 48-pin shrink DIP packages.

**Remarks1.** In the above table, 'O' indicates a package that is available, and ' – ' indicates a package that is unavailable.

2. Some packages may have unavailable pins. Please refer to the Analog Master Package Manual (A10495E) for unavailable pins.

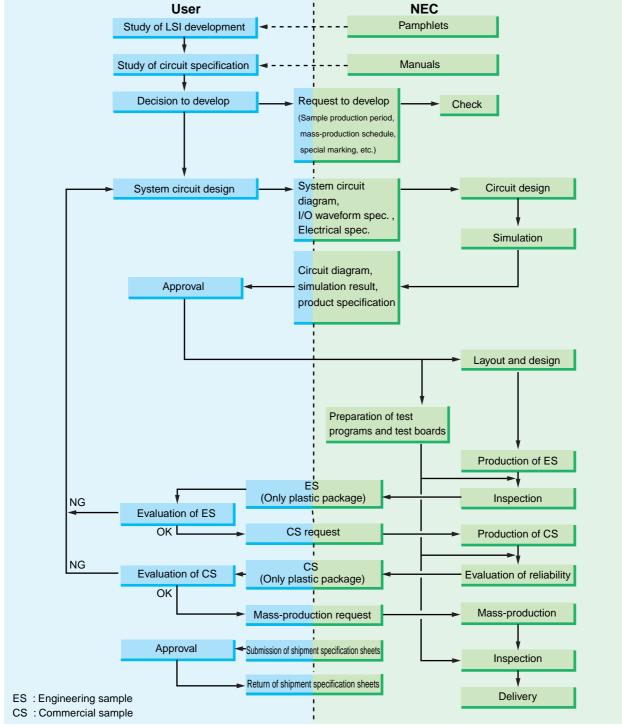

The development of the Analog Master is completed by both the user and NEC. Passing the development work from the user to NEC is called interfacing.

NEC supports only the circuit diagram level interface.

| Interface Level      | System Design | Circuit Design | Layout Design | ES Production |

|----------------------|---------------|----------------|---------------|---------------|

| Circuit design level | User's works  |                | NEC's works   |               |

### Circuit diagram level interface

User completes up to system design, NEC takes over all subsequent works, such as circuit design and simulation.

This interface level is classified into 3 more levels as shown in the table below, depending on parts configuring the circuit and whether or not to create and estimate a breadboard.

| Level   | Creation and Estimation<br>of Breadboard | Parts Configurating the Circuit                                                                                                                       |

|---------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| S level | Not necessary                            | General-purpose SSI <sup>Note 1</sup> , Standard SSI Note 2, Transistor for small signal, Analog Master TEG <sup>Note 3</sup> , Resistors, Capacitors |

| A level | Necessary                                | Standard SSI Note 2, Transistor for small signal, Analog Master TEGNote 3, Resistors, Capacitors                                                      |

| B level | Necessary                                | Analog Master TEG <sup>Note 3</sup> , Resistors, Capacitors (80 % or more is configured with macro)                                                   |

Notes 1. General-purpose SSI : SSI except standard SSI

| 2. Standard SSI      | : OP amp. ( #PC151/741, 251/1458, 258/4558, 451/324, 458/4741, 802/4250, 842, 844, 1251/358, 4556, and |

|----------------------|--------------------------------------------------------------------------------------------------------|

|                      | equivalents of other manufacturers)                                                                    |

|                      | : Comparator ( µPC177/1339, 271/311, 272/319, 277/393, and equivalents of other manufacturers)         |

|                      | : Regulator (Three-terminal regulator, Shunt regulator)                                                |

|                      | : Function block ( µPC617/1555, and equivalents of other manufacturers)                                |

| 3. Analog Master TEG | : Library TEGs, basic block TEGs, super white TEGs provided by NEC.                                    |

|                      |                                                                                                        |

Remark TEG (Test Element Group) is a sample for evaluation.

## Flow for circuit diagram level interface

**Remark** Unlike CS and mass-produced model, the quality of ES is not guaranteed. Therefore, do not use the ES for production or reliability testing.

## Works by user

## (1) Study of circuit specifications

User checks circuit requirements such as supply voltage range, pin voltages, circuit performance, package, and resistance to electro-static discharge (ESD)damage, according to manuals supplied by NEC.

## (2) Request to develop

User requests NEC to develop the chip, and provides detailed descriptions of the followings.

- 1. Interface level

- 2. Master name, package

- 3. Scheduled interface date, ES/CS delivery date, schedule of mass-production

- 4. Request of special marking

- 5. Request of TEG

## (3) Circuit design

User designs circuit configuration so as to realize required function and performance using parts configuring circuit on page 22 (system circuit design).

### (4) Interface (circuit diagram level interface)

User sends the following interface documents to NEC after completion of system circuit design.

- 1. System block diagram

- 2. System circuit diagram

- 3. I/O waveform specifications

- 4. Electrical specifications

- 5. Check sheet

It is recommended that the above documentation be submitted on special forms supplied by NEC.

Describe in as much detail as possible because this is important information for IC design and simulation.

## (5) Approval of circuit diagram

Circuit diagram designed by NEC, simulation result, and product specification are sent to user.

After all items are checked and approved by user, NEC starts layout design and ES production.

## (6) Evaluation of ES and request to prepare CS

User evaluates engineering samples (ES). Two levels of samples are sent. One is standard sample, and the other called variation sample is for assersion of electrical characteristics (note that NEC does not assure characteristic variation to user with this sample). After the samples pass evaluation, user requests NEC to prepare commercial samples (CS) after discussing and determining actual specification of test condition list.

## (7) Evaluation of CS and request to start mass-production

User evaluates commercial samples (CS).

After the samples pass evaluation, user requests NEC to start mass production.

## Works by NEC

## (1) Helping user in studying LSI development

When user plans to develop particular LSIs, NEC is ready to give advices on whether the user's circuit specifications can be achieved from the viewpoint of the number of elements and element characteristics. Please consult NEC after determining the specifications.

## (2) Circuit design

According to user's circuit requirements, NEC completes circuit design, and simulation, and prepares test conditions. This testing is only for DC items.

## (3) Layout design

Layout design requires 1 to 4 weeks. In addition, before completion of layout design, back annotation is performed.

Characteristics will be checked by extracting the parasitic elements to feedback to the circuit design side and performing simulation. Layout design requires one additional week for this checking.

## (4) ES production

The user will usually receive the ES 3 to 4 weeks after completion of layout design.

## (5) CS production

After request by user, NEC starts production of commercial samples. From CS production request, it takes in general 1 month for standard quality grade device, and 2.5 month for special quality grade device to deliver the CS. The above schedule is conditional upon whether the product specifications have been determined between the user and NEC.

## (6) Preparation of shipment specification sheets

The shipment specification sheets describe absolute maximum ratings, electrical characteristics, package outline, and marking.

## (7) Mass-production

NEC mass-produces the LSI according to the user's production schedule.

The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by the customer. The export or re-export of this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

- The information in this document is current as of May, 2001. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC semiconductor products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC

semiconductor products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades: "Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

(Note)

(1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

(2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

M8E 00.4

### For further information, please contact:

#### **NEC Corporation**

NEC Building 7-1, Shiba 5-chome, Minato-ku Tokyo 108-8001, Japan Tel: 03-3454-1111 http://www.ic.nec.co.jp/

#### [North & South America]

#### **NEC Electronics Inc.**

2880 Scott Blvd. Santa Clara, CA 95050-2554, U.S.A. Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288 http://www.necel.com/

#### NEC do Brasil S.A.

Electron Devices Division Rodovia Presidente Dutra, Km 214 07210-902-Guarulhos-SP Brasil Tel: 011-6462-6810 Fax: 011-6462-6829

#### [Europe]

NEC Electronics (Germany) GmbH Kanzlerstr. 2, 40472 Düsseldorf, Germany Tel: 0211-650302 Fax: 0211-6503490 http://www.nec.de/

#### **Munich Office**

Arabellastr. 17 81925 München, Germany Tel: 089-921003-0 Fax: 089-92100315

#### **Stuttgart Office**

Industriestr. 3 D-70565 Stuttgart, Germany Tel: 0711-99010-0 Fax: 0711-99010-19

#### Hannover Office

Podbielskistr. 164 D-30177 Hannover, Germany Tel: 0511-33402-0 Fax: 0511-33402-34

#### **Benelux Office**

Boschdijk 187a 5612 HB Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

#### Scandinavia Office

P.O. Box 134 18322 Taeby, Sweden Tel: 08-6380820 Fax: 08-6380388

### NEC Electronics (UK) Limited

Cygnus House, Sunrise Parkway, Linford Wood, Milton Keynes, MK14 6NP, U.K. Tel: 01908-691-133 Fax: 01908-670-290

#### NEC Electronics (France) S.A.

9, rue Paul Dautier-B.P. 52 78142 Velizy-Villacoublay Cédex France Tel: 01-3067-5800 Fax: 01-3067-5899

#### Madrid Office

Juan Esplandiu, 15 28007 Madrid, Spain Tel: 091-504-2787 Fax: 091-504-2860

#### NEC Electronics Italiana s.r.l.

Via Fabio Filzi, 25/A, 20124 Milano, Italy Tel: 02-667541 Fax: 02-66754299

#### [Asia & Oceania]

### NEC Electronics Hong Kong Limited

12/F., Cityplaza 4, 12 Taikoo Wan Road, Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

### Seoul Branch

10F, ILSONG Bldg., 157-37, Samsung-Dong, Kangnam-Ku Seoul, the Republic of Korea Tel: 02-528-0303 Fax: 02-528-4411

#### NEC Electronics Taiwan Ltd.

7F, No. 363 Fu Shing North Road Taipei, Taiwan, R. O. C. Tel: 02-2719-2377 Fax: 02-2719-5951

#### NEC Electronics Singapore Pte. Ltd.

238A Thomson Road #12-01/10 Novena Square Singapore 307684 Tel: 253-8311 Fax: 250-3583

Document No. A10512EJCV0PF00(12th edition) Date Published September 2001 N CP(K) G01.7