# MOS INTEGRATED CIRCUIT $\mu$ PD1701C-015

# PLL FREQUENCY SYNTHESIZER AND CONTROLLER FOR FM AND AM RADIO

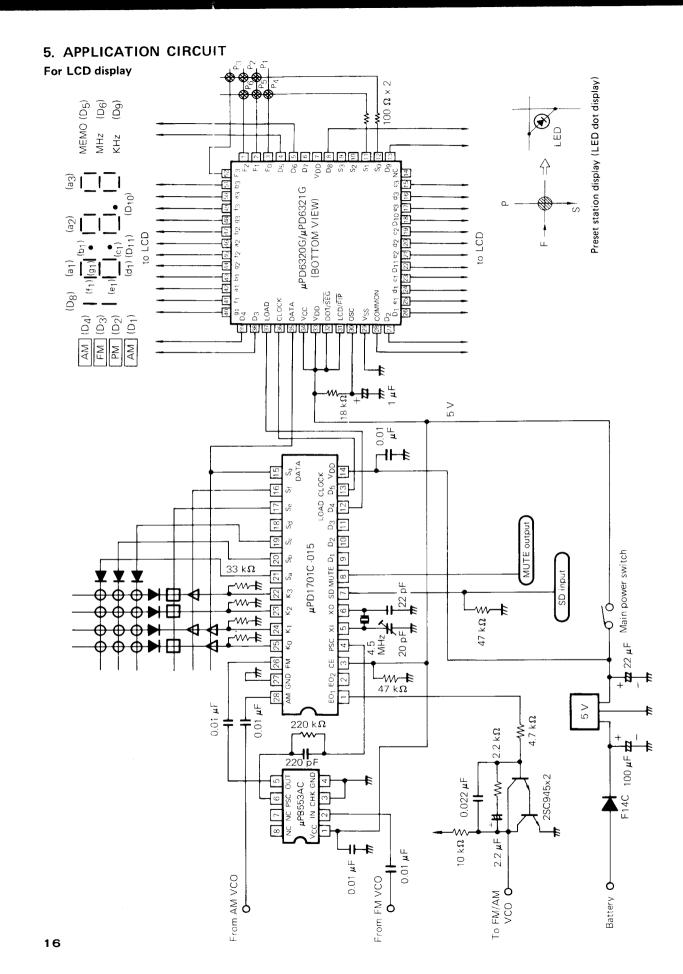

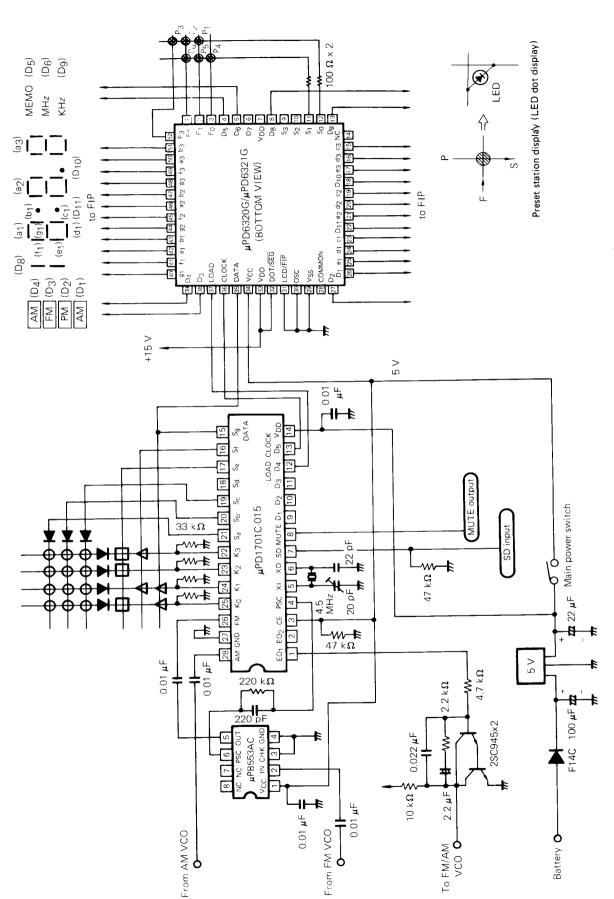

The  $\mu$ PD1701C-015 is a CMOS LSI with built-in PLL synthesizer capable of receiving FM/AM in U.S.A. and Japan. In combination with a dedicated prescalar ( $\mu$ PB553AC), the  $\mu$ PB553AC can be used to construct high fidelity FM/AM digital synthesizer tuners for car audio and home stereo systems.

The device used in the display driver stage may be either  $\mu$ PD6320G or  $\mu$ PD6321G designed for FIP or LCD static display.

#### **FEATURES**

- 12-hour clock function

- Built-in PLL, swallow counter, and controller

- Reference frequency increased to 25 kHz due to use of pulse swallow method for FM

- Reception of Japanese traffic information (522 to 1629 kHz)

- U.S.A. and Japanese FM and AM band selectable by initializing switch

- U.S.A. FM channel space selectable by initializing switch (100/200 kHz)

- FIP or LCD static display (with  $\mu$ PD6320G/ $\mu$ PD6321G)  $\mu$ PD6320G and  $\mu$ PD6321G differ in display of the number "7" ("  $\frac{1}{2}$ " and "  $\frac{1}{2}$ ").

- Built-in seek and scan functions (UP tuning only)

- Low-consumption current: 500  $\mu$ A (TYP.) (clock operation only when CE pin at low level)

- Small 28-pin plastic DIP package (400 mil width) which occupies less circuit board space

- 5 V ±10 % single power supply

#### **FUNCTION**

#### Receiving frequency, channel spacing, reference frequency, intermediate frequency

| COUNTRY | BAND | FREQUENCY RANGE   | CHANNEL SPACE | REFERENCE<br>FREQUENCY | INTERMEDIATE<br>FREQUENCY |

|---------|------|-------------------|---------------|------------------------|---------------------------|

| U.S.A.  |      | 531 to 1 602 kHz  | 9 kHz         | 9 kHz                  | 455 kHz                   |

|         | AM   | 530 to 1 620 kHz  | 10 kHz        | 10 kHz                 | 455 kHz                   |

|         | FM   | 87.9 to 107.9 MHz | 100 kHz       | 25 kHz                 | 10.7 MHz                  |

|         |      | 87.9 to 107.9 MHz | 200 kHz       | 25 kHz                 | 10.7 MHz                  |

|         | AM   | 531 to 1 629 kHz  | 9 kHz         | 9 kHz                  | 455 kHz                   |

| JAPAN   | FM   | 76.1 to 89.9 MHz  | 100 kHz       | 25 kHz                 | -10.7 MHz                 |

#### **Tuning functions**

| (1) | Auto tuning (UP direction sawtooth wave mode)                                |

|-----|------------------------------------------------------------------------------|

|     | Scan Reception for five seconds at a time with frequency display flashing ON |

|     | and OFF during reception.                                                    |

| Cook | Station held once it has been tuned |

|------|-------------------------------------|

| (2) | Manual    | tuning   | (sawtooth    | wave | mode) |

|-----|-----------|----------|--------------|------|-------|

| (2) | iviaiiuai | Lutillig | (Save COOLIT | Wave | mode  |

| Manual UP (MU)   | Stepwise increment/decrement by momentary switch, or if depressed   |

|------------------|---------------------------------------------------------------------|

| Manual Down (MD) | for more than 0.5 seconds, rapid scanning until switch is released. |

- (3) Preset station memory call ..... Six stations in each band

- Preset station display . . . . . . . . . Dot display (LED) or 7-segment numerical display (FIP/LCD) selected by setting the DOT/SEG pin (pin 32) of  $\mu$ PD6320G/ $\mu$ PD6321G to high

- or low level.

- (4) Last station memory ..... One station in each band

#### **Clock functions**

- (1) 12-hour display (with AM/PM display)

- (2) Hour and minute setting functions

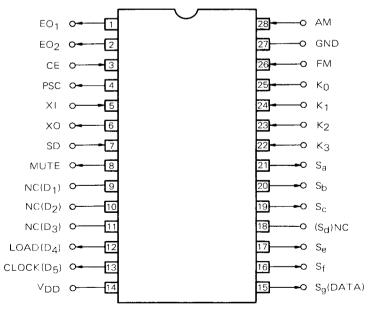

#### PIN CONFIGURATION (Top View)

NC (No Connection)

#### PIN DESCRIPTION

| PIN NO.  | PIN SYMBOL                                | PIN NAME                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|-------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 2      | EO <sub>1</sub><br>EO <sub>2</sub>        | E ror out                | PLL phase detector charge pump outputs. A high level output obtained from these pins if the frequency obtained by dividing the oscillator frequency is higher than the reference frequency, and a low level output is obtained if the divided oscillator frequency is lower.  Since the same output signal is obtained from both EO <sub>1</sub> and EO <sub>2</sub> , either pin may be connected to the L.P.F. |

| 3        | CE                                        | Chip enable              | Device selector signal input pin. Pin is set to high level for normal device operation, and to low level when device is not being used.  High level Normal operation  Low level Display OFF, PLL operation halted, clock operation continued, memory maintained  Note that neither high nor low level pulses of less than 134 µs are accepted.                                                                   |

| 4        | PSC                                       | Pulse swallow<br>control | Output of signal for switching the prescalar frequency division factor for FM reception where pulse swallow is used as the frequency division method.  Connect to PSC pin of the µPB553AC dedicated prescalar via capacitor and resistor elements. The switchable µPB553AC frequency division factors are 1/16 and 1/17.                                                                                         |

| 5<br>6   | XI<br>XO                                  | X'tal                    | Crystal oscillator connector pins.  Connect to a 4.5 MHz crystal oscillator.                                                                                                                                                                                                                                                                                                                                     |

| 7        | SD                                        | Station<br>detector      | Stop signal input pin used in auto tuning. Apply a high level input signal with 45 msec after locking the PLL.                                                                                                                                                                                                                                                                                                   |

| 8        | MUTE                                      | MUTE output              | Active high output pin used to eliminate shock noise when the PLL lock is disrupted.  See the MUTE output timing chart for details.                                                                                                                                                                                                                                                                              |

| 9 to 11  | NC<br>(D <sub>1</sub> to D <sub>3</sub> ) | (Digit out)              | Make no connections to these pins since they are not used in $\mu$ PD1701C-015.                                                                                                                                                                                                                                                                                                                                  |

| 12       | LOAD<br>(D <sub>4</sub> )                 | LOAD                     | Display data latch output to the $\mu PD6320G/\mu PD6321G$ display driver. Connect directly to the $\mu PD6320G/\mu PD6321G$ LOAD pin. See the section on display data for details.                                                                                                                                                                                                                              |

| 13       | CLOCK<br>(D <sub>5</sub> )                | Clock out                | Clock signal output used in transfer of display data to the $\mu$ PD6320G/ $\mu$ PD6321G display driver. Connect directly to the $\mu$ PD6320G/ $\mu$ PD6321G CLOCK pin.  Data passed to $\mu$ PD6320G/ $\mu$ PD6321G is shifted at the leading edge of this clock signal.                                                                                                                                       |

| 14       | V <sub>DD</sub>                           | VDD                      | Device power supply pin (+5 V $\pm$ 10 %). The V <sub>DD</sub> rise time must be less than 500 ms. The device may not be correctly initialized if the rise time is very long.                                                                                                                                                                                                                                    |

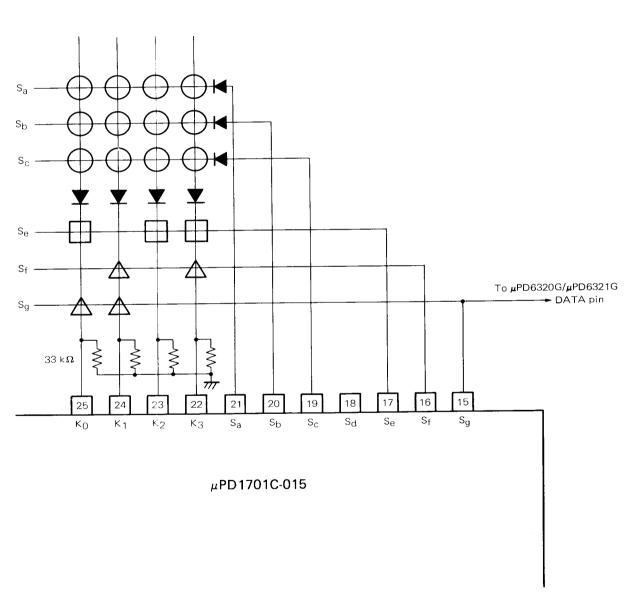

| 15 to 21 | S <sub>a</sub> to S <sub>g</sub>          | Key source               | Signal source for key matrix scanning (active high). In addition to key matrix scanning, the $S_g$ pin also supplies display data to the $\mu PD6320G/\mu PD6321G$ display driver. See the section on display data for details. Note that $S_d$ is not used.                                                                                                                                                     |

| PIN NO.  | PIN SYMBOL                       | PIN NAME                | DESCRIPTION                                                                                                                                                                                              |

|----------|----------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22 to 25 | K <sub>0</sub> to K <sub>3</sub> | Key return signal input | Input pins for key return signals from external key matrix. (See section on key matrix configuration on page 8.)                                                                                         |

| 26       | FM                               | FM VCO<br>signal input  | Input of the µPB553AC prescalar outputs obtained by dividing the FM local oscillator frequency by 16 or 17. Because of the built-in AC amplifier, eliminate the DC components of the input by capacitor. |

| 27       | GND                              | GND                     | Connect to system ground.                                                                                                                                                                                |

| 28       | АМ                               | AM VCO<br>signal input  | Input of the AM local oscillator output. Because of the built-in AC amplifier, eliminate the DC components of the input by capacitor.                                                                    |

#### **CONTENTS**

| 1. KEY MATRIX                          |      |      |

|----------------------------------------|------|------|

| 1.1 CONFIGURATION OF KEY MATRIX        | <br> | 6    |

| 12 SWITCH CONNECTIONS                  | <br> | 6    |

| 1.3 EXAMPLES OF KEY MATRIX CONNECTIONS | <br> | 7    |

| 2. DESCRIPTION OF KEY MATRIX           |      |      |

| 2.1 INITIALIZATION DIODE MATRIX        | <br> | 8    |

| 22 ALTERNATE SWITCHES                  | <br> | 9    |

| 2.3 MOMENTARY SWITCHES                 | <br> | 10   |

| 3. DISPLAY                             |      |      |

| 3.1 DISPLAY DATA                       | <br> | 11   |

| 4. TIMING CHARTS                       | <br> | 14   |

| 4.1 MUTE OUTPUT TIMING CHART           | <br> | 14   |

| 5. APPRICATION CIRCUIT                 | <br> | 16   |

| 6. ELECTRICAL CHARACTERISTICS          |      |      |

| 6.1 ABSOLUTE MAXIMUM RATINGS           | <br> | . 18 |

| 6.2 DC CHARACTERISTICS                 | <br> | . 18 |

| 6.3 AC CHARACTERISTICS                 | <br> | . 18 |

| 7. PACKAGE DIMENSIONS                  | <br> | 19   |

#### 1. KEY MATRIX

#### 1.1 CONFIGURATION OF KEY MATRIX

| OUTPUT         | INPUT | K <sub>0</sub> (25) | K <sub>1</sub> (24) | K <sub>2</sub> (23) | K <sub>3</sub> (22) |

|----------------|-------|---------------------|---------------------|---------------------|---------------------|

| Sa             | (21)  | RCAL                | ME<br>(TIME SET)    | MD<br>(HOUR)        | MU<br>(MINUTE)      |

| S <sub>b</sub> | (20)  | M4                  | МЗ                  | M2                  | M1                  |

| S <sub>c</sub> | (19)  | M6                  | M5                  | SEEK                | SCAN                |

| S <sub>d</sub> | (18)  |                     |                     |                     |                     |

| S <sub>e</sub> | (17)  | AM/FM               |                     | B                   | A                   |

| S <sub>f</sub> | (16)  |                     | 9 k/10 k            |                     | sur P T             |

| S <sub>g</sub> | (15)  | 100 k/200 k         | JPN/USA             |                     |                     |

Figures in parentheses indicate pin nos.

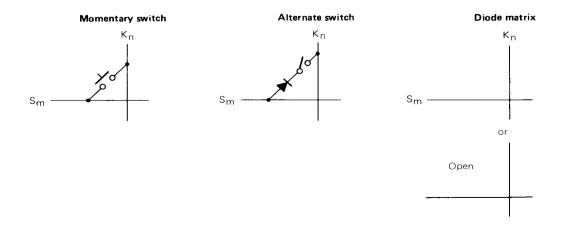

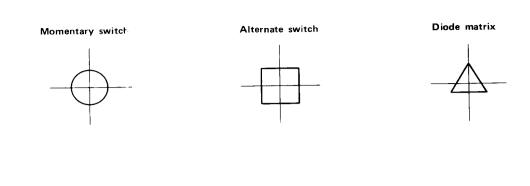

: Momentary switch

: Alternate switch

: Initialization diode matrix (shorted or opened by diode)

#### 1.2 SWITCH CONNECTIONS

# 1.3 EXAMPLES OF KEY MATRIX CONNECTIONS

# 2. DESCRIPTION OF KEY MATRIX

#### 2.1 INITIALIZATION DIODE MATRIX

The initialization diode matrix status is read only when the power is switched on and when the CE pin status is changed from low to high level. The matrix status is disregarded at all other times. This status is set by shorting or opening matrix intersections by diode.

(In the following table, "1" cenotes diode short and "0" denotes open.)

| SYMBOL               | FUNCTION                                                                                                                                                                                                                |                                  |                                             |                             |                        |                           |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------------------|-----------------------------|------------------------|---------------------------|--|--|

|                      | P (Priority) is the display priority selector switch. Priority can be set when the display mode setting switch  A is ON and switch B is OFF. The display reverts to the priority display five seconds after the display |                                  |                                             |                             |                        |                           |  |  |

| _                    | change is mad                                                                                                                                                                                                           | le.                              |                                             |                             |                        |                           |  |  |

| Р                    | А                                                                                                                                                                                                                       | в Р                              | Order of priority                           |                             |                        |                           |  |  |

|                      |                                                                                                                                                                                                                         | 1                                | Frequency priority                          |                             |                        |                           |  |  |

|                      | 1                                                                                                                                                                                                                       | 0 0                              | Clock priority                              |                             |                        |                           |  |  |

|                      | Selector swite                                                                                                                                                                                                          | ch for area setting              | . This switch is set in com                 | nbination with 1            | the following ban      | d setting switche         |  |  |

| JPN/USA              | JPN/USA                                                                                                                                                                                                                 | Area                             |                                             |                             |                        |                           |  |  |

| JPN/USA              | 1                                                                                                                                                                                                                       | Japan                            |                                             |                             |                        |                           |  |  |

|                      | 0                                                                                                                                                                                                                       | U.S.A.                           |                                             |                             |                        |                           |  |  |

| 9 k/10 k             | the channel s                                                                                                                                                                                                           | pace is 9 kHz irre<br>9 k/10 k   | spective of the position o                  | Channel spacing             | Reference<br>frequency | Intermediate<br>frequency |  |  |

|                      | 1                                                                                                                                                                                                                       |                                  | 531 to 1 629 kHz                            | 9 kHz                       | 9 kHz                  | 455 kHz                   |  |  |

|                      |                                                                                                                                                                                                                         | 1                                | 531 to 1 602 kHz                            | 9 kHz                       | 9 kHz                  | 455 kHz                   |  |  |

|                      | 0                                                                                                                                                                                                                       | 0                                | 530 to 1 620 kHz                            | 10 kHz                      | 10 kHz                 | 455 kHz                   |  |  |

|                      | FM channel t                                                                                                                                                                                                            | oand space setting               | switch when used in the                     |                             |                        | vitch is set to JPN       |  |  |

|                      |                                                                                                                                                                                                                         | pace is 100 kHz i                | rrespective of the position                 | n of this switch            |                        |                           |  |  |

|                      | the channel s                                                                                                                                                                                                           |                                  |                                             | n of this switch<br>Channel | Reference              | Intermediate              |  |  |

| 100 k/200 k          |                                                                                                                                                                                                                         | pace is 100 kHz i<br>100 k/200 k | rrespective of the position Frequency range |                             |                        | Intermediate<br>frequency |  |  |

| 100 k/2 <b>0</b> 0 k | the channel s                                                                                                                                                                                                           |                                  |                                             | Channel                     | Reference              |                           |  |  |

| 100 k/200 k          | JPN/USA                                                                                                                                                                                                                 |                                  | Frequency range                             | Channel spacing             | Reference<br>frequency | frequency                 |  |  |

| A B 0 0 1 0 1 1 1 1 Note 1.                  | Reception ban  AM band  FM band  cle setting switches. Th  Display mode  Clock only  Frequency and clock  Display OFF  Frequency | Priority display restored after five seconds. (Note 1) Priority determined by P.  No priority (Note 2)                                                                          | Clock, memory hold  Clock, memory hold  All functions operatable  Clock, memory hold  All functions operatable                                                                                                                                                                                                                                   | the A and B switches.  Input enabled switches  Time adjustment (ME, MD, MU).  A and B switches  All switches  A and B switches                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 0 Display mo A B 0 0 1 1 1 1 1 1 Note 1.   | AM band FM band cle setting switches. The Display mode Clock only Frequency and clock Display OFF Frequency and clock            | Priority display restored after five seconds. (Note 1) Priority determined by P.  No priority (Note 2)                                                                          | Operation  Clock, memory hold  All functions operatable  Clock, memory hold  All functions                                                                                                                                                                                                                                                       | Input enabled switches Time adjustment (ME, MD, MU). A and B switches  All switches  A and B switches                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0 Display mo A B 0 0 1 1 1 1 Note 1.         | FM band  cle setting switches. The Display mode Clock only  Frequency and clock  Display OFF  Frequency and clock                | Priority display restored after five seconds. (Note 1) Priority determined by P.  No priority (Note 2)                                                                          | Operation  Clock, memory hold  All functions operatable  Clock, memory hold  All functions                                                                                                                                                                                                                                                       | Input enabled switches Time adjustment (ME, MD, MU). A and B switches  All switches  A and B switches                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Display mo  A B  O 0  1 0  1 1  1 1  Note 1. | Clock only  Clock only  Frequency and clock  Display OFF  Frequency and clock                                                    | Priority display restored after five seconds. (Note 1) Priority determined by P.  No priority (Note 2)                                                                          | Operation  Clock, memory hold  All functions operatable  Clock, memory hold  All functions                                                                                                                                                                                                                                                       | Input enabled switches Time adjustment (ME, MD, MU). A and B switches  All switches  A and B switches                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A B 0 0 1 0 1 1 1 1 Note 1.                  | Clock only  Frequency and clock  Display OFF  Frequency and clock                                                                | Priority display restored after five seconds. (Note 1) Priority determined by P.  No priority (Note 2)                                                                          | Operation  Clock, memory hold  All functions operatable  Clock, memory hold  All functions                                                                                                                                                                                                                                                       | Input enabled switches Time adjustment (ME, MD, MU). A and B switches  All switches  A and B switches                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0 0 0 0 0 1 1 1 1 1 Note 1.                  | Clock only  Frequency and clock  Display OFF  Frequency and clock                                                                | Priority display restored after five seconds. (Note 1) Priority deter- mined by P.  No priority (Note 2)                                                                        | Clock, memory hold  All functions operatable  Clock, memory hold All functions                                                                                                                                                                                                                                                                   | Time adjustment (ME, MD, MU). A and B switches  All switches  A and B switches                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1 0 0 1 1 1 1 Note 1.                        | Frequency and clock  Display OFF  Frequency and clock                                                                            | restored after five seconds. (Note 1) Priority determined by P.  No priority (Note 2)                                                                                           | All functions operatable  Clock, memory hold All functions                                                                                                                                                                                                                                                                                       | (ME, MD, MU). A and B switches  All switches  A and B switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0 1 1 1 Note 1.                              | and clock  Display OFF  Frequency and clock                                                                                      | restored after five seconds. (Note 1) Priority determined by P.  No priority (Note 2)                                                                                           | Clock, memory hold All functions                                                                                                                                                                                                                                                                                                                 | A and B switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1 1<br>Note 1.                               | Frequency<br>and clock                                                                                                           | (Note 2)                                                                                                                                                                        | memory hold All functions                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Note 1.                                      | and clock                                                                                                                        | (Note 2)                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                  | All switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                              |                                                                                                                                  |                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Mhen in R howeve And if immed Note 2.        | cal key is presser, the frequency displeter RCAL inately.                                                                        | sed. When scanning frequency is maintained for five key is pressed during a connected from display to the AM/FM selector, swi                                                   | uency is displayed<br>uencies during auto<br>e seconds after comp<br>i frequency display<br>switching, the display<br>tch is used.                                                                                                                                                                                                               | for only five seconds if to or manual tuning operation pleting that tuning operation, the clock time is display ay being changed only who                                                                                                                                                                                                                                                                                                                                                                                                 |

| Tuning                                       | key                                                                                                                              | frequency each time th  If clock time is display is changed to frequency                                                                                                        | is key is pressed. ed when one of the                                                                                                                                                                                                                                                                                                            | se keys is pressed, the disp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1                                            | howeve And if immed Note 2. The fiv the RC R Tuning                                                                              | however, the frequency disp And if the RCAL immediately.  Note 2.  The five-second timer is dis the RCAL or a tuning key, or RCAL key  Tuning key AM/FM Tuning keys include the | however, the frequency display is maintained for five And if the RCAL key is pressed during a immediately.  Note 2.  The five-second timer is disconnected from display the RCAL or a tuning key, or the AM/FM selector, swi RCAL key Display is changed from frequency each time th Tuning key If clock time is display is changed to frequency | however, the frequency display is maintained for five seconds after company that if the RCAL key is pressed during a frequency display immediately.  Note 2.  The five-second timer is disconnected from display switching, the display the RCAL or a tuning key, or the AM/FM selector, switch is used.  RCAL key Display is changed from frequency to cloc frequency each time this key is pressed.  Tuning key If clock time is displayed when one of the is changed to frequency immediately.  Tuning keys include the MU , MD , SCAN |

# 2.3 MOMENTARY SWITCHES

| SYMBOL | FUNCTION                                                                                                                                                                                                 |  |  |  |  |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|        | Manual tuning switches                                                                                                                                                                                   |  |  |  |  |  |  |

|        | MU Manual Up                                                                                                                                                                                             |  |  |  |  |  |  |

| MU     | M D Manual Down                                                                                                                                                                                          |  |  |  |  |  |  |

|        | Frequency is increased/decreased by one channel each time, the MU or MD key                                                                                                                              |  |  |  |  |  |  |

| MD     | is pressed. And if either key is pressed for more than 0.5 second, the frequency is changed at a rate of 45                                                                                              |  |  |  |  |  |  |

|        | ms per step until the key is released. And pressing either key together with the ME key                                                                                                                  |  |  |  |  |  |  |

|        | enables the time to be adjusted.                                                                                                                                                                         |  |  |  |  |  |  |

| M1     | Preset memory switches                                                                                                                                                                                   |  |  |  |  |  |  |

| to     | Each key is equipped with an independent memory for FM and AM. Frequencies preset in these memories                                                                                                      |  |  |  |  |  |  |

| М6     | can be called by pressing one of the Preset memory keys. And if M keys is pressed within five seconds                                                                                                    |  |  |  |  |  |  |

| J      | after pressing the ME key, the current corresponding memory.                                                                                                                                             |  |  |  |  |  |  |

|        | When in frequency display mode                                                                                                                                                                           |  |  |  |  |  |  |

|        | The ME key is used to store a frequency in one of the preset memories. After tuning to the                                                                                                               |  |  |  |  |  |  |

|        | desired frequency by using the tuning keys (such as MU and MD , press the                                                                                                                                |  |  |  |  |  |  |

|        | ME key. Then press one of the M1 to M6 keys within five                                                                                                                                                  |  |  |  |  |  |  |

|        | seconds to store that frequency in the corresponding memory.                                                                                                                                             |  |  |  |  |  |  |

|        | When in clock display mode                                                                                                                                                                               |  |  |  |  |  |  |

| ME     | The clock time is advanced by one hour each time the MD key is pressed while the                                                                                                                         |  |  |  |  |  |  |

|        | ME key is depressed. And if the MD key is pressed for more than 0.5 second,                                                                                                                              |  |  |  |  |  |  |

|        | the time is advanced rapidly (4 hours per second). Likewise, the time is advanced by one minute each                                                                                                     |  |  |  |  |  |  |

|        | time the MU key is pressed while the ME key is depressed. If the                                                                                                                                         |  |  |  |  |  |  |

|        | MU key is pressed for more than 0.5 second, the time is advanced rapidly (4 minutes per                                                                                                                  |  |  |  |  |  |  |

|        | second). Note that during this time adjustment, advancing the minutes column does not result in                                                                                                          |  |  |  |  |  |  |

|        | advancement of the hour column, and that the internal seconds counter is reset to zero each time the                                                                                                     |  |  |  |  |  |  |

|        | minutes column is adjusted.                                                                                                                                                                              |  |  |  |  |  |  |

|        | The SCAN key is an auto tuning key used in sawtooth wavemode. When this key is pressed,                                                                                                                  |  |  |  |  |  |  |

|        | scanning is commenced in the UP direction only. If a high level input is applied to the SD pin during                                                                                                    |  |  |  |  |  |  |

| SCAN   | scanning, the frequency at that point is held for five seconds with the frequency display flashing ON and  OFF. If the SCAN key is pressed again during that five second interval, the frequency remains |  |  |  |  |  |  |

| 00,    | held. If on the other hand, no switch at all is pressed during that five second interval, scanning is recom-                                                                                             |  |  |  |  |  |  |

|        | mended.                                                                                                                                                                                                  |  |  |  |  |  |  |

|        | If another key is pressed during scanning, the scanning is stopped and the operation specified by the                                                                                                    |  |  |  |  |  |  |

|        | pressed key is commenced.                                                                                                                                                                                |  |  |  |  |  |  |

|        | The SEEK key is an auto tuning key used in sawtooth wave mode. When this key is pressed,                                                                                                                 |  |  |  |  |  |  |

| SEEK   | seeking is commenced in the UP direction only.                                                                                                                                                           |  |  |  |  |  |  |

|        | The only point in which the seek operation differs from scanning is that held when a high level input is                                                                                                 |  |  |  |  |  |  |

|        | applied to the SD pin during auto tuning.                                                                                                                                                                |  |  |  |  |  |  |

| RCAL   | The RCAL key is used to change frequency and clock displays. The display is changed each                                                                                                                 |  |  |  |  |  |  |

|        | time the key is pressed.                                                                                                                                                                                 |  |  |  |  |  |  |

#### 3. DISPLAY

#### 3.1 DISPLAY DATA

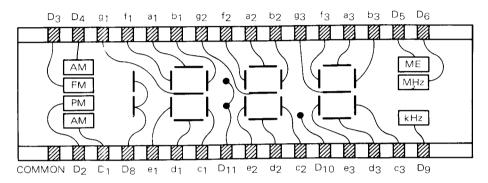

The  $\mu$ PD1701C-015 device is only used in static displays. The DATA output signal is obtained from the S<sub>g</sub> pin, the CLOCK output signal is obtained from the D<sub>5</sub> pin, and the LOAD signal is obtained from the D<sub>4</sub> pin. These three outputs are connected to the respective DATA, CLOCK, and LOAD pins of the  $\mu$ PD6320G/ $\mu$ PD6321G (FIP/LCD static display driver (see the circuit diagram examples).

The DATA signal output is obtained serially one bit at a time in the sequence indicated in Table 1.

13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 Output 7 8 10 11 12 6 2 3 5 ranking 8 4 2 1 8 4 2 1 8 4 2 | 1 Bit 8 ; 4 2 | 1 D<sub>12</sub> D<sub>11</sub> D<sub>10</sub> D<sub>9</sub> D<sub>8</sub> D<sub>7</sub> D<sub>6</sub> D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> D<sub>2</sub> D<sub>1</sub> 4 ; 2 | 1 weight Preset Preset 7-segment 7-segment 7-segment station decoder station decoder decoder display display 0.1 MHz 1 MHz 10 MHz Display \*\* MHz ME AM FM PM AM (LED dot (7-seament (FM) (FM) (FM) data display) 1 kHz display) 100 kHz 10 kHz (AM) (AM) (AM)

Table 1 DATA signal output ranking and display contents

Since  $\mu PD1701C-015$  passes "1" data to flag  $D_{12}$ , the blank display is set by 0000B.

The same output data is passed to the LED dot (output ranking 29 to 32) and 7-segment (output ranking 25 to 28) preset station displays. The display type is selected by the  $\mu PD6320G/\mu PD6321G\ DOT/\overline{SEG}$  pin.

\*\* Flag D7 of output ranking 6 is not used. Due to output of 0 data, the display is blank.

<sup>\*</sup> Flag D<sub>12</sub> at output ranking 1 is the bit used to select the "blank display determining data" for the preset station display (7-segment display) at output rankings 25 to 28.

<sup>&</sup>quot;1" . . . Blank when DATA is 0000B (display is 1 to F)

<sup>&</sup>quot;0" . . . Blank when DATA is 1111B (display is 0 to E)

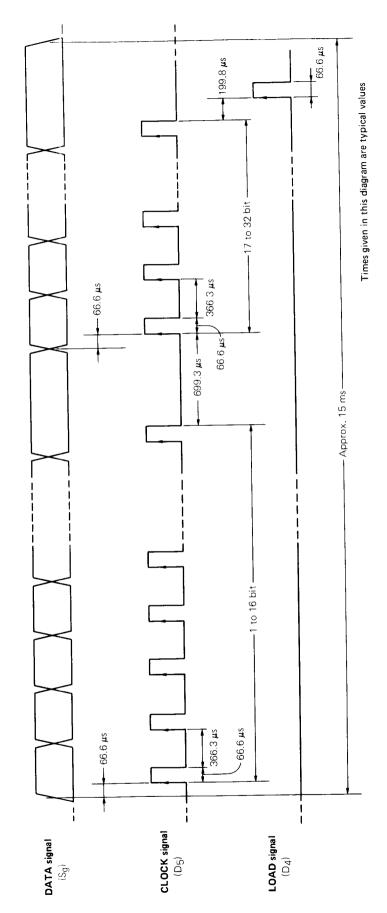

CLOCK signal outputs are generated for each bit of DATA signal, and data is shifted into the  $\mu$ PD6320G/ $\mu$ PD6321G internal register synchronized with CLOCK signal rising edges. A LOAD signal output is generated after 32 bits of data have been transferred, and the  $\mu$ PD6320G/ $\mu$ PD6321G shift register contents are latched to the display buffer. The timing for this data transfer is outlined in Figure 2.

Data is transferred from  $\mu PD$  701C-015 to the  $\mu PD6320G/\mu PD6321G$  display driver in the following seven cases.

- When the clock minute column is increased (unless in frequency display mode)

- When the display mode is switched by A/B switch

- When in NORMAL status (with no key operation) (5 seconds/time)

- When display is changed by key operation

- When frequency (division factor) is changed

- When SD signal is applied during scanning resulting in the scanning being halted and the display flashed ON and OFF (0.5 second/time)

- When there is no display with mode setting switch A OFF and B ON (125 msec/time)

Fig. 1 Display pattern and connection diagram

\* Pin names are µPD6320G/µPD6321G pin names.

Refer to the  $\mu$ PD6320G and  $\mu$ PD6321G catalogs for details on the display driver.

Fig. 2 Static display data transfer timing

#### 4. TIMING CHARTS

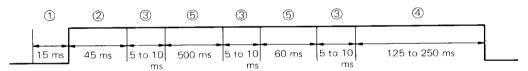

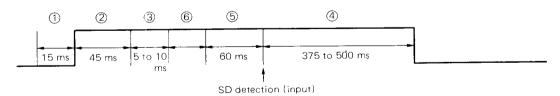

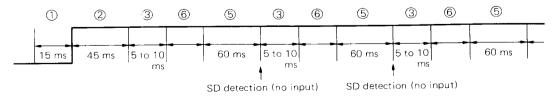

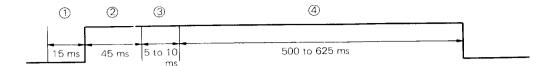

#### 4.1 MUTE OUTPUT TIMING CHART

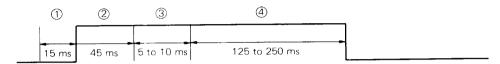

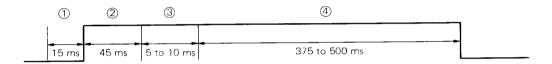

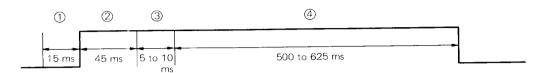

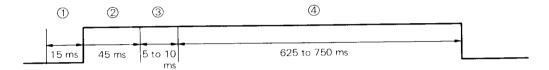

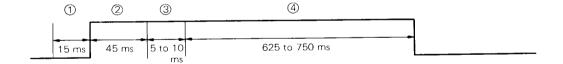

- (1) Key chattering suppression interval (when key switched on)

- (2) MUTE "first out" interval

- (3) Change in the frequency division factor setting and display contents

- 4 MUTE "last out" interval

- (5) Scan time

- (6) PLL Lock time

#### (1) Manual Up and Manual Down

(i) When key is released within 0.5 sec. (except when at edge of band)

Interval 4 commenced after key is released

(ii) When key is released within 0.5 sec. (at edge of band: High frequency switched to low frequency)

(iii) Key depressed for more than 0.5 sec.

Interval (5) becomes 375 to 500 msec. if edge of band is reached.

#### (2) Seek Up

(i) When SD signal is applied

(ii) When SD signal is not applied

Interval (5) becomes 375 to 500 msec. if edge of band is reached.

#### (3) Preset memory call

#### (4) Band switching

#### (5) Mode switching

#### (6) Power ON (CE: Low → High)

#### (7) Chip Enable (CE) change from low to high level

The practical circuits and circuit constants shown in this manual have not be designed for mass production (where deviation between parts and temperature characteristics must also be considered). Also note that NEC bears no responsibility in respect to patents related to these circuits.

17

# 6. ELECTRICAL CHARACTERISTICS

# 6.1 ABSOLUTE MAXIMUM RATINGS (Ta = 25 $^{\circ}$ C)

| Power supply voltage | $V_{DD}$          | -0.3 to $+6.0$      | V            |

|----------------------|-------------------|---------------------|--------------|

| Input voltage        | $\mathcal{N}_{1}$ | $-0.3$ to $+V_{DD}$ | V            |

| Output voltage       | $V_{O}$           | $-0.3$ to $+V_{DD}$ | V            |

| Output current       | $I_{OH}$          | -10                 | mΑ           |

| Storage temperature  | $T_{stg}$         | 55 to +125          | $^{\circ}$ C |

#### 6.2 DC CHARACTERISTICS

# (Measuring conditions $V_{DD}$ = 4.5 to 5.5 V, $T_a$ = -35 to +75 $^{\circ}$ C unless specified otherwise)

| CHARACTERISTIC                 | SYMBOL                 | MIN.                | TYP.                                                            | MAX.                | UNIT                                     | CONDITION                                                        |

|--------------------------------|------------------------|---------------------|-----------------------------------------------------------------|---------------------|------------------------------------------|------------------------------------------------------------------|

| High level input voltage       | V <sub>IH1</sub>       | 0.8 V <sub>DD</sub> |                                                                 | V <sub>DD</sub>     | V                                        | SD pin                                                           |

| High level input voltage       | V <sub>1H2</sub>       | 0.7 V <sub>DD</sub> |                                                                 | VDD                 | V                                        | CE pin                                                           |

| High level input voltage       | V <sub>IH3</sub>       | 0.6 V <sub>DD</sub> |                                                                 | V <sub>DD</sub>     | V                                        | K <sub>0</sub> to K <sub>3</sub> pins                            |

| Low level input voltage        | V <sub>IL1</sub>       | 0                   |                                                                 | 0.3 V <sub>DD</sub> | V _                                      | CE pin                                                           |

| Low level input voltage        | V <sub>IL2</sub>       | 0                   |                                                                 | 0.2 V <sub>DD</sub> | V                                        | SD and K <sub>0</sub> to K <sub>3</sub> pins                     |

| High level output voltage      | V <sub>OH1</sub>       | 4.0                 |                                                                 |                     | V                                        | PSC pin, $I_{OH} = -0.2 \text{ mA}$                              |

|                                | V <sub>OH2</sub> 4.0 V |                     |                                                                 |                     | EO <sub>1</sub> , EO <sub>2</sub> , MUTE |                                                                  |

| High level output voltage      |                        | ·                   | D <sub>4</sub> & D <sub>5</sub> pins, I <sub>OH</sub> = -0.5 mA |                     |                                          |                                                                  |

| High level output voltage      | VOH3                   | 4.0                 |                                                                 |                     | V                                        | $S_a$ to $S_g$ pins, $I_{OH} = -1.0$ mA                          |

| Low level output voltage       | V <sub>OL1</sub>       |                     |                                                                 | 0.5                 | V                                        | EO <sub>1</sub> , EO <sub>2</sub> pins, I <sub>OL</sub> = 0.5 mA |

|                                |                        |                     |                                                                 | 0.5                 | .,                                       | MUTE, D <sub>1</sub> to D <sub>5</sub> PSC,                      |

| Low level output voltage       | VOL2                   |                     |                                                                 | 0.5                 | V                                        | $S_a$ to $S_g$ pins, $I_{OL} = 0.2$ mA                           |

|                                |                        |                     | 100                                                             |                     | K <sub>0</sub> to K <sub>3</sub> pins,   |                                                                  |

| High level input current       | HI                     | 5.0                 | 25                                                              | 100                 | μА                                       | V <sub>1</sub> = V <sub>DD</sub> = 5 V                           |

| AC input voltage               | V <sub>in</sub>        | 1.0                 |                                                                 | V <sub>DD</sub>     | V <sub>p-p</sub>                         | VCOL and VCOH pins                                               |

| Power supply voltage rise time | t <sub>r</sub>         |                     |                                                                 | 0.5                 | s                                        | $V_{DD}$ pin, $V_{DD}$ : $0 \rightarrow 4.5 \text{ V}$           |

| Operating current              | IDD                    |                     | 0.5                                                             | 2.0                 | mA                                       | Display OFF, PLL operation                                       |

|                                |                        |                     |                                                                 |                     |                                          | OFF, clock only operating,                                       |

|                                |                        |                     |                                                                 |                     |                                          | V <sub>DD</sub> = 5 V                                            |

#### 6.3 AC CHARACTERISTICS

# (Measuring conditions $V_{DD}$ = 4.5 to 5.5 V, $T_a$ = -35 to +75 $^{\circ}$ C unless specified otherwise)

| CHARACTERISTIC      | SYMBOL                        | MIN. | TYP.                             | MAX.              | UNIT | CONDITION                      |

|---------------------|-------------------------------|------|----------------------------------|-------------------|------|--------------------------------|

| One-sting frequency | f                             | f    | 2.5                              | 2.5               | MHz  | $V_{in} = 1 V_{p-p}$ , AM pin, |

| Operating frequency | ency f <sub>in1</sub> 0.5 2.5 | 2.5  | 2.5                              | DC cut, sine wave |      |                                |

|                     |                               |      | $V_{in} = 0.8 V_{p-p}$ , FM pin, |                   |      |                                |

| Operating frequency | †in2                          | 0.5  |                                  | 8.8               | MHz  | DC cut, square wave            |

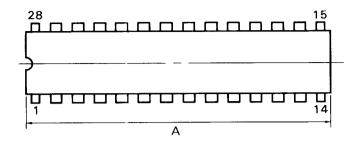

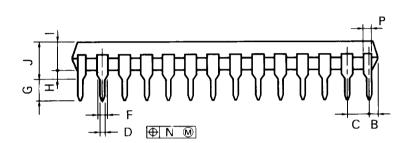

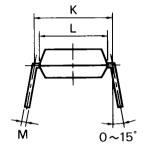

#### 7. PACKAGE DIMENSIONS (unit: mm)

# 28PIN PLASTIC DIP (400 mil)

P28C-100-400

#### **NOTES**

- Each lead centerline is located within 0.25 mm (0.01 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS  | INCHES        |

|------|--------------|---------------|

| Α    | 35.56 MAX.   | 1.400 MAX.    |

| В    | 1.27 MAX.    | 0.050 MAX.    |

| С    | 2.54 (T.P.)  | 0.100 (T.P.)  |

| D    | 0.50 - 0.10  | 0.020 0.004   |

| F    | 1.1 MIN.     | 0.043 MIN.    |

| G    | 3.5 - 0.3    | 0.138 10.012  |

| н    | 0.51 MIN.    | 0.020 MIN.    |

| ı    | 4.31 MAX.    | 0.170 MAX.    |

| J    | 5.72 MAX.    | 0.226 MAX.    |

| К    | 10.16 (T.P.) | 0.400 (T.P.)  |

| L    | 8.6          | 0.339         |

| М    | 0.25         | 0.010 + 0.004 |

| N    | 0.25         | 0.01          |

| Р    | 0.9 MIN.     | 0.035 MIN.    |